Professional Documents

Culture Documents

Universidad Autónoma de Yucatán: Facultad de Ingeniería

Universidad Autónoma de Yucatán: Facultad de Ingeniería

Uploaded by

Lucio Canché SantosOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Universidad Autónoma de Yucatán: Facultad de Ingeniería

Universidad Autónoma de Yucatán: Facultad de Ingeniería

Uploaded by

Lucio Canché SantosCopyright:

Available Formats

UNIVERSIDAD AUTNOMA DE YUCATN

FACULTAD DE INGENIERA

Digital Sistems II

Final Proyect: Conveyor

Canch Santos Lucio, Ojeda Flores Miguel, Santamara Gonzlez Micqui ABSTRACT As a final project for the Digital Systems II optative , a prototype of a conveyor that discriminates chips in base of the image that present is made. The sensing and the mechanic operation code are implemented in one FPGA, while the selection logic has been development in LabVIEW, getting as result that both platform are integrated through a Bluetooth module. Finally, this model is a prototype because we search to connect a Digital Camera to the FPGA by Serial Communication, getting as result a Vision System implemented in one Embedded System.

INTRODUCTION The conveyors are continuous transport systems, thus it can be found in the industry and others areas, like agricultural. The present project search to adapt, the system mentioned before, an optical medium to select pieces, getting an object classifier. DEVELOPMENT The present prototype involves areas that are very important to its development and control. To get a good explanation, it will be divided in the following steps: a)Mechanic and Electronic Assembling b) The conveyors Control c)The Selection Process a) Mechanic and Electronic Assembling To the mechanic assembling, were used too many recycling things, like the rail and some supports (these were useful to hold the camera and the servomotor). The main rail has several openings to adapt sensors, the griper of the servomotor (to get out the rejected coin), and the rails where are released the processed coins.

The electronic section has optocouplers that protect the FPGA ports. Besides, it has included transistors and comparators that condition the analogic signal.

O P T O A C O P L A D O R P U E R T O S C O N T R O

CNY70 SENSOR FOTORESISTOR SERVOMOTOR

E S

Figure 2. Electronic Interface b) Conveyors Control (FPGA) The control of the conveyor involves two State Machines: The first watch the mechanisms state and the sending the byte to get the picture, that depend if the coin is in the camera focus. When the FPGA receive the high level logic, from the sensor, it sends a Byte toward LabView by the UART, keeping itself in the waiting state to receive other byte that represents the classification of that coin after analyzed. That Byte is saved in the FIFO memory from the receptor UART, to store the results in order.

Waiting the Coin

Figure 1. Mechanic Assembling

Figure 3. Taking Picture Control

Take picture

Waiting the result Saiving in FIFO

UNIVERSIDAD AUTNOMA DE YUCATN

FACULTAD DE INGENIERA

Digital Sistems II

The second control the position degree of the servomotor. This amount depends of the received Byte, while each of this will be read if the FIFO isnt empty and the coin is released.

State. 2 State Machine

Figure 4. Decision Control

Wait for answer from LabVIEW

Figure 6. Invariant Moments

coin

To Read FIFO

Rejected coin (Sensor 1)

Accepted (Sensor 2)

*State #3 After a decision was took, based in the similarity of the Invariant Moments, a byte is sending to the FPGA, backing to the first state waiting the order to process other image

c) The Selection Process (LabVIEW) The central logic of LabVIEW consists in one State Machine, which has the following 3 states: *State #1 While the buffer doesnt receive any byte, the process stays in this state, in other case, pass to the next state. This let us to have a control of the sending Bytes, because the FPGA only receive information when is necessary.

State. 3 State Machine

Figure 7. Sending Byte CONCLUSIONES The use of an FPGA in the construction of industrial systems is very efficient, because it allows control over the whole system in a coordinated and synchronized way. Additionally, it is possible to control a set of mechanisms as presented in this report, so is possible to create a synchronized and controlled industrial network. It is intended to replace the camera from the computer for a digital camera with UART communication toward the FPGA, to sorting processes are performed on this platform and get a complete Embedded Vision System.

State. 1 State Machine

Figure 5. Reception Byte *State#2 By this SubVI, is implemented the calculus of the Invariant Moments of the captured image and is compared with the pattern image. .

You might also like

- PLC Report FileDocument36 pagesPLC Report FileRajat100% (2)

- EM9980 Service 4-117248A 09-2014 UkDocument48 pagesEM9980 Service 4-117248A 09-2014 UkIrimia MarianNo ratings yet

- Packet Tracer - Sensors and The PT MicrocontrollerDocument3 pagesPacket Tracer - Sensors and The PT MicrocontrollerMonalyn Señaris100% (1)

- Assignment 1Document12 pagesAssignment 1Mohamad HafizNo ratings yet

- Makalah Line Tracking Robot (By Opick Hidayato)Document36 pagesMakalah Line Tracking Robot (By Opick Hidayato)Opick HidayatoNo ratings yet

- Ultra Ir 10Document4 pagesUltra Ir 10Mani RamNo ratings yet

- GSM Based Arial Photography Using Remote Flying RobotDocument4 pagesGSM Based Arial Photography Using Remote Flying RobotseventhsensegroupNo ratings yet

- 2Document32 pages2oxygenmonitoringiotNo ratings yet

- Automated Intelligent Robot For Surveillance and SecurityDocument6 pagesAutomated Intelligent Robot For Surveillance and SecuritykillermaniNo ratings yet

- Int 0f ThingDocument5 pagesInt 0f Thingzahr49003usaNo ratings yet

- Akhila Sem (22Document10 pagesAkhila Sem (22ISHMAELNo ratings yet

- P1 IotDocument19 pagesP1 IotAmsalSilaban40% (5)

- SIMCON, Ver. 3.0.: FPGA Based, DSP Integrated, 8-ChannelDocument34 pagesSIMCON, Ver. 3.0.: FPGA Based, DSP Integrated, 8-ChanneljuanNo ratings yet

- Design and Implementation of Payload Camera Control System For Unmanned Aerial VehicleDocument7 pagesDesign and Implementation of Payload Camera Control System For Unmanned Aerial VehicleEditor IJTSRDNo ratings yet

- A Low-Cost Hardware-In-The-Loop Real Time Simulation of Control SystemsDocument4 pagesA Low-Cost Hardware-In-The-Loop Real Time Simulation of Control SystemsCarlos de la TorreNo ratings yet

- Underwater Robot Operation Using Optical Communication: Unit 1Document19 pagesUnderwater Robot Operation Using Optical Communication: Unit 1Sanjeev DesaiNo ratings yet

- Intelligent Street Lighting System Using GSMDocument9 pagesIntelligent Street Lighting System Using GSMSuweb RezaNo ratings yet

- Tracking For Studio CamerasDocument6 pagesTracking For Studio CamerasZAIDAN DIDINo ratings yet

- PC Based Robot Controlling Using Wireless Communication With ASK ModulationDocument74 pagesPC Based Robot Controlling Using Wireless Communication With ASK ModulationSyam Kumar SNo ratings yet

- Design of Programmable Logic Controller and I/O ExpansionsDocument5 pagesDesign of Programmable Logic Controller and I/O ExpansionsRanjan JlNo ratings yet

- PLC QuestionsDocument17 pagesPLC QuestionsbahyNo ratings yet

- ATM Terminal Design Based On Figure Print Recognition DocuDocument115 pagesATM Terminal Design Based On Figure Print Recognition DocuPraveen NaiduNo ratings yet

- Final Project Report E3390 Electronic Circuits Design Lab RFID Access Control SystemDocument28 pagesFinal Project Report E3390 Electronic Circuits Design Lab RFID Access Control Systemshanx77No ratings yet

- DC Motor Speed C BcontrolDocument6 pagesDC Motor Speed C BcontrolRoger RozarioNo ratings yet

- Programmable Logic Controller and Its ApplicationsDocument5 pagesProgrammable Logic Controller and Its Applicationssumit100% (1)

- Mechatronics UNIT4&5Document45 pagesMechatronics UNIT4&5saba78% (18)

- VHL Project First SubmissionDocument5 pagesVHL Project First SubmissionPragya SinghNo ratings yet

- Performance Task 1 - 2.3.1.2 Packet TracerDocument11 pagesPerformance Task 1 - 2.3.1.2 Packet TracernajsdnwuNo ratings yet

- Real-Time Implementation of Model Predictive Control in A Low-Cost Embedded DeviceDocument6 pagesReal-Time Implementation of Model Predictive Control in A Low-Cost Embedded DevicesamanNo ratings yet

- 2.3.1.2 Packet Tracer - Sensors and The PT MicrocontrollerDocument4 pages2.3.1.2 Packet Tracer - Sensors and The PT Microcontrollernaif arroishedNo ratings yet

- Case Study Autoclave AutomationDocument8 pagesCase Study Autoclave AutomationÖZER YILDIRIMNo ratings yet

- Apc 3 Module Notes - PLC and SCADA: Use of Relays in Process ControlDocument9 pagesApc 3 Module Notes - PLC and SCADA: Use of Relays in Process Control447 KusumanjaliNo ratings yet

- Verilog Project Report FinalDocument14 pagesVerilog Project Report FinalSandip SolankiNo ratings yet

- Design of Multi-Detrct Surface Algorithm For Home Vacuum Aplication - Mohamad Sahran B. Kamilan - TJ223.P76.M77 2008Document27 pagesDesign of Multi-Detrct Surface Algorithm For Home Vacuum Aplication - Mohamad Sahran B. Kamilan - TJ223.P76.M77 2008Nasir JamshedNo ratings yet

- Automatic Railway Signalling SystemDocument74 pagesAutomatic Railway Signalling SystemVinayakNo ratings yet

- Lab 1Document7 pagesLab 1MoapeNo ratings yet

- Fuzzy Mamdani Logic Inference Model in The Loading of Distribution Substation Transformer SCADA SystemDocument8 pagesFuzzy Mamdani Logic Inference Model in The Loading of Distribution Substation Transformer SCADA SystemIAES IJAINo ratings yet

- PLC Training LiteratureDocument45 pagesPLC Training Literaturealex2gustavo2cuevas2No ratings yet

- Design and Implementation of PLC-Based Monitoring and Sequence Controller SystemDocument9 pagesDesign and Implementation of PLC-Based Monitoring and Sequence Controller SystemMohammed SelmanNo ratings yet

- Control of Electric Drives - D. RamírezDocument187 pagesControl of Electric Drives - D. RamírezCarlos NavarroNo ratings yet

- Microcontroller Based Automatic GateDocument12 pagesMicrocontroller Based Automatic GateAndyNo ratings yet

- Fuzzy Logic Reasoning System For Line Following RobotDocument5 pagesFuzzy Logic Reasoning System For Line Following RobotThảo Dương Thị MinhNo ratings yet

- Ei6002 Power Plant Instrumentation Question BankDocument23 pagesEi6002 Power Plant Instrumentation Question BankLokesh GopinathNo ratings yet

- Control of Two Robotic Platforms Using Multi-Agent SystemsDocument20 pagesControl of Two Robotic Platforms Using Multi-Agent SystemsJaime Andres Rincon Arango100% (1)

- Robojoint Project Addendum: Colin MccarthyDocument30 pagesRobojoint Project Addendum: Colin MccarthySusheela SubramaniumNo ratings yet

- GSM Based Automatic Electricity Billing SystemDocument6 pagesGSM Based Automatic Electricity Billing SystemIJARTETNo ratings yet

- InfoMatrix Abstract PocketBot Project - Ondrej Stanek CZDocument5 pagesInfoMatrix Abstract PocketBot Project - Ondrej Stanek CZLita ClaudiuNo ratings yet

- A Car 20110206Document10 pagesA Car 20110206VICTORSJNo ratings yet

- Iocrsem Ec 21Document4 pagesIocrsem Ec 21Shailesh PatilNo ratings yet

- Integration of Electronic Speed Governor With RFID Technology For Speed LimitingDocument86 pagesIntegration of Electronic Speed Governor With RFID Technology For Speed LimitingNithinReddy100% (1)

- Communication Antenna Switching System Based On Micro ControllerDocument4 pagesCommunication Antenna Switching System Based On Micro ControllerAjay Kumar YadavNo ratings yet

- PLC 1703025724Document14 pagesPLC 1703025724Yeyen RoyhanNo ratings yet

- EIA Notes - Week 2Document7 pagesEIA Notes - Week 2BHARAT NIKKAMNo ratings yet

- Embedded System SolveDocument15 pagesEmbedded System SolveAshish OjhaNo ratings yet

- Lect 11 21 PLCDocument58 pagesLect 11 21 PLCraja_liaqatNo ratings yet

- A R G C: Utomatic Ailway ATE OntrolDocument14 pagesA R G C: Utomatic Ailway ATE OntrolswaarnNo ratings yet

- A Master-Slave DSP Board For Digital ControlDocument5 pagesA Master-Slave DSP Board For Digital Controlfurious143No ratings yet

- Obstacle Avoidance Robot Using Ultrasonic Sensors - FPGAVHDLDocument18 pagesObstacle Avoidance Robot Using Ultrasonic Sensors - FPGAVHDLDipak Bhogulkar100% (1)

- Ij3c 4Document15 pagesIj3c 4Philippe Englert VelhaNo ratings yet

- Advanced Techniques and Technology of Computer-Aided Feedback ControlFrom EverandAdvanced Techniques and Technology of Computer-Aided Feedback ControlNo ratings yet

- Term Paper: Topic: "Document16 pagesTerm Paper: Topic: "Suraj KumarNo ratings yet

- The Mythical Man-MonthDocument56 pagesThe Mythical Man-Monthwooppoowwoop86% (7)

- IC-A23 Service ManualDocument38 pagesIC-A23 Service ManualgeorgeclimaNo ratings yet

- W1PA Sep22Document11 pagesW1PA Sep22Omkar AkulwarNo ratings yet

- Configure IP Address For Ethernet Port PrintersDocument6 pagesConfigure IP Address For Ethernet Port Printersjairson MonteiroNo ratings yet

- Manufacture of Rocket Motor Cases Using Advanced FilameDocument11 pagesManufacture of Rocket Motor Cases Using Advanced FilameSumithrananthanNo ratings yet

- BS en 1926:2006Document20 pagesBS en 1926:2006lkzasj dksikNo ratings yet

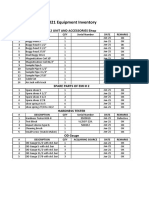

- 2021 Equipment Inventory: Emi 2 Unit and Accessories EitopDocument1 page2021 Equipment Inventory: Emi 2 Unit and Accessories Eitoptafani electricalNo ratings yet

- G3WD 21Document1 pageG3WD 21Иван КадигробNo ratings yet

- ProjectS 2Document25 pagesProjectS 2Ngân Võ Trần TuyếtNo ratings yet

- Man 75-100udg T1 05-15-08Document59 pagesMan 75-100udg T1 05-15-08Miguel Morales Ch100% (1)

- 1.2 FIBONACCI SEQUENCE TTH 12Document11 pages1.2 FIBONACCI SEQUENCE TTH 12Kris CruzNo ratings yet

- Demo Digital Alarm Clock Assembly Source CodeDocument3 pagesDemo Digital Alarm Clock Assembly Source CodeBảo Bình0% (1)

- FFV4Q4-65B-R7 Product SpecificationsDocument6 pagesFFV4Q4-65B-R7 Product SpecificationsyohnnisNo ratings yet

- hw3 SolDocument3 pageshw3 SolDylan LerNo ratings yet

- ch08 SamplingDistDocument43 pagesch08 SamplingDistSeçkin DilekNo ratings yet

- Photoelastic Unit: Technical Teaching EquipmentDocument5 pagesPhotoelastic Unit: Technical Teaching EquipmentpondpakkaNo ratings yet

- Lab02 PDFDocument12 pagesLab02 PDFSiddharth KumraNo ratings yet

- Troubleshooting Uso de CRT ConsolaDocument47 pagesTroubleshooting Uso de CRT ConsolaJorge MartinelliNo ratings yet

- صادق سالم محمد Practicle Cycle and its CalculationDocument18 pagesصادق سالم محمد Practicle Cycle and its Calculationعبدالمحسن علي ENo ratings yet

- UNIT-5: Micro Controller Programming and ApplicationsDocument19 pagesUNIT-5: Micro Controller Programming and ApplicationsSeshan KumarNo ratings yet

- The Secondary CellDocument21 pagesThe Secondary CellMaira PervezNo ratings yet

- Secondary (Mathematics) Legazpi 9-2019 PDFDocument46 pagesSecondary (Mathematics) Legazpi 9-2019 PDFPhilBoardResultsNo ratings yet

- Conducting Strength Tests of Masonry Wall Panels: Standard Test Methods ForDocument6 pagesConducting Strength Tests of Masonry Wall Panels: Standard Test Methods ForOsama BashirNo ratings yet

- CRV User Manual 39 41Document3 pagesCRV User Manual 39 41andi ishakaNo ratings yet

- Gentoo Handbook Amd 64Document105 pagesGentoo Handbook Amd 64Mirza Nazim BegNo ratings yet

- Composición 1Document1 pageComposición 1mayraeb13No ratings yet

- 3b.boiler Treatment MethodsDocument76 pages3b.boiler Treatment Methodsalokbdas100% (1)