Professional Documents

Culture Documents

State Machines

State Machines

Uploaded by

Vikram KulkarniOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

State Machines

State Machines

Uploaded by

Vikram KulkarniCopyright:

Available Formats

Review: State Machine Charts

SM chart or ASM ( Algorithmic State Machine) chart Easier to understand the operation of digital system by examining of the SM chart instead of equivalent state graph SM chart leads directly to hardware realization

CPE/EE 422/522 Advanced Logic Design L16

Electrical and Computer Engineering University of Alabama in Huntsville

21/07/2003

UAH-CPE/EE 422/522 AM

Components of SM charts

SM Blocks

SM chart is constructed from SM blocks

State S1 is entered => Z1 and Z2 become 1 if X1=0 Z3 and Z4 become 1 if X1=1 and X3=0 Z5 become 1

21/07/2003

UAH-CPE/EE 422/522 AM

21/07/2003

UAH-CPE/EE 422/522 AM

Equivalent SM Blocks

Equivalent SM Charts for Comb Networks

21/07/2003

UAH-CPE/EE 422/522 AM

21/07/2003

UAH-CPE/EE 422/522 AM

Block with Feedback

Equivalent SM Blocks

21/07/2003

UAH-CPE/EE 422/522 AM

21/07/2003

UAH-CPE/EE 422/522 AM

Converting a State Graph to an SM Chart

Networks for Arithmetic Operations

Case Study: Serial Adder with Accumulator

21/07/2003

UAH-CPE/EE 422/522 AM

21/07/2003

UAH-CPE/EE 422/522 AM

10

Networks for Arithmetic Operations

Serial Adder with Accumulator

State Graphs for Control Networks

Use variable names instead of 0s and 1s

E.g., XiXj/ZpZq

if Xi and Xj inputs are 1, the outputs Zp and Zq are 1 (all other outputs are 0s)

E.g., X = X1X2X3X4, Z = Z1Z2Z3Z4

X1X4/Z2Z3 == 1 - - 0 / 0 1 1 0

21/07/2003

UAH-CPE/EE 422/522 AM

11

21/07/2003

UAH-CPE/EE 422/522 AM

12

Constraints on Input Labels

Assume: I input expression => we traverse the arc when I=1

Constraints on Input Labels (contd)

Assures that at most one input label can be 1 at any given time

Assures that at least one input label will be 1 at any given time 1 + 2: Exactly one label will be 1 => the next state will be uniquely defined for every input combination

21/07/2003

UAH-CPE/EE 422/522 AM

13

21/07/2003

UAH-CPE/EE 422/522 AM

14

Networks for Arithmetic Operations

Case Study: Serial Parallel Multiplier

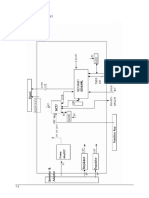

Block Diagram of a Binary Multiplier

Note: we use unsigned binary numbers Ad add signal // adder outputs are stored into the ACC Sh shift signal // shift all 9 bits to right Ld load signal // load multiplier into the 4 lower bits of the ACC and clear the upper 5 bits

21/07/2003 UAH-CPE/EE 422/522 AM 15 21/07/2003 UAH-CPE/EE 422/522 AM 16

Multiplication Example

State Graph for Binary Multiplier

21/07/2003

UAH-CPE/EE 422/522 AM

17

21/07/2003

UAH-CPE/EE 422/522 AM

18

Behavioral VHDL Model

Behavioral VHDL Model (contd)

21/07/2003

UAH-CPE/EE 422/522 AM

19

21/07/2003

UAH-CPE/EE 422/522 AM

20

Multiplier Control with Counter

Current design: control part generates the control signals (shift/add) and counts the number of steps If the number of bits is large (e.g., 64), the control network can be divided into a counter and a shift/add control

Multiplier Control with Counter (contd)

Add-shifts control: tests St and M and generates the proper sequence of add and shift signals Counter control: counter generates a completion signal K that stops the multiplier after the proper number of shifts have been completed

21/07/2003

UAH-CPE/EE 422/522 AM

21

21/07/2003

UAH-CPE/EE 422/522 AM

22

Multiplier Control with Counter (contd)

Operation of a Multiplier Using Counter

Increment counter each time a shift signal is generated Generate K after n-1 shifts occured

21/07/2003

UAH-CPE/EE 422/522 AM

23

21/07/2003

UAH-CPE/EE 422/522 AM

24

Array Multiplier

Array Multiplier (contd)

What do we need to realize Array Multiplier? AND gates = ? FA = ? HA = ?

21/07/2003 UAH-CPE/EE 422/522 AM 25 21/07/2003 UAH-CPE/EE 422/522 AM 26

Array Multiplier (contd)

Complexity of the N-bit array multiplier

number of AND gates = ? number of HA = ? number of FA = ?

Multiplication of Signed Binary Numbers

How to multiply signed binary numbers? Procedure

Complement the multiplier if negative Complement the multiplicand if negative Multiply two positive binary numbers Complement the product if it should be negative

Delay

tg longest AND gate delay tad longest possible delay through an adder

Simple but requires more hardware and time than other available methods

21/07/2003

UAH-CPE/EE 422/522 AM

27

21/07/2003

UAH-CPE/EE 422/522 AM

28

Multiplication of Signed Binary Numbers

Four cases

Multiplicand is positive, multiplier is positive Multiplicand is negative, multiplier is positive Multiplicand is positive, multiplier is negative Multiplier is negative, multiplicand is negative 0111 x 0101 = ? 1101 x 0101 = ? 0101 x 1101 = ? 1011 x 1101 = ?

Preserve the sign of the partial product at each step If multiplier is negative, complement the multiplicand before adding it in at the last step

2s Complement Multiplier

Examples

21/07/2003

UAH-CPE/EE 422/522 AM

29

21/07/2003

UAH-CPE/EE 422/522 AM

30

State Graph for 2s Complement Multiplier

Faster Multiplier

Move wires from the adder outputs one position to the right => add and shift can occur at the same clock cycle

21/07/2003 UAH-CPE/EE 422/522 AM 31 21/07/2003 UAH-CPE/EE 422/522 AM 32

State Graph for Faster Multiplier

Behavioral Model for Faster Multiplier

21/07/2003

UAH-CPE/EE 422/522 AM

33

21/07/2003

UAH-CPE/EE 422/522 AM

34

Behavioral Model for Faster Multiplier

Command File and Simulation

21/07/2003

UAH-CPE/EE 422/522 AM

35

21/07/2003

UAH-CPE/EE 422/522 AM

36

Test Bench for Signed Multiplier

21/07/2003

UAH-CPE/EE 422/522 AM

37

10

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Practical Guides to Testing and Commissioning of Mechanical, Electrical and Plumbing (Mep) InstallationsFrom EverandPractical Guides to Testing and Commissioning of Mechanical, Electrical and Plumbing (Mep) InstallationsRating: 4 out of 5 stars4/5 (4)

- Samsung Panel Repair V1.7Document35 pagesSamsung Panel Repair V1.7Anonymous HAVOQ8995% (132)

- 365 Final Project Bernacki DykeDocument51 pages365 Final Project Bernacki Dykeapi-312670860No ratings yet

- VLSI TimingDocument23 pagesVLSI TimingAhmed ZЗzЗNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-18: Memory Elements, Busses, RegistersDocument26 pagesCPS 104 Computer Organization and Programming Lecture-18: Memory Elements, Busses, RegistersprachesNo ratings yet

- Summary Last Lecture - Continuous-Time Filters (Continued)Document32 pagesSummary Last Lecture - Continuous-Time Filters (Continued)Jo KontNo ratings yet

- Cs2100 6 Combinational CircuitsDocument61 pagesCs2100 6 Combinational CircuitsamandaNo ratings yet

- Analog - Digital - PC Based - PidDocument18 pagesAnalog - Digital - PC Based - PidAAYUSH KUMARNo ratings yet

- TMS320F2812-Analogue To Digital ConverterDocument26 pagesTMS320F2812-Analogue To Digital ConverterPantech ProLabs India Pvt LtdNo ratings yet

- Compensation DesignDocument24 pagesCompensation Designarohianand27100908No ratings yet

- L8-Complex FSM 3pDocument14 pagesL8-Complex FSM 3pAlbertoCasNo ratings yet

- MSDACDocument40 pagesMSDACSonu Alam100% (1)

- Elexp: Instruction ManualDocument11 pagesElexp: Instruction ManualMohd Abu AjajNo ratings yet

- Motor Design Suite V12Document60 pagesMotor Design Suite V12Trần Trung HiếuNo ratings yet

- Topic10 Introduction To The Analog To Digital Subsystem On The Freescale MC9S12X.Document61 pagesTopic10 Introduction To The Analog To Digital Subsystem On The Freescale MC9S12X.Brett WildermothNo ratings yet

- Samsung Sync Master 930bf Chassis Bi17ds Bi19ds Ls17 19bidks SMDocument74 pagesSamsung Sync Master 930bf Chassis Bi17ds Bi19ds Ls17 19bidks SMBradaric BrunoNo ratings yet

- Small Signal Amplifiers Eet3Document67 pagesSmall Signal Amplifiers Eet3Dan ChapsNo ratings yet

- Ecodial 3-3 PDFDocument75 pagesEcodial 3-3 PDFFatena Ha100% (1)

- EFACEC - The Topology ProcessorDocument15 pagesEFACEC - The Topology ProcessorbernardosilvabastosNo ratings yet

- Manual Calculadora ElectricaDocument68 pagesManual Calculadora Electrica12345No ratings yet

- Introduction To Switched-Mode Converter Modeling Using MATLAB/SimulinkDocument37 pagesIntroduction To Switched-Mode Converter Modeling Using MATLAB/SimulinkAhana MalhotraNo ratings yet

- Review: Designing With FSM: Work Together WellDocument11 pagesReview: Designing With FSM: Work Together Welljatanbhatt89100% (1)

- Lecture06 Signal Flow GraphDocument13 pagesLecture06 Signal Flow GraphSai AdarshNo ratings yet

- Amec Spie Kelsop Info UkDocument7 pagesAmec Spie Kelsop Info UkjulesjusayanNo ratings yet

- PTI Section 9 Analog DigitalDocument14 pagesPTI Section 9 Analog Digitalchrist9088No ratings yet

- Fawad Cep ReportDocument26 pagesFawad Cep ReportFawad ArifNo ratings yet

- (Model No:VBMB - 002) : 8-Bit Digital To Analog Converter Interface BoardDocument56 pages(Model No:VBMB - 002) : 8-Bit Digital To Analog Converter Interface BoardSanthanu Surendran100% (1)

- EE 367 - Logic Design: AgendaDocument6 pagesEE 367 - Logic Design: Agendadivya1587No ratings yet

- 1630481949539-Msdac Etw NewDocument52 pages1630481949539-Msdac Etw NewAshim ChakrabortyNo ratings yet

- Samsung Panel RepairDocument18 pagesSamsung Panel RepairRiyad Abdulhafeed Sharaf100% (2)

- Egcp 3 MC: DescriptionDocument4 pagesEgcp 3 MC: DescriptionJuan Jose RodriguezNo ratings yet

- Lecture 5Document39 pagesLecture 5Anonymous PaUyyhf1OTNo ratings yet

- BJT Ebers-Moll Model and SPICE MOSFET ModelDocument40 pagesBJT Ebers-Moll Model and SPICE MOSFET ModelDragana MladjenovicNo ratings yet

- L21 ECEN5827 NotesDocument21 pagesL21 ECEN5827 Notes3nadhsNo ratings yet

- Isoparametric Elements and Solution TechniquesDocument41 pagesIsoparametric Elements and Solution Techniquessir867413140No ratings yet

- DPCO Unit1 Two Marks Q&ADocument17 pagesDPCO Unit1 Two Marks Q&Akanimozhi rajasekarenNo ratings yet

- ADE7753 EvalBoardDocument20 pagesADE7753 EvalBoardRicardo Hyppolite FleriscatNo ratings yet

- By Robert Prieto, Associate Professor, Universidad: Power Electronics Technology March 2005Document5 pagesBy Robert Prieto, Associate Professor, Universidad: Power Electronics Technology March 2005Constantin DorinelNo ratings yet

- Chapter 7. PROGRAMMABLE Logic Controller: Dr. T.C. Chang School of Industrial Engineering Purdue UniversityDocument57 pagesChapter 7. PROGRAMMABLE Logic Controller: Dr. T.C. Chang School of Industrial Engineering Purdue UniversityAishwarya Kumar PandeyNo ratings yet

- CE1000Document581 pagesCE1000Mike WilsonNo ratings yet

- Mec500 Chapter 2 - AtmaDocument31 pagesMec500 Chapter 2 - AtmaFaez FeakryNo ratings yet

- PExprt v71 L01 IntroductionDocument26 pagesPExprt v71 L01 IntroductionEdwin C. Abregú100% (2)

- Mathcad - Opamp 1974Document7 pagesMathcad - Opamp 1974Frank KarthikNo ratings yet

- Module 3Document121 pagesModule 3venuraoNo ratings yet

- Using The ADC0808/ADC0809 8-Bit P Compatible A/D Converters With 8-Channel Analog MultiplexerDocument23 pagesUsing The ADC0808/ADC0809 8-Bit P Compatible A/D Converters With 8-Channel Analog MultiplexerRiskyNo ratings yet

- Low Power and Area Delay Efficient Carry Select AdderDocument92 pagesLow Power and Area Delay Efficient Carry Select AdderKiran KumarNo ratings yet

- Euler's PathDocument10 pagesEuler's PathSatish Kumar0% (1)

- GVT Case Study Solutionv2Document3 pagesGVT Case Study Solutionv2johnknight000No ratings yet

- Closed Loop Control System (CSL - 04) : Technical Manual FORDocument19 pagesClosed Loop Control System (CSL - 04) : Technical Manual FORAAYUSH KUMARNo ratings yet

- CMOS Logic DesignDocument35 pagesCMOS Logic DesignsomosreeNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveدانشجویان فوق لیسانس الکترونیک 91 سیرجانNo ratings yet

- Marwan K. Abbadi Advisor: Dr. Winfred AnakwaDocument35 pagesMarwan K. Abbadi Advisor: Dr. Winfred AnakwaAniruddha NarkhedeNo ratings yet

- 7-2 Main Board Part: 7 Block DiagramsDocument14 pages7-2 Main Board Part: 7 Block DiagramsAlbert OstNo ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Introduction To HCIDocument29 pagesIntroduction To HCIChristian Bulan CorpuzNo ratings yet

- DataDocument272 pagesDataomgan1042No ratings yet

- Lab 2Document6 pagesLab 2Martha Nita FlorentinaNo ratings yet

- Medical Registeration-RetiredDocument2 pagesMedical Registeration-RetiredAsadAli50% (2)

- Jbase EditorDocument53 pagesJbase EditorMamat AdoumaNo ratings yet

- Baca Gratis Ebook Novel Terjemahan Fifty Shades DarkerDocument3 pagesBaca Gratis Ebook Novel Terjemahan Fifty Shades DarkerRina KusnawatyNo ratings yet

- Creative UI Design by Cosmin Capitanu - Abduzeedo Design InspirationDocument18 pagesCreative UI Design by Cosmin Capitanu - Abduzeedo Design InspirationLeonardo MontoyaNo ratings yet

- PeopleSoft Administration ToolsDocument134 pagesPeopleSoft Administration ToolsEzequiel Moreira100% (1)

- Ps 0Document3 pagesPs 0Rupesh ParabNo ratings yet

- Guy Kawasaki Presantation - Turkcell Teknoloji Zirvesi SunumDocument55 pagesGuy Kawasaki Presantation - Turkcell Teknoloji Zirvesi SunumArda KutsalNo ratings yet

- Chapter 1Document34 pagesChapter 1api-3805856No ratings yet

- The COPAR ProcessDocument2 pagesThe COPAR ProcessMicMic PadillaNo ratings yet

- Pitram Fleet ManagementDocument2 pagesPitram Fleet ManagementJean-Paul MwambaNo ratings yet

- Electroplating Engineering Handbook: Printed BookDocument1 pageElectroplating Engineering Handbook: Printed BookasnazfywNo ratings yet

- Cs701 Data Warehouse and Data MiningDocument23 pagesCs701 Data Warehouse and Data MiningMahara Jothi EswaranNo ratings yet

- VBSCriptDocument8 pagesVBSCriptShiv ShankarNo ratings yet

- Proceeding Book - Mahsa MinaeiDocument8 pagesProceeding Book - Mahsa MinaeiKshitij NashineNo ratings yet

- Master Production ScheduleDocument10 pagesMaster Production ScheduleUn IntNo ratings yet

- FEMA P752 NONLIN EQTools PDFDocument1 pageFEMA P752 NONLIN EQTools PDFRolex11No ratings yet

- Jail Breaking - iOS SecurityDocument7 pagesJail Breaking - iOS SecurityKai ArasNo ratings yet

- Getting Started With JavaCCDocument9 pagesGetting Started With JavaCCtruthraNo ratings yet

- BrochureDocument2 pagesBrochurejoydeepsen06No ratings yet

- Cairo-Media & Protest - CodebookDocument3 pagesCairo-Media & Protest - CodebookgmNo ratings yet

- Location Wise Stock For RegionDocument3 pagesLocation Wise Stock For RegionFarNo ratings yet

- Btech NC 3 Sem Python Programming knc302 2022Document2 pagesBtech NC 3 Sem Python Programming knc302 2022Anushka ChaudharyNo ratings yet

- Elec4633 Lab 1Document9 pagesElec4633 Lab 1billNo ratings yet

- Grade 11 Maths Paper 1 Exemplar 2013 MemoDocument2 pagesGrade 11 Maths Paper 1 Exemplar 2013 MemoMeganNo ratings yet

- 100 Top Data Structures and Algorithms Multiple Choice Questions and AnswersDocument31 pages100 Top Data Structures and Algorithms Multiple Choice Questions and AnswersSantosh RathodNo ratings yet

- Unit 5 Embedded System Development EnvironmentDocument22 pagesUnit 5 Embedded System Development EnvironmentAakarsh KumarNo ratings yet

- Brochure - TemplateDocument4 pagesBrochure - TemplateZamri HashimNo ratings yet