Professional Documents

Culture Documents

CSCE 313 Embedded Systems Design

CSCE 313 Embedded Systems Design

Uploaded by

Sudhakar SpartanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CSCE 313 Embedded Systems Design

CSCE 313 Embedded Systems Design

Uploaded by

Sudhakar SpartanCopyright:

Available Formats

CSCE 313 Embedded Systems Design

2004/1/12

Lecture 1 Overview of Embedded Systems & Architecture

2003 Dr. James P. Davis

Some figures from Tanenbaum 1999 Prentice Hall Publishers, Inc.

CSCE 313 Lecture 1 - Outline

z

Introduction

9 9 9 9

Why this course is important to Computer Engineering. Drivers for Embedded Systems. Example: Wireless Communications. The CPU is the Heart of an Embedded System.

Computer Architecture

9 9 9 9

Computer Engineering Design Space (Y-chart). Abstraction Levels and Representation Domains. Organization of a Computing System. Organization of the CPU.

Course Drivers

9 9 9 9

The CPU architecture and programming model. The layers of the virtual machine (the Instruction Set Architecture). The program development process. Operating at the Hardware-Software boundary.

2003 Dr. James P. Davis

Page 2

Embedded Systems - The New Realities

Telecomm

Computers

Consumer Electronics

VLSI Silicon "chip"

"At the root of cascading changes of modern economic life...devaluing resources in technology, business and geopolitics...overcoming the the constraints of material resources, the microchip has devalued most large accumulations of physical capital and made possible the launching of global economic enterprises...microchips find their value not in their substance but in their intellectual content: their design..." George Gilder, Microcosm, 1989

2003 Dr. James P. Davis

Page 3

Embedded Systems - Industry Drivers

z

Many market and technology factors coming together to create pressure on electronics product engineering organizations worldwide.

9 9 9 9 9 9 9 9

Increasing global competition and new markets. Increasing rate of product innovations and new product introductions. Decreasing time-to-market windows. Decreasing shelf life for products in many categories. Increasing pressure on competitive cost containment, profit margins. Increasing convergence: integrated functionality in single electronics devices and product packages. Increasing quality expectations: means for containing distribution and support costs. Increasing innovation in silicon process technology and wafer scale integration densities, also in embedded software technologies.

Increasing disparity: capacity of the underlying technologies versus capability of designers to manage increasing design complexity.

2003 Dr. James P. Davis

Page 4

The Capacity vs. Capability Gap

z

Increasing capacity of the technology:

9

The rate of new technology and associated silicon process changes has continued to follow Moores Law.

24

10,000K

The capability of designers and design teams to use 9 this capacity isnt keeping Months up.

9 9

Device Capacity

D esign Size

Product Tim e-to-Market The Capacity versus Capability Gap is widening. 1,000K Each set of technology and process changes requires 3 designers to manage ever Design Capability more complexity in the design 100K process. New architectures, 1985 1990 1995 2000 abstractions, methods and Source: Dataquest tools are required to address this increasing complexity.

2003 Dr. James P. Davis

Page 5

Example Wireless Communications

z

Range

The market is seeking product technology options to cover different geography ranges and data rates.

9 9 9

Bluetooth WPAN. IEEE 802.11 - WLAN. 2/3G Network WWAN.

WWAN

The opportunity for creating value chains encompassing product offerings, distribution and new service offerings hinges on the ability to get low cost solutions to market quickly.

9 9 9

G2/G3 Network CDMA

WPAN WLAN

Deliver content to wireless handheld devices. Function convergence in the handset and at the base station. Requires large cross-functional design teams in varied disciplines.

Blue Tooth 802.11b

IEEE802.11a Data Rate

Source: Knowledge Edge KK

2003 Dr. James P. Davis

Page 6

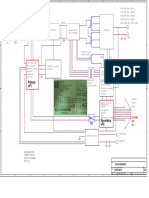

Embedded System 802.11 WLAN NIC

C P U c o re D ie a re a

4 .9 m m 2 o n 0 .1 8 m e s tim a te d s ize w ith 1 6 K B in s tru c tio n & 4 K B d a ta c a c h e s a n d n o TCM s U s in g A rtis a n c e ll lib ra ry & R A M co m p ile r

Peak Pow er C o n s u m p tio n (m W /M H z )

M e m o ry S ys te m

S e le c ta b le I & D c a c h e s ize s : 0 , 4 K , 8 K ... 1 M S e le c ta b le I & D T C M size s : 0 , 4 K , 8 K ... 1 M

C lo c k fre q u e n c y & M IP S p e rfo rm a n c e

150M H z on TSM C 0 .1 8 m (w o rs t case) 230M H z on TSM C 0 .1 8 m (typ ic a l)

A R M 9 E / A R M 9 4 6 E -S c a c h e d p ro c e s s o r w ith tig h tly c o u p le d m e m o ry in te rfa c e s

1 .1 m W /M H z @ 1 .8 V (e s tim a te d )

M AC c o n tro lle r BUS in te rfa c e RF F ro n t End BBP M AC

d e v ic e d riv e r (b a s ic fu n c tio n c a ll, m e m o ry c o n tro l e tc .

P ro to c o l S ta c k & OS k e rn e l

C lie n t d riv e r Ap p lic a tio n AP d riv e r

T a rg e t B B P & M A C C o n tro lle r C h ip

S o ftd rive r

PHY

M AC

M e m o ry b lo c k (4 ~ 1 5 k B ) + c o n tro l b lo c k

O n c h ip m e m o ry d e p e n s o n firm w a re s iz e (1 0 0 ~ 2 0 0 K B ) th e F W s iz e d e p e n d s o n th e M A C fe a tu re 1 1 e & i?

1 0 K g a te s P C I/P C M C IA

Source: Knowledge Edge KK

Page 7

2003 Dr. James P. Davis

Computing System Design Space (Y-chart)

Most embedded systems exist at this level of systems design abstraction.

2003 Dr. James P. Davis

Page 8

Categories of Digital Systems Design

"Layered" Computing System

z

Electronic systems today are of different types, depending on the (1) function, (2) application.

9

VLSI hardware microcode machine code operating system application

ASICs and FPGAs

Classes of Electronic Systems

Embedded System

ROM RAM

uC

9

I/O

On-chip System

9

Computing system: CPU and hardware executing O/S, with applications running on top of O/S. Embedded system: fixedfunctions, instruction-based micro-controller with both hardware and software components. On-chip system: complete control and data functions implemented in "custom logic" VLSI package. On-chip systems can be components of embedded systems, which can be part of a layered "virtual" machine. All these systems do interface with the outside analog world.

2003 Dr. James P. Davis

Page 9

Continuum of Embedded System Types

We want the development productivity and existing code base using a standard CPU We want the higher speed and lower power consumption of a custom logic package.

Industry trends have us focusing on the use of CPU cores and EEPROM/Flash memory packaged with other logic in reconfigurable FPGA devices for small form-factor products (e.g., PDAs).

2003 Dr. James P. Davis

Page 10

Computer Structure & Organization-1

z

Basic systems components of Computer:

9

CPU, Memory, I/O Devices, Bus

CPU decomposes into basic components:

9

Control unit, Arithmetic Logic Unit (ALU), Registers

Source: Tanenbaum, 4th ed. 1999, Prentice-Hall

2003 Dr. James P. Davis

Page 11

Computer Structure & Organization-2

z

Von Neumann computer architecture:

9

Developed in the late 1940s by John Von Neumann (Princeton U.) Combined the elements of stored program machine: one machine could run many programs. Program instructions stored in memory and fetched, in sequence, to be executed by CPU. Results of execution stored in Registers, later written back to memory.

Source: Tanenbaum, 4th ed. 1999, Prentice-Hall

2003 Dr. James P. Davis

Page 12

Computer Structure & Organization-3

z

Instruction Sequencing 9 This CPU has the sequencing of data path operations by one or more state machines 9 The example shown is the data path for a small CPU, where microoperations based on program instructions are decoded and staged to execute multicycle instructions out of memory. 9 This example also used pipelining (discussed on next slide).

Source: Tanenbaum, 4th ed. 1999, Prentice-Hall

2003 Dr. James P. Davis

Page 13

Computer Structure & Organization-4

z

N-Stage Pipeline

9

Pipeline allows serial processing, in sequence, of instructions or data elements. Each n-element in the pipeline processes its task, then passes the element to the stage n+1 in the pipeline. Design structures that use pipelining: CPU Instruction Fetch Unit (IFU), Digital filters (e.g., FIR, IIR).

Source: Tanenbaum, 4th ed. 1999, Prentice-Hall

2003 Dr. James P. Davis

Page 14

Computer Structure & Organization-5

Pipelining Instructions

The sequence of figures show how pipelining works in the control path. The control pipelining is the Instruction Fetch, Decode, Execute cycle used in all CPU architectures. Each stage of the control pipeline is buffered by registers that provide setup of data. The different stages of the pipeline also use handshaking.

2003 Dr. James P. Davis

Source: Tanenbaum, 4th ed. 1999, Prentice-Hall

Page 15

Summary - What Youll Get in This Course

z

This course is about analysis, architecture and programming of digital embedded systems.

9 9

We assume the presence of a CPU, and therefore our primary task is to implement functionality using the CPUs Instruction Set. We are concerned about efficiencyin terms of execution speed of instructions, and in the amount of memory we consumeto get a specific programming task accomplished.

You will learn development process, assembler program design methods, and program verification framework, allowing you to take an embedded systems application, analyze it, and implement it.

9 9

Iterative enhancement, top-down/bottom-up, stepwise refinement (stables of software engineering discipline) Additional heuristics in relating properties of the CPUs computer architecture (instruction set, bus structure, interrupt handling, etc.) to the embedded systems application, to make the systems planning process more effective.

You will learn how to evaluate the goodness of your embedded systems programs based on the use of tools, and by collecting and analyzing program execution data to tune your programs.

9

Well use the WISM68K emulator/debugger, and the 68KMB hardware lab apparatus as our tools.

2003 Dr. James P. Davis

Page 16

You might also like

- RE10, RG8, RF8 SeriesDocument330 pagesRE10, RG8, RF8 Seriesanggie93% (58)

- Computer Organization and Architecture 10th Edition Stallings Test BankDocument8 pagesComputer Organization and Architecture 10th Edition Stallings Test BankShirley Wynder100% (35)

- Multicore Processors and Systems PDFDocument310 pagesMulticore Processors and Systems PDFwkfzar100% (1)

- EDUC5711 Week 8 Discussion Assignment Unit 8Document3 pagesEDUC5711 Week 8 Discussion Assignment Unit 8Meleisa WrayNo ratings yet

- Explorent - Micro-Laryngoscopy-CatalogueDocument80 pagesExplorent - Micro-Laryngoscopy-Cataloguedrtarek255442No ratings yet

- Unlawful Detainer CCP 1161a Foreclosure Sale Ud Issues of Title General Equitable ConsiderationsDocument38 pagesUnlawful Detainer CCP 1161a Foreclosure Sale Ud Issues of Title General Equitable Considerationsdavidchey4617100% (5)

- Science in The Clouds: History, Challenges, and OpportunitiesDocument59 pagesScience in The Clouds: History, Challenges, and OpportunitiesQamar NangrajNo ratings yet

- Research Paper Computer Architecture PDFDocument8 pagesResearch Paper Computer Architecture PDFcammtpw6100% (1)

- Term Paper On Embedded SystemsDocument7 pagesTerm Paper On Embedded Systemsaflsbbesq100% (1)

- Unit 1Document22 pagesUnit 1HariniNo ratings yet

- Introduction To Multisim Schematic Capture and Spice SimulationDocument96 pagesIntroduction To Multisim Schematic Capture and Spice SimulationAbhishek yadavNo ratings yet

- Chapter # 1 COALDocument24 pagesChapter # 1 COALShahzael MughalNo ratings yet

- Understanding The Impact of Multi-Core Architecture in Cluster Computing: A Case Study With Intel Dual-Core SystemDocument8 pagesUnderstanding The Impact of Multi-Core Architecture in Cluster Computing: A Case Study With Intel Dual-Core SystemhfarrukhnNo ratings yet

- Embedded System Design: Synopsys Inc., 700 East Middlefield Road, Mountain View, CA 94043-4033. USADocument46 pagesEmbedded System Design: Synopsys Inc., 700 East Middlefield Road, Mountain View, CA 94043-4033. USASaulo FigliuoloNo ratings yet

- WRL TN 11Document20 pagesWRL TN 11kgrhoadsNo ratings yet

- ACA NotesDocument156 pagesACA NotesSharath MonappaNo ratings yet

- Reconfigurable Computing: Architectures and Design MethodsDocument15 pagesReconfigurable Computing: Architectures and Design MethodsLuis Charrua FigueiredoNo ratings yet

- Mainframe Architecture Product Overview 1218153498319609 9Document69 pagesMainframe Architecture Product Overview 1218153498319609 9adrianpurbamanahanNo ratings yet

- Computer Organization and Architecture 10th Edition Stallings Test BankDocument9 pagesComputer Organization and Architecture 10th Edition Stallings Test BankCarrieSchmidtabsde100% (11)

- System On Chip Design and ModellingDocument131 pagesSystem On Chip Design and ModellingGurram KishoreNo ratings yet

- EC8791 Important QuestionsDocument27 pagesEC8791 Important QuestionsSurendar PNo ratings yet

- Linux Programming and Data Mining Lab ManualDocument97 pagesLinux Programming and Data Mining Lab ManualKomali RavindraNo ratings yet

- CS6303 Computer Architecture ACT Notes b6608Document76 pagesCS6303 Computer Architecture ACT Notes b6608mightymkNo ratings yet

- RTL Compiler PDFDocument49 pagesRTL Compiler PDFStudent100% (1)

- Chapter 6 - Introduction To An Embedded System and ITs Design - Microcontrollers & Embedded SystemsDocument16 pagesChapter 6 - Introduction To An Embedded System and ITs Design - Microcontrollers & Embedded SystemsAmish VermaNo ratings yet

- Vlsi Term Paper TopicsDocument7 pagesVlsi Term Paper Topicsafmzxppzpvoluf100% (1)

- Cs 6303 Unit 1Document90 pagesCs 6303 Unit 1Raghu Raman DuraiswamyNo ratings yet

- ACE TutorialDocument306 pagesACE TutorialSusnata BiswasNo ratings yet

- STL For Large Data ManagementDocument51 pagesSTL For Large Data Managementmanoj-kumar-jainNo ratings yet

- BCS-011 Computer Basics and PC Software Solved Assignment 2017Document17 pagesBCS-011 Computer Basics and PC Software Solved Assignment 2017Sumit RanjanNo ratings yet

- CS6303 Computer Architecture ACT NotesDocument76 pagesCS6303 Computer Architecture ACT NotesSuryaNo ratings yet

- NO. 1 System-On-Chip Research Leads To Hardware/software Co-Design DegreeDocument14 pagesNO. 1 System-On-Chip Research Leads To Hardware/software Co-Design DegreeSamir TabibNo ratings yet

- lv02 - 25 NuklirDocument7 pageslv02 - 25 Nuklir302345No ratings yet

- Research Paper On Embedded Systems PDFDocument5 pagesResearch Paper On Embedded Systems PDFjrcrefvhf100% (1)

- Practice Questions For 15.561 Final Examination Spring 2005Document13 pagesPractice Questions For 15.561 Final Examination Spring 2005Jona Marie ReborosoNo ratings yet

- Practice Questions For 15.561 Final Examination Spring 2005Document13 pagesPractice Questions For 15.561 Final Examination Spring 2005pradhan.neeladriNo ratings yet

- Practice Questions For 15.561 Final Examination Spring 2005Document13 pagesPractice Questions For 15.561 Final Examination Spring 2005Jona Marie ReborosoNo ratings yet

- Cse Viii Advanced Computer Architectures (06cs81) NotesDocument156 pagesCse Viii Advanced Computer Architectures (06cs81) NotesJupe JonesNo ratings yet

- CFlab Assignment and Question BankDocument26 pagesCFlab Assignment and Question Bankjek vinNo ratings yet

- CF (Lab Assignment and Question Bank)Document14 pagesCF (Lab Assignment and Question Bank)jek vinNo ratings yet

- Computer Organization and Architecture 10th Edition by Stallings ISBN Test BankDocument9 pagesComputer Organization and Architecture 10th Edition by Stallings ISBN Test Bankstephanie100% (27)

- The Performance and Energy Consumption of Three Embedded Real-Time Operating SystemsDocument8 pagesThe Performance and Energy Consumption of Three Embedded Real-Time Operating SystemssnathickNo ratings yet

- Term Paper About Computer ArchitectureDocument6 pagesTerm Paper About Computer Architectureaflsmceoc100% (1)

- Asv Platform Based2Document13 pagesAsv Platform Based2ultimatekp144No ratings yet

- Paper 63Document12 pagesPaper 632654720877No ratings yet

- Xu 2005 Step Compliant NC Research The SearDocument42 pagesXu 2005 Step Compliant NC Research The Sear林北煎包侠No ratings yet

- Computer Hardware Research Paper TopicsDocument7 pagesComputer Hardware Research Paper Topicscaq5s6ex100% (1)

- Gems: A New Model of Parallelism in PC Workstations For Multimedia ApplicationsDocument14 pagesGems: A New Model of Parallelism in PC Workstations For Multimedia ApplicationsShyamSundarNo ratings yet

- The Landscape of Parallel Computing Research: A View From BerkeleyDocument56 pagesThe Landscape of Parallel Computing Research: A View From BerkeleyDima LitvinovNo ratings yet

- ASEE2011 Win DSK8Document9 pagesASEE2011 Win DSK8Rajavel RNo ratings yet

- Performance of A ComputerDocument83 pagesPerformance of A ComputerPrakherGuptaNo ratings yet

- Coa New1 PDFDocument24 pagesCoa New1 PDFmanalabNo ratings yet

- Operating Systems Lab ManualDocument56 pagesOperating Systems Lab ManualAnonymous AVjZFiYcltNo ratings yet

- Term Paper On VlsiDocument5 pagesTerm Paper On Vlsiaflsvagfb100% (1)

- Ec6009 Advanced Computer Architecture Unit I Fundamentals of Computer Design 9Document15 pagesEc6009 Advanced Computer Architecture Unit I Fundamentals of Computer Design 9Anitha DenisNo ratings yet

- The Nesc Language: A Holistic Approach To Networked Embedded SystemsDocument11 pagesThe Nesc Language: A Holistic Approach To Networked Embedded SystemsMarco Franco AparicioNo ratings yet

- System Design: Traditional Concepts and New ParadigmsDocument12 pagesSystem Design: Traditional Concepts and New ParadigmsArun MohanarajNo ratings yet

- Ilot Te Vi Ia Week 13Document42 pagesIlot Te Vi Ia Week 13Shreyas MuraliNo ratings yet

- SoC Design - A ReviewDocument131 pagesSoC Design - A ReviewSambhav VermanNo ratings yet

- Pipelined Processor Farms: Structured Design for Embedded Parallel SystemsFrom EverandPipelined Processor Farms: Structured Design for Embedded Parallel SystemsNo ratings yet

- Energy Efficient High Performance Processors: Recent Approaches for Designing Green High Performance ComputingFrom EverandEnergy Efficient High Performance Processors: Recent Approaches for Designing Green High Performance ComputingNo ratings yet

- Fundamentals of Modern Computer Architecture: From Logic Gates to Parallel ProcessingFrom EverandFundamentals of Modern Computer Architecture: From Logic Gates to Parallel ProcessingNo ratings yet

- Embedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingFrom EverandEmbedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingNo ratings yet

- How To Install Windows 7Document2 pagesHow To Install Windows 7Sudhakar SpartanNo ratings yet

- A Novel Charge Recycling Design Scheme Based On Adiabatic Charge PumpDocument13 pagesA Novel Charge Recycling Design Scheme Based On Adiabatic Charge PumpSudhakar SpartanNo ratings yet

- VP-Administrative VP-Conferences VP-Publications VP-Technical ActivitiesDocument1 pageVP-Administrative VP-Conferences VP-Publications VP-Technical ActivitiesSudhakar SpartanNo ratings yet

- Microarchitecture Configurations and Floorplanning Co-OptimizationDocument12 pagesMicroarchitecture Configurations and Floorplanning Co-OptimizationSudhakar SpartanNo ratings yet

- Internal Combustion Engine: Induction TuningDocument39 pagesInternal Combustion Engine: Induction TuningSudhakar SpartanNo ratings yet

- February 2007 Number 2 Itcob4 (ISSN 1063-8210) : Regular PapersDocument1 pageFebruary 2007 Number 2 Itcob4 (ISSN 1063-8210) : Regular PapersSudhakar SpartanNo ratings yet

- VP-Administrative VP-Conferences VP-Publications VP-Technical ActivitiesDocument1 pageVP-Administrative VP-Conferences VP-Publications VP-Technical ActivitiesSudhakar SpartanNo ratings yet

- AUGUST 2007 Number 8 Itcob4 (ISSN 1063-8210) : Special Section PapersDocument1 pageAUGUST 2007 Number 8 Itcob4 (ISSN 1063-8210) : Special Section PapersSudhakar SpartanNo ratings yet

- Double Error Correcting Codes With Improved Code Rates: Martin Rak Us - Peter Farka SDocument6 pagesDouble Error Correcting Codes With Improved Code Rates: Martin Rak Us - Peter Farka SSudhakar SpartanNo ratings yet

- Icao Flight Plan FilingDocument2 pagesIcao Flight Plan FilingAnwar MuhammadNo ratings yet

- Module 2 NotesDocument10 pagesModule 2 NotesSanthosh Y MNo ratings yet

- Welding Procedure Specification: Company Dodsal Pte Ltd. Approved by KBRT Signature Name DateDocument1 pageWelding Procedure Specification: Company Dodsal Pte Ltd. Approved by KBRT Signature Name DateS GoudaNo ratings yet

- 2017 Winter Model Answer PaperDocument21 pages2017 Winter Model Answer PaperjohnNo ratings yet

- ASTM C627 Robinson TestDocument4 pagesASTM C627 Robinson TestSiu Hei LauNo ratings yet

- CC 110 Syllabus in Financial Management For Agri-Based Enterprises (F)Document11 pagesCC 110 Syllabus in Financial Management For Agri-Based Enterprises (F)Cesar Della33% (3)

- Engine Electrical SystemDocument57 pagesEngine Electrical SystemZatovonirina RazafindrainibeNo ratings yet

- DNS in Lync Server 2010Document13 pagesDNS in Lync Server 2010kamakom78No ratings yet

- Mtm800 Enh Tetra Mobile Terminal 806-870 MHZ (Mt912M) : Part Number: 6866539D32-ADocument225 pagesMtm800 Enh Tetra Mobile Terminal 806-870 MHZ (Mt912M) : Part Number: 6866539D32-AThanh Kieu Tien100% (1)

- Design of Critical Two-Way SlabDocument8 pagesDesign of Critical Two-Way SlabBevelyn Manalo100% (1)

- College of Engineering KIET, Karachi: I. ObjectivesDocument2 pagesCollege of Engineering KIET, Karachi: I. ObjectivesAbdul Muqeet Ahmed KhanNo ratings yet

- Dramasystem Reference Document / Robin D. Laws / P. 1Document27 pagesDramasystem Reference Document / Robin D. Laws / P. 1JamieNo ratings yet

- MDP43887 Mileage Warranty Flyer Quick GuideDocument2 pagesMDP43887 Mileage Warranty Flyer Quick GuideScenic777No ratings yet

- HP - HSTNS PL11 - PS 2122 1CDocument11 pagesHP - HSTNS PL11 - PS 2122 1CStephen SoosaiNo ratings yet

- Essar Steel-Defaulting On Debt RepaymentDocument9 pagesEssar Steel-Defaulting On Debt RepaymentSudani Ankit100% (1)

- DynaQuip Comoso de Manual LowresDocument12 pagesDynaQuip Comoso de Manual Lowresluis angelNo ratings yet

- GenC Hiring - Student BrochureDocument5 pagesGenC Hiring - Student BrochureSweety QuotesNo ratings yet

- IU Video IndexDocument24 pagesIU Video IndexRhian VelasquezNo ratings yet

- Local TaxationDocument29 pagesLocal Taxationdlo dphroNo ratings yet

- Non-Dimensional Rates - Aircraft Flight Mechanics by Harry Smith, PHDDocument1 pageNon-Dimensional Rates - Aircraft Flight Mechanics by Harry Smith, PHDhung dangNo ratings yet

- FP75E eDocument4 pagesFP75E estar990No ratings yet

- Building Technology 4 ModuleDocument35 pagesBuilding Technology 4 ModuleCARLA PASCUALNo ratings yet

- LM Comandi Marzo 2022Document11 pagesLM Comandi Marzo 2022grazianonetNo ratings yet

- Zwcad Cost ComparisonDocument1 pageZwcad Cost ComparisonVishvam Vishu 26No ratings yet

- C. Health Problems Common in ToddlerDocument72 pagesC. Health Problems Common in ToddlerRika MaeNo ratings yet

- Gmail - Your Monday Ride With OlaDocument2 pagesGmail - Your Monday Ride With OlaViswa BhuvanNo ratings yet