Professional Documents

Culture Documents

Junctionless CMOS Transistors With Independent Double Gates

Junctionless CMOS Transistors With Independent Double Gates

Uploaded by

Biswajit BeheraCopyright:

Available Formats

You might also like

- Ref615+technical+presentation 756407 EneDocument84 pagesRef615+technical+presentation 756407 EneicovinyNo ratings yet

- Sansung CL21A551MLDocument9 pagesSansung CL21A551MLAdriano SantosNo ratings yet

- Questionaires No. 04Document15 pagesQuestionaires No. 04Er Raushan Kumar YadavNo ratings yet

- Approved Project 25 StandardsDocument5 pagesApproved Project 25 StandardsepidavriosNo ratings yet

- Performance Improvement of FinFET Using Nitride SpacerDocument3 pagesPerformance Improvement of FinFET Using Nitride SpacerseventhsensegroupNo ratings yet

- Finfet With Isolated N+ and P+ Gate Regions Strapped With Metal and PolysiliconDocument2 pagesFinfet With Isolated N+ and P+ Gate Regions Strapped With Metal and PolysiliconNishana KumarNo ratings yet

- A Study On Multi Material Gate All Around SOI MOSFETDocument5 pagesA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelNo ratings yet

- 60nm P-Well MOSFETDocument4 pages60nm P-Well MOSFETKathleen Zipora RahuellahNo ratings yet

- Silicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalDocument4 pagesSilicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalMas MoNo ratings yet

- Comparative Study of Leakage Power in CNTFET Over MOSFET DeviceDocument6 pagesComparative Study of Leakage Power in CNTFET Over MOSFET DeviceAhmed HussainNo ratings yet

- Fermi FET Technology Seminar ReportDocument21 pagesFermi FET Technology Seminar Reportimcoolsha999No ratings yet

- FinfetsDocument27 pagesFinfetsAjay JoshyNo ratings yet

- Investigation of Charge Plasma Based Nanowire Field Effect Transistor For Sub 5 NMDocument9 pagesInvestigation of Charge Plasma Based Nanowire Field Effect Transistor For Sub 5 NMNeethu SNo ratings yet

- Design and Implementation of 4-Bit Alu Using Finfet TechnologyDocument12 pagesDesign and Implementation of 4-Bit Alu Using Finfet TechnologyDinesh Kumar J RNo ratings yet

- FinFET Inverter Anlaysis PDFDocument14 pagesFinFET Inverter Anlaysis PDFRakeshNo ratings yet

- Thesis Paper On TransistorsDocument7 pagesThesis Paper On TransistorsRabib HossainNo ratings yet

- Sic Mos Trench Self Align Micromachines-14-02212Document12 pagesSic Mos Trench Self Align Micromachines-14-02212terry chenNo ratings yet

- Cmos IssuesDocument180 pagesCmos IssuesArun Dev Dhar DwivediNo ratings yet

- Final RepDocument36 pagesFinal RepSubramaniam GanesanNo ratings yet

- Improved DC Performances of Gate-All-Around Si-NanDocument9 pagesImproved DC Performances of Gate-All-Around Si-Nansignallab82No ratings yet

- Fermi FET Technology Seminar ReportDocument42 pagesFermi FET Technology Seminar ReportPragati VawtulakrNo ratings yet

- Fermi FET Technology Seminar ReportDocument42 pagesFermi FET Technology Seminar Reportshefeena_anaz100% (1)

- 279 E317 PDFDocument6 pages279 E317 PDFJubin JainNo ratings yet

- Cnt-Fet A ReviewDocument5 pagesCnt-Fet A ReviewEr Ashish BahetiNo ratings yet

- Silicon Vertically Integrated Nanowire Field Effect TransistorsDocument5 pagesSilicon Vertically Integrated Nanowire Field Effect TransistorsMas MoNo ratings yet

- Future MOSFET Devices Using High-K (TiO2) DielectricDocument6 pagesFuture MOSFET Devices Using High-K (TiO2) DielectricIJRASETPublicationsNo ratings yet

- Rural News, Jul 2011Document4 pagesRural News, Jul 2011emediageNo ratings yet

- Dynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIDocument9 pagesDynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIBüşra AkyıldızNo ratings yet

- Microelectronic CircuitDocument696 pagesMicroelectronic CircuitImtiaz AhmedNo ratings yet

- Engineered Substrates: Options at The 45nm Node IncludeDocument4 pagesEngineered Substrates: Options at The 45nm Node IncludeAnkit PawarNo ratings yet

- Introduction To Vlsi TechnologyDocument32 pagesIntroduction To Vlsi TechnologysivaNo ratings yet

- Transformable Junctionless Transistor (T-JLT)Document6 pagesTransformable Junctionless Transistor (T-JLT)Rakesh KumarNo ratings yet

- Finfet: 5Nm Technology: Presented by Syed Hussain Razavi (Ece-19-38)Document14 pagesFinfet: 5Nm Technology: Presented by Syed Hussain Razavi (Ece-19-38)I m RizviNo ratings yet

- FinFet TechnologyDocument13 pagesFinFet TechnologyChintha VenuNo ratings yet

- Dančak2018 Chapter TheFinFETATutorialDocument33 pagesDančak2018 Chapter TheFinFETATutorialAhmed KamalNo ratings yet

- A Novel TFET StructureDocument23 pagesA Novel TFET StructureRohith ChowdaryNo ratings yet

- Brain Teaser AssignmentDocument6 pagesBrain Teaser AssignmentSyed Saud Ur RehmanNo ratings yet

- Design, Simulation and Characterization of 50nm P-Well MOSFET Using Sentaurus TCAD SoftwareDocument3 pagesDesign, Simulation and Characterization of 50nm P-Well MOSFET Using Sentaurus TCAD SoftwareDavid Villamarin RiveraNo ratings yet

- Electronic Devices in MTL Annual Report 1998Document20 pagesElectronic Devices in MTL Annual Report 1998tbsuirNo ratings yet

- Analytical Modeling of Double Gate MosfeDocument57 pagesAnalytical Modeling of Double Gate MosfeVijaya Kumar100% (1)

- Question & AnswerDocument10 pagesQuestion & AnswerArighna BasakNo ratings yet

- MosfetDocument20 pagesMosfetMohammad Rameez100% (2)

- A Review Paper On Cmos, Soi and Finfet TechnologyDocument18 pagesA Review Paper On Cmos, Soi and Finfet TechnologyRamakrishnaRao SoogooriNo ratings yet

- Ramesh Job PaperDocument7 pagesRamesh Job PaperAshish AwasthiNo ratings yet

- Abstract 1Document1 pageAbstract 1Manasa UpadhyayaNo ratings yet

- 5 NM) Gate-All-Around CMOS Devices: High-Performance Fully Depleted Silicon Nanowire (DiameterDocument4 pages5 NM) Gate-All-Around CMOS Devices: High-Performance Fully Depleted Silicon Nanowire (DiameterRàhuł MathiasNo ratings yet

- Gate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsDocument12 pagesGate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsNK NKNo ratings yet

- Electronics: Self-Aligned Metal Electrodes in Fully Roll-to-Roll Processed Organic TransistorsDocument10 pagesElectronics: Self-Aligned Metal Electrodes in Fully Roll-to-Roll Processed Organic TransistorsJorge Mideros ArboledaNo ratings yet

- Recent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewDocument6 pagesRecent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Mosfet: Surface-Mount D2Pak Volts Amperes Watts MatchstickDocument7 pagesMosfet: Surface-Mount D2Pak Volts Amperes Watts MatchstickJudel AnovaNo ratings yet

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamNo ratings yet

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDocument6 pagesLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupNo ratings yet

- Vlsi QBDocument34 pagesVlsi QBKaviya dharshini S -ECE-028No ratings yet

- Vertical Silicon-Nanowire Formation and Gate-All-Around MOSFETDocument4 pagesVertical Silicon-Nanowire Formation and Gate-All-Around MOSFETMas MoNo ratings yet

- Enhancement-Mode Metal Organic Chemical Vapor Deposition-Grown Zno Thin-Film Transistors On Glass Substrates Using N O Plasma TreatmentDocument7 pagesEnhancement-Mode Metal Organic Chemical Vapor Deposition-Grown Zno Thin-Film Transistors On Glass Substrates Using N O Plasma TreatmentYUTAKA09No ratings yet

- Seminar On FINFET TechnologyDocument25 pagesSeminar On FINFET TechnologyNamrata Saxena100% (1)

- Introduction To VLSI Technology: Abhijeet KumarDocument32 pagesIntroduction To VLSI Technology: Abhijeet KumarPrithireddy ThenetiNo ratings yet

- MOSFETDocument11 pagesMOSFETpaupauganda7No ratings yet

- Iiiyr Visem Vlsi DesignDocument20 pagesIiiyr Visem Vlsi DesignlokeshwarrvrjcNo ratings yet

- Fabricación Modificada de Uniones Josephson de Superconductor-Metal Normal-Superconductor para Usar en Un Sintetizador de Forma de Onda ArbitrariaDocument6 pagesFabricación Modificada de Uniones Josephson de Superconductor-Metal Normal-Superconductor para Usar en Un Sintetizador de Forma de Onda ArbitrariajamesNo ratings yet

- Chapter 4 Metal Oxide Semiconductor FET (MOSFET)Document47 pagesChapter 4 Metal Oxide Semiconductor FET (MOSFET)redhataNo ratings yet

- Automated Optical Inspection: Advancements in Computer Vision TechnologyFrom EverandAutomated Optical Inspection: Advancements in Computer Vision TechnologyNo ratings yet

- Copper Electrodeposition for Nanofabrication of Electronics DevicesFrom EverandCopper Electrodeposition for Nanofabrication of Electronics DevicesNo ratings yet

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- Planets and Education by Naval SinghDocument204 pagesPlanets and Education by Naval SinghBiswajit BeheraNo ratings yet

- New Rules Combinations in Hindu Astrology by S K MehtaDocument100 pagesNew Rules Combinations in Hindu Astrology by S K MehtaBiswajit Behera100% (1)

- Jyotish Sidantha SaralDocument96 pagesJyotish Sidantha SaralBiswajit BeheraNo ratings yet

- House BhavasDocument3 pagesHouse BhavasBiswajit BeheraNo ratings yet

- JK 1602251Document7 pagesJK 1602251Biswajit BeheraNo ratings yet

- So176 (2024)Document7 pagesSo176 (2024)Biswajit BeheraNo ratings yet

- The Prisons Act - 1894Document56 pagesThe Prisons Act - 1894Biswajit BeheraNo ratings yet

- Mahalaxmi MantraDocument7 pagesMahalaxmi MantraBiswajit Behera100% (2)

- Union of India V Gadadhar Paridawatermark 1604343Document37 pagesUnion of India V Gadadhar Paridawatermark 1604343Biswajit BeheraNo ratings yet

- Reportable: Signature Not VerifiedDocument52 pagesReportable: Signature Not VerifiedBiswajit BeheraNo ratings yet

- English Grammar Made Easy by Dreambig InstitutionDocument56 pagesEnglish Grammar Made Easy by Dreambig InstitutionBiswajit BeheraNo ratings yet

- Handling of Disciplinary Proceedings DoPT 26 03 2024Document74 pagesHandling of Disciplinary Proceedings DoPT 26 03 2024Biswajit BeheraNo ratings yet

- 150 Cloze Tests by Dream Big InstitutionDocument55 pages150 Cloze Tests by Dream Big InstitutionBiswajit BeheraNo ratings yet

- Itu-T G.664Document20 pagesItu-T G.664moneyminderNo ratings yet

- Bipolar Stepper MotorDocument3 pagesBipolar Stepper Motordirty_harry1992No ratings yet

- PDH and SDH 2Document47 pagesPDH and SDH 2Damian Blink100% (1)

- Legrand Pricelist 2018 1Document48 pagesLegrand Pricelist 2018 1SAGAR ROYNo ratings yet

- D-A Converter (Weighted Resistor Method)Document3 pagesD-A Converter (Weighted Resistor Method)neha yarrapothuNo ratings yet

- Chapter8 - VHDL - Sequential CircuitsDocument64 pagesChapter8 - VHDL - Sequential CircuitsRagheb IbrahimNo ratings yet

- Detector Apolo S 65Document2 pagesDetector Apolo S 65Demóstenes Moraes OlintoNo ratings yet

- 2n Sip Speaker Manual 1.15.2 enDocument74 pages2n Sip Speaker Manual 1.15.2 enCHOMCRPANo ratings yet

- Manual Service Dell 1600nDocument103 pagesManual Service Dell 1600nLuis Enrique Medina MartinezNo ratings yet

- Online Control of Smart Inverter For PhotovoltaicDocument17 pagesOnline Control of Smart Inverter For PhotovoltaicAaishiki GhoshNo ratings yet

- Lec 074821Document340 pagesLec 074821Mohamed Rashed100% (2)

- Catalog AMP PDFDocument18 pagesCatalog AMP PDFDragota CristinelNo ratings yet

- Research Papers On Vlsi Design PDFDocument5 pagesResearch Papers On Vlsi Design PDFruogdicnd100% (1)

- Book 002 LaMeres Logic Circuits W VHDL CoverNtocDocument15 pagesBook 002 LaMeres Logic Circuits W VHDL CoverNtocHiten AhujaNo ratings yet

- 3102213-En FW-UL6W FireWorks Workstation Installation ManualDocument62 pages3102213-En FW-UL6W FireWorks Workstation Installation ManualTrung Thành VõNo ratings yet

- Samsung Gt-p1000 Service Manual r1Document80 pagesSamsung Gt-p1000 Service Manual r1Alfred Vivien BossonNo ratings yet

- Jackery Explorer 1000 Pro User ManualDocument1 pageJackery Explorer 1000 Pro User Manualyushengcao99No ratings yet

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocument6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETNo ratings yet

- A Simple Method To Measure Unknown InductorsDocument4 pagesA Simple Method To Measure Unknown InductorsRXRSNo ratings yet

- Final Project Report Mobile Phone JammerDocument19 pagesFinal Project Report Mobile Phone JammerFarine TripoliNo ratings yet

- Ds Ctos0x01.ds3 1 6 1Document2 pagesDs Ctos0x01.ds3 1 6 1Belahcen AmineNo ratings yet

- Toughbook 55mk2 HD Model Spec Sheet (En) - DatasheetDocument2 pagesToughbook 55mk2 HD Model Spec Sheet (En) - DatasheetAnton ZhyrkovNo ratings yet

- 1MRK511289-BEN A en Product Guide Bay Control REC650 1.3 IECDocument66 pages1MRK511289-BEN A en Product Guide Bay Control REC650 1.3 IECInsan AzizNo ratings yet

- Allgon 7143.26.34.00Document1 pageAllgon 7143.26.34.00РоманКочневNo ratings yet

- A200911 1003Document6 pagesA200911 1003polururamNo ratings yet

- Mini ServoDocument2 pagesMini ServoShukri FaezNo ratings yet

Junctionless CMOS Transistors With Independent Double Gates

Junctionless CMOS Transistors With Independent Double Gates

Uploaded by

Biswajit BeheraOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Junctionless CMOS Transistors With Independent Double Gates

Junctionless CMOS Transistors With Independent Double Gates

Uploaded by

Biswajit BeheraCopyright:

Available Formats

International Journal of Information and Electronics Engineering, Vol. 3, No.

1, January 2013

Junctionless CMOS Transistors with Independent Double Gates

A. Kamath, Z. X. Chen, N. Shen, X. Li, N. Singh, G. Q. Lo, and D.-L. Kwong

characteristics, which makes it suitable for ULSI integration.

AbstractScaling is getting challenging with every technology node. Implant process requirements for defining conformal junctions in 3D device are very stringent. In addition, defining gate over topography is limited by lithography. Our solution to these problems is a novel junction-less FiNFET like transistor. Unlike conventional FiNFET the gate definition in this device is lithography independent. The fabricated NMOS and PMOS shows good transistor characteristics: ION =52.3 uA/um, ION/IOFF ratio = 107, SS = 92mV/dec for NMOS and ION =15.4 uA/um, ION/IOFF ratio = 105, SS = 90mV/dec for PMOS. We also show inverter VTC characteristics fabricated using this NMOS and PMOS. Index TermsCMOS, junctionless, independent gates

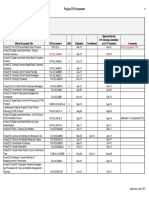

II. DEVICE FABRICATION We started the fabrication using standard 8 p-type boron doped (1E15 cm-3) SOI wafers with 1140A top silicon on 1450A BOX. Wafers were first implanted with phosphorus for N channel devices and boron for P channel devices through a resist mask (to isolate other areas) and annealed to yield uniform doping concentrations of 5E17cm-3 in both regions, a number obtained through TCAD simulations. Silicon nitride was deposited using LPCVD process on thin 30A pad oxide, which was thermally grown. Fins were patterned by DUV lithography on silicon nitride which later acted as a hard mask for etch. The nitride hard mask and the underlying silicon were both dry-etched. Gate oxide of thickness 45 was grown in dry oxygen, which was followed by deposition of amorphous silicon as gate material. Gate silicon was then polished to isolate the two gates from top. It was followed by BF2 implantation for N channel device and Phosphorus for P channel devices into the gate and then activation. Hence the channel and the gate are of opposite doping. During the gate implant, channel was protected by SiN hard mask. It was followed by active area etch. Then, 4000A pre-metal dielectric was deposited followed by contact hole etching and standard metallization processes. TEM of the final device across the FIN showing channel dimensions and two independent gates is shown in Figure

I. INTRODUCTION Short channel effects in planar CMOS transistors are a major hurdle for scaling. The main reason for Short channel effects in scaled transistors is poor gate control. To counter this, the current focus is to have Channel in the third dimension in the form of vertical Fin or Nano wires, controlled by gate around the channel. Hence FinFET [1], tri-gate MOSFET [2], and gate-all-around (GAA) Nano wire MOSFET [3], [4] have been researched extensively as solutions. Though promising from a scalability perspective, all these devices might suffer from fabrication or reliability related issues. For example, the FinFET requires gate to be patterned across the fin. Three-dimensional devices also require doping to be conformal, increasing the complexity of junction formation, which, in any case, becomes more challenging with every new technology node [6]. Junction-less devices have started to gain research focus to tackle junction related issues [7]-[9]. In this work, we experimentally demonstrate a junction-less independent gate transistor. The process flow designed helps to keep the cost low owing to lesser process steps and also mitigates several problems associated with other devices with similar architecture. This device has a channel in the form of a vertical Fin; the current is modulated by two independent gates formed on the side walls. Unlike conventional transistors, this device is free from doped-junctions, which alleviates the need for precise conformal doping required for other junction based 3D devices. In our first demonstration of N and P channel transistors presented here, we find the device exhibits good transistor

Manuscript received June 6, 2012; revised September 5, 2012. The authors are with Institute of Microelectronics, A*STAR (Agency for Science, Technology and Research), CO 117685 Singapore (e-mail: kamathar@ ime.a-star.edu.sg).

Fig. 1. TEM of the device taken across the FIN.

III. ELECTRICAL RESULTS We characterized the devices with independent gates by applying different fixed potentials on one gate and varying the other and with gates shorted together to see the impact of second gate. Shown in Fig. 2 are the Id-Vg characteristics of NMOS and PMOS device with slit doping of 5E17cm-3,

13

DOI: 10.7763/IJIEE.2013.V3.254

International Journal of Information and Electronics Engineering, Vol. 3, No. 1, January 2013

channel (FIN) width of 40nm (Using average of top and bottom width of the FIN) with two gates tied. NMOS device shows good electrical characteristics with a ION of 52 uA/um with SS = 92mV/dec and has a threshold voltage of 0.45V. PMOS device has relatively high threshold value of 1V and a relatively low ION of 15.4 uA/um with a SS of 90mV/dec. The reason higher threshold voltage in PMOS is because of Boron out diffusion (from channel) during sacrificial oxidation done to make the FIN narrower, (Process flow followed is channel doping first followed by FIN etch and Sacrificial oxidation to make the FIN narrow) this out diffusion of boron causes relative lower doping in P channel resulting in increased depletion region in the channel from the N type gate around the channel. The relative lower doping in the P channel is also the cause for Low ION as in a junctionless device the ON current is directly proportional to the dopant density. An ON current is normalized to FIN height.

can be changed by careful layout planning.

Fig. 3. Id-Vd characteristics of NMOS and PMOS device respectively.

Fig. 4. Voltage transfer characteristics of inverter.

IV. CONCLUSION

Fig. 2. Id-Vg Characteristics of NMOS and PMOS device respectively.

Fig. 3 shows the Id-Vd characteristics of the transistors. The drain Voltage shown is absolute value. The fixed drain voltages were varied till 2V in case of PMOS because of its high threshold voltage. Fig 4 Show the Voltage transfer characteristics of Inverter. This inverter was fabricated using the NMOS and PMOS described in this work. It shows a transition voltage of around 0.4V. This is expected as the NMOS device is stronger compared to PMOS. The voltage swing is not full rail voltage due to relatively higher OFF current in PMOS transistor and High drain extension resistance. We need to further optimize this by fine tuning the implant condition for P channel implant. Extension resistance

14

In this work we present a novel Junction less CMOS transistors fabricated on SOI wafer using conventional CMOS Processes. The process flow used makes this device low cost owing to simpler and reduced number of process steps. This flow also helps to mitigate lithography restrictions plaguing other similar independent devices during gate definition. This initial work shows good NMOS characteristics high ION and ION/IOFF ratio. While PMOS characteristic exhibits high threshold voltage, it can easily be rectified by fine tuning the P channel implant. In addition to above, we also present Inverter voltage transfer characteristics. The simple process flow of this device and its junctionless nature along with good electrical characteristics will make it a good contender for future USLI.

International Journal of Information and Electronics Engineering, Vol. 3, No. 1, January 2013

REFERENCES

[1] [2] C. Y. Chang et al. A 25-nm gate-lenth FinFET transistor module for 32nm node, IEDM Tech. Dig, pp. 1-4, 2009. S. Xin, L. Qiang, V. Moroz, H. Takeuchi, G. Gebara, J. Wetzel, S. Ikeda, C. Shin, and T. J. K. Liu, Tri-Gate Bulk MOSFET Design for CMOS Scaling to the End of the Roadmap, IEEE Electron Device Lett, pp. 491-493, 2008. N. Singh, F. Y. Lim, W. W. Fang, S. C. Rustagi, L. K. Bera, A. Agarwal, C. H. Tung, K. M. Hoe, S. R. Omanpuliyur, D. Tripathi, A. O. Adeyeye, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, Ultra-Narrow Silicon Nanowire Gate-All-Around CMOS Devices: Impact of Diameter, Channel-Orientation and Low Temperature Device Performance, IEDM Tech. Dig, pp. 1-4, 2006. B. Yang, K. D. Buddharaju, S. H. G. Teo, N. Singh, G. Q. Lo, and D. L Kwong, Vertical silicon-nanowire formation and gate-all-around MOSFET, IEEE Electron Device Lett, no 29, 2008.

[5]

[6] [7]

[3]

[8] [9]

[4]

T. Honda, M. Kawashima, Y. Sekine, K. Yamazoe, and E. Sakamotom, Hyper-NA imaging in ArF immersion lithography, In Microprocesses and Nanotechnology Conference. 2005. S. Borkar, Design perspectives on 22nm CMOS and beyond, IEDM Tech. Dig, pp. 93-94, 2009. J. P. Colinge, C. W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. Oneill, A. Blake, M. White, A.M. Kelleher, B. McCarthy, and R. Murphy, Nanowire transistors without junctions, Nature Nanotechnology, 2010. A. M. Ionescu, Electronic Devices:Nanowire transistors made easy, Nature Nanotechnology, 2010. C. W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J. P. Colinge, High-Temperature Performance of Silicon Juntionless MOSFETs, IEEE Tran. Electron Devices, 2010.

15

You might also like

- Ref615+technical+presentation 756407 EneDocument84 pagesRef615+technical+presentation 756407 EneicovinyNo ratings yet

- Sansung CL21A551MLDocument9 pagesSansung CL21A551MLAdriano SantosNo ratings yet

- Questionaires No. 04Document15 pagesQuestionaires No. 04Er Raushan Kumar YadavNo ratings yet

- Approved Project 25 StandardsDocument5 pagesApproved Project 25 StandardsepidavriosNo ratings yet

- Performance Improvement of FinFET Using Nitride SpacerDocument3 pagesPerformance Improvement of FinFET Using Nitride SpacerseventhsensegroupNo ratings yet

- Finfet With Isolated N+ and P+ Gate Regions Strapped With Metal and PolysiliconDocument2 pagesFinfet With Isolated N+ and P+ Gate Regions Strapped With Metal and PolysiliconNishana KumarNo ratings yet

- A Study On Multi Material Gate All Around SOI MOSFETDocument5 pagesA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelNo ratings yet

- 60nm P-Well MOSFETDocument4 pages60nm P-Well MOSFETKathleen Zipora RahuellahNo ratings yet

- Silicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalDocument4 pagesSilicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalMas MoNo ratings yet

- Comparative Study of Leakage Power in CNTFET Over MOSFET DeviceDocument6 pagesComparative Study of Leakage Power in CNTFET Over MOSFET DeviceAhmed HussainNo ratings yet

- Fermi FET Technology Seminar ReportDocument21 pagesFermi FET Technology Seminar Reportimcoolsha999No ratings yet

- FinfetsDocument27 pagesFinfetsAjay JoshyNo ratings yet

- Investigation of Charge Plasma Based Nanowire Field Effect Transistor For Sub 5 NMDocument9 pagesInvestigation of Charge Plasma Based Nanowire Field Effect Transistor For Sub 5 NMNeethu SNo ratings yet

- Design and Implementation of 4-Bit Alu Using Finfet TechnologyDocument12 pagesDesign and Implementation of 4-Bit Alu Using Finfet TechnologyDinesh Kumar J RNo ratings yet

- FinFET Inverter Anlaysis PDFDocument14 pagesFinFET Inverter Anlaysis PDFRakeshNo ratings yet

- Thesis Paper On TransistorsDocument7 pagesThesis Paper On TransistorsRabib HossainNo ratings yet

- Sic Mos Trench Self Align Micromachines-14-02212Document12 pagesSic Mos Trench Self Align Micromachines-14-02212terry chenNo ratings yet

- Cmos IssuesDocument180 pagesCmos IssuesArun Dev Dhar DwivediNo ratings yet

- Final RepDocument36 pagesFinal RepSubramaniam GanesanNo ratings yet

- Improved DC Performances of Gate-All-Around Si-NanDocument9 pagesImproved DC Performances of Gate-All-Around Si-Nansignallab82No ratings yet

- Fermi FET Technology Seminar ReportDocument42 pagesFermi FET Technology Seminar ReportPragati VawtulakrNo ratings yet

- Fermi FET Technology Seminar ReportDocument42 pagesFermi FET Technology Seminar Reportshefeena_anaz100% (1)

- 279 E317 PDFDocument6 pages279 E317 PDFJubin JainNo ratings yet

- Cnt-Fet A ReviewDocument5 pagesCnt-Fet A ReviewEr Ashish BahetiNo ratings yet

- Silicon Vertically Integrated Nanowire Field Effect TransistorsDocument5 pagesSilicon Vertically Integrated Nanowire Field Effect TransistorsMas MoNo ratings yet

- Future MOSFET Devices Using High-K (TiO2) DielectricDocument6 pagesFuture MOSFET Devices Using High-K (TiO2) DielectricIJRASETPublicationsNo ratings yet

- Rural News, Jul 2011Document4 pagesRural News, Jul 2011emediageNo ratings yet

- Dynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIDocument9 pagesDynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIBüşra AkyıldızNo ratings yet

- Microelectronic CircuitDocument696 pagesMicroelectronic CircuitImtiaz AhmedNo ratings yet

- Engineered Substrates: Options at The 45nm Node IncludeDocument4 pagesEngineered Substrates: Options at The 45nm Node IncludeAnkit PawarNo ratings yet

- Introduction To Vlsi TechnologyDocument32 pagesIntroduction To Vlsi TechnologysivaNo ratings yet

- Transformable Junctionless Transistor (T-JLT)Document6 pagesTransformable Junctionless Transistor (T-JLT)Rakesh KumarNo ratings yet

- Finfet: 5Nm Technology: Presented by Syed Hussain Razavi (Ece-19-38)Document14 pagesFinfet: 5Nm Technology: Presented by Syed Hussain Razavi (Ece-19-38)I m RizviNo ratings yet

- FinFet TechnologyDocument13 pagesFinFet TechnologyChintha VenuNo ratings yet

- Dančak2018 Chapter TheFinFETATutorialDocument33 pagesDančak2018 Chapter TheFinFETATutorialAhmed KamalNo ratings yet

- A Novel TFET StructureDocument23 pagesA Novel TFET StructureRohith ChowdaryNo ratings yet

- Brain Teaser AssignmentDocument6 pagesBrain Teaser AssignmentSyed Saud Ur RehmanNo ratings yet

- Design, Simulation and Characterization of 50nm P-Well MOSFET Using Sentaurus TCAD SoftwareDocument3 pagesDesign, Simulation and Characterization of 50nm P-Well MOSFET Using Sentaurus TCAD SoftwareDavid Villamarin RiveraNo ratings yet

- Electronic Devices in MTL Annual Report 1998Document20 pagesElectronic Devices in MTL Annual Report 1998tbsuirNo ratings yet

- Analytical Modeling of Double Gate MosfeDocument57 pagesAnalytical Modeling of Double Gate MosfeVijaya Kumar100% (1)

- Question & AnswerDocument10 pagesQuestion & AnswerArighna BasakNo ratings yet

- MosfetDocument20 pagesMosfetMohammad Rameez100% (2)

- A Review Paper On Cmos, Soi and Finfet TechnologyDocument18 pagesA Review Paper On Cmos, Soi and Finfet TechnologyRamakrishnaRao SoogooriNo ratings yet

- Ramesh Job PaperDocument7 pagesRamesh Job PaperAshish AwasthiNo ratings yet

- Abstract 1Document1 pageAbstract 1Manasa UpadhyayaNo ratings yet

- 5 NM) Gate-All-Around CMOS Devices: High-Performance Fully Depleted Silicon Nanowire (DiameterDocument4 pages5 NM) Gate-All-Around CMOS Devices: High-Performance Fully Depleted Silicon Nanowire (DiameterRàhuł MathiasNo ratings yet

- Gate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsDocument12 pagesGate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsNK NKNo ratings yet

- Electronics: Self-Aligned Metal Electrodes in Fully Roll-to-Roll Processed Organic TransistorsDocument10 pagesElectronics: Self-Aligned Metal Electrodes in Fully Roll-to-Roll Processed Organic TransistorsJorge Mideros ArboledaNo ratings yet

- Recent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewDocument6 pagesRecent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Mosfet: Surface-Mount D2Pak Volts Amperes Watts MatchstickDocument7 pagesMosfet: Surface-Mount D2Pak Volts Amperes Watts MatchstickJudel AnovaNo ratings yet

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamNo ratings yet

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDocument6 pagesLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupNo ratings yet

- Vlsi QBDocument34 pagesVlsi QBKaviya dharshini S -ECE-028No ratings yet

- Vertical Silicon-Nanowire Formation and Gate-All-Around MOSFETDocument4 pagesVertical Silicon-Nanowire Formation and Gate-All-Around MOSFETMas MoNo ratings yet

- Enhancement-Mode Metal Organic Chemical Vapor Deposition-Grown Zno Thin-Film Transistors On Glass Substrates Using N O Plasma TreatmentDocument7 pagesEnhancement-Mode Metal Organic Chemical Vapor Deposition-Grown Zno Thin-Film Transistors On Glass Substrates Using N O Plasma TreatmentYUTAKA09No ratings yet

- Seminar On FINFET TechnologyDocument25 pagesSeminar On FINFET TechnologyNamrata Saxena100% (1)

- Introduction To VLSI Technology: Abhijeet KumarDocument32 pagesIntroduction To VLSI Technology: Abhijeet KumarPrithireddy ThenetiNo ratings yet

- MOSFETDocument11 pagesMOSFETpaupauganda7No ratings yet

- Iiiyr Visem Vlsi DesignDocument20 pagesIiiyr Visem Vlsi DesignlokeshwarrvrjcNo ratings yet

- Fabricación Modificada de Uniones Josephson de Superconductor-Metal Normal-Superconductor para Usar en Un Sintetizador de Forma de Onda ArbitrariaDocument6 pagesFabricación Modificada de Uniones Josephson de Superconductor-Metal Normal-Superconductor para Usar en Un Sintetizador de Forma de Onda ArbitrariajamesNo ratings yet

- Chapter 4 Metal Oxide Semiconductor FET (MOSFET)Document47 pagesChapter 4 Metal Oxide Semiconductor FET (MOSFET)redhataNo ratings yet

- Automated Optical Inspection: Advancements in Computer Vision TechnologyFrom EverandAutomated Optical Inspection: Advancements in Computer Vision TechnologyNo ratings yet

- Copper Electrodeposition for Nanofabrication of Electronics DevicesFrom EverandCopper Electrodeposition for Nanofabrication of Electronics DevicesNo ratings yet

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- Planets and Education by Naval SinghDocument204 pagesPlanets and Education by Naval SinghBiswajit BeheraNo ratings yet

- New Rules Combinations in Hindu Astrology by S K MehtaDocument100 pagesNew Rules Combinations in Hindu Astrology by S K MehtaBiswajit Behera100% (1)

- Jyotish Sidantha SaralDocument96 pagesJyotish Sidantha SaralBiswajit BeheraNo ratings yet

- House BhavasDocument3 pagesHouse BhavasBiswajit BeheraNo ratings yet

- JK 1602251Document7 pagesJK 1602251Biswajit BeheraNo ratings yet

- So176 (2024)Document7 pagesSo176 (2024)Biswajit BeheraNo ratings yet

- The Prisons Act - 1894Document56 pagesThe Prisons Act - 1894Biswajit BeheraNo ratings yet

- Mahalaxmi MantraDocument7 pagesMahalaxmi MantraBiswajit Behera100% (2)

- Union of India V Gadadhar Paridawatermark 1604343Document37 pagesUnion of India V Gadadhar Paridawatermark 1604343Biswajit BeheraNo ratings yet

- Reportable: Signature Not VerifiedDocument52 pagesReportable: Signature Not VerifiedBiswajit BeheraNo ratings yet

- English Grammar Made Easy by Dreambig InstitutionDocument56 pagesEnglish Grammar Made Easy by Dreambig InstitutionBiswajit BeheraNo ratings yet

- Handling of Disciplinary Proceedings DoPT 26 03 2024Document74 pagesHandling of Disciplinary Proceedings DoPT 26 03 2024Biswajit BeheraNo ratings yet

- 150 Cloze Tests by Dream Big InstitutionDocument55 pages150 Cloze Tests by Dream Big InstitutionBiswajit BeheraNo ratings yet

- Itu-T G.664Document20 pagesItu-T G.664moneyminderNo ratings yet

- Bipolar Stepper MotorDocument3 pagesBipolar Stepper Motordirty_harry1992No ratings yet

- PDH and SDH 2Document47 pagesPDH and SDH 2Damian Blink100% (1)

- Legrand Pricelist 2018 1Document48 pagesLegrand Pricelist 2018 1SAGAR ROYNo ratings yet

- D-A Converter (Weighted Resistor Method)Document3 pagesD-A Converter (Weighted Resistor Method)neha yarrapothuNo ratings yet

- Chapter8 - VHDL - Sequential CircuitsDocument64 pagesChapter8 - VHDL - Sequential CircuitsRagheb IbrahimNo ratings yet

- Detector Apolo S 65Document2 pagesDetector Apolo S 65Demóstenes Moraes OlintoNo ratings yet

- 2n Sip Speaker Manual 1.15.2 enDocument74 pages2n Sip Speaker Manual 1.15.2 enCHOMCRPANo ratings yet

- Manual Service Dell 1600nDocument103 pagesManual Service Dell 1600nLuis Enrique Medina MartinezNo ratings yet

- Online Control of Smart Inverter For PhotovoltaicDocument17 pagesOnline Control of Smart Inverter For PhotovoltaicAaishiki GhoshNo ratings yet

- Lec 074821Document340 pagesLec 074821Mohamed Rashed100% (2)

- Catalog AMP PDFDocument18 pagesCatalog AMP PDFDragota CristinelNo ratings yet

- Research Papers On Vlsi Design PDFDocument5 pagesResearch Papers On Vlsi Design PDFruogdicnd100% (1)

- Book 002 LaMeres Logic Circuits W VHDL CoverNtocDocument15 pagesBook 002 LaMeres Logic Circuits W VHDL CoverNtocHiten AhujaNo ratings yet

- 3102213-En FW-UL6W FireWorks Workstation Installation ManualDocument62 pages3102213-En FW-UL6W FireWorks Workstation Installation ManualTrung Thành VõNo ratings yet

- Samsung Gt-p1000 Service Manual r1Document80 pagesSamsung Gt-p1000 Service Manual r1Alfred Vivien BossonNo ratings yet

- Jackery Explorer 1000 Pro User ManualDocument1 pageJackery Explorer 1000 Pro User Manualyushengcao99No ratings yet

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocument6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETNo ratings yet

- A Simple Method To Measure Unknown InductorsDocument4 pagesA Simple Method To Measure Unknown InductorsRXRSNo ratings yet

- Final Project Report Mobile Phone JammerDocument19 pagesFinal Project Report Mobile Phone JammerFarine TripoliNo ratings yet

- Ds Ctos0x01.ds3 1 6 1Document2 pagesDs Ctos0x01.ds3 1 6 1Belahcen AmineNo ratings yet

- Toughbook 55mk2 HD Model Spec Sheet (En) - DatasheetDocument2 pagesToughbook 55mk2 HD Model Spec Sheet (En) - DatasheetAnton ZhyrkovNo ratings yet

- 1MRK511289-BEN A en Product Guide Bay Control REC650 1.3 IECDocument66 pages1MRK511289-BEN A en Product Guide Bay Control REC650 1.3 IECInsan AzizNo ratings yet

- Allgon 7143.26.34.00Document1 pageAllgon 7143.26.34.00РоманКочневNo ratings yet

- A200911 1003Document6 pagesA200911 1003polururamNo ratings yet

- Mini ServoDocument2 pagesMini ServoShukri FaezNo ratings yet