Professional Documents

Culture Documents

Different Low Power Techniques: Trade-Offs Associated With The Various Power Management Techniques

Different Low Power Techniques: Trade-Offs Associated With The Various Power Management Techniques

Uploaded by

naveen silveriOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Different Low Power Techniques: Trade-Offs Associated With The Various Power Management Techniques

Different Low Power Techniques: Trade-Offs Associated With The Various Power Management Techniques

Uploaded by

naveen silveriCopyright:

Available Formats

Michael Keating et al.

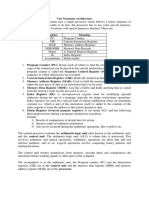

[1] lists several low power techniques to tackle the dynamic and static power consumption in modern SoC designs. Dynamic power control techniques include clock gating, multi voltage, variable frequency, and efficient circuits. Leakage power control techniques include power gating, multi Vt cells. Common methods supported by EDA tools include clock gating, gate sizing, low power placement, register clustering, low power CTS, multi Vt optimization. Some of the low power techniques in use today are listed in below table.

Different Low Power Techniques

Trade-offs associated with the various power management techniques [2]Above table summarizes

trade-

offs associated with different power management techniques. Power gating and DVFS demand large methodology change whereas multi vt and clock gating affect least. Unless large leakage optimization is not necessary it is always beneficial to go with either multi vt or clock gating techniques. Based on the design complexity and requirements combination of any low power techniques can be adopted. Multi vt optimization along with the power gating is found to be efficient in some of the complex designs. Advanced improvements in the implementation (i.e. fabrication) technology has allowed substrate biasing techniques to be used heavily as it does not pose any architectural and design verification challenges and also provides high leakage reduction.

"Latch" Vs "Flip Flop"

A flip-flop is Edge sensitive: Output only changes on rising (or falling) edge of clock. A latch is Level sensitive: Output changes whenever clock/Enable is high (or low) A common implementation of a flip-flop is a pair of latches (Master/Slave flop). Latches are sometimes called transparent latches, because they are transparent (input directly connected to output) when the clock is high. The clock to a latch is primarily called the enable. For more information have a look at the picture below.

Deprecated Hardware: Latches: Use flops, not latches 1. Latch-based designs are susceptible to timing problems 2. The transparent phase of a latch can let a signal leak through a latch causing the signal to affect the output one clock cycle too early 3. Its possible for a latch-based circuit to simulate correctly, but not work in real hardware, because the timing delays on the real hardware dont match those predicted in synthesis Flip-flops: 1. Limit yourself to D-type flip-flops 2. Some FPGA and ASIC cell libraries include only D-type flip flops. Others, such as Alteras APEX FPGAs, can be configured as D, T, JK, or SR flip-flops.

For every signal in your design, know whether it should be a flip-flop or combinational. Examine the log file e.g. dc shell.log to see if the flip-flops in your circuit match your expectations, and to check that you dont have any latches in your design. Do not assign a signal to itself (e.g. a <= a; is bad). If the signal is a flop, use an enable to cause the signal to hold its value. If the signal is combinational, then assigning a signal to itself will cause combinational loops, which are very bad.

You might also like

- STA Concepts and Interview Questions PDFDocument173 pagesSTA Concepts and Interview Questions PDFAtul100% (4)

- DGD 9 SolDocument9 pagesDGD 9 SolDolores Makaruina100% (1)

- VLSI Interview Questions With Answers - Ebook - VLSI Design Interview Questions With Answers - Ebook PDFDocument4 pagesVLSI Interview Questions With Answers - Ebook - VLSI Design Interview Questions With Answers - Ebook PDFnaveen silveri50% (4)

- VLSI Design Interview QuestionsDocument79 pagesVLSI Design Interview QuestionsashhbamNo ratings yet

- Power Gating - Power Management Technique: VLSI Basics and Interview QuestionsDocument12 pagesPower Gating - Power Management Technique: VLSI Basics and Interview QuestionsRohith RajNo ratings yet

- ASIC-System On Chip-VLSI Design - Clock GatingDocument4 pagesASIC-System On Chip-VLSI Design - Clock Gatinguni_saraNo ratings yet

- Clock GatingDocument4 pagesClock Gatingvaibhav.1991No ratings yet

- TP LeakagePowerOptimizationFlowDocument11 pagesTP LeakagePowerOptimizationFlowSathyanarayana RaoNo ratings yet

- Clock Gating Circuits PDFDocument4 pagesClock Gating Circuits PDFTej Pal Singh100% (1)

- Comparative Analysis of Different Clock Gating TechniquesDocument55 pagesComparative Analysis of Different Clock Gating Techniquesvsangvai26No ratings yet

- GlitchLess Dynamic Power Minimization in FPGAs Through Edge Alignment and Glitch FilteringDocument14 pagesGlitchLess Dynamic Power Minimization in FPGAs Through Edge Alignment and Glitch Filteringmossaied2No ratings yet

- Power Reduction Through RTL Clock GatingDocument10 pagesPower Reduction Through RTL Clock GatingAishwarya TekkalakotaNo ratings yet

- A Better Tool For Functional Verification of Low-Power Designs With IEEE 1801 UPFDocument13 pagesA Better Tool For Functional Verification of Low-Power Designs With IEEE 1801 UPFSamNo ratings yet

- Clock GatingDocument2 pagesClock GatingvarshakothapalliNo ratings yet

- Low Power Vlsi ThesisDocument5 pagesLow Power Vlsi Thesismariapadillaomaha100% (2)

- Magic Blue Smoke Low Power General PDFDocument6 pagesMagic Blue Smoke Low Power General PDFSumanth VarmaNo ratings yet

- Low Power Register Design With Integration Clock Gating and Power GatingDocument6 pagesLow Power Register Design With Integration Clock Gating and Power GatingInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Xilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingDocument4 pagesXilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingjackNo ratings yet

- Mnaual Lab 1Document6 pagesMnaual Lab 1hamzadaud032No ratings yet

- Xilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyDocument5 pagesXilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyjackNo ratings yet

- Startup Design and Analysis NoteDocument6 pagesStartup Design and Analysis NoteDeepa DevarajNo ratings yet

- Digital SystemsDocument45 pagesDigital SystemsSindhu ManchukondaNo ratings yet

- ASIC Interview QuestionsDocument6 pagesASIC Interview QuestionsNandeesh VeerannaNo ratings yet

- Placement Aware Clock Gate Cloning and Redistribution Methodology PDFDocument4 pagesPlacement Aware Clock Gate Cloning and Redistribution Methodology PDFHarish Kumar100% (1)

- Clock and Data Recovery PHD ThesisDocument6 pagesClock and Data Recovery PHD Thesisazyxppzcf100% (2)

- Clock Gating: K.Harshavardhan 19021D6802 M-Tech (Vlsi & Es)Document14 pagesClock Gating: K.Harshavardhan 19021D6802 M-Tech (Vlsi & Es)Bunny harshaNo ratings yet

- Gditechnology 151220144934Document80 pagesGditechnology 151220144934bharath kishore reddyNo ratings yet

- Designing A Robust Clock Tree StructureDocument9 pagesDesigning A Robust Clock Tree StructureStudent100% (1)

- Isolation Retention DefinitionDocument10 pagesIsolation Retention DefinitionSuma P RNo ratings yet

- VLSI Interview Questions - FPGA Interview QuestionsDocument8 pagesVLSI Interview Questions - FPGA Interview QuestionsBhyrapaneni LakshmanNo ratings yet

- A Review Report On Multi-Voltage Rule Check - HBRP PublicationDocument11 pagesA Review Report On Multi-Voltage Rule Check - HBRP PublicationSaisantosh RajputhNo ratings yet

- Lec 38Document31 pagesLec 38sk_sulabhNo ratings yet

- Research Paper On Programmable Logic ControllerDocument5 pagesResearch Paper On Programmable Logic Controllerefdwvgt4No ratings yet

- Ap Note 204189Document13 pagesAp Note 204189Obi InwelegbuNo ratings yet

- Xilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingDocument4 pagesXilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingjackNo ratings yet

- RTL Resistor-Transistor Logic CookbookDocument247 pagesRTL Resistor-Transistor Logic Cookbookpikymail100% (2)

- EC 303 Chapter 2Document48 pagesEC 303 Chapter 2PrevenaManiamNo ratings yet

- D Flip FlopDocument5 pagesD Flip FlopNaveen Kumar RavillaNo ratings yet

- FPGA Based Control Unit For Marx GeneratorsDocument57 pagesFPGA Based Control Unit For Marx GeneratorsAnshuman SahooNo ratings yet

- Low-Power Digital VLSI DesignDocument530 pagesLow-Power Digital VLSI DesignAllanki Sanyasi Rao50% (2)

- Dynamic Power Reduction WPDocument6 pagesDynamic Power Reduction WPRanganadh MvNo ratings yet

- Xilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyDocument4 pagesXilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyjackNo ratings yet

- Power Gating Implementation in SOCDocument23 pagesPower Gating Implementation in SOCmaxxtorr723No ratings yet

- Low Power Verification Methodology Using UPF: Freddy Bembaron Sachin KakkarDocument6 pagesLow Power Verification Methodology Using UPF: Freddy Bembaron Sachin KakkarharikrishnarockNo ratings yet

- Thesis Flyback ConverterDocument5 pagesThesis Flyback ConverterAngela Tyger100% (2)

- Vlsi FaqsDocument29 pagesVlsi Faqsanon-417212100% (4)

- SET-1: Answer To The Interview QuestionsDocument9 pagesSET-1: Answer To The Interview QuestionsÆshok IncreĐible KingNo ratings yet

- Term Paper Report MODIFIEDDocument21 pagesTerm Paper Report MODIFIEDUma SankarNo ratings yet

- Dual-Vt Design of Fpgas For Subthreshold Leakage ToleranceDocument6 pagesDual-Vt Design of Fpgas For Subthreshold Leakage Tolerancerostamedastan65No ratings yet

- Low Power Techniques For VLSI DesignDocument6 pagesLow Power Techniques For VLSI DesignjainatinNo ratings yet

- Mixed-Signal IP Design Challenges in 28 NM and BeyondDocument14 pagesMixed-Signal IP Design Challenges in 28 NM and BeyondyvarshneyNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- On-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsFrom EverandOn-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsNo ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- PLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsFrom EverandPLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsRating: 5 out of 5 stars5/5 (1)

- Low Power VLSI Chip Design: Circuit Design TechniquesDocument11 pagesLow Power VLSI Chip Design: Circuit Design Techniquesnaveen silveriNo ratings yet

- Clock BuffersDocument29 pagesClock Buffersnaveen silveri100% (2)

- Unix Vi HelpDocument2 pagesUnix Vi HelpJobin IdicullaNo ratings yet

- 1.1 Research Motivation: Optimization Techniques For Allocation of Resources in OFDMA Down Link Network SystemsDocument3 pages1.1 Research Motivation: Optimization Techniques For Allocation of Resources in OFDMA Down Link Network Systemsnaveen silveriNo ratings yet

- Orthogonal Frequency Division Multiple Access (OFDMA) Is Becoming A Widely De-PloyedDocument6 pagesOrthogonal Frequency Division Multiple Access (OFDMA) Is Becoming A Widely De-Ployednaveen silveriNo ratings yet

- Irst Drive: G - Enter 2. G: Attrib - S - H /s /D . 3Document1 pageIrst Drive: G - Enter 2. G: Attrib - S - H /s /D . 3naveen silveriNo ratings yet

- Important VLSI Commands1Document6 pagesImportant VLSI Commands1naveen silveriNo ratings yet

- Design Technologies For Low Power VLSI: To Appear in Encyclopedia of Computer Science and Technology, 1995Document32 pagesDesign Technologies For Low Power VLSI: To Appear in Encyclopedia of Computer Science and Technology, 1995naveen silveriNo ratings yet

- Manage Active Users: Welcome Operator 7.3.0 Build 2.7Document4 pagesManage Active Users: Welcome Operator 7.3.0 Build 2.7naveen silveriNo ratings yet

- ModelDocument457 pagesModelnaveen silveriNo ratings yet

- Floor PlanningDocument28 pagesFloor Planningnaveen silveriNo ratings yet

- 8D02EDocument20 pages8D02EtesdaNo ratings yet

- Clock Generation and DistributionDocument57 pagesClock Generation and Distributionmanohar487100% (1)

- Von Neumann ArchitectureDocument8 pagesVon Neumann ArchitectureDinesh KumarNo ratings yet

- HS Systems Table of ContentsDocument8 pagesHS Systems Table of ContentsGrimmjow JaegerjaquezNo ratings yet

- Dual, 8-Bit, Voltage-Output Serial DAC in 8-Pin SO PackageDocument12 pagesDual, 8-Bit, Voltage-Output Serial DAC in 8-Pin SO PackagemvpgmNo ratings yet

- Read & Write CycleDocument22 pagesRead & Write CycleAditeeNo ratings yet

- Dynamic JitterDocument10 pagesDynamic JitterNishanth DoddamaneNo ratings yet

- FM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- Actividad Previa Practica 2 - MicroprocesadorDocument4 pagesActividad Previa Practica 2 - MicroprocesadorNorabel PerezcondeNo ratings yet

- 4740 Lecture07 PowerDocument14 pages4740 Lecture07 Powerkrrish06230No ratings yet

- EC8095 QB VLSI DesignDocument10 pagesEC8095 QB VLSI Designsanthosh sekarNo ratings yet

- Timing Diagram of 8085Document20 pagesTiming Diagram of 8085FRAG么 OFFICIALNo ratings yet

- 5 Timer (Part 1)Document29 pages5 Timer (Part 1)lsuwdaa100% (1)

- MODULE-5:Analysis of Sequential Circuit:: Asynchronous Counters Synchronous CountersDocument22 pagesMODULE-5:Analysis of Sequential Circuit:: Asynchronous Counters Synchronous CountersChaitanya J S ReddyNo ratings yet

- BTS3900 Product Description - (V300R008 02)Document85 pagesBTS3900 Product Description - (V300R008 02)phanlinh1987No ratings yet

- Sony MDX-C7900R Service ManualDocument62 pagesSony MDX-C7900R Service Manualremus161No ratings yet

- Image Convolution On FPGAs The Implementation of A multi-FPGA FIFO StructureDocument8 pagesImage Convolution On FPGAs The Implementation of A multi-FPGA FIFO StructureNgô Minh KhánhNo ratings yet

- Design of Digital Clock Calendar Using FPGA: April 2014Document7 pagesDesign of Digital Clock Calendar Using FPGA: April 2014Archit GharatNo ratings yet

- PB7200 Series Service ManualDocument91 pagesPB7200 Series Service ManualGsouzaNo ratings yet

- GPT - General Purpose Timer Reference ManualDocument90 pagesGPT - General Purpose Timer Reference ManualIkram El JamaiNo ratings yet

- Timing DiagramDocument15 pagesTiming DiagramKUMARASWAMY A MECNo ratings yet

- General Organisation of A Micro ProcessorDocument8 pagesGeneral Organisation of A Micro ProcessornelsrodrigNo ratings yet

- Digital-To-Analog Converter ICs SB Vol11 Issue5Document12 pagesDigital-To-Analog Converter ICs SB Vol11 Issue5Hooman KaabiNo ratings yet

- 24aa256uid 256k I2c Serial Eeprom With Eui48 Eui64 20005215dDocument28 pages24aa256uid 256k I2c Serial Eeprom With Eui48 Eui64 20005215dAbhishek BhattacharjeeNo ratings yet

- Computer Organisation and Architecture - COA-Asynchronous Data TransferDocument6 pagesComputer Organisation and Architecture - COA-Asynchronous Data TransferSUPRIYA KUMBHAKARANNo ratings yet

- Digital Clock Frequency Multiplier Using Floating Point ArithmeticDocument4 pagesDigital Clock Frequency Multiplier Using Floating Point ArithmeticIJERDNo ratings yet

- Curtain Control Systems Development On Mesh Wireless Network of The Smart HomeDocument12 pagesCurtain Control Systems Development On Mesh Wireless Network of The Smart HomeNguyen QuocNo ratings yet

- Chapter 2Document63 pagesChapter 2Mohammad ja'farNo ratings yet

- Z8581 Clock Generator and Controller PDFDocument8 pagesZ8581 Clock Generator and Controller PDFkhawar mukhtarNo ratings yet