Professional Documents

Culture Documents

Development and Distribution of TSMC 0.25 Cells

Development and Distribution of TSMC 0.25 Cells

Uploaded by

Duc DucCopyright:

Available Formats

You might also like

- Mips Fpga LabDocument10 pagesMips Fpga LabBiloKhanNo ratings yet

- Seminar Report On VLSIDocument21 pagesSeminar Report On VLSIGaurav Jaiswal75% (4)

- P200 New VersionDocument103 pagesP200 New VersionDELSP - Dynamic Elevator Services Pakistan81% (42)

- h11909 Emc Isilon Best Practices Eda WPDocument34 pagesh11909 Emc Isilon Best Practices Eda WPgabbu_No ratings yet

- Lab Module 1 - MySQL LabDocument10 pagesLab Module 1 - MySQL LabnutanayaNo ratings yet

- Phy Ie Report 17-20Document6 pagesPhy Ie Report 17-20RITIK JAINNo ratings yet

- Development of TSMC 0.25 M Standard Cell LibraryDocument3 pagesDevelopment of TSMC 0.25 M Standard Cell Libraryhex0x1No ratings yet

- Vlsi Design Thesis TopicsDocument8 pagesVlsi Design Thesis Topicsbsqfc4d5100% (2)

- AbstractDocument10 pagesAbstractbarsharaniraul123No ratings yet

- Thesis On Vlsi DesignDocument7 pagesThesis On Vlsi Designbrendatorresalbuquerque100% (2)

- Synopsys Open Educational Design KitDocument5 pagesSynopsys Open Educational Design KitAbhishek AvNo ratings yet

- VHDL Modeling and Design FlowDocument455 pagesVHDL Modeling and Design FlowPrabakaran RajendranNo ratings yet

- Very Large Scale IntegrationDocument3 pagesVery Large Scale IntegrationGowtham SpNo ratings yet

- Built-In Fault-Tolerant Computing Paradigm For Resilient Large-Scale Chip DesignDocument318 pagesBuilt-In Fault-Tolerant Computing Paradigm For Resilient Large-Scale Chip DesignostomaconsultingNo ratings yet

- Research Paper VlsiDocument6 pagesResearch Paper Vlsiafedsxmai100% (1)

- Basic VLSI Design ConceptDocument18 pagesBasic VLSI Design ConceptMoon Sadia DiptheeNo ratings yet

- PHD Thesis On Vlsi DesignDocument5 pagesPHD Thesis On Vlsi DesignBuyEssaysTulsa100% (2)

- Very Large Scale Integration (Vlsi)Document49 pagesVery Large Scale Integration (Vlsi)sayyioNo ratings yet

- Very-Large-Scale Integration - Wikipedia, The Free EncyclopediaDocument4 pagesVery-Large-Scale Integration - Wikipedia, The Free EncyclopediaSuneelkrishna RallabhandiNo ratings yet

- EECE 452 - Selected Topics in VLSIDocument3 pagesEECE 452 - Selected Topics in VLSIMarwan EidNo ratings yet

- Work?: International Test Conference PaperDocument2 pagesWork?: International Test Conference PaperTom MathewNo ratings yet

- Vlsi Research Paper TopicsDocument7 pagesVlsi Research Paper Topicsaflbtrnpf100% (1)

- The Very Large Scale IntegrationDocument7 pagesThe Very Large Scale IntegrationPallavi JayramNo ratings yet

- An Overview of VLSI: 1.2 What Is VLSI? 1.3 Complexity 1.4 Design 1.5 Basic Concepts 1.6 Summary 1.7 Problems ReferencesDocument14 pagesAn Overview of VLSI: 1.2 What Is VLSI? 1.3 Complexity 1.4 Design 1.5 Basic Concepts 1.6 Summary 1.7 Problems ReferencesVikas SurveNo ratings yet

- Research Paper Topics VlsiDocument7 pagesResearch Paper Topics Vlsihyzypif0gif3100% (1)

- Designing For Cisco Internetwork Solutions Lab Guide (CCDA DESGN 640-864) v2.1Document95 pagesDesigning For Cisco Internetwork Solutions Lab Guide (CCDA DESGN 640-864) v2.1axidnet100% (2)

- Introductory Chapter ASIC Technologies and DesignDocument11 pagesIntroductory Chapter ASIC Technologies and DesignDeev DeevNo ratings yet

- Multi-Project Wafer Serv..., The Free EncyclopediaDocument1 pageMulti-Project Wafer Serv..., The Free EncyclopediaSuneelkrishna RallabhandiNo ratings yet

- Research Paper Topics in VlsiDocument4 pagesResearch Paper Topics in Vlsij1zijefifin3100% (1)

- Vast - ITDocument15 pagesVast - ITpradeep9007879No ratings yet

- 1.1 Introduction of VlsiDocument35 pages1.1 Introduction of VlsiSneha GurrapuNo ratings yet

- Cad PDFDocument366 pagesCad PDFNitish KumarNo ratings yet

- About VlsiDocument14 pagesAbout VlsiAnonymous 1aqlkZNo ratings yet

- Adding Analog and Mixed Signal Concerns To A Digital VLSI CourseDocument8 pagesAdding Analog and Mixed Signal Concerns To A Digital VLSI CourseLavanya SelvarajNo ratings yet

- Vlsi Application: Applications of VLSI Circuits To Medical ImagingDocument4 pagesVlsi Application: Applications of VLSI Circuits To Medical ImagingshadhanaaNo ratings yet

- VLSI System Design Using Verilog - Step by Step Designing Procedure For CADENCE Incisive Enterprise SimulatorDocument150 pagesVLSI System Design Using Verilog - Step by Step Designing Procedure For CADENCE Incisive Enterprise Simulatorkolaverididhanush1No ratings yet

- IEEEVCAL Vol6 Issue3 Aug2020Document49 pagesIEEEVCAL Vol6 Issue3 Aug2020ET171046 JobaerNo ratings yet

- Course Code: Course Title: Pre-Requisite: Course ContentDocument2 pagesCourse Code: Course Title: Pre-Requisite: Course ContentFaisal HossainNo ratings yet

- Digital VLSI Chip Design With Cadence and Synopsys CAD ToolsDocument366 pagesDigital VLSI Chip Design With Cadence and Synopsys CAD ToolsMacy Yuan80% (5)

- Fire Alarm Controller ReportDocument18 pagesFire Alarm Controller ReportAnil KumarNo ratings yet

- Introduction To VLSI SystemDocument16 pagesIntroduction To VLSI SystemPrabakaran RajendranNo ratings yet

- Soas For Scientific Applications: Experiences and ChallengesDocument20 pagesSoas For Scientific Applications: Experiences and Challengesxico107No ratings yet

- Elena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Auth.), Elena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Eds.)-Wireless Sensor Networks_ Deployments AnDocument307 pagesElena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Auth.), Elena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Eds.)-Wireless Sensor Networks_ Deployments AnrmieringeominasNo ratings yet

- IITD BrochureDocument10 pagesIITD Brochurejitu_4No ratings yet

- CSCE 612: VLSI System Design: Instructor: Jason D. BakosDocument14 pagesCSCE 612: VLSI System Design: Instructor: Jason D. BakosVinod RajNo ratings yet

- Standard Cell Library Design and Characterization Using 45nm TechnologyDocument5 pagesStandard Cell Library Design and Characterization Using 45nm TechnologyTitan FredNo ratings yet

- Cisco IT ACI DesignDocument28 pagesCisco IT ACI DesignCalota Mugurel AdrianNo ratings yet

- New Microsoft Word DocumentDocument3 pagesNew Microsoft Word DocumentSannena GovindaNo ratings yet

- VLSIDocument14 pagesVLSIPravallika RepanaNo ratings yet

- Ieee Research Paper On VlsiDocument6 pagesIeee Research Paper On Vlsiebvjkbaod100% (1)

- Term Paper On VlsiDocument5 pagesTerm Paper On Vlsiaflsvagfb100% (1)

- Chapter 1 IntroductionDocument21 pagesChapter 1 IntroductionIshrak AhmedNo ratings yet

- Design and Implementation of VLSI SystemsDocument41 pagesDesign and Implementation of VLSI SystemsCuong HuynhNo ratings yet

- Program Name Semester Course Code Course Name Lecture / Tutorial (Per Week) Lect. No. Course Coordinator NameDocument33 pagesProgram Name Semester Course Code Course Name Lecture / Tutorial (Per Week) Lect. No. Course Coordinator Nameishan goyalNo ratings yet

- Science China Information Sciences: Mingzhen LI, Yi Liu, Bangduo CHEN, Hailong YANG, Zhongzhi LUAN & Depei QIANDocument19 pagesScience China Information Sciences: Mingzhen LI, Yi Liu, Bangduo CHEN, Hailong YANG, Zhongzhi LUAN & Depei QIANBoul chandra GaraiNo ratings yet

- Debugging Systems-on-Chip: Communication-centric and Abstraction-based TechniquesFrom EverandDebugging Systems-on-Chip: Communication-centric and Abstraction-based TechniquesNo ratings yet

- Remoting Patterns: Foundations of Enterprise, Internet and Realtime Distributed Object MiddlewareFrom EverandRemoting Patterns: Foundations of Enterprise, Internet and Realtime Distributed Object MiddlewareRating: 3.5 out of 5 stars3.5/5 (3)

- Embedded Systems: Analysis and Modeling with SysML, UML and AADLFrom EverandEmbedded Systems: Analysis and Modeling with SysML, UML and AADLFabrice KordonNo ratings yet

- SCCharts - Language and Interactive Incremental CompilationFrom EverandSCCharts - Language and Interactive Incremental CompilationNo ratings yet

- A Practical Approach to VLSI System on Chip (SoC) Design: A Comprehensive GuideFrom EverandA Practical Approach to VLSI System on Chip (SoC) Design: A Comprehensive GuideNo ratings yet

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipFrom EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNo ratings yet

- Validating Direct Memory Access Interfaces With Conformance CheckingDocument8 pagesValidating Direct Memory Access Interfaces With Conformance CheckingDuc DucNo ratings yet

- CMOS High Performance Programmable DMA Controller Features: Data Sheet FN2967.4 October 2, 2015Document26 pagesCMOS High Performance Programmable DMA Controller Features: Data Sheet FN2967.4 October 2, 2015Duc DucNo ratings yet

- A High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDocument4 pagesA High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDuc DucNo ratings yet

- 130nm CMOS Technology Design of Passive UHF RFID Tag inDocument4 pages130nm CMOS Technology Design of Passive UHF RFID Tag inDuc DucNo ratings yet

- Near-Field Loop Antenna For The UHF RFID Reader: Peng Yang, Yan Li, Li-Jun Jiang, and Feng YangDocument5 pagesNear-Field Loop Antenna For The UHF RFID Reader: Peng Yang, Yan Li, Li-Jun Jiang, and Feng YangDuc DucNo ratings yet

- Types - Difference Between Timestamps With - Without Time Zone in PostgreSQL - Stack OverflowDocument7 pagesTypes - Difference Between Timestamps With - Without Time Zone in PostgreSQL - Stack Overflow阿JuNo ratings yet

- Wiistron Raichu WL Pikachu WL 18730 R-1mDocument106 pagesWiistron Raichu WL Pikachu WL 18730 R-1mPhan ThanhNo ratings yet

- KXPDocument78 pagesKXPseintecNo ratings yet

- Computer Computer A AW Wareness Areness: Chapter - 1 Chapter - 1Document13 pagesComputer Computer A AW Wareness Areness: Chapter - 1 Chapter - 1uppaliNo ratings yet

- Control System Specification Energy Equity KeeraDocument42 pagesControl System Specification Energy Equity KeeraIkhtiander IkhtianderNo ratings yet

- Modicon M580 - BMEH586040Document6 pagesModicon M580 - BMEH586040Murat SultanovNo ratings yet

- 5 Apostila Manual de Instrução Cx-OneDocument65 pages5 Apostila Manual de Instrução Cx-OneSamuelVazDinizNo ratings yet

- Oracle DBA Workshop IIDocument4 pagesOracle DBA Workshop IIpgupta101No ratings yet

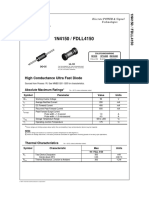

- 1N4150 FDLL4150Document3 pages1N4150 FDLL4150jsalinas88No ratings yet

- Tequed Labs PVT LTD: Recognized by Govt of IndiaDocument2 pagesTequed Labs PVT LTD: Recognized by Govt of IndiaAditya S KNo ratings yet

- Silo - Tips - Acunetix Web Vulnerability ScannerDocument101 pagesSilo - Tips - Acunetix Web Vulnerability ScannerCarlos Mejía GrandaNo ratings yet

- Manual BMW Ace3 enDocument23 pagesManual BMW Ace3 enoplcapitalinvestmentsNo ratings yet

- PtplogDocument510 pagesPtplogarthur KERRADNo ratings yet

- Programmable Logic DevicesDocument12 pagesProgrammable Logic Devicesrobinpt100% (1)

- Nexus Integration in JenkinsDocument13 pagesNexus Integration in JenkinsRahul BhatiNo ratings yet

- Synology DS1019 Plus Data Sheet EnuDocument6 pagesSynology DS1019 Plus Data Sheet EnuSteve AttwoodNo ratings yet

- Product Briefing ATN950 Ver1Document19 pagesProduct Briefing ATN950 Ver1Musoft AmasoftNo ratings yet

- Battery-Powered RS-232 To RS-422/485 Converter: Model 485BAT3Document2 pagesBattery-Powered RS-232 To RS-422/485 Converter: Model 485BAT3Ágost VitaNo ratings yet

- gps2436 OgDocument28 pagesgps2436 OgVince Joseph FabayNo ratings yet

- 10G SFPP Optical Transceivers Data Sheet by JTOPTICSDocument9 pages10G SFPP Optical Transceivers Data Sheet by JTOPTICSJayani Technologies LtdNo ratings yet

- Design and Simulation of Campus Area Network Using Cisco Packet TracerDocument7 pagesDesign and Simulation of Campus Area Network Using Cisco Packet TracerBaktiar HossainNo ratings yet

- Data Sheet 6ES7511-1AK01-0AB0: General InformationDocument11 pagesData Sheet 6ES7511-1AK01-0AB0: General Information蘇意正No ratings yet

- Specification: Mode: ZBT-WE826-T2 Description: Wi-Fi RouterDocument7 pagesSpecification: Mode: ZBT-WE826-T2 Description: Wi-Fi RouterManta Systems0% (1)

- NHD C12864LZ FSW FBW 3V3Document13 pagesNHD C12864LZ FSW FBW 3V3SrishtiNo ratings yet

- GA-990FXA-UD3: User's ManualDocument104 pagesGA-990FXA-UD3: User's ManualthqthqNo ratings yet

- Git For Devops Study MaterialDocument197 pagesGit For Devops Study Materialmuna cliffNo ratings yet

- Cerwin Vega CLSC 15 User ManualDocument4 pagesCerwin Vega CLSC 15 User Manualandrius.ringysNo ratings yet

Development and Distribution of TSMC 0.25 Cells

Development and Distribution of TSMC 0.25 Cells

Uploaded by

Duc DucOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Development and Distribution of TSMC 0.25 Cells

Development and Distribution of TSMC 0.25 Cells

Uploaded by

Duc DucCopyright:

Available Formats

Development and Distribution of TSMC 0.

25 m Standard CMOS Library Cells

Jeannette Donan Djigbenou and Dong Sam Ha VTVT (Virginia Tech VLSI for Telecommunications) Lab Bradley Department of Electrical and Computer Engineering Virginia Tech, Blacksburg VA 24061 E-mail: {jddjig01, ha}@vt.edu Abstract

Cell-based design is a widely adopted design approach in current ASIC and SOC designs. Standard cell libraries are a collection of basic building blocks that can be used in cell-based designs. The use of standard cell libraries offers shorter design time, induces fewer errors in the design process, and is easier to maintain. This paper presents the TSMC 0.25 m standard CMOS cell library designed and distributed by the Virginia Tech VLSI for Telecommunications (VTVT) Group, and its impact on the VLSI design community and VLSI education. real world design environment. Our standard cell library supports the following tools: Synopsys Design Compiler and Design Vision, as library compilation and logic synthesis tools, respectively. Synopsys VCS-MX, as a logic simulation tool. Cadence SOC Encounter, as a place-and-route tool. Cadence Virtuoso, as a verification and layout tool. In the design flow adopted for our standard cell library, the design entry is a VHDL or Verilog behavioral description. Using Synopsys synthesis and simulation tools, the behavioral description of the design is simulated and then synthesized into a gatelevel circuit. The synthesized design is extracted in the Verilog format and imported into the Cadence physical design environment. After place-and-route of the design, the synthesized layout is compared against its schematic.

1. Introduction

Commercial library cells are proprietary information of the suppliers, and suppliers usually impose certain restrictions on the access and use of their library cells. Those restrictions on commercial library cells hamper VLSI research and teaching activities of academia. In order to address this problem, the Virginia Tech VLSI for Telecommunications (VTVT) group took an initiative to develop and distribute standard cell libraries under the sponsorship of the National Science Foundation. Currently, a TSMC 0.25 m CMOS standard cell library developed by the VTVT group is available to academia without any restrictions [1], and 258 universities worldwide have received the cell library from the VTVT group as of March, 2007 [2].

3. Characteristics

The target technology for our standard cell library is TSMC 0.25 m CMOS with a supply voltage of 2.5 V. The cells were developed using the NCSU Cadence Design Kit [3] and following MOSIS deep submicron rules. Our cell library contains 84 cells with various primitive gates, multiplexers, and flip-flops with a variety of drive strengths and dummy pads. It includes layout, symbol, schematic views and functional models of all the cells, to support logic simulation and synthesis, place-and-route, and LVS (Logic Versus Schematic). Table 1 and Table 2 include our rules for layout of cells and a sample list of cells from the library, respectively.

2. Design flow

Our cell library was developed using commercial design and simulation tools with the intention to promote users as well as developers to experience the

2007 IEEE International Conference on Microelectronic Systems Education (MSE'07) 0-7695-2849-X/07 $20.00 2007

Table 1: Layout Development Rules

Cell Layout Setting

Cell Height Cell Width Metal Pitch Metal Width Metal Offset Power/Ground Pins/Rails Note: is 0.12 m.

Value

108 Multiple of 9 9 for metal 1 through metal 4, 18 for metal 5 4 for all layers 0 for all layers 11 for VDD and VSS

Table 2: Sample List of VTVT Library Cells Cell Name Description inv_[1,2,4] Inverter, drive strength 1, 2 or 4 2-input OR gate, drive strength 1, or2_[1,2,4] 2, or 4 nand4_[1,2,4] 4-input NAND gate, drive strength 1, 2, or 4 xnor2_[1,2] input XNOR gate, drive strength 1 or 2 mux2_[1,2,4] 2-to-1 multiplexer, drive strength 1, 2, or 4 fulladder One-bit ripple-carry adder, drive strength 1 ABnorC (ip1*ip2+ip3) drive strength 1 cd_16 clock driver, drive strength 16 lrsp_[1, 2, 4] active D latch with asynchronous low dp_[1,2,4] edge triggered D flip

include TSMC 0.18 m and 0.13 m by early 2009. We also plan to develop RAM compilers and data converters (analog-to-digital converters and digital-toanalog converters) for those technologies. We will verify our cell libraries through fabrication of test chips and report the results on our web sites. As technology advances, it is apparent that our group alone cannot keep up with cell libraries for new technologies. Our long term vision is to adopt the Open Source community approach. Whenever a new processing technology is available through MOSIS, we will provide guidelines (such as cell height, power/ground routing) and ask our users to develop, characterize and deposit a few new cells on our web site. After verification, the cells will be available to the general public, with due credit to contributors. This approach is not only sustainable, but will help the academic community to contribute to VLSI education and research needs and issues.

6. Summary

We believe that our standard cell library has greatly benefited both VLSI design and research communities in academia. Numerous universities across the globe have used our cells and provided feedback regarding future updates. We intend to test and release cuttingedge, reliable and diversified standard cell libraries. Moreover, our major design milestone will be to integrate academic institutions worldwide into a VLSI design community sharing critics and issues regarding pertinent and upcoming design approaches. This project is not only necessary for the present design community; its vision will also significantly impact future designers performance in industry, as they are being formed in academia through extensive and up-todate design materials.

4. Support to VLSI education

About 92 US and 166 international academic institutions have received our cell library for VLSI teaching and research [2]. In addition to development and distribution of our cell library, we have developed and maintained extensive tutorials of CAD tools for VLSI [4]. Major tutorials include: Cadence SOC Encounter, Synopsys Design Vision, and Synopsys VCS Scirocco simulator. A graduate and a senior level VLSI design courses at Virginia Tech use our library cells for class projects. Our online tutorials have also been extensively used in academia and frequently referred by companies. Approximately 20,000 visitors accessed our tutorials since March 2002.

Acknowledgment

This material is based upon work supported by the National Science Foundation under Grant No. 0551652.

References

[1] VTVT web site for a cell library request: www.vtvt.ece.vt.edu/vlsidesign/cell.php [2] VTVT web site for a users list: www.vtvt.ece.vt.edu/vlsidesign/users.php [3] NCSU design kit web site: www.eda.ncsu.edu/wiki/NCSU_EDA_Wiki [4] VTVT web site for tutorials: www.vtvt.ece.vt.edu/vlsidesign/tutorials.php

5. Our plan and vision

Since our initial release in 2002, we have received numerous requests to provide more cell libraries. These inquiries forged our groups plan and vision for the next two years. We plan to expand our cell libraries to

2007 IEEE International Conference on Microelectronic Systems Education (MSE'07) 0-7695-2849-X/07 $20.00 2007

You might also like

- Mips Fpga LabDocument10 pagesMips Fpga LabBiloKhanNo ratings yet

- Seminar Report On VLSIDocument21 pagesSeminar Report On VLSIGaurav Jaiswal75% (4)

- P200 New VersionDocument103 pagesP200 New VersionDELSP - Dynamic Elevator Services Pakistan81% (42)

- h11909 Emc Isilon Best Practices Eda WPDocument34 pagesh11909 Emc Isilon Best Practices Eda WPgabbu_No ratings yet

- Lab Module 1 - MySQL LabDocument10 pagesLab Module 1 - MySQL LabnutanayaNo ratings yet

- Phy Ie Report 17-20Document6 pagesPhy Ie Report 17-20RITIK JAINNo ratings yet

- Development of TSMC 0.25 M Standard Cell LibraryDocument3 pagesDevelopment of TSMC 0.25 M Standard Cell Libraryhex0x1No ratings yet

- Vlsi Design Thesis TopicsDocument8 pagesVlsi Design Thesis Topicsbsqfc4d5100% (2)

- AbstractDocument10 pagesAbstractbarsharaniraul123No ratings yet

- Thesis On Vlsi DesignDocument7 pagesThesis On Vlsi Designbrendatorresalbuquerque100% (2)

- Synopsys Open Educational Design KitDocument5 pagesSynopsys Open Educational Design KitAbhishek AvNo ratings yet

- VHDL Modeling and Design FlowDocument455 pagesVHDL Modeling and Design FlowPrabakaran RajendranNo ratings yet

- Very Large Scale IntegrationDocument3 pagesVery Large Scale IntegrationGowtham SpNo ratings yet

- Built-In Fault-Tolerant Computing Paradigm For Resilient Large-Scale Chip DesignDocument318 pagesBuilt-In Fault-Tolerant Computing Paradigm For Resilient Large-Scale Chip DesignostomaconsultingNo ratings yet

- Research Paper VlsiDocument6 pagesResearch Paper Vlsiafedsxmai100% (1)

- Basic VLSI Design ConceptDocument18 pagesBasic VLSI Design ConceptMoon Sadia DiptheeNo ratings yet

- PHD Thesis On Vlsi DesignDocument5 pagesPHD Thesis On Vlsi DesignBuyEssaysTulsa100% (2)

- Very Large Scale Integration (Vlsi)Document49 pagesVery Large Scale Integration (Vlsi)sayyioNo ratings yet

- Very-Large-Scale Integration - Wikipedia, The Free EncyclopediaDocument4 pagesVery-Large-Scale Integration - Wikipedia, The Free EncyclopediaSuneelkrishna RallabhandiNo ratings yet

- EECE 452 - Selected Topics in VLSIDocument3 pagesEECE 452 - Selected Topics in VLSIMarwan EidNo ratings yet

- Work?: International Test Conference PaperDocument2 pagesWork?: International Test Conference PaperTom MathewNo ratings yet

- Vlsi Research Paper TopicsDocument7 pagesVlsi Research Paper Topicsaflbtrnpf100% (1)

- The Very Large Scale IntegrationDocument7 pagesThe Very Large Scale IntegrationPallavi JayramNo ratings yet

- An Overview of VLSI: 1.2 What Is VLSI? 1.3 Complexity 1.4 Design 1.5 Basic Concepts 1.6 Summary 1.7 Problems ReferencesDocument14 pagesAn Overview of VLSI: 1.2 What Is VLSI? 1.3 Complexity 1.4 Design 1.5 Basic Concepts 1.6 Summary 1.7 Problems ReferencesVikas SurveNo ratings yet

- Research Paper Topics VlsiDocument7 pagesResearch Paper Topics Vlsihyzypif0gif3100% (1)

- Designing For Cisco Internetwork Solutions Lab Guide (CCDA DESGN 640-864) v2.1Document95 pagesDesigning For Cisco Internetwork Solutions Lab Guide (CCDA DESGN 640-864) v2.1axidnet100% (2)

- Introductory Chapter ASIC Technologies and DesignDocument11 pagesIntroductory Chapter ASIC Technologies and DesignDeev DeevNo ratings yet

- Multi-Project Wafer Serv..., The Free EncyclopediaDocument1 pageMulti-Project Wafer Serv..., The Free EncyclopediaSuneelkrishna RallabhandiNo ratings yet

- Research Paper Topics in VlsiDocument4 pagesResearch Paper Topics in Vlsij1zijefifin3100% (1)

- Vast - ITDocument15 pagesVast - ITpradeep9007879No ratings yet

- 1.1 Introduction of VlsiDocument35 pages1.1 Introduction of VlsiSneha GurrapuNo ratings yet

- Cad PDFDocument366 pagesCad PDFNitish KumarNo ratings yet

- About VlsiDocument14 pagesAbout VlsiAnonymous 1aqlkZNo ratings yet

- Adding Analog and Mixed Signal Concerns To A Digital VLSI CourseDocument8 pagesAdding Analog and Mixed Signal Concerns To A Digital VLSI CourseLavanya SelvarajNo ratings yet

- Vlsi Application: Applications of VLSI Circuits To Medical ImagingDocument4 pagesVlsi Application: Applications of VLSI Circuits To Medical ImagingshadhanaaNo ratings yet

- VLSI System Design Using Verilog - Step by Step Designing Procedure For CADENCE Incisive Enterprise SimulatorDocument150 pagesVLSI System Design Using Verilog - Step by Step Designing Procedure For CADENCE Incisive Enterprise Simulatorkolaverididhanush1No ratings yet

- IEEEVCAL Vol6 Issue3 Aug2020Document49 pagesIEEEVCAL Vol6 Issue3 Aug2020ET171046 JobaerNo ratings yet

- Course Code: Course Title: Pre-Requisite: Course ContentDocument2 pagesCourse Code: Course Title: Pre-Requisite: Course ContentFaisal HossainNo ratings yet

- Digital VLSI Chip Design With Cadence and Synopsys CAD ToolsDocument366 pagesDigital VLSI Chip Design With Cadence and Synopsys CAD ToolsMacy Yuan80% (5)

- Fire Alarm Controller ReportDocument18 pagesFire Alarm Controller ReportAnil KumarNo ratings yet

- Introduction To VLSI SystemDocument16 pagesIntroduction To VLSI SystemPrabakaran RajendranNo ratings yet

- Soas For Scientific Applications: Experiences and ChallengesDocument20 pagesSoas For Scientific Applications: Experiences and Challengesxico107No ratings yet

- Elena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Auth.), Elena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Eds.)-Wireless Sensor Networks_ Deployments AnDocument307 pagesElena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Auth.), Elena Gaura, Michael Allen, Lewis Girod, James Brusey, Geoffrey Challen (Eds.)-Wireless Sensor Networks_ Deployments AnrmieringeominasNo ratings yet

- IITD BrochureDocument10 pagesIITD Brochurejitu_4No ratings yet

- CSCE 612: VLSI System Design: Instructor: Jason D. BakosDocument14 pagesCSCE 612: VLSI System Design: Instructor: Jason D. BakosVinod RajNo ratings yet

- Standard Cell Library Design and Characterization Using 45nm TechnologyDocument5 pagesStandard Cell Library Design and Characterization Using 45nm TechnologyTitan FredNo ratings yet

- Cisco IT ACI DesignDocument28 pagesCisco IT ACI DesignCalota Mugurel AdrianNo ratings yet

- New Microsoft Word DocumentDocument3 pagesNew Microsoft Word DocumentSannena GovindaNo ratings yet

- VLSIDocument14 pagesVLSIPravallika RepanaNo ratings yet

- Ieee Research Paper On VlsiDocument6 pagesIeee Research Paper On Vlsiebvjkbaod100% (1)

- Term Paper On VlsiDocument5 pagesTerm Paper On Vlsiaflsvagfb100% (1)

- Chapter 1 IntroductionDocument21 pagesChapter 1 IntroductionIshrak AhmedNo ratings yet

- Design and Implementation of VLSI SystemsDocument41 pagesDesign and Implementation of VLSI SystemsCuong HuynhNo ratings yet

- Program Name Semester Course Code Course Name Lecture / Tutorial (Per Week) Lect. No. Course Coordinator NameDocument33 pagesProgram Name Semester Course Code Course Name Lecture / Tutorial (Per Week) Lect. No. Course Coordinator Nameishan goyalNo ratings yet

- Science China Information Sciences: Mingzhen LI, Yi Liu, Bangduo CHEN, Hailong YANG, Zhongzhi LUAN & Depei QIANDocument19 pagesScience China Information Sciences: Mingzhen LI, Yi Liu, Bangduo CHEN, Hailong YANG, Zhongzhi LUAN & Depei QIANBoul chandra GaraiNo ratings yet

- Debugging Systems-on-Chip: Communication-centric and Abstraction-based TechniquesFrom EverandDebugging Systems-on-Chip: Communication-centric and Abstraction-based TechniquesNo ratings yet

- Remoting Patterns: Foundations of Enterprise, Internet and Realtime Distributed Object MiddlewareFrom EverandRemoting Patterns: Foundations of Enterprise, Internet and Realtime Distributed Object MiddlewareRating: 3.5 out of 5 stars3.5/5 (3)

- Embedded Systems: Analysis and Modeling with SysML, UML and AADLFrom EverandEmbedded Systems: Analysis and Modeling with SysML, UML and AADLFabrice KordonNo ratings yet

- SCCharts - Language and Interactive Incremental CompilationFrom EverandSCCharts - Language and Interactive Incremental CompilationNo ratings yet

- A Practical Approach to VLSI System on Chip (SoC) Design: A Comprehensive GuideFrom EverandA Practical Approach to VLSI System on Chip (SoC) Design: A Comprehensive GuideNo ratings yet

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipFrom EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNo ratings yet

- Validating Direct Memory Access Interfaces With Conformance CheckingDocument8 pagesValidating Direct Memory Access Interfaces With Conformance CheckingDuc DucNo ratings yet

- CMOS High Performance Programmable DMA Controller Features: Data Sheet FN2967.4 October 2, 2015Document26 pagesCMOS High Performance Programmable DMA Controller Features: Data Sheet FN2967.4 October 2, 2015Duc DucNo ratings yet

- A High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDocument4 pagesA High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDuc DucNo ratings yet

- 130nm CMOS Technology Design of Passive UHF RFID Tag inDocument4 pages130nm CMOS Technology Design of Passive UHF RFID Tag inDuc DucNo ratings yet

- Near-Field Loop Antenna For The UHF RFID Reader: Peng Yang, Yan Li, Li-Jun Jiang, and Feng YangDocument5 pagesNear-Field Loop Antenna For The UHF RFID Reader: Peng Yang, Yan Li, Li-Jun Jiang, and Feng YangDuc DucNo ratings yet

- Types - Difference Between Timestamps With - Without Time Zone in PostgreSQL - Stack OverflowDocument7 pagesTypes - Difference Between Timestamps With - Without Time Zone in PostgreSQL - Stack Overflow阿JuNo ratings yet

- Wiistron Raichu WL Pikachu WL 18730 R-1mDocument106 pagesWiistron Raichu WL Pikachu WL 18730 R-1mPhan ThanhNo ratings yet

- KXPDocument78 pagesKXPseintecNo ratings yet

- Computer Computer A AW Wareness Areness: Chapter - 1 Chapter - 1Document13 pagesComputer Computer A AW Wareness Areness: Chapter - 1 Chapter - 1uppaliNo ratings yet

- Control System Specification Energy Equity KeeraDocument42 pagesControl System Specification Energy Equity KeeraIkhtiander IkhtianderNo ratings yet

- Modicon M580 - BMEH586040Document6 pagesModicon M580 - BMEH586040Murat SultanovNo ratings yet

- 5 Apostila Manual de Instrução Cx-OneDocument65 pages5 Apostila Manual de Instrução Cx-OneSamuelVazDinizNo ratings yet

- Oracle DBA Workshop IIDocument4 pagesOracle DBA Workshop IIpgupta101No ratings yet

- 1N4150 FDLL4150Document3 pages1N4150 FDLL4150jsalinas88No ratings yet

- Tequed Labs PVT LTD: Recognized by Govt of IndiaDocument2 pagesTequed Labs PVT LTD: Recognized by Govt of IndiaAditya S KNo ratings yet

- Silo - Tips - Acunetix Web Vulnerability ScannerDocument101 pagesSilo - Tips - Acunetix Web Vulnerability ScannerCarlos Mejía GrandaNo ratings yet

- Manual BMW Ace3 enDocument23 pagesManual BMW Ace3 enoplcapitalinvestmentsNo ratings yet

- PtplogDocument510 pagesPtplogarthur KERRADNo ratings yet

- Programmable Logic DevicesDocument12 pagesProgrammable Logic Devicesrobinpt100% (1)

- Nexus Integration in JenkinsDocument13 pagesNexus Integration in JenkinsRahul BhatiNo ratings yet

- Synology DS1019 Plus Data Sheet EnuDocument6 pagesSynology DS1019 Plus Data Sheet EnuSteve AttwoodNo ratings yet

- Product Briefing ATN950 Ver1Document19 pagesProduct Briefing ATN950 Ver1Musoft AmasoftNo ratings yet

- Battery-Powered RS-232 To RS-422/485 Converter: Model 485BAT3Document2 pagesBattery-Powered RS-232 To RS-422/485 Converter: Model 485BAT3Ágost VitaNo ratings yet

- gps2436 OgDocument28 pagesgps2436 OgVince Joseph FabayNo ratings yet

- 10G SFPP Optical Transceivers Data Sheet by JTOPTICSDocument9 pages10G SFPP Optical Transceivers Data Sheet by JTOPTICSJayani Technologies LtdNo ratings yet

- Design and Simulation of Campus Area Network Using Cisco Packet TracerDocument7 pagesDesign and Simulation of Campus Area Network Using Cisco Packet TracerBaktiar HossainNo ratings yet

- Data Sheet 6ES7511-1AK01-0AB0: General InformationDocument11 pagesData Sheet 6ES7511-1AK01-0AB0: General Information蘇意正No ratings yet

- Specification: Mode: ZBT-WE826-T2 Description: Wi-Fi RouterDocument7 pagesSpecification: Mode: ZBT-WE826-T2 Description: Wi-Fi RouterManta Systems0% (1)

- NHD C12864LZ FSW FBW 3V3Document13 pagesNHD C12864LZ FSW FBW 3V3SrishtiNo ratings yet

- GA-990FXA-UD3: User's ManualDocument104 pagesGA-990FXA-UD3: User's ManualthqthqNo ratings yet

- Git For Devops Study MaterialDocument197 pagesGit For Devops Study Materialmuna cliffNo ratings yet

- Cerwin Vega CLSC 15 User ManualDocument4 pagesCerwin Vega CLSC 15 User Manualandrius.ringysNo ratings yet