Professional Documents

Culture Documents

Embedded System Design

Embedded System Design

Uploaded by

Kirthi Rk0 ratings0% found this document useful (0 votes)

66 views15 pagesThis document contains information about Shirdi Sai Engineering College. It repeats the name of the college 8 times. No other information is provided about the college or its programs.

Original Description:

esd

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains information about Shirdi Sai Engineering College. It repeats the name of the college 8 times. No other information is provided about the college or its programs.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

66 views15 pagesEmbedded System Design

Embedded System Design

Uploaded by

Kirthi RkThis document contains information about Shirdi Sai Engineering College. It repeats the name of the college 8 times. No other information is provided about the college or its programs.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 15

SHIRDI SAI ENGINEERING COLLEGE

SHIRDI SAI ENGINEERING COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

f

I

I

r =

0)

'0

Z

;:

l

t

o

c.

E

~~~~

~~~l l l It5

USN

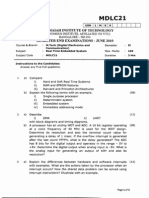

EC835

Eighth Semester B.E. Degr ee Examination, December 2010

Embedded System Design

Time: 3 hr s. Max. Mar ks: 100

Note: 1.Answer any FIVEfull questions.

2. Standard notations are used.

3. Missing data may be suitably assumed.

1 a. Whatar ethe char acter istics of anembedded systemdesign? Listthe design metr ics used to

compar e them. (07Mar ks)

b. Deter mine ther evenue l oss, if thepr oduct's l ifetime is74 weeks and thedel ay inthemar ket

is6weeks. Der ive thefor mul a used for thecal cul ation. (07Mar ks)

c. For apar ticul ar pr oduct, deter mine theNRE costand unitcostto be the fol l owing for the

thr eel isted IC technol ogies:

FPGA ($10000, $50): ASIC ($50000, $10)

VLSI ($200000, $5)

Deter mine thepr ecise vol umes for which eachtechnol ogy yiel ds thel owesttotal cost.

(06 Mar ks)

2 a. Devel op an efficient al gor ithm for GCD. Conver t itto FSMD and show the optimized

FSMD. (10Mar ks)

b. Withaneatdiagr am, expl ain thear chitectur e of agener al pur pose pr ocessor . (10Mar ks)

3 a. Define thefol l owing: (04 Mar ks)

i) Cr oss compil er ii) Emul ator iii) Debugger iv) Incir cuitsimul ator

b. Differ entiate between:

i) Singl e pur pose and gener al pur pose pr ocessor s

ii) Har var d and von-Neumann ar chitectur e (06 Mar ks)

c. With a neat diagr am, expl ain how the pul se width modul ator wor ks. What ar e the

consider ations in sel ecting the cl ock, the pr escal ar and the counter ? Assuming an 8-bitup

counter , cal cul ate the countto be l oaded in the 'cycl e-high' r egister to getpul ses of duty

cycl e75%. (10Mar ks)

4 a. Given an anal og inputsignal whose vol tage r anges fr om 0 to 5 v and an 8-bitdigital

encoding, cal cul ate the cor r ect encoding for 3.5 v and then tr ace the successive

appr oximation appr oach tofind thecor r ectencoding. (08Mar ks)

b. Whatiscachemapping? Expl ain thedir ectmapping techniques for cache. (08Mar ks)

c. Expl ain theter ms wr iteabil ity and stor ageper manence. (04Mar ks)

5 a. Expl ain two l evel mul ti busar chitectur e, withaneatdiagr am. (06 Mar ks)

b. Compose l Kx 8ROMs into2K x 16ROM. (06Mar ks)

c. Given the fol l owing thr ee cache designs, find the one with the bestper for mance, by

cal cul ating theaver age costof access. Show al l cal cul ations.

i) 4K byte, 8-way-setassociative cache, with a6% miss r ate; cache hitcosts onecycl e,

cache miss costs 12cycl es

ii) 8K byte, 4-way-set associative cache with a4% miss r ate; cache hitcosts 2cycl es,

cache miss costs 12cycl es

iii) 16K byte, 2-way-set associative cache with a2% miss r ate; cache hitcosts 3cycl es,

cache miss costs 12cycl es. (08 Mar ks)

10f2

SHIRDI SAI ENGG COLLEGE

6 a.

b.

c.

7 a.

b.

c.

8 a.

b.

c.

d.

...

EC835~

Whatisinter r uptl atency? Whatar ethefactor s affecting it? (08Mar ks)

Expl ain withanexampl e, how theRound-Robin ar chitectur e wor ks. When isitnotsuitabl e?

(08 Mar ks)

Whatisar eentr antfunction? Givethethr eer ul es todecide r eentr antfunctions. (04Mar ks)

Whatissemaphor e? Expl ain RTOS semaphor e. (10Mar ks)

Differ entiate between har d and softRTOS highl ighting theadvantages and disadvantages of

~h. ~~~

Expl ain 'deadl y embr ace'. (04 Mar ks)

Whatisanevent? Givethr eestandar d featur es of anevent. (05 Mar ks)

Giveacompar ison of methods for inter task communication. (04 Mar ks)

Expl ain thetwo r ul es, thattheinter r uptr outines mustfol l ow, inRTOS envir onment. Whatis

theeffectof bl ocking oninter r upts? Expl ain withadiagr am. (08 Mar ks)

Expl ain ther ol eoftimer function inRTOS. (03Mar ks)

* * * * *

20f2

SHIRDI SAI ENGG COLLEGE

Eighth Semester B.E. Degree Examination, May/June 2010

Embedded System Design

Note: Answer any FIVE full questions, selecting

. at least TWO questions from each part.

1 a.

b.

c.

2 a.

b.

c.

3 a.

b.

c.

Mention thecharacteristics and briefly list thedesign metrics of anembedded system.

(08 Marks)

Determine thepercentage of revenue loss if theproducts lifetime is 86 weeks and thedelay

inthemarket is8weeks. Derive theformula used for this calculation. (06 Marks)

Explain how thetop-down design process improves theproductivity. (06 Marks)

Briefly explain thepurpose of thedatapathand controller inasingle purpose processor.

(06 Marks)

Write anefficient algorithm for finding theGCD of two integer numbers. Also explain how

theFSMD for this canbeoptimized. (08 Marks)

Explain various addressing modes that arecommonly used byprocessors, withanexample.

(06 Marks)

Explain how DART isused for communication. List its advantages. (08 Marks)

What is awatch dog timer? List its uses. A 16 bit timer operates at a clock frequency of

12MHz. Determine theresolution and rangeof this timer. .. (06 Marks)

The analog input range for a8-bit ADC isfrom-2.5V to 8.5V. Determine theresolution of

ADC and digital output in hexadecimal, when the input voltage is 1.2V. Trace successive

approximation steps and show thebinary output of theADC. (06 Marks)

4 a. What is memory hierarchy? How does the cache operate? Discuss the cache mapping

techniques. List their merits and demerits. (10 Marks)

b. Briefly explain OTPROM, EEPROM, RDRAM and FPM DRAM. (10Marks)

5 a. Explain theneed for interrupts inprocessors and mention briefly thevarious events that take

placewhen aprocessor isinterrupted. (10Marks)

b. Explain the problems of shared-data interrupts and suggest the solution to solve the

problems. (10Marks)

6 a. Explain with anexample, how theRound-Robin architecture works. What is its limitation?

(12Marks)

b. List the characteristics of four software architectures available for building embedded

software. (08 Marks)

a. Mention the two rules of interrupt routines in an RTOS environment. With an example,

briefly explain, what happens when eachruleisviolated. (15 Marks)

b. Describe theuseof message queues. (05 Marks)

a. What ismeant byencapsulating thesemaphores? Bring out theneed for it.

b. Explain any six problems of semaphores.

c. Explain themethods tosolvememory spaceand methods tosavepower.

(08 Marks)

(06 Marks)

(06 Marks)

SHIRDI SAI ENGG COLLEGE

Eighth Semester B.E. Degree Examination, May/June 2010

Embedded System Design

o

()

'~ Note: Answer any FIVEfull questions.

0-

g 1 a. Define an Embedded system. Explain any three important characteristics of an embedded

~ system. (06Marks)

'E b. What is a Watchdog Timer? Why it is so called? Explain its role in the design of any

C < i

~ embedded system. (06Marks)

<I i Q)

~.D c. Determine the percentage revenue loss if theproduct lifetime is 74 weeks and thedelay in

oj=:

~'~ themarket is 6weeks. Derive theformula used. (08Marks)

6

::c'; 2 a. Explain theconcept of 'datapath' as applied toan embedded system. Give an example.

en

,5 '!f (06Marks)

,~~ b. Explain the role of a Finite State Machine (FSM) model in the design of an embedded

~~ system using a suitable example. (06Marks)

.s ~ c. Assume an 8bit encoding of input voltage in the range -5V to+5V. C alculate theencoding

'~ for 1,2V and trace the successive approximation approach to find the correct encoding.

,~ What is theresolution of theconversion? (08Marks)

:;.~

1350 Explain the steps involved in designing ageneral purpose processor. (06Marks)

ti Q)

OJ 0 Explain theconcept ofPWM speed control circuit as applied toan embedded system.

:; (06Marks)

enc

:6 ~ Define thefollowing: i) Assembler ii) C ross compiler iii) Emulator iv) Simulator.

~.8 (08Marks)

~. 2

~ ~ Differentiate between: i) PSRAM and NVRAM ii) SRAM and DRAM

' .8 iii) FLASH and EPROM. (06Marks)

</} -

]. [ Briefly describe theprinciples used in three replacement policies normally employed during

- cachememory operation. (06Marks)

() 0

i, In a hierarchy design of memory, the cache miss rate is 15%, cost of memory access is 20

Q) - -

~~ cycles and cost of cache access is 2 cycles. Determine theaverage cost of access. (08Marks)

; ~ Show an interface of2kx16ROM from lkx8ROM. Explain thedecoding logic used.

>-. '+-< (06Marks)

en

o

.~r Explain the features of the following bus architecture : i) C AN bus ii) IEEE - 802.11.

0. ~ (06Marks)

~ What is multi - level bus architecture? Explain its need and also thereasons toimprove the

<5 t processor performance by this architecture. (08Marks)

3 a.

b.

c.

4 a.

b.

c.

5 a.

b.

c.

a. What is interrupt latency? Explain thefactors affecting it.

b. Describe Round Robin architecture with an example.

c. Define semaphore and critical sections as applied to real time operating system.

a. Describe the function of ascheduler with asuitable transition diagram.

b. Explain theuseof message queues with an example.

c. Explain therole of timer function in RTOS.

a. Discuss briefly Hard Real time scheduling considerations.

b. What is meant by encapsulating asemaphores? Mention its applications.

c. Write abrief note on: i) Deadly Embrace ii) Priority Inversion.

(06Marks)

(06Marks)

(08Marks)

(06Marks)

(06Marks)

(08Marks)

(06Marks)

(06Marks)

(08Marks)

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

SHIRDI SAI ENGG COLLEGE

You might also like

- Introductory Statistics 8th Edition Mann Solutions ManualDocument29 pagesIntroductory Statistics 8th Edition Mann Solutions ManualJohnWhitextnzm100% (13)

- Faith, Rita - Neville Goddard - Master Your Inner Game To Achieve Your Every Desire (2016) - Libgen - LiDocument41 pagesFaith, Rita - Neville Goddard - Master Your Inner Game To Achieve Your Every Desire (2016) - Libgen - LiDipikaNo ratings yet

- Ervin Laszlo Science and The Akashic Field PDFDocument2 pagesErvin Laszlo Science and The Akashic Field PDFSara0% (2)

- Lllit5: Embedded System DesignDocument4 pagesLllit5: Embedded System DesignAnonymous 2MwnnyNo ratings yet

- Embedded System Design PDFDocument37 pagesEmbedded System Design PDFLavanya R GowdaNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- 2010 - May - June-2010Document1 page2010 - May - June-2010nitte5768No ratings yet

- Computer Organization Jan 2014Document1 pageComputer Organization Jan 2014Prasad C MNo ratings yet

- RTS QPDocument6 pagesRTS QPbalajibs203285No ratings yet

- 7th Sem Cse 2010 Scheme - Question PaperDocument8 pages7th Sem Cse 2010 Scheme - Question PaperReshma BJ67% (3)

- Adca / Mca (Iii Year) 7t' Term-End Examination December, 2011 Cs-12: Computer ArchitectureDocument3 pagesAdca / Mca (Iii Year) 7t' Term-End Examination December, 2011 Cs-12: Computer Architecturehaider_ali980No ratings yet

- 06 CS81 ACADec 10Document2 pages06 CS81 ACADec 10Mohammed YasinNo ratings yet

- 2010 - May - June-2010)Document1 page2010 - May - June-2010)nitte5768No ratings yet

- r05410207 Vlsi DesignDocument7 pagesr05410207 Vlsi Design9010469071No ratings yet

- Digital System Design Using Verilog December 2011Document1 pageDigital System Design Using Verilog December 2011Vinayaka HmNo ratings yet

- DCSFinal II April21 AssignmenrtDocument45 pagesDCSFinal II April21 AssignmenrtChirantan BiswasNo ratings yet

- 5 Oct11Document12 pages5 Oct11Manu SeaNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- Embedded Systems Model Question PaperDocument6 pagesEmbedded Systems Model Question PaperSubramanyaAIyerNo ratings yet

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzNo ratings yet

- (3965) - 636 M.E. (E & TC) : (VLSI & Embedded Systems)Document14 pages(3965) - 636 M.E. (E & TC) : (VLSI & Embedded Systems)Manu SeaNo ratings yet

- BE 2008 Electronics&Telecommunication PDFDocument71 pagesBE 2008 Electronics&Telecommunication PDFcontrasterNo ratings yet

- Question BanksDocument74 pagesQuestion BanksVidhya GanesanNo ratings yet

- Mca RevisedDocument130 pagesMca RevisedAmbalika SharmaNo ratings yet

- Tutorial 3 2022 StudentsDocument5 pagesTutorial 3 2022 StudentsIndongo EliaserNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- Vlsi QP 1Document6 pagesVlsi QP 1Sailesh PosaniNo ratings yet

- r05320402 Vlsi DesignDocument4 pagesr05320402 Vlsi DesignSRINIVASA RAO GANTANo ratings yet

- 7th ITDocument6 pages7th ITYashika JindalNo ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Document9 pagesM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaNo ratings yet

- Simulation Modeling of Manufacturing SystemsDocument8 pagesSimulation Modeling of Manufacturing SystemsSrimanthula SrikanthNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssushNo ratings yet

- Ap7202-Asic and FpgaDocument12 pagesAp7202-Asic and FpgaMOTHI.R MEC-AP/ECENo ratings yet

- 07a80402 EmbeddedandrealtimesystemsDocument6 pages07a80402 EmbeddedandrealtimesystemsSharanya ThirichinapalliNo ratings yet

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- Te Oct 2014Document149 pagesTe Oct 2014contrasterNo ratings yet

- Nited Nstitute of EchnologyDocument11 pagesNited Nstitute of Echnologykeerthi3214No ratings yet

- (3hours) : CompulsoryDocument7 pages(3hours) : CompulsorySaima ZainabNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Karthiga MuruganNo ratings yet

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MNo ratings yet

- Question Bank CompleteDocument5 pagesQuestion Bank CompleteSaurabh SenNo ratings yet

- Nr-Vlsi Technology and DesignDocument2 pagesNr-Vlsi Technology and DesignSudhakar SpartanNo ratings yet

- AFD Important QuestionsDocument6 pagesAFD Important QuestionsManikandan RajuNo ratings yet

- CAO 2021 Assignment QuestionDocument9 pagesCAO 2021 Assignment Questiondawit tadewoseNo ratings yet

- DDCO UPDATED QUESTION BANKttttDocument4 pagesDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseNo ratings yet

- Adv. Computer Architecture CS701 - Jan 011Document2 pagesAdv. Computer Architecture CS701 - Jan 011Sachin Kumar GoyelNo ratings yet

- Computer Organization Jun 2010Document2 pagesComputer Organization Jun 2010Prasad C MNo ratings yet

- EC2303 Computer Architecture and Organization QUESTION PAPERDocument4 pagesEC2303 Computer Architecture and Organization QUESTION PAPERJayagopal JaiNo ratings yet

- Co ImpDocument7 pagesCo ImpG09Deviprasad N shettyNo ratings yet

- Real Time Embedded Systems M TechDocument2 pagesReal Time Embedded Systems M Techammayi9845_930467904No ratings yet

- Micro Processor and ApplicationsDocument2 pagesMicro Processor and Applicationsapi-3782519No ratings yet

- 7 Dec09-Jan10 DSP Al and Arch.Document2 pages7 Dec09-Jan10 DSP Al and Arch.suresha vNo ratings yet

- QP April2011 42 Mec IcgDocument4 pagesQP April2011 42 Mec IcgMohammedshafeeq Ahmed0% (1)

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- Computer Integrated Manufacturing (Model QP) : CBCS SchemeDocument2 pagesComputer Integrated Manufacturing (Model QP) : CBCS SchemeMuwaizNo ratings yet

- MCS 012Document118 pagesMCS 012SongYak YamNo ratings yet

- Old Q.papers M.tech I SemDocument15 pagesOld Q.papers M.tech I SemallakagopichandNo ratings yet

- MCA (Revised) Term-End Examination - Une, 2409Document4 pagesMCA (Revised) Term-End Examination - Une, 2409ammanNo ratings yet

- Introduction Microprocessors July 2005 OldDocument2 pagesIntroduction Microprocessors July 2005 OldPrasad C MNo ratings yet

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingFrom EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingNo ratings yet

- M/M/1 Model Arrival Service 1 ServerDocument3 pagesM/M/1 Model Arrival Service 1 ServerKirthi RkNo ratings yet

- KedaDocument2 pagesKedaKirthi RkNo ratings yet

- Bella Heath Care IndiaDocument8 pagesBella Heath Care IndiaKirthi RkNo ratings yet

- Research ReviewDocument6 pagesResearch ReviewKirthi RkNo ratings yet

- Com PatternsDocument15 pagesCom PatternsKirthi RkNo ratings yet

- Keerthi R: ObjectiveDocument3 pagesKeerthi R: ObjectiveKirthi RkNo ratings yet

- Macroeconomics Study SheetDocument2 pagesMacroeconomics Study SheetKirthi RkNo ratings yet

- Rearrange The Following Letters ND Identify The Economic Concept - Toscunitpopyrt - Ductioprossibilityp - Tivemaorn - Osiptive - Tarpial - ArcarcitysDocument2 pagesRearrange The Following Letters ND Identify The Economic Concept - Toscunitpopyrt - Ductioprossibilityp - Tivemaorn - Osiptive - Tarpial - ArcarcitysKirthi RkNo ratings yet

- Privatization of IRKDocument1 pagePrivatization of IRKKirthi RkNo ratings yet

- Procedures in Setting Up An Enterprise & Legal Requirements: PRE - Operational StageDocument2 pagesProcedures in Setting Up An Enterprise & Legal Requirements: PRE - Operational StageKirthi RkNo ratings yet

- Factors Affecting Shift of Demand: When The Demand Curve ShiftsDocument7 pagesFactors Affecting Shift of Demand: When The Demand Curve ShiftsKirthi RkNo ratings yet

- Blood Donation Campaign Theni DistrictDocument4 pagesBlood Donation Campaign Theni DistrictKirthi RkNo ratings yet

- ITS Frito Lay CaseDocument2 pagesITS Frito Lay CaseKirthi RkNo ratings yet

- Host A Blood Donation CampDocument1 pageHost A Blood Donation CampKirthi RkNo ratings yet

- Financial Accounting For ManagersDocument23 pagesFinancial Accounting For ManagersKirthi Rk100% (1)

- Image Processing1Document6 pagesImage Processing1Kirthi RkNo ratings yet

- TE040 System Test ScriptDocument10 pagesTE040 System Test ScriptPrasad RajashekarNo ratings yet

- Global Political Economy Exam PaperDocument10 pagesGlobal Political Economy Exam PaperNenad Krstevski100% (1)

- Air Quality Standard BIDocument1 pageAir Quality Standard BIFirrdhaus SahabuddinNo ratings yet

- Basics of Remote Sensing and Gis Ce 333 Unit - 1 Remote SensingDocument13 pagesBasics of Remote Sensing and Gis Ce 333 Unit - 1 Remote SensingShanmuga SundaramNo ratings yet

- Aldrich Polymer Products - CD Catalog and Reference GuideDocument546 pagesAldrich Polymer Products - CD Catalog and Reference GuideanbuchelvanNo ratings yet

- Gkindiaonline.comDocument19 pagesGkindiaonline.comVarun Yadav100% (1)

- ACS Guide UserDocument124 pagesACS Guide UserJose GomesNo ratings yet

- ASME Flange Loading CalculationDocument1 pageASME Flange Loading CalculationssjunedNo ratings yet

- MMR Round3Document152 pagesMMR Round3Abhishek YadavNo ratings yet

- Crim TicDocument38 pagesCrim TicTORRES , VENUSNo ratings yet

- Algorithms and Data Structures: Simonas ŠaltenisDocument49 pagesAlgorithms and Data Structures: Simonas ŠaltenisMahdiyah M. SaidNo ratings yet

- IEEE Transactions on Industrial Electronics Volume issue 2018 [doi 10.1109_TIE.2018.2866115] Mohapatra, Soumya Ranjan; Agarwal, Vivek -- Model Predictive Controller with Reduced Complexity for Grid .pdfDocument5 pagesIEEE Transactions on Industrial Electronics Volume issue 2018 [doi 10.1109_TIE.2018.2866115] Mohapatra, Soumya Ranjan; Agarwal, Vivek -- Model Predictive Controller with Reduced Complexity for Grid .pdfElahe Hoseini NasabNo ratings yet

- Errors in Chemical AnalysisDocument51 pagesErrors in Chemical AnalysisJeffrey PalconeNo ratings yet

- M20 Operatives Dossier (Final Download)Document102 pagesM20 Operatives Dossier (Final Download)Michael SearleNo ratings yet

- PresentaionDocument12 pagesPresentaionMidhun MvNo ratings yet

- Ordysy Capabilities DeckDocument6 pagesOrdysy Capabilities DeckKunal BajajNo ratings yet

- Stability of StructuresDocument12 pagesStability of StructuresPriyaNo ratings yet

- Revised PlanDocument10 pagesRevised PlanRinoy R BhagoraNo ratings yet

- Screen 2014 Uricchio 119 27Document9 pagesScreen 2014 Uricchio 119 27NazishTazeemNo ratings yet

- Tajuk 2 Personaliti Dan SukanDocument42 pagesTajuk 2 Personaliti Dan SukanMee Lian FongNo ratings yet

- CTR Tti Misc YukselDocument99 pagesCTR Tti Misc YukselMahnooranjumNo ratings yet

- Extended Viterbi Algorithm For Second Order Hidden Markov ProcessesDocument3 pagesExtended Viterbi Algorithm For Second Order Hidden Markov Processestable999No ratings yet

- GradesDocument4 pagesGradesJericho PedragosaNo ratings yet

- D3711Document5 pagesD3711rimi7alNo ratings yet

- SCIENCE K 12 Curriculum GuidesDocument172 pagesSCIENCE K 12 Curriculum GuidesRichealyn C. TadeoNo ratings yet

- 1.3 Creating Effective Prompt GuideDocument1 page1.3 Creating Effective Prompt Guidetonbar000No ratings yet

- Tự Luận 1. Question 1. (6 points) The Vietnamese poem and its English translationDocument7 pagesTự Luận 1. Question 1. (6 points) The Vietnamese poem and its English translationVothi ThuyhanhNo ratings yet

![IEEE Transactions on Industrial Electronics Volume issue 2018 [doi 10.1109_TIE.2018.2866115] Mohapatra, Soumya Ranjan; Agarwal, Vivek -- Model Predictive Controller with Reduced Complexity for Grid .pdf](https://imgv2-2-f.scribdassets.com/img/document/442862669/149x198/015e35b7eb/1578984110?v=1)