Professional Documents

Culture Documents

Gottlieb System 80 Technical Seminar

Gottlieb System 80 Technical Seminar

Uploaded by

api-3713719100%(1)100% found this document useful (1 vote)

509 views62 pagesOriginal Title

Gottlieb System 80 technical seminar

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF or read online from Scribd

Download as pdf

100%(1)100% found this document useful (1 vote)

509 views62 pagesGottlieb System 80 Technical Seminar

Gottlieb System 80 Technical Seminar

Uploaded by

api-3713719Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 62

mien eae

BS YA ea ke

- Y/ORKBOOK

165 W.loke Sect Nevihiale,

(sia}sez"ra00 Telex 72-644

iLeorea

63

‘AColumbio Pictures incusties Company na

TECHNICAL

SEMINAR

WORKBOOK

AMUSEMENT GAMES

165 W.Loxe sree! Nochigke, sms

312) 862-7400 Telex 72-6463,

ACowmbla Plctues ndusties Company

COPYRIGHT ©1983

ALL RIGHTS RESERVED

i

TABLE OF CONTENTS

PAGE

L. INTRODUCTION ....

Il. POWER DISTRIBUTION ........... settee ee seeeeee B

III. MODES OF OPERATION ..........0eceeeeeeeeeee eens B

Iv. CONTROLLED DEVICES «1.0... 00. eeee essen sence ee ee LL

@ CONTROLLED LAMPS «1.0... esse sees eee e eee ee 14

@ CONTROLLED SOLENOIDS ...........---

@ SOLENOID OPERATION ....-.-.-22.2-22222005 7

@ NON-CONTROLLED SOLENOIDS .......-..-.---- 18

@ «SWITCH MATRIX .... 19

© DISPLAYS ...

@ SOUND/SPEECH .....-02 202202002 ceeeeeeeees 24

v. MEMORY DEVICES ......-2...02.222220255 seeeeee es BB

VI. VIDEO TROUBLESHOOTING «1.00... .e sees sees eee sees 32

@ INTRODUCTION .. 0.0.00. cece cence eee eee eee 82

@ POWER DISTRIBUTION ........

@ =LOGIC/CONTROL BOARD «1.0.00... cece ence eee 42

VII. GENERAL INFORMATION .. 1-0... ssc eee eee e eee eeeee 45

@ MECHANICAL ASSEMBLIES ...........5

@ CHARTS oot eee ee 8B

@ BOOKKEEPING 0.0.00... see e sees eee rece eee ee 56

@ GLOSSARY OF TERMS 26.00... eee e eee ee 87

ii

I. INTRODUCTION

The objective of this manual is to

provide operators and servicemen

with a basic knowledge and under-

standing of Gottlieb's game sys-

tems, This knowledge will provide

a better understanding of how to

troubleshoot a Gottlieb game on lo-

cation.

This manual concentrates on simple,

fast maintenance for on-location

troubleshooting. It also contains

technical information that can be

used to understand basic electron-

ies and schematic reading. For all

procedures covered in this seminar

and most problems that will be en-

countered in the field, the test

equipment required will be a multi-

meter and a pair of jumper wires.

GENERAL TROUBLESHOOTING GUIDE

Identify the symptoms. (Recog-

nizing and establishing the

Le

symptoms early will narrow down

the problem).

2, Determine in what operation

mode(s) symptom(s) occur. (Dif-

ferent modes of the game are

controlled by specific devices).

Use the Self-Test feature to

help determine where the prob-

lem is.

Determine if problem is mechani-

cal or electronic in nature,

i.e., a short on a switch line

can cause problems with the CPU

board, but the solution is me-

chanical in nature.

9.

Check for common or shared cir- 10.

cuits, i-e., one display, two

displays, or all displays have

a common symptom.

6. After using the Self-Test to nar-

INTRODUCTION

row down the problem, check the

easy things first...fuses, wir-

ing faults, burned out bulbs,

ete.

Use wire color codes and plug

numbers to guide yourself through

the game. Gottlieb has a stan-

dardized numbering system to aid

in troubleshooting and schematic

reading.

Intermittent problems:

A. Pinched or hanging wires

(check near edges of play-

field).

B, Switch adjustments or defec-

tive diodes.

Check voltage levels at their

destination points. Check the

+5V DC at the Al control board.

Call our toll-free number, 1-800-

323-9121 (outside Illinois) and

1-800-942-1620 (in Illinois),

with this background information

to get the quickest and most

complete answer possible.

$a VOLUME

Sw CONTROL

SPEAKERS

1. INR

SLAM SWITCH

CONTROLLED SOLENOIDS

(connec cs) LAMPS

NOT MICROPROCESSOR CONTROLLED

NON-CONTROLLED SOLENOIDS

+24V DC

FIGURE 1. GOYTLI

UCTION

FRONT DOOR,

TILTS ANO

SWITCH MATRIX P| STROBE

CONTROL BOARD A‘

Hevicos 4cuz—

MEMORIES

ROM, RAM, PROM

SCORE/

STATUS

DISPLAYS

Av

AUXILIARY

POWER SUPPLY

1. Arrows point in direction of flow.

2. Display problems and switch matrix problems, do not involve

(A3) DRIVER BOARD.

3. Non-Controlled Solenoids and tilumination lamps, are not

. microprocessor controlled (DON'T LOOK AT CONTROL BOARD).

} SYSTEM 80/804

4

Il. POWEE

[BOTTOM BOARD

1

1

a4

ee

=

bat

-y rok

+evoc oFrser

cs l

SAC RETURN = t

i I

vac -—__.

4#5¥v0C OFFSET |

ima I

SAC RETURN pla.

1] fre ac

lev Ac

Le2av 06

TT LMP

MATCH LAMP Q

BALL

paar Le

com CHUTE

‘CONTROLLED (>)

PLAYFIELD CAMPS.

coNTROLLED (>)

uciteox Laws (fl) sevoe

TRIBUTION

+8v 00

+8v0C

‘GND

‘OND

+60v0

| [9881_,.aev 0c

| geno

+8v 0c

—r+sv 0c

vo six o16iT

4 oiseLay

To Foun Digit

BisbLay

AT

SOUND/SPEECH

‘POWER SUPPLY

“$ 1BPS. ro sounovsreEcH

—S Uiver "soar ae

TRANSFORMER PANEL

NoTES:

|. SOLENOIDS AND OPTIONAL COUNTERS

USE Insooe Doves,

Z.QPTIONAL CON METERS, USED

PHROUSH HAUNTED.

SLMS ARE 14a,

House

4-{I-INDICATES CONNECTOR

‘5, (288L INOCATES WIRE COLOR.

ofecacx [5 Green

1 Tenown tre | ewe

2 TRED 7 | PURPLE

| onance |e] suare.

| vettow — [fe] wHiTe

{FUSE RATING OEPENOENT CN SPECIFIC

(GAME

7 PRIMARY FUSE. VALUE:

Tisv~ USE’ SA Sto.

2oV- Use 258

18.230 TRANSFORMER:

PRIMARY WARING:

B0V,

sy,

100,

ofr cu,

S.GERMAN TRANSFORMERS:

10

30

19849

19583

REFER TO WSTAUCTION MANUAL. FOR

‘SERMAN GAME VARIATIONS.

10,0, RELAYS NOT FUSED.

1 UNLESS OTHERWSSE SPECIFIED:

“$3.VCC WIRE COLOR.

Geo WiRe COLOR Se

FIGURE 2, GOTTLIEB SYSTEM 80/804

POWER DISTRIBUTION

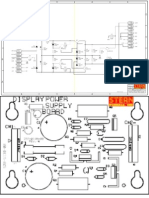

The transformer panel is the origin

of all power to the game. The line

filter, on-off switch, primary fuse

and line cord are also vital parts

of the bottom board assembly but not

directly connected to it, The line

power is applied to two transformers

which create two main supply voltage

groups. The large transformer sup-

plies all the controlled and non-

controlled device voltages for lamps

and solenoids, and is protected by

fuses F4 through F8. The small

transformer supplies the voltages

that drive the electronic devices

in the game.

Fuses Fl through F3 protect each of

these voltages. The only cross be-

tween the two power supply groups

is the +24V DC from the large trans-

former, It is used by the A7 Sound/

Speech Power Supply Board and is

fused by F8,

The transformer panel also contains

the bridge rectifiers and filters

to produce the necessary unregulated

+DC voltages. ‘The unregulated +12V

DC is filtered by a 6800 mfd capa—

citor to reduce A.C. ripple. It is

then routed to the a2 Power Supply

Board to produce the +5V DC logic

supply.

Il. POWER DISTRIBUTION

1 COWTROL BOARD

+s0v 06

4 b¢T DISPLAYS

STATUS UISPLAY

STATUS DISPLAY

AuyaYS Re-A0QUST +5eDC POT.

en MOUING GARE TOA EW

Lack

Ds1-LED MnscATES +Lavpe, tepUT

Bote INDEEATES +64ne UTP

TEs. LED's INpTOMTE WOLTAGE

PRESENS, SUT ADT NECESSARILY

CORRECT

OV AC RETURN

“$80 DG OFFSET

cova.

TRANSFORMER PANEL

FIGURE 3.

POWER SUPPLY

The A2J1 connector, carries an un-

regulated +12V DC and a 60V AC sup-

ply for power supply regulation.

It also contains three outputs:

+5V DC logic for the Sound/Speech

Board and +5V DC and +8V DC offset

voltages for the status and player

displays. The +5V DC. offset is the

same as the logic +5V DC supply.

The +8V DC offset is pulled off of

the +12V DC input by zener diode

CR7 through resistor R10. The off-

set voltages return to center taps

on the small transformer's 3V AC

and SV AC display filament supplies.

The A2J2 connector carries the +5V

DC logic supply to the Al Control

Board. The unregulated +12v DC

from A2J1-1 is applied to the col-

lector of Q3, an emitter-follower

pass transistor. The regulation

for the base of the transistor is

provided through an IC regulator,

UA723CN. The voltage output level

is established at a non-inverting

input, pin 5, depending on the ad-

justment of the reference voltage

through pin 6 and the potentiome-

ter. Current regulation is sensed

through R8, R9 and R12 at pins 2

and 3. Voltage stability is reg-

ulated at the inverting input pin

4 through R13.

The outputs of A2J3 are the display

The 60V AC is rec-

tified by bridge rectifier OR1

through CR4 and is filtered by ca-

pacitor C1.

drive voltages.

It is regulated by ze~

ner diode CR5, setting the voltage

level at the base of Q1. The +63V

DC output of Qi is tied to the base

of Q2.

across R4 will turn Q2 on or off to

The +42V

DC is generated from the +60V DC by

zener diode CR6 and R65.

Any fluctuations of current

regulate the base of Ql.

III. MODES OF OPERATION

A valuable tool that you can uti-

lize to troubleshoot the game sys-~

tem is the modes of operation and

the indicators they provide. In

the different modes, certain areas

of the game may or may not be used.

Understanding the correct operation

of the different modes can help to

break down a problem to the most

likely cause. For instance, in the

attract (game over) mode, the "Q"

relay de-energizes to cut off power

to portions of the game. If the

pop bumpers or the flippers are ac-

tive during the attract mode, there

is a short on the contacts or the

wiring of the "Q" relay.

A. INITIALIZATION

B. GAME OPERATION

GAME START

© FIRST PLAYER

© ADDITIONAL PLAYERS

C, GAME OVER

D, TILT AND SLAM

III. MODES OF OPERATION

INITIALIZATION

The Initialization Mode and its

power-up-to-attract sequence is de-

tailed above. The Initialization

Mode can tell a good deal of in-

formation about the game.

When the game is turned on, the

playfield, lightbox and coin chute

illumination lamps will turn on to

indicate there are no serious prob-

lems with the operational power

supplies. There should be a 103

msec. delay (for System 80A games)

before the coin-lockout coil ener~

gizes and the scoring and credit

displays light up, with any credits

remaining in memory displayed.

After five seconds, the High Game

to Date will be displayed in all

player displays, and the controlled

playboard lamps will strobe and

flash. This initialization sequence

indicated the Control Board and +5V

DC are functioning correctly and

there are no serious problems with

the Input/Output portion of the game

AFTER A JO3MSEC DELAY

HIGH GAME TO DATE SCORE WiLL FLASH AND CONTINUE UNTIL START OF GAME.

GAME ISNOW IN ATTRACT MODE. NOTE GAME ADAISTMENT SWITCHES #23 & #24 J

FIGURE 4.

III. MODES OF

OPERATION

The balls must be in the ball re-

turn trough to start a game.

1. Insert coins into coin chute.

a. Coin chute tune is played.

b. Total credits are displayed

in status display,

Press Credit Button to start game.

a. Credit tune is played.

b. Total credits displayed de-

crease by one.

All playfield features reset.

The first player score display

flashes 2 zeros.

When the ball is released to the

shooter, the playfield-controlled

lamps flash.

FIRST PLAYER

1, First player's score display

flashes two zeros.

2. The other player's displays are

now blank.

3. A "1" appears on the ball-in-

play display.

4. When the ball enters the outhole,

any bonus earned is scored.

ADDITIONAL PLAYERS

1. Additional players are indicated

by 2 zeros (not flashing) in each

corresponding player's display.

2, after the maximum number of

players are added, or no more

credits remain, the Credit Button

has no effect.

3. Additional players can be added

anytime the first player's ball

is still in play. If the Credit

Button is pressed after the first

player's first ball has entered

the outhole, all players’ scores

will be erased with the first

player's score display showing

a flashing zerc, indicating a

new game only for the first player.

10

OPERATION

GAME OVER

1, When the last ball enters the

outhole, the GAME OVER lamp con-

tinually flashes,

A random number appears in the

ball-in-play display. If this

number matches the last two

digits in any player's score, a

replay (dependent on Switch #27)

is awarded.

HIGH GAME TO DATE is periodically

flashed in all players score dis-

plays. When a score higher than

HIGH GAME TO DATE is achieved,

an award (dependent on Switches

#23 and #24) is given.

All of the target banks will reset.

2.

4,

TILT MODE

1, Tilting the game results in a

loss of ball in play.

When the game is tilted, all the

playfield lamps go off.

All accumulated bonus and bonus

multipliers are lost,

2.

3.

SLAM MODE

1. If the normally closed slam

switch (located inside front

door) is opened, the entire game

is ended for all players.

The GAME OVER lamp comes on,

The entire switch matrix is in-

active for three seconds.

All coins will be rejected if

dropped into eny coin chute

during the three-second delay.

if the match feature exists

(dependent on Switch #26), a

replay can be won even if the

game is slammed,

Game returns to the attract mode.

FRONT

DOOR

CONTROL

‘BOARD

At

88-10

GND

FIGURE 5.

Iv.

An electronic pinball machine is

operated and played through the use

of controlled devices. The con-

trolled devices are the majority of

components in a game creating all

of the input and output extensions

of the Al Control Board.

vices are the interface between the

player and the Control Board com-

These de-

puter that allows an assembly of

1.C. components and programming to

create a fast, interacting game for

the player.

CONTROLLED DEVICES

The controlled devices within a

game consist of lamps, relays, so-

lenoids, switches, displays and

The following chapter ex-

amines each area of control and its

specific devices.

the theories of how each type of

device is controlled, the signals

used to generate control, and how

sounds.

It will focus on

to use the Self-Test and trouble-

shoot in each category of controlled

devices.

A. CONTROLLED LAMPS

B. CONTROLLED SOLENOIDS

C. SOLENOID OPERATION

D. NON-CONTROLLED SOLENOIDS

E. SWITCH MATRIX

F, DISPLAYS

G, SOUND/SPEECH

a

IV, CONTROLLED DEVICES

SELF-TEST in each game manual along with any

special notes. All bookkeeping in-

The Self-Test contained in the Con— formation is checked against itself

trol Board includes four steps that to make sure it is correct. If any

will exercise all Input/Output por- steps in the bookkeeping portion

tions of the game and one step that display flashing information, the

will exercise all memory devices on data may be invalid.

the board.

Press SELF/TEST button on front coor Credit

Each test will be detailed in the ‘espa sous read “00” yer sore plays soa

following pages, but the specific

devices that are tested in each game oO Press mee

can be found in the individual game O Paves | ceeoireurron

surton

manuals. Points to remember are:

After a test is finished, each test

can be repeated by pressing the re-

play button on the front door; if

the replay or Self-Test buttons are

not pressed within 20 seconds after

[STEP #7—SOLENOID TEST, SOUND TEST, AND

a test, the game will return to the ‘OPERATOR SWATCH TEST

attract mode.

The bookkeeping portion of the test

can be bypassed if dealing with a

service-related problem. Press the

STEP 18—SWATCH TEST: At switches in te

swten matrx are specced. AI swecres open "99"

wl be displayed. Ie or more are cased, tek

‘signed number wi be asplayed.

Self-Test button to enter the test

mode. Next, press the replay but-

ton on the front door and Step 16 Serene ane

will appear in the credit display. sero Era ri are ejuencest

to

In the Self-Test /Bookkeeping Mode,

‘STEP 20—MEMORY TEST: Each contol board

one can use either portion to check By doe tages hy ee dah

eed umber doplayed in Payer

the Control Board and game opera- Number ore Won we OK 991% depayed Come

tion. ‘The bookkeeping portion is ‘rom check sum daplayed in Payer # 2 depey.

all steps from 1 through 15, and

Tore eT

each is a record of a particular 3] Wart 89 seconds

Dun power eton

function or event in the game that 6) Open slam sth

Chose sont

is important to an operator, The

individual functions are detailed FIGURE 6.

12

IV. CONTROLLED DEVICES

DRIVER BOARD

The A3 Driver Board consists of all

necessary circuitry to interface

the Control Board to the playfield.

It contains three types of driver

circuits; lamps, solenoids, and

sound signals, These circuits pro-

vide four sound enable signals and

61 individual transistor outputs

for both low current and high cur-

rent applications.

The Self-Test Steps 16 and 17 will

exercise all Driver Board outputs

to the playboard. Step 16 will

pulse the "Q", "T", and Coin Lock-

out relays twice each, and then

sequentially strobe all Controlled

Lamps on the playboard and in the

lightbox. All the Controlled Lamps

ee

26043 (6 AMP)

tw Daruineton —_]

used in a particular game will be

turned on or off within 7 to 10 sec-

onds and then cycle through again.

This cyclo will be repeated about

15 times within the 90-second test

period, allowing each lamp to be

turned on or off about 15 times for

testing (cycle time and number of

cycles depends on the particular

game).

Step 17 of the Self-Test will pulse

all Controlled Solenoids once, in-

cluding any solenoids driven through

the Controlled Lamp circuitry. The

test will then pulse each of the

Sound Enable lines once, and the

Operator Adjustable Option switch

settings will be displayed in hexa-

decimal format in the First and

Second Player displays,

EBC

MPs-At3 (172 AM

NPN DARLINGT

JoRIVES ONE Lan

i

We

c io’ Ee .

vara Higa:

13

IV. CONTROLLED DEVICES

PLAYFIELD LAM

‘ONLY (NORMALLY) >=

BLL LAMPS ARE 33441

a7 way Be suBstiTul

FIGURE 8.

CONTROLLED LAMPS

The circuitry of the Controlled

Lamp section provides for the con-

trol of 52 individual transistors

through the use of only 16 signal

lines from the Control Board. Four

of these signals are Lamp Data (LD)

lines, each of which is applied to

all 12 of the 74175 D-type Flip-

Flops on the board, The remaining

12 signal lines are the Data Strobe

(DS) lines, one each for the clock

input (or output enable) connection

on each of the 12 1.C.'s. When a

DS line pulses high, any high sig-

nals at the LD inputs to that I,C.

will be Flipped to the output gates,

14

turning on one or more of the four

output transistors.

The circuit for a typical lamp is

shown in its entirety, including

the Flip-Flop, the transistor, and

all the signals required to turn

Note that the

positive DC output of the bridge

on a given lamp.

rectifier is connected directly to

the bulb through a set of normally

relay.

All Controlled Lamps in the game

closed contacts on the "T"

are electrically “hot” and the cir-

cuit path to ground is completed

through the transistor when it is

turned on.

IV. CONTROLLED DEVICES

PROBLEM

ONE CONTROLLED LAMP

ALWAYS OFF

CHANGE

GAME PROM

JUMPER TRANSISTOR

COLLECTOR

TO GROUND

CHECK FOR;

BROKEN

WIRES,

BAD LAMP

SOCKET

CHECK TRANSISTOR

BASE FOR +

REPLACE

DRIVER

TRANSISTOR

VOLTAGE

PRESENT?

REPLACE FLIP-FLOP CHIP}

ON DRIVER BOARD

FIGURE 9.

15

PROBLEM

ONE CONTROLLED LAMP

ALWAYS ON

GO TO SELF-TEST #16

CHECK BASE VOLTAGE

oF

DRIVER TRANSISTOR

REPLACE FLIP-FLOP CHIP]

ON DRIVER BOARD

CONTROLLED LAMPS

CHANGE

GAME PROM

REPLACE

DRIVER

TRANSISTOR

IV. CONTROLLED DEVICES

CONTROL. BOARD

v4

(oF 9)

DRIVER BOARD:

AS

TRANSFORMER PANEL

5 AMP

sy ac

60 Hy

UMPER WIRE

"TO GROUND

INd004

FIGURE 10.

CONTROLLED SOLENOIDS

The Solenoid Driver section of the

board drives nine outputs. Six of

these outputs are single transis—

tors which receive a positive pulse

from the Control Board. A positive

voltage above +1.4V DC applied to

the base of the transistor will turn

on the transistor, completing the

circuit path from the collector to

the emitter,energizing the solenoid.

The other three Solenoid Driver out-

puts are designed for high current

applications by using transistor

pairs. The positive pulse from the

Control Board turns on the first

transistor, a MPS-U45, causing the

16

+5V

the

the

the high current transistor, a

2N3055, which will then turn on and

energize the solenoid. Solenoids

1, 8, and 9 are isolated by 1N4148

diodes, to protect the Control

Board from switching transient or

feedback voltages.

DC from the collector to pull

emitter high. The emitter of

MPS-U45 is tied to the base of

The Solenoid Driver outputs will be

assigned to the necessary devices

according to the needs of the game

and the programmer. However, Sole-

noid 8 is always assigned to the

cabinet knocker coil, and Solenoid

9 is always dedicated to the Out-

hole coil.

IV. CONTROLLED DEVICES

s2av0e

tuaoos

CATHODE 1ANP_400PIV

MINA

+2ay oc RATING

BACK EMF

7+ PROBLEMS!

ALL SOLENOIDS INOPERATIVE

1) szavoc FUSE

- 2) s2aype BRIDGE

2) oR T ReLay

GROUND

ENERGIZED

+20v oe

PULSE JUMPS CONT~

VOLTS — ACTS OR SHORTS

TRANSISTOR (MAY

BE SEVERAL THOU

‘SAND VOLTS).

7Me

yours

ie

N o ve

rive

ROUND

‘SWITCH OPENS

WITH OfODE ON COM

FIGURE

“B\ 4

aN

f

ROUND

SWITCH OPENS

NO DIODE ON COIL

eave

La

i.

SOLENOID OPERATION

Any current flow through a wire

will produce a magnetic field

around that wire. If the wire is

17

tightly wound many times around a

core (hollow or iron) then a large

magnetic field is produced. This

magnetic field is then used to

pull in a solenoid plunger or to

magnetize an iron core which pulls

in a relay armature.

When a D.C. current (EMF or Elec-

tro Motive Force) is first turned

on to a coil, energy is absorbed

to create a magnetic field which

is called Back EMP.

When the current is turned off,

energy still exists in the magnetic

field which collapses, releasing

energy back to the circuit. ‘The

reverse current normally cannot

flow anywhere when the switch is

opened. The field collapses never-

theless, and the lack of current

flow is made up for by the genera~

tion of a very large voltage. The

reverse voltage creates a new mag-

netic field in the reverse direc~

tion and this process continues

for several cycles until the energy

is dissapated by the coil resistance.

The purpose of the diode across the

coil is to dissapate these voltage

spikes. When the current is turned

on, the diode is reverse biased

and no current flows through it.

As the current is turned off and

the reverse voltage is generated,

the diode becomes forward biased,

and the resistance of the diode

absorbs most of these voltage spikes.

iv.

NON-CONTROLLED SOLENOIDS

The Non-Controlled Solenoids are

the coils in a game that are direct

switch activated. They are not

electrically "hot" like the Con-

trolled Solenoids, rather the +24V

DC is sent to them only when the

switch for that coil is closed.

The physical movement of the plun-

ger will then pull or push close

a separate scoring switch on the

Switch Matrix.

The microprocessor does have some

control over all these devices in

the form of two relays which will

switch voltages on or off as needed.

The "Q", or Game Over, relay will

energize when a game is started

and close a set of normally open

contacts to switch the voltage up

to the playfield, The "I", or

Tilt, relay will open a number of

normally closed contacts to remove

the playfield voltages.

The Pop Bumpers are driven by in-

dividual transistors on separate

printed circuit boards mounted un-

der the playfield. The Pop Bumper

Driver Board has an RC time con-

stant circuit setting the output

pulse time from a 74121 Flip-Flop

when the switch input is pulled

low. This output pulse is inverted

and then turns on a 2N6057 high

current NPN transistor which in-

sures a strong complete travel of

the kicker ring attached to the

Pop Bumper plunger.

18

CONTROLLED DEVICES

Zz "SANEREIBe NB TERURRONER”

2 pot A

mitcuE “ey 06

‘ounce

err ripper

(sam Se RET

av ao Rerun

5 pe

a City

FIGURE 12.

TILT RELAY (1)

GAME OVER RELAY(Q) FLIPPER. aU

1

‘SIDE OF CABINET

+28v 06

GROUND

FIGURE 13.

IV, CONTROLLED DEVICES

pane

Ms

AC

x

PIN

fp Ea

ro sLMINATE

FIGURE 14

Strobes: Fight atgnals froo tne PB Right rete

port of C4, 9 6552-1 RIOT 1.c., which

are inverted by two 7404 1.C."8,

enipa 721 and 212. (Control Board

devices are exanined in Saotion V.)

he U4 RIOT Tc.

SWITCH MATRIX

The switch matrix of a pinball game

is a network of switches that allow

the Control Board to monitor the

conditions of 64 switch positions

while using 16 strobe and return

lines. All switches in the matrix

are normally open. Eight of the

16 signal lines from the Al Control

Board are called strobe (STR) lines.

The remaining eight are called re~

turn (RIN) lines.

This is the operation of a single

19

fone input each, of = two-input AND

ate 7400 T-C. The two AND eat

cchipa 213 and Zi4,

return intormtion to the PA port of

Lines tied to

Operator Adjustable Option seit

Four eignata froe chip 218, » 7432

twociaput OR gate, are applied to

‘aight DID avttcnes exch, with diodes

CR through CRS providing ewiteh

ssolation. The othor input of the

tro-input MAND gatos, chips 213 and

244, will read four DIP eritenes cach.

strobe and single return line, The

Al Control Board places a negative

pulse oY on the STR 9 line.

The Control Board examines the

RTN 9 line and detects no logic

level change (RIN 9 remains at a

logic high, +5V DC). So, no action

by the Control Board is taken.

ever, close the switch and a com-

How-

plete path for the negative pulse

from STR 9 to RTN 9 is made. RIN 9

is pulled to a logic low “Li”

for the pulse duration.

‘The Control Board now responds to

the RIN 9 signal change.

IV, CONTROLLED DEVICES

FIGURE 15.

Figure 15 illustrates the complete

operation of the STR 9 line, con—

necting to eight switches. The

other end of each switch is attached

to a different return line. When

STR @ pulses low, eight switches

are "Looked at" by the Control Board

at the return line inputs. lere,

switches 91, 92, 95 and 97 are

closed. RIN lines 1, 2, 5 and 7

will change their state to a logic

ow. The Control Board will ac-

cept all return line data simul-

taneously, store it, and then pro-

cess each data bit (return line

information) in programmed sequence.

Looking at a Switch Matrix Schema-

tic Diagram in its entirety will

show that eight switches are at-

tached to each strobe line and

each return line, This makes a

total of 64 possible switch posi-

tions.

switch is assigned a two-digit num-

ber, as in Figure 15. The left

digit designates the strobe number

Also observe that each

and the right digit designates the

return line number. Therefore,

20

switch number 23 is connected from

STR 2 to RIN 3, and so on.

STROBE SEQUENCING

Strobe lines are not pulsed at the

same time, Each strobe Tine is

sequentially pulsed from STR to

STR 7 (See Figure 16), All strobe

lines are pulsed fast enough so

that no switch closures anywhere

in the matrix are missed. All

switches are examined by the Con-

trol Board in 10 milliseconds. &

strobe pulse width is 1.25 milli-

seconds. Switch debounce is han-

dled by the system software. No

debounce capacitors across switches

are found on Gottlieb's pinball games.

STROBES

°

SHIOMS -> [+ 1.25Ms,

FIGURE 16.

Iv.

(agete Lowy San ZE

FIGURE 174,

ISOLATION DIODES

Switch matrix isolation diodes give the

matrix individual integrity for each

switch, If all diodes are removed as

shown in Figure 17A, false switch clos-

ures will be sensed by the Control Board.

The illustration shows switches 42, 52,

and 53 closed. A conductive path is

made not only for RTN 2, but for RTN 3

as well. When STR 4 is pulsed, RTN 2

and RIN 8 lines will both change logic

stat However, notice switch 43. It

da open, and yet the Control Board will

process « changed logic state as if it

If a coin switch was as-

were closed.

signed to the 43 switch position,a credit

was just given without inserting a coin.

aznone «

Sn hy

ncfune

FIGURE 173.

In Figure 17B, the diodes are placed

back inte the circuit. STR 4 pulses low,

but because the diode becomes reversed

biased, no completed circuit to RIN 3

is possible. With the diodes, no com-

bination of switch closures will cause

false signals.

21

CONTROLLED DEVICES

The diodes used by Gottlieb are 1N270

germanium type. Using silicon diodes

will not guarantee valid logic states

when a switch matrix employs a negative

strobe system. Do not replace these

germanium diodes with silicon type di-

odes, such as the 1N4148 or 1N4004 diodes.

Dependent on how a diode fails, several

Afferent symptoms could appear.

If a diode internally opens, the effect

will be isolated to that particular

switch. Closing the switch will have no

effect on game play, and Test #18 will

not display a matrix number.

FIGURE 18.

If a diode shorts, the effect becomes

more serious. Figure 18 demonstrates

that the game loses its ewitch isolation,

and that the return lines may detect

false signals. This will cause the game

to malfunction and may lead the tech-

njecian to believe that a bid Control

Board or Power Supply is the cause. Note

that @ reversed diode may generate the

same problem as a shorted diode.

‘The Control Board will not respond cor-

rectly if particular strobe or return

line is either open or shorted from one

to another. A short to ground or another

voltage source on a strobe or return line

would also make the Control Board respond

incorrectly. In these cases, switches

common to the bad strobe or return line

will all be affected.

IV. CONTROLLED DEVICES

EVEN DIGIT

DISPLAY

a

Four pisiT

DISPLAY

a

i

t

' ED

i rae we

| | [Correct [rayne savoe

| 1 (eee Tesow ne [aay

FIGURE 19.

DISPLAYS power, The constant variation of

The theory of operation of a fluor-

escent digit display tube is simi-

lar to the vacuum tube theory.

The filament acts as the cathode.

When the filament is charged with

electricity and heated, electrons

are emitted. if a more positive

voltage is applied to the anode

and grid at this time, electrons

emitted from the filament are

drawn into the anode through the

grid. These electrons striking

the anode will excite the fluor-

escent substance on the anode and

emit light. If the anode and grid

voltages are dropped to zero or

negative, no electrons will be

drawn to the anode and no light

will be emitted.

The filament, which acts as a di-

rect heated cathode, works on AC

22

the AC voltage provides uniform

brightness across the face of the

display and also assures that the

filament wire will not get over-

heated and break or wear at any

point. To cut off the flow of

electrons to the grid and anode,

a negative voltage (in reference

to the filament) must be applied

to the grid or anode. Since the

filament AC voltage swings nega-

tive every half-cycle, just

grounding the grid would still

allow electrons to flow every

half-cycle. For this reason, a

low +DC voltage is applied to the

filament in addition to the AC

voltage. On the negative half-

cycle the filament will still have

a positive potential above the

This is

the purpose of the offset vol-

tages for the displays.

grounded grid or anode.

IV. CONTROLLED DEVICES

The 7-digit display filament off-

set voltage is +8V DC generated

by the +12V DC input to the A2

power supply board by zener diode

CRT and R10, The 4-digit display

filament offset voltage is +5v DC,

which is the same as the logic

supply voltage. The +8V DC is

applied to the center tap of the

5V AC winding on the small trans-

former. The +5V DC is applied to

the center tap of the 3V AC wind-

ing on the small transformer. The

two pairs of AC offset voltages

then go up to the displays in the

lightbox via connector A12J4.

‘The display control signals ori-~

ginate at the Al control board

and are wired directly to the dis~

plays. ‘There are 16 digit con-

trol lines and three groups of 8

segment lines that are common

wired to three groups of displays.

The common wiring is actually a

combination of cross wiring be~

tween digits, segments, and displays.

The digit lines are always sequen-

tially strobed, so only one line

at a time will be high. The pro~

cessor will fill each segment

group with the data or blanking

information that is necessary for

each digit.

For instance, if there is a first

and second player up, then the

"B" segment group will always be

23

filled with blanking information.

So when the digits are strobed

for the 3rd and 4th player, the

segments will be low, and the dis-

play will be blank. If 1st player

only is up, then the processor

will fill the "A" group with blank-

ing information when the digits

D7 through D13 are high.

croprocessor scans each digit 61

The mi-

times a second so displayed data

will look constant to the eye.

The configuration of our display

signal wiring is as follows:

Group

Segments: A

Player Display

1st & 2nd player

B 3rd & 4th player

C Status (& Bonus if

present)

Digits: Di - Dé

& DIS

1st & Srd player

(& Bonus if present)

D7 -D12 2nd & 4th player

& DIS

D13-D16 Status

1. Segment problems will be shared

by displays of Players 1 & 2

and 3 & 4,

2. Digit problems will be shared

by displays of Players 1 & 3

and 2 & 4,

3. One bad display may cause other

displays to appear defective;

however, this may not be the

case. Disconnect one display

at a time and observe what hap-

pens to the other displays.

CAUTION: Do not plug or unplug

displays with the power on.

Damage to the control board will

result.

IV. CONTROLLED DEVICES

CONTROL BOARD

Al

a

A

—

(2) =

BOHM SW 4 C= yxy

SPEAKERS, VOLUME y

CONTROL

POT, 100 OHM

FROM A3u2-9 —m—!

FIGURE

IN JUMPER TO GROUND (TYP.)

DRIVER BOARD

AS

a

20.

SOUND/SPEECH

POWER SOURCE

Four input voltages are required

for proper operation of the Sound/

Speech Board. They are:

1, #30V DC - used for the LM379

Amplifier

2, +12V DC - used for the DAC's,

the SCO1A and the

LM741's.

3. -12V DC - used for the DAC's

and the LM741's.

4, +8V DC - used for the 6502 (CPU),

the 6532 and all TTL.

The #30, +12, and -12 DC voltages

are supplied to the A6J1 connector

from the A7 Auxilliary Power Supply.

24

The +5V DC originates at the AZ

Power Supply.

SIGNAL SOURCE

The binary sound information ori~

ginates in the A1 Control Board and

is then sent to the A3 Driver Board

to be inverted.

S1, S2, $4 and $8 go through 213,

a 7404 hex inverter and are then

output to the Sound/Speech Board

through connector A3J5. The Sound/

Speech Board also receives a signal

from Q10 (on the Driver Board)

which is part of the Lamp Circuitry,

and is output as $16 through con-

nector A3J2.

The four signals,

Vv. MEMORY

A, MICROPROCESSOR

Gottlieb's System 80/80A Control

Boards are built around a Rockwell

6502 microprocessor which operates

on a single +5V DC supply voltage.

A brief description of each LST

component follows.

The Rockwell 6502 is an 8-bit micro-

processor which has many positive

features: single supply

full 16-bit address bus,

of interrupt priorities,

phase clock which is generated on—

voltage,

two levels

and a two-

board.

‘The microprocessor receives instruc-

tions off the data bus from peri-

pheral devices; RAM, ROM, and PROM.

It is an 8-bit bus, DBO-DB7, with

the data being transferred while

the 92 clock is high. Addressing

for all external memory is output

trom the microprocessor on the 16

address bus lines, ABO-AB15. In

this particular application, ABI4

and ABI5 are not used. ABO through

AB6 are applied directly to the

address bus. AB7 through AB13 are

applied to the bus, however they are

also combined through various gat-

ing combinations for PROM select,

RAM select, RIOT enable, etc.

These lines are buffered by 27 and

Z10 since they are capable of

driving only one TTL load each.

25

DEVICES

vss |_ RES

RDY L_ 2(OUT)

1 (OUT) | so

ro }~ be (IN)

NC. | Nc,

NMI | NC.

SYNC |_ RW

vec |. DBO

ABO L_ 0B!

ABI | oB2

AB2 | 0B3

ABS |. DB4

AB4 _| 13 28} DBS

ABs | 14 27 _ Be

Age | 15 26 |_ 0B7

ABT 16 25 | ABIS

ABB | 17 24|_ apie

Ago _| 18 23) ABI3

AB10 _| 19 22! apie

ABI 20 at F VSS:

FIGURE 21.

AQ TO A15— 16 address lines, designated in

hexadecimal notation in 4 groups

of 4lines,

DOTOD7 —8 data lines—bi-directional—

designated in hex in 2 groups of 4

lines.

RES

iRQ — Interrupt request—high for normal

program sequence—low when

one of the RIOT's requests an in-

terrupt

— Read write line. High to read, low

to write. Instructs RAM and RIOT's

whether data on the bus is being

written or being read.

— Clock circuit. G0 is input from the

crystal. $2 is output to RIOTs.

— Low to reset system, high to run.

go-d2

MEMORY

The microprocessor receives an ap—

proximately .85MHz clock signal on

pin 37, @o(IN) from 22, pin 9. The

clock signal is converted into a

two-phase system clock internally

and is output on pin 39, 99(OUT)

to other devices which require sys-

tem timing.

The reset line, RES, pin 40, is

held low when power is first applied.

Once Vgcreaches a level determined

by the reset hardware, RES goes high

and remains high as long as power

remains on. This reset insures

that as the microprocessor starts

to operate the program counter is

initialized to zero, and execution

of the program begins at the proper

address.

Interrupt request, TRQ, pin 4, re-

ceives low going signals from the

three RIOT devices when an inter-

rupt needs to be serviced. The mi-

croprocessor then completes its

current instruction and goes di-

rectly to the designated interrupt

routine. ‘The non-maskable inter-

rupt, NMI, is not used and is tied

high through R10.

Read/Write control, pin 34, deter-

mines whether data on the bus is

read from RAM or written into RAM.

This signal is high to read, low

to write, and goes to the three

RIOT devices and the bookkeeping RAM.

26

DEVICES

B. RAM I/O TIMER

All input-output functions of the

microprocessor are handled by R6532

RAM INPUT-OUTPUT TIMER devices

(RIOT). 8-

bit bidirectional data ports which

can be used to transmit data from

the microprocessor system to exter-

Each RIOT contains two

nal circuitry or to receive data

from external circuits and enter it

The 1/0

lines are directly compatible with

TTL or CMOS devices. Each line is

capable of driving one TTL load.

into the microprocessor.

Each RIOT also contains 1024 bits

of RAM memory in a 128 x 8 config-

uration. Addressing is accomplished

through the seven address lines, AO

to AG. RS, pin 36, must be low for

the RAM section to be enabled. When

the READ/WRITE line, pin 35, is

high, the RAM is in the read mode.

When R/W is low, the RAM is in the

write mode.

Two chip select lines CS1 and C52

are provided as enable lines for

the RIOT. CS1 must be high and

SZ must be low for the RIOT to be

enabled. A reset input, RES, pin

34, must be held low as the system

is initialized to zero all internal

registers and to prevent false data

from being transferred out of the

Once the

microprocessor has initialized, the

RES line should go high and remain high.

system during power up.

Vv. MEMORY

=

“q

a

sq

“q

“q

“U

nor

ms |

ver

mac]

mq

oso

vod]

mer

wee

mq

=

(|

wo

FIGURE 22.

080

bet

82

sof jome

es

cs1-CS2 —Chip select lines. CS1

select, CS2 low to select.

RS —RAM select—low to select the

RAM section of the RIOT.

PBO-PB7 —A group of 8 lines which may be

used as inouts or outputs from the

system, PB ports are capable of

direct drive of Darlington Tran-

sistors.

PAO-PA7 —A second group of 8 lines for

inputfoutput uses. PA7 can be

used as an edge detecting input

high to

that generates an interrupt

A0-A6 — — Address bus.

DOD? — Data bus.

27

DEVICES

The interrupt request line, IRQ, pin

25, is normally high and goes low

whenever the RIOT wants to transmit

an interrupt to the microprocessor.

System timing is maintained by the

92 clock which enters the RIOT at

pin 39, All data transfers on the

bus take place when 92 is high.

One RIOT, U5, uses 1/0 port PA7 as

an edge triggered interrupt for the

slam switch input. This gives the

slam switch a higher priority than

other input functions,

C. BACKGROUND ROM (2332A)

Two ROMs, U2 and U3, each contain

4K bytes of memory in a 4K x 8 con-

figuration.

memory and does not change from

game to game.

ceived from the microprocessor and

data is read directly onto the data

bus. The S2 input, pin 21, is used

to select which of the two ROMs is

This is "background"

Addressing is re~

enabled at any given time.

FIGURE 23.

AQ-A11 — 12address lines.

DOD? — 8data lines.

$1-S2__—Chip select lines—both high to

enable chip.

D. BOOKEEPING RAM

Data which must be retained when

the game is turned off is stored in

25, a P5101 CMOS RAM. The 5101 is

a 256 x 4 RAM with low power con-

sumption when the CE2 line, pin 17

is low. Since the 5101 is a 4-bit

RAM, it is connected only to the

lower four data bus lines, DBO

through DB3.

directly off the address bus from

Addressing is provided

the microprocessor.

ag =H Yee

ad? aba

ada ahi ww

ads wb a

as qs 2D oo

ade wB en

aq wB 00

ow q #4

a de +B 20

we, dw Bb 95

md 2h om

FIGURE 24.

CE —Chip enable—low to enable

RAM—does not disable input and

output buffers.

CE2 — —Chip enable—low to disable RAM

and place it in low power standby.

op Output disable—places outputs in

3 state configuration “OF!

high to disable.

RW — Read/Write control, High to read

RAM—low to write into RAM

OI-1-DI-4 — Data in lines 1 thru 4

DO-1-D0-4 — Data out fines 1 thru 4,

The data in and data out lines are

tied together in this system and the

RIW and OD lines are used to con-

trol data direction flow.

AOQ-A7 — Address bus

28

MEMORY DEVICES

E. PROM

The other type of memory used is

the programmable ROM (PROM) which

is changed from game to game. The

PROM is a 2K byte device with a 2K

x 8 configuration.

data information is transferred on

the microprocessor bus system.

Chip Enable, CE at pin 18, is used

as the PROM SELECT. As the 8/W

line is pulled high, then the Out-

put Enable, OE at pin 20, will be

pulled low so the data can be read

out of the PROM onto the data bus.

Address and

FIGURE 25.

Chip Enable ~ low to enable

ROM ~ does not enable data

outputs.

Output Enable - low to en-

able data outputs after the

address has been selected.

Data bus.

Address bus.

00-07 —

AO-A10—

The remaining circuitry on the con-

trol board is standard TTL and cuos.

It is used primarily to buffer all

inputs and outputs from the micro-

processor to the external areas of

the game.

ternal failures in the game from

damaging any of the LSI devices.

This prevents most ex-

Vv. MEMORY DEVICES

F, CONTROL BOARD

Gottlieb has used three generations

of the System 80/80A Control Board.

The boards can be identified by the

board assembly detail number in the

lower left corner of the board un-

derneath the DIP switches (See Fig—

ure 26).

FIGURE 26.

The first generation of Control

Boards used two HM7641 PROMs and

can be recognized by the detail

number following the assembly num-

The number reads:

DET. PBO3-D102-001 or

DET. PBO3-D102-002

REV. A or REV. B

ber.

This board was used with the first

System 80 game, Spiderman, and in

Panthera, Circus, Counterforce,

and Star Race. If there are four

jumper wires and two traces cut on

the non-component side of the board,

then it has been modified to be

used with the one PROM system.

‘The first single PROM Control Board

used a 2K x 8 2716 EPROM. The sec~

ond PROM socket was left in the

board, but the trace changes left

29

it unusable. The detail numbers are:

DETAIL PBO3-D107-001 or

DETAIL PBO3-D107-003

This Control Board was used with all

remaining System 80 games from James

Bond through Haunted House.

Beginning with the first System 804

game, Caveman, the Control Board

incorporated four changes:

* The unused PROM 2 socket was re-

moved.

* The Program Background ROMs at

locations U2 and U3 were rewritten

for our improved Self-Test, im-

proved Option Switch settings,

and new Seven Digit Display.

* The two ROMs at U2 and U3 were

socketed.

* The Control Board assembly number

was removed and replaced with the

board's part number, D-20869.

By socketing the two ROMs the Con-

trol Board can be used with either

System 80 or System 80A one PROM

games, by simply using the appro-

priate set of ROM memory chips.

Refer to your specific game manual

to determine the system type.

However, for testing purposes, any

System 80/80A Control Board will

power-up normally in any Gottlieb

System 80/80A game. Also, any Con-

trol Board will respond to the Self-

Test switch, the coin switches, the

Replay button, and the Tilt and

Slam switches. All other switches

will differ from game to game.

V. MEMORY DEVICES

SYSTEM 80/80A MEMORY

ROM

Read Only Memory

MICROPROCESSOR RAM

Random Access Memory

BOOKKEEPING

MEMORY. GAME PROM

E Sas 3

vn aisnour sere

Eg A ot (ur ge

a =

needs +o

XS

5 © foil oh ok ths a

’ SS rey

wes a 5 oF ae

LH a i =

i 4 * so

| re

GAME ADJUSTMENT SWITCHES

FIGURE 27.

30

VI.

A, INTRODUCTION

The Gottlieb video graphics genera-

tor system consists of the game

printed circuit board, inputs and

outputs to switches, speakers, and

lamps, the video monitor, the power

input and the transformer panel.

Each of these devices has specific

functions which can be defined as

follows.

‘The 115V AC input and transformer

panel receive the line voltage and

break it down into the unregulated

AC supplies to the Power Supply

Assembly, and 115V AC isolated for

the monitor and fluorescent illumi-

nation. There are two Bridge rec-

tifiers on the panel to supply un-

regulated +5V DC for the Coin Door

lamps and an unregulated +11.5V DC

for the Logic Supply reference.

The video monitor is a Wells-Gardner

19" In-Line Color monitor providing

a high resolution color display

from the three color input signals

and horizontal and vertical syncro-

nization.

Inputs come from Coin switches 1 and

2, Self Test, and Control panel

switches. The outputs from the CPU

board control the coin meter, con~

32

VIDEO TROUBLESHOOTING

trol panel lamps, and the sound

codes to the Sound Speech Board.

There are also internal CPU Board

input and output functions used to

synchronize various portions of the

system.

The A3 printed circuit board is

the Power Supply Assembly which

provides the regulated DC voltages

to the electronics boards to control

the game. There are regulated DC

outputs of +5V DC, +30V DC, +12V DC,

-12V DC, and an unregulated +20V DC

for the coin meter.

The Sound/Speech Board contains it's

own semi-intelligeat processor,

RAM, and Sound ROM's, which receive

input sound codes from the Al CPU

Board and then outputs the appropri-

ate signals to it's internal ampli-

fier which directly drives the

speaker system.

The Interface Boards allows one

input port to interface to the track

ball or rotary encoder. This de-

vice will decode the player control

inputs into 8-bit binary information

for the CPU board to read. Also

after each read cycle the interface

board resets the output buffers to

logic 0.

VI.

The CPU/Video Board contains an

Inte], 8088 Central Processing Unit

(CPU) microprocessor, Memory, In-

put/Qutput Ports, and the Video

sub-system. The microprocessor

performs the logic functions of

accessing and using the system areas

mentioned above, according to the

game program, The Video sub-system

is a semi-independent Video-State

Machine generator, which is further

|

VIDEO TROUBLESHOOTING

sub-divided into three parts; A

separate System Clock to generate the

verticle, horizontal, enable and

syne lines; An “object oriented"

Foreground generator; And a "charac-

ter-oriented" Background generator.

The State machine address and data

lines also access separate Video

ROMs to generate the objects and

characters that the microprocessor

ROM program selects.

PU Loci BOARD

¢

POWER SUPPLY

“Assy

INTERFACE

BOARD

assy.

((OPTIONAE)

dh EARTH GROUND

ecu enouno

—— a)

FIGURE 28.

33

VI. VIDEO TROUBLESHOOTING

POWER SUPPLY SPECIFICATIONS

DESTINATION

OF VOLTAGE | VOLTAGE PROTECTION AND REGULATION

Sound/Speech| +30V DC |2 Amps fused for over-current protection. The

Board, reference for this circuit is a 1N5363B +30V DC

Audio Amp Zener controlling the base of an emitter

Supply follower pass transistor. The reference Volt-

age is a nominal 48V DC supplied from a bridge-

rectified, fused 35V AC input.

Sound/Speech| -12V DC |100 milliamps fused for over-current protection.

Board The plus and minus 12 volts supplies are the

igvoc |7812 and 7912 IC regulators respectively. Both

devices have a reference voltage of + and

-19.3V DC supplied from a bridge-rectified,

fused 15V AC input.

Senet or +4.5V DC |Rectified unfiltered voltage, fused for over-

Coin Chute current protection, taken directly off the

Lights bridge rectifier on transformer Panel.

Coin Meter | +20V DC |Full wave rectified unfiltered voltage, fused

for over-current protection. The AC Input for

the rectifiers is the 15V AC supply for #12V

above.

Monitor and |100V AC or|Isolated, fused AC voltage. supplied directly

Marquee 416V AC, |from the Transformer secondary on the bottom

6ORZ Panel.

Logic Board | +5V DC {Voltage adjustable. 5 Amps fused for over current!

Assy. protection and uses SCR "crowbar" over-voltage

protection, The +11V DC input is supplied from a

filtered, bridge rectified 9V AC on the

Transformer Bottom Panel.

34

TO Al LOGIC BOARD

+5v 00

GROUND LOGIC

VI. VIDEO TROUBLESHOOTING

A3 POWER SUPPLY BOARD

> +5v oc

‘ons

int RAR A

HT

3h

T

oo va

‘4

alee

[+11.6V DG 35V AC]

+IL5Y OC}

SND, IY AC GND]

GND, AUDIO GND

‘GND

35V AC RETURN]

TO TRANSFORMER

BOTTOM PANEL ie eT

‘AC INPUT

FIGURE 29.

35

TO AGut

‘SOUND /SPEECH

‘BOARD

LED'S INDICATE VOLTAGE

PRESENT AT INPUT, BUT

NOT NECESSARILY AT

OUTPUT OR CORRECT

D1l INDICATES APPROX-

IMATELY +5V DC OUTPUT

D25 INDICATES +48V DC

RECTIFIED 35V AC INPUT

D35_ INDICATES +19,3V DC

RECTIFIED 15V AC INPUT

D43_ INDICATES -19.3V DC

RECTIFIED 15V AC INPUT

SEE POWER SUPPLY

SPECIFICATIONS FOR

FUSE RATING AND

APPLICATION

VI. VIDEO TROUBLESHOOTING

LOGIC SUPPLY CIRCUIT DESCRIPTION

The basic configuration of the cir-

cuit is an common-base series pass

regulator with SCR crowbar over-

voltage protection.

for the base of the regulator

transistor is the TL431, an adjust~

able precision shunt regulator.

‘The regulator output voltage at the

cathode of this device is inversely

The reference

proportional to the difference be-

tween the voltage at its reference

pin and its internal 2.5V bandgap

reference.

A current amplifier is formed by the

two transistors, Ql1 and Q12. The

amplifiers voltage gain is fixed at

approximately double with the resis-

tor values shown. For a +5V DC out-

put, the voltage at the cathode of

the shunt regulator will be approx-

imately +3.5V DC and will change

little for all values of load

current.

The over-voltage protection circuit

uses a +5.6V DC Zener diode. If

the Zener diode senses enough cur-

rent to develop 1 volt across R18,

a 20 obm resistor, it will gate

the SCR shorting the transistor out-

put to ground,

Glee athe ne tos yg eRBRGT

he oh ‘

FIGURE 30.

VI. VIDEO

— a= _

PL snsy 06 Fu serse, ~

i v toon,

2<+ iw

i fie [se

: lout

: 16v

' ull

‘ TL a3! +

70-82 -

set

2a 58.

pe lcs scour

Fal

aw

22

2s

wvs752

P31 258

2

931

45V AC CENTER TAP + ¢19.3v 06 i"

s

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5823)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Gottlieb System 80 ServicemanualDocument64 pagesGottlieb System 80 Servicemanualapi-3713719No ratings yet

- Gottlieb System 80 Bench Test ProceduresDocument9 pagesGottlieb System 80 Bench Test Proceduresapi-3713719No ratings yet

- GamePlan Model 130 PartsDocument30 pagesGamePlan Model 130 Partsapi-3713719No ratings yet

- GamePlan ModelsDocument3 pagesGamePlan Modelsapi-3713719No ratings yet

- GamePlan Coney Island ManualDocument5 pagesGamePlan Coney Island Manualapi-3713719No ratings yet

- Gameplan Andromeda Manual Model 850Document17 pagesGameplan Andromeda Manual Model 850api-3713719No ratings yet

- GamePlan Model 110 Service ManualDocument27 pagesGamePlan Model 110 Service Manualapi-3713719No ratings yet

- GamePlan Mpu2-Rev1Document2 pagesGamePlan Mpu2-Rev1api-3713719No ratings yet

- GamePlan Ssu1-2Document1 pageGamePlan Ssu1-2api-3713719No ratings yet

- Stern CPU Sound BDDocument9 pagesStern CPU Sound BDapi-3713719No ratings yet

- Stern Game SetUpDocument3 pagesStern Game SetUpapi-3713719No ratings yet

- Williams System 9 Pinball TroubleshootingDocument78 pagesWilliams System 9 Pinball Troubleshootingapi-3713719No ratings yet

- CN2 CN2 Key CN2 CN2 CN2 CN2 CN2Document3 pagesCN2 CN2 Key CN2 CN2 CN2 CN2 CN2api-3713719No ratings yet