Professional Documents

Culture Documents

Advanced Advanced Computer Computer Architecture Architecture

Advanced Advanced Computer Computer Architecture Architecture

Uploaded by

Sam Thui Sam ThuiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Advanced Advanced Computer Computer Architecture Architecture

Advanced Advanced Computer Computer Architecture Architecture

Uploaded by

Sam Thui Sam ThuiCopyright:

Available Formats

2/25/2013

1

BK

TP.HCM

2011

dce

ADVANCED ADVANCED COMPUTER COMPUTER

ARCHITECTURE ARCHITECTURE

Khoa Khoa hc v K thut My tnh

BM K thut My tnh

Trn Ngc Thnh

http://www.cse.hcmut.edu.vn/~tnthinh

2013, dce

2011

dce

Review of Instructions Set

Architecture

Review of Instructions Set

Architecture

Computer Architecture, Chapter 2

2

2/25/2013

2

2011

dce

Outline

3

Computer Architecture, Chapter 2

Instruction structure

ISA styles

Addressing modes

Analysis on instruction set

Case study: MIPS

2011

dce

Machine Instruction

4

Computer Architecture, Chapter 2

Computer can only understand binary values

The operation of a computer is defined by

predefined binary values called Instruction

2/25/2013

3

2011

dce

5

Computer Architecture, Chapter 1

instruction set

software

hardware

The Instruction Set

Instruction set: set of all instructions a processor

can perform

Interface between software and hardware

2011

dce

Instruction execution cycle

6

Computer Architecture, Chapter 2

Instruction

Fetch

Instruction

Decode

Operand

Fetch

Execute

Write

Back

Obtain the instruction

Determine action to be perform

Obtain the operand data

Compute the result (update status)

Store the result

2/25/2013

4

2011

dce

ISA Styles

ISA Styles?

Stack

Accumulator

Register memory/ Memory memory

Register register/load store

Operation

Input1 Input2

Output

7

2011

dce

ISA Styles: Stack

8

Computer Architecture, Chapter 2

Stack: The operands is on top of stack. The

result is push back to the stack

(+): Code density, simple hardware

(-): Low parallelism, stack bottle-neck

Stack Element

Stack Element

TOS

C= A+B?

PUSH A

PUSH B

ADD

POP C

2/25/2013

5

2011

dce

ISA Styles: Accumulator

9

Computer Architecture, Chapter 2

Accumulator: One accumulator register is used in all

operations

(+): Easy to write compiler, few instruction

(-): Very high memory traffic, variable CPI

Accumulator

Memory

C= A+B?

LOAD A - Put A in

Accumulator

ADD B - Add B with AC

put result in AC

STORE C- Put AC in C

2011

dce

ISA Styles: Memory-memory

10

Computer Architecture, Chapter 2

Memory-memory: The operands is located in

memory

(+): Simple hardware, design & understand

(-): Accumulator bottle-nect, memory access

Memory

2/25/2013

6

2011

dce

ISA Styles: Register-Memory

2011, Dr. Dinh Duc Anh Vu 11

Computer Architecture, Chapter 2

Register

Register

Register

Memory

Input, Output: Register

or Memory

C= A+B?

LOAD R1, A

ADD R3, R1, B

STORE R3, C

2011

dce

ISA Styles: Register-Register

12

Computer Architecture, Chapter 2

Register-Register: All operation is on registers

Need specific Load and Store instruction to

access memory

Register

Register

Register

C= A+B?

LOAD R1, A

LOAD R2, B

ADD R3, R1, R2

STORE R3, C

2/25/2013

7

2011

dce

ISA Styles

13

Computer Architecture, Chapter 2

Machine # general-purpose

registers

Architecture style Year

Motorola 6800 2 Accumulator 1974

DEC VAX 16 Register-Memory/ Memory-Memory 1977

Intel 8086 1 Extended Accumulator 1978

Motorola 68000 16 Register-Memory 1980

Intel 80386 32 Register-Memory 1985

Power PC 32 Load-Store 1992

Dec Alpha 32 Load-Store 1992

2011

dce

Other ISA Styles

14

Computer Architecture, Chapter 2

High-level-language architecture:

In the 1960s (B5000)

Lack of effective compiler

Reduced Instruction Set architecture:

Simplify hardware

Simplify the instruction set

Simplify the instruction format

Rely on compiler to perform complex

operation

2/25/2013

8

2011

dce

Evolution of Instruction Sets

Single Accumulator (EDSAC 1950)

Accumulator + Index Registers

(Manchester Mark I, IBM 700 series 1953)

Separation of Programming Model

from Implementation

High-level Language Based Concept of a Family

(B5000 1963) (IBM 360 1964)

General Purpose Register Machines

Complex Instruction Sets Load/Store Architecture

RISC

(Vax, Intel 432 1977-80)

(CDC 6600, Cray 1 1963-76)

(Mips,Sparc,HP-PA,IBM RS6000,PowerPC . . .1987)

LIW/EPIC? (IA-64. . .1999)

Computer Architecture, Chapter 2

15

2011

dce

Instruction set design

16

Computer Architecture, Chapter 2

The design of an Instruction Set is critical to

the operation of a computer system.

Including many aspects

Operation repertoire

Addressing modes

Data types

Instruction format

Registers

2/25/2013

9

2011

dce

Simple format

17

Computer Architecture, Chapter 2

Operation Code: the operation to be performed

by the processor

Source Operand Reference: Input of the

operation. One or more source operands can

be involved

Result Operand Reference: Result of the

operation

Opcode Operand reference Operand reference

2011

dce

Instruction Types

18

Computer Architecture, Chapter 2

Can be classified into 4 types:

- Data processing: Arithmetic, Logic

Ex: ADD, SUB, AND, OR,

- Data storage: Move data from/to memory

Ex: LD, ST

- Data movement: Register and register/IO

Ex: MOV

- Control: Test and branch

Ex: JMP, CMP

2/25/2013

10

2011

dce

Operations

19

Computer Architecture, Chapter 2

There must certainly be instructions for performing

the fundamental arithmetic operations

Burkes, Goldstine and Von Neumann, 1947

How many programs have IF statement?

-> Branch instructions

How many programs have Call statement?

-> Call, Return instructions

How many programs have to access memory?

and so on

2011

dce

Operations

20

Computer Architecture, Chapter 2

Operator type Example

Arithmetic & Logical Integer arithmetic and logical operations: add, and, subtract

Data transfer Loads-stores (move instructions on machines with memory addressing)

Control Branch, jump, procedure call and return, trap

System Operating system call, Virtual memory management instructions

Floating point Floating point instructions: add, multiply

Decimal Decimal add, decimal multiply, decimal to character conversion

String String move, string compare, string search

Graphic Pixel operations, compression/decompression operations

2/25/2013

11

2011

dce

Operations

21

Computer Architecture, Chapter 2

Arithmetic, logical, data transfer and control

are almost standard categories for all

machines

System instructions are required for multi-

programming environment although support

for system functions varies

Others can be primitives (e.g. decimal and

string on IBM 360 and VAX), provided by a

co-processor, or synthesized by compiler

2011

dce

Operation usage

22

Computer Architecture, Chapter 2

Simple instructions are the most widely

executed

Make the common case fast

2/25/2013

12

2011

dce

Operations

23

Computer Architecture, Chapter 2

Jump: unconditional (Goto statement)

Branch: conditional (if/else statement)

Call/return: procedure call/return

2011

dce

Operations

24

Computer Architecture, Chapter 2

PC-Relative addressing: short and position-

indipendent jump

Register indirect addressing: Long jump,

dynamic library, virtual function,

2/25/2013

13

2011

dce

Operation

25

Computer Architecture, Chapter 2

2011

dce

Operation

26

Computer Architecture, Chapter 2

Load/Store: There must be mechanism to

access memory

Is Jump necessary?

Is Call/Return necessary?

Is Arithmetic/Logical necessary?

Is Move register-register necessary?

What types of comparison need to be

supported?

2/25/2013

14

2011

dce

Addressing Modes

27

Computer Architecture, Chapter 2

The way the processor refers to the operands is

called addressing mode

The addressing modes can be classified based

on:

The source of data: Immediate, registers,

memory

The address calculation: Direct, indirect,

indexed

2011

dce

Addressing modes

28

Computer Architecture, Chapter 2

- Immediate addressing: the operand is put in

the instruction

Ex: ADD R0, #10

- Register addressing: the index of the register

which contains the operand is specified in the

instruction

Ex: ADD R0, R1

- Direct addressing: the address of the operand

is put in the instruction

Ex: ADD R0, (100)

2/25/2013

15

2011

dce

Addressing modes

29

Computer Architecture, Chapter 2

- Register Indirect addressing: the address of

the operand is put in the register which is

specified in the instruction

Ex: ADD R0, (R1)

- Displacement addressing: the address of the

operand is Base register + Displacement

Ex: LD R1, 100(R2)

- Indexed addressing: The address of the

operand is Base register + Indexed register

Ex: ADD R3, (R1+R2)

2011

dce

Addressing mode use

30

Computer Architecture, Chapter 2

2/25/2013

16

2011

dce

Addressing mode

31

Computer Architecture, Chapter 2

2011

dce

Addressing mode

32

Computer Architecture, Chapter 2

2/25/2013

17

2011

dce

Addressing modes

33

Computer Architecture, Chapter 2

Based on Alpha

(only 16-bit immediate allowed)

On VAX: 20%-25% longer than 16-bit

2011

dce

Addressing modes

34

Computer Architecture, Chapter 2

Is Memory indirect addressing necessary?

Is Scaled addressing necessary?

Is Register addressing necessary?

How long should a displacement value be?

How long should an immediate value be?

2/25/2013

18

2011

dce

Operand types

35

Computer Architecture, Chapter 2

Character:

- ACSII (8-bit): amost always used

- Unicode (16-bit): sometime

Integer: 2s complement

- Short: 16 bit

- Long: 32 bit

Floating point:

- Single precision: 32 bit

- Double precision: 64 bit

2011

dce

Operand types

36

Computer Architecture, Chapter 2

Business

- Binary Coded Decimal (BCD): Accurately

represents decimal fraction

DSP

- Fixed point

- Block floating point

Graphic: RGBA or XYZW

- 8-bit, 16-bit or single precision floating

point

2/25/2013

19

2011

dce

Operand types & size

37

Computer Architecture, Chapter 2

SPEC 2000 on Alpha

Double word: double-precision floating point /

address on 64-bit machine

Word: integer / address in 32-bit machine

2011

dce

Operand types and size

38

Computer Architecture, Chapter 2

Should CPU support all those types of

operand?

Should CPU support very big-size operand?

Is DSPs data types used frequently?

Is BCD used in most of operations?

How about RGBA?

2/25/2013

20

2011

dce

Instruction format

39

Computer Architecture, Chapter 2

Instruction must be encoded to binary values

Effect the size of compiled program

Easy to decode -> Simple to implement

Support as many registers and addressing

modes as possible

MIPS

Ex: ADD $t0, $s1, $s2

000000 10001 10010 01000 00000 100000

0x02324020

Opcode Rs Rt Rd Shamt Funct

2011

dce

Instruction format

40

Computer Architecture, Chapter 2

Opcode

Addr

Specifier

Addr

Field

Addr

Specifier

Addr

Field

Opcode

Addr

Field 1

Addr

Field 2

Addr

Field 3

Variable insrtuction length (e.g. VAX, X86)

Fixed insrtuction length (e.g. ARM, MIPS, PowerPC)

Hybrid: to gain high code density, use 2 type of

fixed length instruction (e.g. MIPS16, Thumb)

2/25/2013

21

2011

dce

Registers file

41

Computer Architecture, Chapter 2

Register is the fastest memory element

Register cost much more than main memory

Register is flexible for compiler to use

More register need more bits to encode

Register file with more locations can be

slower

How many locations in register file is the most

effective?

2011

dce

Case study: MIPS

42

Computer Architecture, Chapter 2

Used as the example throughout the course

Stanford MIPS commercialized by MIPS

Technologies (www.mips.com)

Large share of embedded core market

Applications in consumer electronics, network/storage

equipment, cameras, printers,

Typical of many modern ISAs

2/25/2013

22

2011

dce

The MIPS ISA

Instruction Categories

Load/Store

Computational

Jump and Branch

Floating Point

coprocessor

Memory Management

Special

3 Instruction Formats: all 32 bits wide

43

Computer Architecture, Chapter 2

R0 - R31

PC

HI

LO

OP

OP

OP

rs rt rd shamt funct

rs rt immediate

jump target

Registers

R-format

I-format

J-format

2011

dce

MIPS (RISC) Design Principles

Simplicity favors regularity

fixed size instructions

small number of instruction formats

opcode always the first 6 bits

Smaller is faster

limited instruction set

limited number of registers in register file

limited number of addressing modes

Make the common case fast

arithmetic operands from the register file (load-store machine)

allow instructions to contain immediate operands

Good design demands good compromises

Same instruction length

Single instruction format => 3 instruction formats

44

Computer Architecture, Chapter 2

2/25/2013

23

2011

dce

MIPS Instruction Classes Distribution

Frequency of MIPS instruction classes for

SPEC2006

45

Computer Architecture, Chapter 2

Instruction Class Frequency

Integer Ft. Pt.

Arithmetic 16% 48%

Data transfer 35% 36%

Logical 12% 4%

Cond. Branch 34% 8%

Jump 2% 0%

2011

dce

MIPS Register Convention

Name Register

Number

Usage Preserve on

call?

$zero 0 constant 0 (hardware) n.a.

$at 1 reserved for assembler n.a.

$v0 - $v1 2-3 returned values no

$a0 - $a3 4-7 arguments yes

$t0 - $t7 8-15 temporaries no

$s0 - $s7 16-23 saved values yes

$t8 - $t9 24-25 temporaries no

$k0 - $k1 26-27 reserved for operating system n.a

$gp 28 global pointer yes

$sp 29 stack pointer yes

$fp 30 frame pointer yes

$ra 31 return addr (hardware) yes

Computer Architecture, Chapter 2

46

2/25/2013

24

2011

dce

MIPS - Endianness

Big Endian: Most-significant byte at lowest

address of a word

Little Endian: Least-significant byte at lowest

address of a word

MIPS is Big-endian

2011

dce

MIPS R-Format instructions

Op: opcode

Rs: First source register number

Rt: Second source register number

Rd: Destination register number

Shamt: shift amount

Number of bit-shift (left/right)

Funct: Extend opcode

ALU function to encode the data path operation

Execution: Rd <- Rs func Rt

48

Computer Architecture, Chapter 2

Op Rs Rt Rd Shamt Funct

2/25/2013

25

2011

dce

MIPS R-Format instructions

Arithmetic operations on register

Logical operations on register

And more (refer [1])

For arithmetic and logical instruction: opcode

is always SPECIAL (000000), Funct indicates

the specific operation to be performed

What addressing mode do these instructions

use?

49

Computer Architecture, Chapter 2

2011

dce

Arithmetic instruction

ADD, SUB, MUL, DIV,

Ex: ADD $t0, $s1, $s2

Encoded instruction word is:

0x02324020

50

Computer Architecture, Chapter 2

Special $s1 $s2 $t0 0 add

0 17 18 8 0 32

000000 10001 10010 01000 00000 100000

2/25/2013

26

2011

dce

Logical operations

AND, OR, XOR, XNOR (bit-wise)

Ex: OR $t0, $t1, $t2 #$t0 = $t1 | $t2

Please calculate the encoded instruction word

for the above instruction

Shift left, shift right

Shamt indicates the number of bit to shift

Ex: SLL $t2, $s0, 8

51

Computer Architecture, Chapter 2

000000 00000 10000 01010 01000 000000

2011

dce

Logical operations

Shift Right Arithmetic (SRA) use MSB as the

shift-in bit

Ex: SRA $t2, $s0, 8

Why is there no SLA?

Why is there no NOT?

52

Computer Architecture, Chapter 2

000000 00000 10000 01010 01000 000011

2/25/2013

27

2011

dce

Jump register

Register indirect addressing

JR: Jump register

- Rs: target address

- Rd, Rt = 0; shamt: special purpose (hint) [1]

JALR: Jump and link register

- Rs: target address

- Rd: return address

- Rt = 0; shamt: special purpose (hint) [1]

53

Computer Architecture, Chapter 2

2011

dce

MIPS I-Format instructions

This types of instruction can be:

- Operation with immediate addressing

- Operation with displacement addressing

- Operation with PC-relative addressing

54

Computer Architecture, Chapter 2

Opcode Rs Rt 16-bit immediate value

2/25/2013

28

2011

dce

Immidiate arithmetic and logical

Arithmetic and Logical instruction with immediate

value

- Op: opcode

- Rs: source register

- Rt: destination register

- Constant: immediate value (-32768 to 32767)

Opcode Rs Rt 16-bit Immediate Value

2011

dce

Immediate arithmetic and logical

Ex: ADDI $t0, $t1, 0x0005

Ex: ORI $t0, $t1, 0xFF00

Why is there no SUBI?

56

Computer Architecture, Chapter 2

001000 01001 01000 0000000000000101

001101 01001 01000 1111111100000000

2/25/2013

29

2011

dce

Load-Store (Displacement)

Load/Store instructions with offset

Rs: base register number

16-bit immediate value: offset added to base

address in Rs

The effective address (EA) = Rs + 16-bit

immediate value

Load: Rt is the destination register number

Store: Rt is the value to be store to the EA in

memory

57

Computer Architecture, Chapter 2

Opcode Rs Rt 16-bit immediate value

2011

dce

Load-Store (Displacement)

Ex: LW $t0, 16($t1)

Ex: SW $t0, 16($t1)

58

Computer Architecture, Chapter 2

100011 01001 01000 0000000000010000

101011 01001 01000 0000000000010000

2/25/2013

30

2011

dce

PC-Relative

Near branch instructions

Rs: source register number

Rt: source register number

Target address = PC + offset x 4

PC already incremented by 4 by this time

EX: BEQ $s0, $s1, 256

if($s0 == $s1) goto PC+256;

59

Computer Architecture, Chapter 2

Opcode Rs Rt 16-bit Immediate Value

000100 10000 10001 0000000100000000

2011

dce

MIPS J-format Instructions

Jump (J and JAL)

Pseudo-Direct addressing

Cannot put 32-bit value in instruction

Target address = PC

3128

: (26-bit offset 4)

Ex: J 0x01000000

Opcode 26-bit Offset

000010 00000001000000000000000000000000

2/25/2013

31

2011

dce

Working with byte/halfword

LB/LH/LBU/LHU: Load byte/haftword from

memory

LBU $t0, 1($s0): Zero-extended

LH $t0, 2($s0): Sign-extended

SB, SH: Store byte/halfword to memory

SB $t0, 1($s0)

SH $t0, 2($s0)

Why dont we have SBU, SHU?

61

Computer Architecture, Chapter 2

2011

dce

Atomic operation

An atomic Read-Modify-Write operation can

be done by a pair of instructions: LL (Load

Link Word) and SC (Store Conditional Word)

LL $Rt, offset($Rs)

SC $Rt, offset($Rs)

If the content at memory address specified by

LL is modified before SC to the same address,

SC fails and return 0 in $Rt. Or else, SC store

$Rt to memory and return 1 in $Rt

62

Computer Architecture, Chapter 2

2/25/2013

32

2011

dce

Atomic operation

Example atomic swap:

try: ADD $t0, $zero, $s4 //$t0 = $s4

LL $t1, 0($s1) //$t1 = mem($s1)

SC $t0, 0($s1) //mem($s1) = $t0

BEQ $t0, $zero, try //if mem($s1) changed,

//try again

//else mem($s1) = $t0

ADD $s4, $zero, $t1//$s4 = $t1

63

Computer Architecture, Chapter 2

2011

dce

Constant (Immediate) value

Small constants are used quite frequently

(50% of operands in many common programs)

Ex: $t0 = 0x1234

ADDI $t0, $zero, 0x1234

How to use 32-bit constant?

Ex: $t0 = 0x12345678

LUI $t0, 0x1234

ORI $t0, $t0, 0x5678

64

Computer Architecture, Chapter 2

2/25/2013

33

2011

dce

Procedure call

Save return address

Save necessary registers

Callee execute the function

Restore previously saved registers

Restore return address

Jump to the return address

JAL: Jump to a Label (Procedure), return address

is stored in $ra (register 31)

JR: Jump to the address which is stored in a

register

65

Computer Architecture, Chapter 2

2011

dce

Procedure call: Factorial

MIPS code:

fact:

addi $sp, $sp, -8 # adjust stack for 2 items

sw $ra, 4($sp) # save return address

sw $a0, 0($sp) # save argument

slti $t0, $a0, 1 # test for n < 1

beq $t0, $zero, L1

addi $v0, $zero, 1 # if so, result is 1

addi $sp, $sp, 8 # pop 2 items from stack

jr $ra # and return

L1: addi $a0, $a0, -1 # else decrement n

jal fact # recursive call

lw $a0, 0($sp) # restore original n

lw $ra, 4($sp) # and return address

addi $sp, $sp, 8 # pop 2 items from stack

mul $v0, $a0, $v0 # multiply to get result

jr $ra # and return

Computer Architecture, Chapter 2

66

2/25/2013

34

2011

dce

Reference

[1]Mips instruction set reference.pdf

67

Computer Architecture, Chapter 2

You might also like

- Computer Architecture Question PaperDocument14 pagesComputer Architecture Question Paperheaughfrds100% (1)

- ABB 3HAC050988 AM Arc and Arc Sensor RW 6-En PDFDocument238 pagesABB 3HAC050988 AM Arc and Arc Sensor RW 6-En PDForefat1No ratings yet

- System Software: An Introduction To Systems Programming Leland L. Beck 3rd Edition Addison-Wesley, 1997Document40 pagesSystem Software: An Introduction To Systems Programming Leland L. Beck 3rd Edition Addison-Wesley, 1997Shoyab Ahamed50% (4)

- Computer Interface Trainer (MDA-Win8086) - ProjectDocument77 pagesComputer Interface Trainer (MDA-Win8086) - Projectranahamid00783% (12)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- Microprocessor and Interfacing Techniques: (Course Code: CET208A) Credits-3Document147 pagesMicroprocessor and Interfacing Techniques: (Course Code: CET208A) Credits-3Sorab KhoslaNo ratings yet

- 492 Processor MemoryDocument11 pages492 Processor MemorydharanistrikezNo ratings yet

- I2c PaperDocument14 pagesI2c PaperParvinder SinghNo ratings yet

- Introduction To MicrocontrollersDocument52 pagesIntroduction To MicrocontrollersSanjayaRangaLSenavirathnaNo ratings yet

- Microprocessor ApplicationsDocument100 pagesMicroprocessor Applicationsjai prakashNo ratings yet

- Cs/Coe 1541: Single and Multi-Cycle ImplementationsDocument93 pagesCs/Coe 1541: Single and Multi-Cycle ImplementationsBobo JooNo ratings yet

- William Stallings Computer Organization and Architecture: Reduced Instruction Set ComputersDocument39 pagesWilliam Stallings Computer Organization and Architecture: Reduced Instruction Set ComputersreinaldoopusNo ratings yet

- Embeddedsystem Lecture1Document25 pagesEmbeddedsystem Lecture1Ankita SinghNo ratings yet

- MC & ESY NotesDocument144 pagesMC & ESY NotesgodaserbNo ratings yet

- 2.1 8085 PROGRAMMING 2.1.1 Addressing Modes (Ref2: Section 0.9.2)Document16 pages2.1 8085 PROGRAMMING 2.1.1 Addressing Modes (Ref2: Section 0.9.2)UiNo ratings yet

- cs1104 p2 01Document35 pagescs1104 p2 01hafzalmjNo ratings yet

- Advanced Computer Architecture Bahria Summer 2012 Instructor: Shaftab AhmedDocument43 pagesAdvanced Computer Architecture Bahria Summer 2012 Instructor: Shaftab AhmedBilal HassanNo ratings yet

- Chapter8Document38 pagesChapter8Georgian ChailNo ratings yet

- MP Notes 1675143848Document80 pagesMP Notes 1675143848gokul docNo ratings yet

- CA Classes-51-55Document5 pagesCA Classes-51-55SrinivasaRaoNo ratings yet

- Isa 1Document13 pagesIsa 1awais_alii56No ratings yet

- System-On-Chip Design Introduction: Marcel Jacomet Bern University of Applied Sciences Bfh-Ti Huce-Microlab, Biel/BienneDocument55 pagesSystem-On-Chip Design Introduction: Marcel Jacomet Bern University of Applied Sciences Bfh-Ti Huce-Microlab, Biel/BienneboppanamuralikrishnaNo ratings yet

- Ramesh .B ELEC 6200 Computer Architecture & Design Fall 2008Document17 pagesRamesh .B ELEC 6200 Computer Architecture & Design Fall 2008Amandeep Kaur JunejaNo ratings yet

- Week 3 - Four Instruction CPUDocument8 pagesWeek 3 - Four Instruction CPUGame AccountNo ratings yet

- MAX PLUS II and ALTERA UP1 BoardDocument58 pagesMAX PLUS II and ALTERA UP1 BoardMuntoiaNo ratings yet

- CENG 331 Course Slides Chapter 5Document73 pagesCENG 331 Course Slides Chapter 5Odunayo KusoroNo ratings yet

- Ece Embed Ed SystemDocument27 pagesEce Embed Ed SystemlakshmigajendranNo ratings yet

- 8 Bit Risc Processor PresentationDocument36 pages8 Bit Risc Processor PresentationSantanu KumarNo ratings yet

- MEL G642-Compre Solution - 2 2016-17Document9 pagesMEL G642-Compre Solution - 2 2016-17Gaurav PatilNo ratings yet

- Keil C51 Cross Compiler: Embedded Systems 2 2 - 1 C ProgrammingDocument35 pagesKeil C51 Cross Compiler: Embedded Systems 2 2 - 1 C ProgrammingPrapulla KumarNo ratings yet

- Final Mapi Lab ManualDocument44 pagesFinal Mapi Lab ManualRamachandra ReddyNo ratings yet

- Pape 3Document20 pagesPape 3Aayush PatidarNo ratings yet

- Instructional Tools For Designing and Analysing A Very Simple CPUDocument10 pagesInstructional Tools For Designing and Analysing A Very Simple CPUFrancisco Javier Cesni MaldonadoNo ratings yet

- Advantbasics TrainingDocument36 pagesAdvantbasics TrainingRavi Kumar BandarulankaNo ratings yet

- DCA2203 - System Software Merged Sem 4thDocument424 pagesDCA2203 - System Software Merged Sem 4thadobeindustrialsystemsNo ratings yet

- CA Project ReportDocument26 pagesCA Project ReportShivam SisodiaNo ratings yet

- Assignment 22u02032Document27 pagesAssignment 22u02032Harsh ShivhareNo ratings yet

- Lecture01 s07Document41 pagesLecture01 s07Ali AhmadNo ratings yet

- 1.1 Vlsi (Very Large Scale Integeration)Document36 pages1.1 Vlsi (Very Large Scale Integeration)Rishiraj NalandiNo ratings yet

- DR/ Hassan Shehata: Microprocessor Assignments 1, 2,3Document6 pagesDR/ Hassan Shehata: Microprocessor Assignments 1, 2,3manhagNo ratings yet

- DR/ Hassan Shehata: Microprocessor Assignments 1, 2,3Document6 pagesDR/ Hassan Shehata: Microprocessor Assignments 1, 2,3manhagNo ratings yet

- System and Devices Latency On LinuxDocument30 pagesSystem and Devices Latency On Linuxwanna_acNo ratings yet

- Cs 9303 System Software Internals: V.P Jaya ChitraDocument88 pagesCs 9303 System Software Internals: V.P Jaya ChitraSagar ChingaliNo ratings yet

- 2 Marks With AnswersDocument14 pages2 Marks With Answersprisci_durai83% (6)

- Design and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformDocument6 pagesDesign and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformIheb HamedNo ratings yet

- Minor Project: DTMF Controlled Robot "Mobot"Document65 pagesMinor Project: DTMF Controlled Robot "Mobot"Shyami GovindNo ratings yet

- Introduction - Unit I MCDocument35 pagesIntroduction - Unit I MCKirthi RkNo ratings yet

- Altera's MAX+plus II and The UP 1 Educational Board: Advanced Logic Design, CPE/EE 422/502Document59 pagesAltera's MAX+plus II and The UP 1 Educational Board: Advanced Logic Design, CPE/EE 422/502IbrahimFaroukSolarNo ratings yet

- Two Mark Questions and AnswersDocument29 pagesTwo Mark Questions and Answerssuganrhithu9389No ratings yet

- CompilerDocument29 pagesCompilerAnu Hridya SNo ratings yet

- Computer Architecture - Our NoteDocument3 pagesComputer Architecture - Our NoteGarima PaudelNo ratings yet

- Assemblers: System Software by Leland L. BeckDocument66 pagesAssemblers: System Software by Leland L. Beckckakorot92No ratings yet

- Assembler Pass 1.Document66 pagesAssembler Pass 1.akbisoi1No ratings yet

- Getting Started With The SDCC/MetaLink 8051 C Cross Compiler/Assembler and The XS 40 Prototyping Platform - A User's GuideDocument46 pagesGetting Started With The SDCC/MetaLink 8051 C Cross Compiler/Assembler and The XS 40 Prototyping Platform - A User's Guideprabhunithin1No ratings yet

- Assemblers: System Software by Leland L. BeckDocument66 pagesAssemblers: System Software by Leland L. Beckajinkya684No ratings yet

- Design of A RISC Microcontroller Core in 48 HoursDocument11 pagesDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediNo ratings yet

- ADvance MIcroprocessor Scheme GTUDocument4 pagesADvance MIcroprocessor Scheme GTUamitcrathodNo ratings yet

- Automated Solution For Data Monitoring (Dashboard) of ASIC Design FlowDocument4 pagesAutomated Solution For Data Monitoring (Dashboard) of ASIC Design FlowseventhsensegroupNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Roboremo User Manual V1.9Document23 pagesRoboremo User Manual V1.9DhaniNo ratings yet

- 02 SetupDocument38 pages02 SetupJohn Restrepo GrisalesNo ratings yet

- 1.3 Future Scaling: Where Systems and Technology Meet: 25 Digest of Technical PapersDocument5 pages1.3 Future Scaling: Where Systems and Technology Meet: 25 Digest of Technical Papersck maitiNo ratings yet

- Grade 3 Quarterly ExamsDocument3 pagesGrade 3 Quarterly ExamsJM JMNo ratings yet

- Book Title: Integrated Devices and Circuits For Artificial IntelligenceDocument1 pageBook Title: Integrated Devices and Circuits For Artificial IntelligenceSathesh KNo ratings yet

- ONYX THRIVE RIP - Quick Reference GuideDocument4 pagesONYX THRIVE RIP - Quick Reference Guidejjugumi777No ratings yet

- Brochure PaviroDocument7 pagesBrochure PaviroHussain BagasrawalaNo ratings yet

- Chapter 9: Microsoft Powerpoint - Intermediate: ObjectivesDocument26 pagesChapter 9: Microsoft Powerpoint - Intermediate: ObjectivesEA BuoNo ratings yet

- Annexure - I: - Core Network Deployment - UTRAN Network VT Setup - UTRAN Protocol and Connectivity DiagramDocument5 pagesAnnexure - I: - Core Network Deployment - UTRAN Network VT Setup - UTRAN Protocol and Connectivity DiagramsumitgoraiNo ratings yet

- Gigabyte Ga-b85m-Ds3h Rev 3.0Document30 pagesGigabyte Ga-b85m-Ds3h Rev 3.0YosbelNo ratings yet

- 14 Routing ProtocolsDocument37 pages14 Routing ProtocolsPratibhaNo ratings yet

- TSSN4 - VERSA SD-WAN and SASE OfferingDocument29 pagesTSSN4 - VERSA SD-WAN and SASE OfferingCristian ReyesNo ratings yet

- CT1 NNDL Question BankDocument8 pagesCT1 NNDL Question BankTECH TALKSNo ratings yet

- Catalogue 2022 r02Document22 pagesCatalogue 2022 r02EmilioGastónNo ratings yet

- Docs Slides Lecture1Document31 pagesDocs Slides Lecture1PravinkumarGhodakeNo ratings yet

- Introduction To Approximation Algorithms: Proximation Ratio. Informally, For A Minimization Problem Such As The VDocument15 pagesIntroduction To Approximation Algorithms: Proximation Ratio. Informally, For A Minimization Problem Such As The VPritish PradhanNo ratings yet

- Assertions PDFDocument11 pagesAssertions PDFMurthy MallikarjunaNo ratings yet

- GU Syllabus B.TECH. (ECE) LatestDocument6 pagesGU Syllabus B.TECH. (ECE) LatestME VideoNo ratings yet

- SDLCDocument11 pagesSDLCRAVITEJA TELUGARANo ratings yet

- Percona Distribution Mysql Operator 1.10.0Document231 pagesPercona Distribution Mysql Operator 1.10.0Mari MirandaNo ratings yet

- File 661 GL300-Manage-Tool-User-Guide R1.04Document23 pagesFile 661 GL300-Manage-Tool-User-Guide R1.04Jameson ValerysNo ratings yet

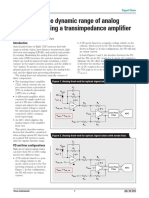

- TIA+Differential Amplifier TexasDocument8 pagesTIA+Differential Amplifier TexasHrishikesh KunchepuNo ratings yet

- Software Engineering AssignmentDocument17 pagesSoftware Engineering AssignmentSajjad QureshiNo ratings yet

- Dot Net Questions LatestDocument54 pagesDot Net Questions LatestravigudiseNo ratings yet

- Csc134 Lab WEEK 1 - Introduction To Operating System (OS)Document2 pagesCsc134 Lab WEEK 1 - Introduction To Operating System (OS)Syazwani Mas ImranNo ratings yet

- WC LAB Manual FinalDocument73 pagesWC LAB Manual FinalhtasarpnuraNo ratings yet

- WT1500 Series External Modulation Optical TransmitterDocument3 pagesWT1500 Series External Modulation Optical TransmitterDaniel TacoNo ratings yet

- Alpha GoDocument24 pagesAlpha Gojoseph676No ratings yet

- CS436 - Mobile Application Development: Dr. Usman Khan DurraniDocument35 pagesCS436 - Mobile Application Development: Dr. Usman Khan DurraniZohaib AhmadNo ratings yet