Professional Documents

Culture Documents

Digital Two-Loop Controller Design For Fourth Order Split-Inductor Converter

Digital Two-Loop Controller Design For Fourth Order Split-Inductor Converter

Uploaded by

Raveendhra IitrCopyright:

Available Formats

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Cascade Controller For DCDC Buck ConvertorDocument6 pagesCascade Controller For DCDC Buck ConvertorCristóbal Eduardo Carreño MosqueiraNo ratings yet

- Predictive Current Controlled 5-kW Single-Phase Bidirectional Inverter With Wide Inductance Variation For DC-Microgrid ApplicationsDocument9 pagesPredictive Current Controlled 5-kW Single-Phase Bidirectional Inverter With Wide Inductance Variation For DC-Microgrid ApplicationsJitender KaushalNo ratings yet

- Electronics 11 01693Document20 pagesElectronics 11 01693Bùi Quốc DuyNo ratings yet

- Transformer Less DC - DC Converter With High Step Up Voltage Gain MethodDocument6 pagesTransformer Less DC - DC Converter With High Step Up Voltage Gain Methodsurendiran123No ratings yet

- Two-Loop Hysteretic Control of 3 Order Buck Converter: M. Veerachary and Deepen SharmaDocument8 pagesTwo-Loop Hysteretic Control of 3 Order Buck Converter: M. Veerachary and Deepen SharmaDeepen SharmaNo ratings yet

- Ijre 3 An Integrated DC DC Converter Topology With Buck and Boost Outputs V3i1 3113Document3 pagesIjre 3 An Integrated DC DC Converter Topology With Buck and Boost Outputs V3i1 3113KEERTHY SNo ratings yet

- 3939 Ijet IjensDocument9 pages3939 Ijet IjensGarudaOzoNo ratings yet

- Boost Converter Based On State Space Modeling Ebrahimi2015Document7 pagesBoost Converter Based On State Space Modeling Ebrahimi2015shrikrisNo ratings yet

- An Introduction To Sepic ConverterDocument2 pagesAn Introduction To Sepic Converterleemoh8190No ratings yet

- Fuzzy Logic Controlled Bidirectional DC-DC Converter Applied To DC DriveDocument12 pagesFuzzy Logic Controlled Bidirectional DC-DC Converter Applied To DC DriveTJPRC PublicationsNo ratings yet

- Bidirectional DC To DC Converters: An Overview of Various Topologies, Switching Schemes and Control TechniquesDocument6 pagesBidirectional DC To DC Converters: An Overview of Various Topologies, Switching Schemes and Control TechniquesVo Thanh TungNo ratings yet

- ICPE11 ImplDocument8 pagesICPE11 Implhans_fitz4134No ratings yet

- Current Mirror 1Document5 pagesCurrent Mirror 1Shaheer DurraniNo ratings yet

- Single-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeDocument12 pagesSingle-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeZhongpeng LiangNo ratings yet

- Bidirectional DC-DC Converter Based On Quasi-Sepic For Battery Charging SystemDocument9 pagesBidirectional DC-DC Converter Based On Quasi-Sepic For Battery Charging SystemRofiqun NobiNo ratings yet

- Bidirectional LLC Resonant Converter For Energy Storage ApplicationsDocument7 pagesBidirectional LLC Resonant Converter For Energy Storage ApplicationsRodrigo MesquitaNo ratings yet

- Analysis of Single Switch Step Up DC-DC Converter For Alternative Energy SystemsDocument6 pagesAnalysis of Single Switch Step Up DC-DC Converter For Alternative Energy SystemsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Analysis and Design of A Bidirectional Isolated DC-DC Converter For Fuel Cell and Super-Capacitor Hybrid SystemDocument13 pagesAnalysis and Design of A Bidirectional Isolated DC-DC Converter For Fuel Cell and Super-Capacitor Hybrid SystemHernandaBudiSantosoNo ratings yet

- Closed Loop Control Design of Two Inductor Current-Fed Isolated DC-DC Converter For Fuel Cells To Utility Interface ApplicationDocument8 pagesClosed Loop Control Design of Two Inductor Current-Fed Isolated DC-DC Converter For Fuel Cells To Utility Interface ApplicationNagababuMutyalaNo ratings yet

- Sepic ReportDocument55 pagesSepic ReportHEERAVATHINo ratings yet

- AarthiDocument10 pagesAarthiSoniya CsNo ratings yet

- Dynamic Modeling and Controller Design For A SinglDocument13 pagesDynamic Modeling and Controller Design For A SinglSkp FANo ratings yet

- Power Converters, Control, and Energy Management For Distributed GenerationDocument5 pagesPower Converters, Control, and Energy Management For Distributed GenerationAbdelaziz IsmealNo ratings yet

- LED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForDocument5 pagesLED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForArun KumarNo ratings yet

- Cta 2701Document25 pagesCta 2701pedroNo ratings yet

- IET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsDocument10 pagesIET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsHsekum RamukNo ratings yet

- Compact Dualoutput Inverter Based On Flyingcapacitor Modelling Control and Prototype ValidationDocument8 pagesCompact Dualoutput Inverter Based On Flyingcapacitor Modelling Control and Prototype ValidationkhasimNo ratings yet

- A Parallel-Resonant Isolated Bidirectional DC-DC Converter With Low Current Ripple For Battery Storage SystemsDocument6 pagesA Parallel-Resonant Isolated Bidirectional DC-DC Converter With Low Current Ripple For Battery Storage SystemsSaurabh KaduskarNo ratings yet

- State Space Averaging Model of Boost ConvDocument60 pagesState Space Averaging Model of Boost ConvBharti Thakur100% (1)

- An Interleaved Bi-Directional AC-DC ConverterDocument5 pagesAn Interleaved Bi-Directional AC-DC ConverterAsad HameedNo ratings yet

- ELEC 6411 - Project Final FinalDocument30 pagesELEC 6411 - Project Final FinalAndrewJohnsonJenssonNo ratings yet

- 10.1007@s00202 019 00901 XDocument12 pages10.1007@s00202 019 00901 XfarhaniNo ratings yet

- Closed Sepic1Document6 pagesClosed Sepic1Thimothy BasavaNo ratings yet

- Modelling and Simulation of High Step Up DC To AC Converter For Microsource ApplicationDocument5 pagesModelling and Simulation of High Step Up DC To AC Converter For Microsource ApplicationtheijesNo ratings yet

- Soft Switched High Step-Up DC-DC Converter For Automotive ApplicationDocument4 pagesSoft Switched High Step-Up DC-DC Converter For Automotive Applicationkarthi.r.tNo ratings yet

- A Boost Converter With Capacitor Multiplier and Coupled Inductor For AC Module ApplicationsDocument9 pagesA Boost Converter With Capacitor Multiplier and Coupled Inductor For AC Module ApplicationsChinni NeeluNo ratings yet

- ModelingandSimulationofDC DCConvertersDocument13 pagesModelingandSimulationofDC DCConvertersSureshkumar AlagarsamyNo ratings yet

- Step Down PSIMDocument6 pagesStep Down PSIMAnonymous W44hzJ9roNo ratings yet

- A Two Stage Buck Boost Converter With SoDocument7 pagesA Two Stage Buck Boost Converter With Sodd1663No ratings yet

- Bridgeless AC-DC Buck-Boost Converter WithDocument5 pagesBridgeless AC-DC Buck-Boost Converter WithJishnu VenugopalNo ratings yet

- High-Efficiency Bidirectional DC - DC Converter With High-Voltage GainDocument12 pagesHigh-Efficiency Bidirectional DC - DC Converter With High-Voltage GainghiocelNo ratings yet

- A Modified DC Power Electronic TransformerDocument15 pagesA Modified DC Power Electronic TransformerArun KumarNo ratings yet

- Final ReportDocument88 pagesFinal ReportYOKESH BNo ratings yet

- Design and Implementation of Luo Converter For Electric Vehicle ApplicationsDocument5 pagesDesign and Implementation of Luo Converter For Electric Vehicle ApplicationsseventhsensegroupNo ratings yet

- Continuous Conduction Mode of Bridgeless SEPIC Power Factor Correction RectifierDocument4 pagesContinuous Conduction Mode of Bridgeless SEPIC Power Factor Correction Rectifiersindhuja selvamNo ratings yet

- 2 Bobine CuplateDocument26 pages2 Bobine CuplateParvulescu Mihai LucianNo ratings yet

- Ijert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterDocument9 pagesIjert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterAnjali SharmaNo ratings yet

- Design of Transformer-Less DC To AC Converter Using PWM TechniqueDocument6 pagesDesign of Transformer-Less DC To AC Converter Using PWM TechniqueHariesh WaranNo ratings yet

- Efficiency and Cost Optimization of Dual Active Bridge Converter For 350kW DC Fast ChargersDocument6 pagesEfficiency and Cost Optimization of Dual Active Bridge Converter For 350kW DC Fast ChargersJaja LocoNo ratings yet

- Modelling Bidirectional Buck BoostDocument7 pagesModelling Bidirectional Buck BoostAkay HanafiahNo ratings yet

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDocument14 pagesWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06No ratings yet

- Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterDocument9 pagesTwo-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterRaveendhra IitrNo ratings yet

- Large Step Ratio Input-Series-Output-Parallel Chain-Link DC-DC ConverterDocument12 pagesLarge Step Ratio Input-Series-Output-Parallel Chain-Link DC-DC ConverterArunavaNo ratings yet

- A Single-Switch Transformerless DC-DC Converter With Universal Input Voltage For Fuel Cell Vehicles: Analysis and DesignDocument13 pagesA Single-Switch Transformerless DC-DC Converter With Universal Input Voltage For Fuel Cell Vehicles: Analysis and DesignahmedNo ratings yet

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDocument9 pagesHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNo ratings yet

- Voltage-Lift-Type Cu K Converters: Topology and Analysis: M. Zhu F.L. LuoDocument14 pagesVoltage-Lift-Type Cu K Converters: Topology and Analysis: M. Zhu F.L. LuomenguemengueNo ratings yet

- Hybrid Switched-Inductor Converters For High Step-Up ConversionDocument11 pagesHybrid Switched-Inductor Converters For High Step-Up ConversionRahim SamanbakhshNo ratings yet

- Design of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemDocument6 pagesDesign of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemRaveendhra IitrNo ratings yet

- Telephone Directory: Telephone Exchange Indian Institute of Technology Roorkee ROORKEE - 247 667 June - 2017Document72 pagesTelephone Directory: Telephone Exchange Indian Institute of Technology Roorkee ROORKEE - 247 667 June - 2017Raveendhra IitrNo ratings yet

- High Power Topology: "AlbacomDocument7 pagesHigh Power Topology: "AlbacomRaveendhra IitrNo ratings yet

- Bi-Directional Fonvard-Flyback DC-DC Converter: IEEE PowerDocument4 pagesBi-Directional Fonvard-Flyback DC-DC Converter: IEEE PowerRaveendhra IitrNo ratings yet

- Design of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemDocument6 pagesDesign of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemRaveendhra IitrNo ratings yet

- A New Single Switch Buck-Boost Type DC-DC ConverterDocument4 pagesA New Single Switch Buck-Boost Type DC-DC ConverterRaveendhra IitrNo ratings yet

- Synthesis and Analysis of A Multiple-Input Parallel SC DC-DC ConverterDocument4 pagesSynthesis and Analysis of A Multiple-Input Parallel SC DC-DC ConverterRaveendhra IitrNo ratings yet

- High Performance DC-DC Converter For Wide Voltage Range OperationDocument8 pagesHigh Performance DC-DC Converter For Wide Voltage Range OperationRaveendhra IitrNo ratings yet

- 0628-1 Course MinhCTaDocument1 page0628-1 Course MinhCTaRaveendhra IitrNo ratings yet

- Design of Robust Digital PID Controller For H-Bridge Soft-Switching Boost ConverterDocument15 pagesDesign of Robust Digital PID Controller For H-Bridge Soft-Switching Boost ConverterRaveendhra IitrNo ratings yet

- Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterDocument9 pagesTwo-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterRaveendhra IitrNo ratings yet

- Based Power Tracking For Nonlinear PV SourcesDocument8 pagesBased Power Tracking For Nonlinear PV SourcesRaveendhra IitrNo ratings yet

- Maximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemDocument10 pagesMaximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemRaveendhra IitrNo ratings yet

- 19-GB 50030-91氧气站设计规范en PDFDocument34 pages19-GB 50030-91氧气站设计规范en PDFyyyy071220No ratings yet

- 1308020EN Electrical EngineeringDocument20 pages1308020EN Electrical EngineeringamrehmaniNo ratings yet

- Lexmark C91x C912 5505 Service ManualDocument492 pagesLexmark C91x C912 5505 Service ManualMichael HanniganNo ratings yet

- Flow Properties and Design Procedures For Coal Storage Bins PDFDocument401 pagesFlow Properties and Design Procedures For Coal Storage Bins PDFEmaVanni100% (2)

- Grid Station PresentationDocument40 pagesGrid Station Presentationranafaizan773750% (2)

- Manual YbportDocument105 pagesManual YbportMan GeekaaNo ratings yet

- Fro 15210C 0510Document36 pagesFro 15210C 0510davisNo ratings yet

- Research Paper On Building MaterialsDocument7 pagesResearch Paper On Building Materialsafnknlsjcpanrs100% (1)

- Ship Power PlantDocument141 pagesShip Power Plantnguyentrunghieu51dltt100% (2)

- BCS 051 Solved AssignmentsDocument11 pagesBCS 051 Solved AssignmentsAmit GuptaNo ratings yet

- ZK - ZK Component Reference - Essential Components - Fileupload - DocumentationDocument5 pagesZK - ZK Component Reference - Essential Components - Fileupload - DocumentationEmerson JoaquimNo ratings yet

- APX Portable Accessory CatalogDocument12 pagesAPX Portable Accessory Catalogcraig_ochsNo ratings yet

- Flight Management and NavigationDocument18 pagesFlight Management and NavigationmohamedNo ratings yet

- Copyright ProtectionDocument6 pagesCopyright ProtectionKamalbir KaurNo ratings yet

- Mve Vapor Shippers (Regular) - Cryogenic Vapor Shippers - Cryo Cube - Cryo Moover - Mini Moover - Cryo Shipper - Cryo Shipper XCDocument9 pagesMve Vapor Shippers (Regular) - Cryogenic Vapor Shippers - Cryo Cube - Cryo Moover - Mini Moover - Cryo Shipper - Cryo Shipper XCPrincestonNo ratings yet

- ZL300 Main Contact Kit: Product-DetailsDocument3 pagesZL300 Main Contact Kit: Product-DetailsMahyar MashayekhiNo ratings yet

- Mte 3152 Electric Drives Mid TermDocument2 pagesMte 3152 Electric Drives Mid TermAjitash TrivediNo ratings yet

- Inf Luence of Tip Clearance On The Flow Field and Aerodynamic Performance of The Centrif Ugal ImpellerDocument6 pagesInf Luence of Tip Clearance On The Flow Field and Aerodynamic Performance of The Centrif Ugal Impellerarm coreNo ratings yet

- The Sproutling Baby Monitor Keep Tabs On Your Newborn With This Smart Ankle BraceletDocument2 pagesThe Sproutling Baby Monitor Keep Tabs On Your Newborn With This Smart Ankle BraceletAllanStevenNo ratings yet

- CV Shanmugaraj.rDocument2 pagesCV Shanmugaraj.rpreanandNo ratings yet

- Pipe Size CalculationDocument42 pagesPipe Size CalculationfelipeNo ratings yet

- Design Planning Records Center of The Future 2004-10Document29 pagesDesign Planning Records Center of The Future 2004-10Talam KeladiNo ratings yet

- Solar Photovoltaic Wire 600V: DescriptionDocument1 pageSolar Photovoltaic Wire 600V: DescriptionAMARENDRA SINo ratings yet

- Coolant Contains Oil: TroubleshootingDocument2 pagesCoolant Contains Oil: TroubleshootingPutra JawaNo ratings yet

- Industrial Automation Technical Interview QuestionsDocument27 pagesIndustrial Automation Technical Interview Questionsanon_680083156100% (1)

- MASTER FLOW p2 - BB - 6000 - NewDocument4 pagesMASTER FLOW p2 - BB - 6000 - NewJosé Daniel ArenasNo ratings yet

- Construction Material Lecture NoteDocument12 pagesConstruction Material Lecture NoteMohamedNo ratings yet

- Tech Paper Performance Analysis of 6 Axis RobotDocument10 pagesTech Paper Performance Analysis of 6 Axis RobotSyahril PabloNo ratings yet

- 2D CFD Transient Analysis of Darrieus H Type Vertical Axis Wind TurbineDocument43 pages2D CFD Transient Analysis of Darrieus H Type Vertical Axis Wind TurbinekaushikNo ratings yet

- Information Gain CalculatorDocument16 pagesInformation Gain CalculatorShashiBhushanSahani0% (1)

Digital Two-Loop Controller Design For Fourth Order Split-Inductor Converter

Digital Two-Loop Controller Design For Fourth Order Split-Inductor Converter

Uploaded by

Raveendhra IitrOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Two-Loop Controller Design For Fourth Order Split-Inductor Converter

Digital Two-Loop Controller Design For Fourth Order Split-Inductor Converter

Uploaded by

Raveendhra IitrCopyright:

Available Formats

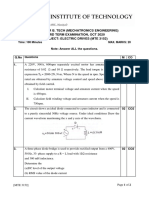

Digital Two-Loop Controller Design for Fourth

Order Split-Inductor Converter

Mummadi Veerachary

Dept. of Electrical Engineering, IIT Delhi, New Delhi, India

E-mail: mvchary@ee.iitd.ac.in

Abstract- In this paper a digital two-loop controller design

methodology is proposed for the fourth order split inductor

converter load voltage regulation. The salient features of the

split-inductor converter are compared with the conventional

SEPIC converter and then discrete-time mathematical models

are established. Digital two-loop controller, inner current-loop

and outer voltage-loop, is designed using direct digital design

approach. A two-pole two-zero compensator is adopted in the

outer voltage-loop, while one-pole and one zero is used in the

inner current-loop design. Compensator design is validated

through simulations and then experimental measurements. Load

voltage regulation characteristics are obtained against line and

load perturbations. A 25 watt 15 to 36 V prototype converter is

built and experimental investigations are carried out. The

measured results obtained from the prototype converter are in

close agreement with those obtained in the analysis.

I. INTRODUCTION

Application of high frequency switch-mode power

conversion is increasing in the low power compact electronic

circuits. As the power conversion system is becoming

miniaturized, increasing the power density is one of the

challenging issues for the power supply designers. One of the

main orientations in power electronics in the last decade has

been the development of switching-mode converters with

higher power density and low electromagnetic interference

(EMI). Light weight, small size and high power density are

also some of the key design parameters [1]-[3].

Switch-mode power supplies (SMPS) are becoming an

integral part of many electronic systems [1] and the dc-dc

converters are mainly used in these application areas.

Technological developments are is taking place in order to:

(i) improve converter performance, (ii) achieve better

reliability, and (iii) increasing the power density, etc. The

aspect of increasing the power density is mainly related to the

converter design and packaging. Performance improvement

of the dc-dc converter topologies is broadly classified into

two different categories, which are: (i) steady-state

performance, and (ii) dynamic performance. Among these

two, the converter system dynamic performance mainly

governed by the type of controller used. Conventional SEPIC

converter based topologies are well established for

applications requiring both bucking and boosting the up-

stream voltages. However, in the applications where the

voltage gain requirement is higher, not possible to realize

with single conventional converter, then there are two

alternate solutions, which are: (i) cascading the boost

converters, (ii) cascading the SEPIC converters. Although

these methods are capable of resulting higher transformation

ratios, but more number of components are required for their

realization and also results in lesser efficiency. Some times to

realize the predefined transformation ratio the converter

needs to be operated at the extreme duty ratios wherein the

device utilization is poor with increased thermal loading. In

order to alleviate some of these limitations coupled inductor

boost converters and quadratic topologies have been proposed

in the literature [1]-[4]. However, more device stress is the

major limitation of these topologies. By using the split-

inductor [2] concept it is possible to increase the voltage gain

of the conventional SEPIC converter, without increasing the

device stress, and one such fourth order split-inductor

converter (FSC) is discussed in this paper.

The dynamic performance of the converter is primarily

decided by the control strategy employed for a particular

topology. The two most commonly used control schemes in

dc-dc switching power converters are: (i) single loop voltage-

mode control, (ii) current-mode control. It is well known that

the single loop voltage-mode control is slow in its response

against supply disturbances [7]. On the other hand the two-

loop control strategy, inner current mode control together

with outer voltage loop, results in faster dynamic response.

However, selection of a particular control scheme is

essentially decided by the complexity and cost trade-offs

requirements imposed by the end-user. In any case selection

of the control strategy is also depends on the speed of

response and robustness requirement. Considering speed of

response as the requirement a two-loop digital controlling

scheme is designed in this paper for the FSC and detailed

design methodology is given in the following paragraphs.

2 2

, L r

3

3

,

L

r

1 1

,

c

C r

0

0

,

c

C

r

1 1

, L r

Fig. 1. Fourth-Order Split Inductor Converter circuit diagram.

IEEE PEDS 2011, Singapore, 5 - 8 December 2011

978-1-4577-0001-9/11/$26.00 2011 IEEE

1137

Fig. 2. Control block diagram of voltage-mode controlled FSC.

TABLE I. PERFORMANCE COMPARISON

SEPIC FSC

Voltage gain Low High

Efficiency Moderate Moderate

Transient response Moderate Low

Switching stresses

on elements

High Low

II. MODELING AND ANALYSIS OF THE FOURTH ORDER

SPLIT-INDUCTOR CONVERTER

The fourth order split-inductor converter is shown in Fig. 1.

This converter is derived from the conventional SEPIC

converter where-in the source side inductance is divided into

two halves and then arranged in a bridge form as shown in

Fig. 1. In comparison to the conventional SEPIC converter, as

it is indicated within the box, it consists of three additional

diodes (D

1

, D

2

and D

3

) and inductors (L

1

,

L

2

). Due to this

structural arrangement the circuit exhibits more important

features as compared to the conventional SEPIC converter,

which are: (i) the FSC is capable of giving higher load

voltage boosting at lower duty ratios, (ii) switch

voltage/current stress is almost same as conventional

converter, and (iii) inductance requirement is almost same as

the conventional converter. Steady-state performance

comparison of this converter with SEPIC converter is given

in Table I for ready reference.

This FSC can operate either in continuous or discontinuous

inductor current mode of operation. However, for a given

power rating and boosting factor requirement the source

current magnitude is high for most of the loading conditions

and correspondingly the current is continuous in all the three

inductors. In view of this, the FSC analysis as well as its

discrete-time model formulation is discussed here for the

continuous inductor current mode of operation. As stated

earlier the high voltage gain of this converter is mainly due to

the presence of the split inductors (L

1

, L

2

), while there is no

change in the load side ripple current as there is no structural

change in the circuit configuration. The split inductor

combination will draw the energy from the dc-voltage source

during switch-ON time period and then pumps into the load

for the remaining time period. In this process the split

inductors will be connected in series during the switch-OFF

period contributing to additional boosting as compared to

conventional SEPIC converter. The split inductor

combination resulting in an additional boosting at the expense

of increased source current ripple.

A. Converter parameter Design Equations

The steady-state analysis of the FSC is carried out in this

section and the analysis is developed here after including the

following simplifying assumptions: (i) switching devices are

ideal, i.e voltage drops in the switching devices are neglected

and the transition time is very small, (ii) ripple current/

voltage magnitude is very small, (iii) converter time constant

is very high as compared to the switching period, and (iv)

non-idealities of the energy storage elements are neglected.

By employing the KVL and KCL the steady-state

relationships among the various voltage and currents are

established. Assuming voltage drops across inductors L

1

, L

2

are same, various voltages across inductor elements L

1

, L

2

and L

3

during switch-ON/OFF periods respectively are:

Inductor ON-time OFF-Time

L

1

V

g

(V

g

- V

c

- V

o

)/2

L

2

V

g

(V

g

- V

c

- V

o

)/2

L

3

V

c

-V

o

Applying volt-sec balance to the inductor L

1

and L

3

the

following voltage gain [7] of the converter is obtained.

( )

( )

0

1

1 -

g

D D V

V D

+

=

(1)

Using the power balance, V

g

I

g

=V

0

I

0

, and time-domain

analysis the FSC design equations are established. The

minimum and maximum inductor current expressions can

easily be obtained by using the ripple quantities,

L1 g 1

i V DT L ; =

L2 g 2

i V DT L = and the capacitor

voltage ripple relationships are:

C1 L2 1

V I DT C , =

2

C0 g 2 0

V V (DT) (8L C ). = These

expressions together with current/ voltage ripple requirements

give the basis for the design of energy storage components

L

1

, L

2

, L

3

and C

1

, C

2

.

B. State-space Models For Continuous Inductor Current

Mode of Operation

Application of state-space modeling is widely used in the

switch-mode power conversion systems. Conventionally, the

discrete-time models are obtained through suitable

transformation applied to the state-space models. However,

accuracy of such discrete-time models mainly governed by

the type of transformation used and the switching frequency

employed. In ref[4] discrete-time modeling of digitally

controlled converters has been reported, where-in it has been

demonstrated that it is possible to include type of pulse width

modulation strategy as well as the sampling instant

information in the model itself. This methodology is used to

formulate the discrete-time model for the proposed FSC

1138

operating at trailing-edge OFF-time sampling [7]. In

continuous inductor current mode of operation the circuit has

two operating modes; Mode-1: S-ON (0<t<DT

s

); Mode-2: S-

OFF (DT

s

<t<T

s

). In each mode of operation the circuit is

linear, and its behavior can easily be described by the state-

space model [13] given by

[ ] [ ] [ ]

[ ] [ ]

( 1)

j j

j j

j

x A x B u

t t t

y E x

+

= +

< <

=

(2)

where [A

j

]- state matrix, [B

j

]- input matrix, [E

j

]- output

matrix, and [x]- state vector, [y]- output vector, [u]- forcing

function vector.

1 1

1 3 3

1

2

1 2

/ 0 0 0

0 / 1/ 0

;

0 1/ 0 0

0 0 0 1/ ( ( ))

c

c

r L

r L L

A

C

C R r

=

+

2

3 3 3 3 3

2

1

2 2 2 2

[ ] / / 1/ / ( * )

/ [ ] / 0 / ( * )

;

1/ 0 0 0 0

/ ( ) / ( ) 0 1/ ( ( ))

e c

c c

c

a r L a L L a r L

a L a r L a r L

A

C

R C R R C R C R r

+

+

=

+

[ ]

2 1

1/ 0 0 0 ;

T

B L = [ ]

2

1/ 0 0 0

T

B L =

C3

1 2

C3 C3

Rr R

E =E = 0 0 0

(R+r ) (R+r )

The above matrices gives an idea of the system that they are

linear in each mode of operation, and the circuit behavior can

easily be obtained by the discrete-time state- model [4] given

by eqns. (3) and (4).

^ ^ ^

[ ] [ 1] [ 1] x n x n d n = + ; (3)

0 k

v = E x ; (4)

s d d 1 2 1

DT -t ) T A ( A A D Ts

=e e e ;

s d 2 1

DT -t ) A A ( D Ts

s

=KT e e

where

[ ]

T

L1 L3 c1 c0

x = i i v v ,

g

u=[V ]. Detailed discrete-

time formulations are reported in ref[4] are used and they are

listed here, eqns. (5)-(9), for ready reference.

-1

vg

G ( ) E (z- ) +F z =

(5)

-1

vd

G ( ) E (z- ) z = (6)

-1

( ) P [(ZI- ) ]

in

Z z = (7)

-1

( ) [E (zI- ) +J ]

o

Z z = (8)

3 2

3 2 1 o

vd

4 3 2

4 3 2 1 o

p z +p z +p z+a

G (z)=

[q z +q z +q +q z+q ] z

(9a)

Substituting the converter parameters, given in Section IV,

results in the following control-to-output transfer function.

3 2

vd

4 3 2

12.68z -31.85z +28.66z-8.982

G (z)=

[z -3.519z +4.833 -3.072z+0.76] z

(9b)

3 2

id

4 3 2

6.632z -16.83z +15.64z-5.383

G (z)=

[z -3.519z +4.833 -3.072z+0.76] z

(9c)

TABLE II. FOURTH ORDER SPLIT-INDUCTOR CONVERTER PARAMETERS

Parameter Value

Vg 15 V 20%

Vo 36 V

R 26 50%

L1, r1 100 H, 0.08

L2, r2 100 H, 0.05

L3, r3 200 H, 0.07

C1, rc1 50 F, 0.14

C0, rc0 100 F, 0.22

fs 50 kHz

III. DIGITAL CONTROLLER DESIGN GUIDELINES

Once the power stage transfer functions are known, then

the digital controller can easily be designed to obtain the

desired closed-loop dynamical performance. Several

compensator design approaches [5]-[10] have been reported

in the literature for the analogue controllers. However, there

are two different approaches can be used while designing the

digital compensator, which are: (i) digital redesign approach,

(ii) digital direct design approach (DDDA). The detailed

discussion about these methods have been given in Ref[7].

The second method, DDDA, is used in this paper for digital

controller design. Pole-zero placement technique is used

while arriving at suitable digital compensator, and its brief

description for one such compensator, two-zero two-pole

structure, is given in the following steps: (i) to reduce

regulation error of the load voltage, the loop gain crossover

frequency, f

c

, should be as high as possible, (ii) set the loop

gain crossover frequency, f

c

be in the range of 1/20 ~ 1/50

of the switching frequency f

s

, (iii) select f

3

as multiples of

f

c

like (

3

2

c

f f =

), (iv) select the frequencies f

2

and

f

3

such that they are in geometric mean with respect to f

c

i.e.,

1 3 c

f f f =

, (v) place the two compensator zeroes

below the crossover frequency (f

1

< f

2

< fc), f

1

=f

2

/10, f

2

=f

c

/f

3

,

(vi) place the two compensator poles above the cross over

frequency (f

c

< f

3

< f

4

), f

4

=10f

3

. These design steps have been

taken into consideration while designing the digital

compensator. However, fine tuning of these locations is

needed depending on the nature of converter transfer

functions. The closed-loop block diagram is shown in Fig. 2.

Use of this approach allows the designer to incorporate the

inherent digital delays present in the actual system. By using

above steps the compensator design can be carried out with

the help of any software program. However, MATLAB [11]

platform is the good choice for compensator design as it is

having all the control related functions. Check all the closed-

loop converter performance specifications, and if the design

is not fulfilling the requirements repeat the process by

1139

changing the crossover frequency, location of pole-zeros and

controller gain. By embedding the closed-loop converter into

any of the power electronic simulators it is easy to verify the

time domain responses through simulations. The overall loop

gain of the closed loop system, including inner current-loop

and outer voltage loop, is in the form given in eqn. 10.

( )

i v

T z T T = +

(10)

( ) ( ) ( ) ( ) ,

( ) ( ) ( ) ( ) ,

i c i d p

v c v d p

T z G z G z G z

T z G z G z G z

=

=

(11)

1 2

3

1

( )( )

( )

( 1)( )

( )

( )

( 1)

v

cv

i

ci

k z a z a

G z

z z a

k z b

G z

z

=

(12)

Among all the above equations the control-to-output

transfer function, G

vd

(z), and control-to-inductor current,

G

id

(z), given by eqn. 9, is required while designing the outer

voltage-loop and inner current-loop controllers. After

substituting the required matrices in the mathematical

identities the resulting transfer function is given by (9). Once

having these transfer functions the individual loop design can

easily be carried out and the corresponding steps explained

above the compensator is designed with the help of

MATLAB [8] platform, wherein almost all linear system

theory related functions are readily available. Check all the

closed-loop converter performance specifications, gain

margin (GM) at least 6 dB and phase margin (PM) in between

30

0

~ 75

0

, and if the design is not fulfilling the requirements

repeat the process by changing the crossover frequency,

locations of poles/zeros.

IV. DISCUSSIONS ON THE SIMULATION AND

EXPERIMENTAL RESULTS

In order to demonstrate the proposed converter salient

features and its controlling capability a 25 W, 15 to- 36 V

FSC is considered here and its parameters are listed in Table

II. State-space models, derived in Section II, have been used

and then important small-signal frequency response

characteristics have been obtained, using MATLAB. For

illustration, the overall loop design frequency response bode

plot is shown in Fig. 3. In order to stabilize the two-loop

system, the overall loopgain should follow the T

v

in the low

frequency region and T

i

in the high frequency region. To

achieve this, a two pole two zero compensators in outer loop

and one pole-zero in the inner loop is now included and the

corresponding loopgain frequency response plot is also

shown in Fig. 3. The digital controllers, G

cv

(z) and G

ci

(z),

parameters are: k

v

=0.9123, a

1

=0.941, a

2

=0.704, a

3

=0.849,

k

i

=0.5623, b

1

=0.941. This overall loopgain plot is exhibiting

a GM= 6.11 dB, PM=61

0

which are within the acceptable

stability limits.

To test the designed controller performance several

simulations, using PSIM simulator [12], have been performed

and then found that load regulation together with faster

dynamic response achieved in each case. Detailed simulation

results will be given in the final paper. The steady-state

voltage gain of the FSC has been verified by varying the duty

ratio, and found that the gain is increasing with increased

duty ratios. In order to validate the mathematical analysis and

simulation results a 25 Watts laboratory prototype FSC is

built and tested for its steady-state and dynamic performance.

To validate the developed theoretical analysis and

simulation results, a laboratory prototype closed-loop

converter has been built and then tested for its load voltage

regulation feature against source and load perturbations. The

digital control algorithm has been implemented using a

AMDC401digital signal processor (DSP) [10]. The devices

used in the prototype converter circuits are: Switch IRF540,

Diode MUR860, Driver circuit IR2110, Opto-coupler 6N137.

The load voltage is sensed and is brought down into the range

(0~1 V), which is passed on to the onboard ADC of the DSP.

The digital controller, given by eqn. 12, has been transformed

into a discrete-time control law given by:

( ) 1.849 ( 1) 0.849 ( 2) 0.9123 ( )

1.5 ( 1) 0.6044 ( 2)

v v v v

v v

d n d n d n e n

e n e n

= +

+

( ) ( 1) 0.5623 ( ) 0.5297 ( 1)

i i i i

d n d n e n e n = +

where d(n), d(n-1) and d(n-2) are the new, one-cycle-before

and two-cycles-before duty ratios, respectively; while e(n),

e(n-1) and e(n-2) are the new, one-cycle-before and two-

cycles-before error signals, respectively.

For demonstration of the principle sample experimentally

measured load voltage dynamic response characteristics for

the following cases: (i) load disturbance from 52 26

(50% variation), (ii) supply voltage change from 15 19 V

(20% variation). These measured results, Fig. 5, clearly

indicate that the designed digital controllers are regulating the

load voltage to the reference value of 36 V and exhibiting

faster dynamics response against source and load

disturbances.

-50

0

50

100

M

a

g

n

i

t

u

d

e

(

d

B

)

10

0

10

1

10

2

10

3

10

4

10

5

-270

-180

-90

0

90

P

h

a

s

e

(

d

e

g

)

Bode Diagram

Frequency (Hz)

Ti

Tv

T1

Fig. 3. Frequency response bode plot of Ti, Tv, overall loopgain T transfer

functions.

1140

(a) Load perturbation (R: 52 26 )

(b) Source perturbation (Vg: 15 19 V)

Fig. 4. Simulated dynamic response of the load voltage.

(a) Load resistance perturbation (R: 52 26 )

(b) Source voltage perturbation (Vg: 15 19 V)

Fig. 5. Measured dynamic response of the load voltage.

V. CONCLUSION

Digital two-loop controller was designed for fourth order

split inductor converter. The comparative study shown that

the proposed converter has resulted in better performance

over the conventional SEPIC converter. Digital two-loop

controller, with inner current-loop and outer voltage-loop has

resulted better dynamic response against the source and load

perturbations. Simulation and experimental were in close

agreement with each other and thus validating the controller

design.

REFERENCES

[1] Veerachary. M, ``Two-loop voltage-mode control of coupled inductor

step-down buck converter,'' IEE Proc. On Electric Power Applications,

Vol. 152(6), pp. 1516 - 1524, 2005.

[2] Jian Liu, Zhiming Chen, Zhong Du, A new design of power supplies

for pocket computer system, IEEE Trans. on Ind. Electronics, 1998,

Vol. 45(2), pp. 228-234.

[3] Barrado. A, Lazaro. A and etc, "Linear-non-linear control for DCDC

Buck converters: stability and transient response analysis", IEEE

Applied Power Electronics Conf. (APEC), 2004, pp.1329 - 1335.

[4] B. Krishna Mohan, Robust Digital Voltage-mode Controller for fifth

order Boost Converter, IEEE Trans. Ind. Electron., Jan. 2011, vol.58,

no.1, pp. 263-277.

1141

[5] M. Veerachary, "Design of Robust Digital PID Controller for H-Bridge

Soft-Switching Boost Converter," IEEE Trans. Ind. Electron., July

2011, vol. 58, no.7, pp. 2883-2897.

[6] Sungsik Park, Sewan Choi, Soft Switched CCM Boost Converters

With High Voltage Gain For High-Power Applications, IEEE Trans.

On Power Electronics, 2010, Vol. 25(5), pp. 1211-1217.

[7] R. Sekhar, Digital Voltage-mode Controller Design for High gain

Soft-Switching Boost Converter, IEEE Proc. on PEDES2010, Dec.

2010, pp. 1-5.

[8] Jianping Xu and C.Q.Lee, Unified Averaging Technique for the

Modeling of Quasi-Resonant Converters, IEEE Transactions on Power

Electronics, Vol. 13(3), 1998, pp. 556-563.

[10] A. C. Bartlett, C. V. Hollot, and H. Lin, Root locations for a polytope

of polynomials: Check the edges, Math. Contro., Signals Syst., 1988,

no. 1, pp. 61-71.

[11] H. Chapellat, and S. P. Bhattacharyya, "A Generalization of

Kharitonov's theorem: Robust Stability of Interval Plants," IEEE Trans.

on Automat. Contr., Mar. 1989, vol. AC34, no.3, pp. 306-311.

[12] A. Katbab and E. I. Jury, "Robust Schur-stability of Discrete-Time

Interval Plants," IEEE Proc. on American Control Conference, 1990,

vol. 51, no. 6, pp. 1343-1352.

[13] MATLAB, user manual, 2005.

[14] PSIM, user manual, 2005.

[15] dSPIC30F2020, Microchip, user manual, 2009.

1142

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Cascade Controller For DCDC Buck ConvertorDocument6 pagesCascade Controller For DCDC Buck ConvertorCristóbal Eduardo Carreño MosqueiraNo ratings yet

- Predictive Current Controlled 5-kW Single-Phase Bidirectional Inverter With Wide Inductance Variation For DC-Microgrid ApplicationsDocument9 pagesPredictive Current Controlled 5-kW Single-Phase Bidirectional Inverter With Wide Inductance Variation For DC-Microgrid ApplicationsJitender KaushalNo ratings yet

- Electronics 11 01693Document20 pagesElectronics 11 01693Bùi Quốc DuyNo ratings yet

- Transformer Less DC - DC Converter With High Step Up Voltage Gain MethodDocument6 pagesTransformer Less DC - DC Converter With High Step Up Voltage Gain Methodsurendiran123No ratings yet

- Two-Loop Hysteretic Control of 3 Order Buck Converter: M. Veerachary and Deepen SharmaDocument8 pagesTwo-Loop Hysteretic Control of 3 Order Buck Converter: M. Veerachary and Deepen SharmaDeepen SharmaNo ratings yet

- Ijre 3 An Integrated DC DC Converter Topology With Buck and Boost Outputs V3i1 3113Document3 pagesIjre 3 An Integrated DC DC Converter Topology With Buck and Boost Outputs V3i1 3113KEERTHY SNo ratings yet

- 3939 Ijet IjensDocument9 pages3939 Ijet IjensGarudaOzoNo ratings yet

- Boost Converter Based On State Space Modeling Ebrahimi2015Document7 pagesBoost Converter Based On State Space Modeling Ebrahimi2015shrikrisNo ratings yet

- An Introduction To Sepic ConverterDocument2 pagesAn Introduction To Sepic Converterleemoh8190No ratings yet

- Fuzzy Logic Controlled Bidirectional DC-DC Converter Applied To DC DriveDocument12 pagesFuzzy Logic Controlled Bidirectional DC-DC Converter Applied To DC DriveTJPRC PublicationsNo ratings yet

- Bidirectional DC To DC Converters: An Overview of Various Topologies, Switching Schemes and Control TechniquesDocument6 pagesBidirectional DC To DC Converters: An Overview of Various Topologies, Switching Schemes and Control TechniquesVo Thanh TungNo ratings yet

- ICPE11 ImplDocument8 pagesICPE11 Implhans_fitz4134No ratings yet

- Current Mirror 1Document5 pagesCurrent Mirror 1Shaheer DurraniNo ratings yet

- Single-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeDocument12 pagesSingle-Inductor Multiple-Output Switching Converters With Time-Multiplexing Control in Discontinuous Conduction ModeZhongpeng LiangNo ratings yet

- Bidirectional DC-DC Converter Based On Quasi-Sepic For Battery Charging SystemDocument9 pagesBidirectional DC-DC Converter Based On Quasi-Sepic For Battery Charging SystemRofiqun NobiNo ratings yet

- Bidirectional LLC Resonant Converter For Energy Storage ApplicationsDocument7 pagesBidirectional LLC Resonant Converter For Energy Storage ApplicationsRodrigo MesquitaNo ratings yet

- Analysis of Single Switch Step Up DC-DC Converter For Alternative Energy SystemsDocument6 pagesAnalysis of Single Switch Step Up DC-DC Converter For Alternative Energy SystemsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Analysis and Design of A Bidirectional Isolated DC-DC Converter For Fuel Cell and Super-Capacitor Hybrid SystemDocument13 pagesAnalysis and Design of A Bidirectional Isolated DC-DC Converter For Fuel Cell and Super-Capacitor Hybrid SystemHernandaBudiSantosoNo ratings yet

- Closed Loop Control Design of Two Inductor Current-Fed Isolated DC-DC Converter For Fuel Cells To Utility Interface ApplicationDocument8 pagesClosed Loop Control Design of Two Inductor Current-Fed Isolated DC-DC Converter For Fuel Cells To Utility Interface ApplicationNagababuMutyalaNo ratings yet

- Sepic ReportDocument55 pagesSepic ReportHEERAVATHINo ratings yet

- AarthiDocument10 pagesAarthiSoniya CsNo ratings yet

- Dynamic Modeling and Controller Design For A SinglDocument13 pagesDynamic Modeling and Controller Design For A SinglSkp FANo ratings yet

- Power Converters, Control, and Energy Management For Distributed GenerationDocument5 pagesPower Converters, Control, and Energy Management For Distributed GenerationAbdelaziz IsmealNo ratings yet

- LED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForDocument5 pagesLED Applications Design and Implementation of A Novel Bridgeless Interleaved SEPIC Converter ForArun KumarNo ratings yet

- Cta 2701Document25 pagesCta 2701pedroNo ratings yet

- IET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsDocument10 pagesIET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsHsekum RamukNo ratings yet

- Compact Dualoutput Inverter Based On Flyingcapacitor Modelling Control and Prototype ValidationDocument8 pagesCompact Dualoutput Inverter Based On Flyingcapacitor Modelling Control and Prototype ValidationkhasimNo ratings yet

- A Parallel-Resonant Isolated Bidirectional DC-DC Converter With Low Current Ripple For Battery Storage SystemsDocument6 pagesA Parallel-Resonant Isolated Bidirectional DC-DC Converter With Low Current Ripple For Battery Storage SystemsSaurabh KaduskarNo ratings yet

- State Space Averaging Model of Boost ConvDocument60 pagesState Space Averaging Model of Boost ConvBharti Thakur100% (1)

- An Interleaved Bi-Directional AC-DC ConverterDocument5 pagesAn Interleaved Bi-Directional AC-DC ConverterAsad HameedNo ratings yet

- ELEC 6411 - Project Final FinalDocument30 pagesELEC 6411 - Project Final FinalAndrewJohnsonJenssonNo ratings yet

- 10.1007@s00202 019 00901 XDocument12 pages10.1007@s00202 019 00901 XfarhaniNo ratings yet

- Closed Sepic1Document6 pagesClosed Sepic1Thimothy BasavaNo ratings yet

- Modelling and Simulation of High Step Up DC To AC Converter For Microsource ApplicationDocument5 pagesModelling and Simulation of High Step Up DC To AC Converter For Microsource ApplicationtheijesNo ratings yet

- Soft Switched High Step-Up DC-DC Converter For Automotive ApplicationDocument4 pagesSoft Switched High Step-Up DC-DC Converter For Automotive Applicationkarthi.r.tNo ratings yet

- A Boost Converter With Capacitor Multiplier and Coupled Inductor For AC Module ApplicationsDocument9 pagesA Boost Converter With Capacitor Multiplier and Coupled Inductor For AC Module ApplicationsChinni NeeluNo ratings yet

- ModelingandSimulationofDC DCConvertersDocument13 pagesModelingandSimulationofDC DCConvertersSureshkumar AlagarsamyNo ratings yet

- Step Down PSIMDocument6 pagesStep Down PSIMAnonymous W44hzJ9roNo ratings yet

- A Two Stage Buck Boost Converter With SoDocument7 pagesA Two Stage Buck Boost Converter With Sodd1663No ratings yet

- Bridgeless AC-DC Buck-Boost Converter WithDocument5 pagesBridgeless AC-DC Buck-Boost Converter WithJishnu VenugopalNo ratings yet

- High-Efficiency Bidirectional DC - DC Converter With High-Voltage GainDocument12 pagesHigh-Efficiency Bidirectional DC - DC Converter With High-Voltage GainghiocelNo ratings yet

- A Modified DC Power Electronic TransformerDocument15 pagesA Modified DC Power Electronic TransformerArun KumarNo ratings yet

- Final ReportDocument88 pagesFinal ReportYOKESH BNo ratings yet

- Design and Implementation of Luo Converter For Electric Vehicle ApplicationsDocument5 pagesDesign and Implementation of Luo Converter For Electric Vehicle ApplicationsseventhsensegroupNo ratings yet

- Continuous Conduction Mode of Bridgeless SEPIC Power Factor Correction RectifierDocument4 pagesContinuous Conduction Mode of Bridgeless SEPIC Power Factor Correction Rectifiersindhuja selvamNo ratings yet

- 2 Bobine CuplateDocument26 pages2 Bobine CuplateParvulescu Mihai LucianNo ratings yet

- Ijert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterDocument9 pagesIjert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterAnjali SharmaNo ratings yet

- Design of Transformer-Less DC To AC Converter Using PWM TechniqueDocument6 pagesDesign of Transformer-Less DC To AC Converter Using PWM TechniqueHariesh WaranNo ratings yet

- Efficiency and Cost Optimization of Dual Active Bridge Converter For 350kW DC Fast ChargersDocument6 pagesEfficiency and Cost Optimization of Dual Active Bridge Converter For 350kW DC Fast ChargersJaja LocoNo ratings yet

- Modelling Bidirectional Buck BoostDocument7 pagesModelling Bidirectional Buck BoostAkay HanafiahNo ratings yet

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDocument14 pagesWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06No ratings yet

- Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterDocument9 pagesTwo-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterRaveendhra IitrNo ratings yet

- Large Step Ratio Input-Series-Output-Parallel Chain-Link DC-DC ConverterDocument12 pagesLarge Step Ratio Input-Series-Output-Parallel Chain-Link DC-DC ConverterArunavaNo ratings yet

- A Single-Switch Transformerless DC-DC Converter With Universal Input Voltage For Fuel Cell Vehicles: Analysis and DesignDocument13 pagesA Single-Switch Transformerless DC-DC Converter With Universal Input Voltage For Fuel Cell Vehicles: Analysis and DesignahmedNo ratings yet

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDocument9 pagesHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNo ratings yet

- Voltage-Lift-Type Cu K Converters: Topology and Analysis: M. Zhu F.L. LuoDocument14 pagesVoltage-Lift-Type Cu K Converters: Topology and Analysis: M. Zhu F.L. LuomenguemengueNo ratings yet

- Hybrid Switched-Inductor Converters For High Step-Up ConversionDocument11 pagesHybrid Switched-Inductor Converters For High Step-Up ConversionRahim SamanbakhshNo ratings yet

- Design of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemDocument6 pagesDesign of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemRaveendhra IitrNo ratings yet

- Telephone Directory: Telephone Exchange Indian Institute of Technology Roorkee ROORKEE - 247 667 June - 2017Document72 pagesTelephone Directory: Telephone Exchange Indian Institute of Technology Roorkee ROORKEE - 247 667 June - 2017Raveendhra IitrNo ratings yet

- High Power Topology: "AlbacomDocument7 pagesHigh Power Topology: "AlbacomRaveendhra IitrNo ratings yet

- Bi-Directional Fonvard-Flyback DC-DC Converter: IEEE PowerDocument4 pagesBi-Directional Fonvard-Flyback DC-DC Converter: IEEE PowerRaveendhra IitrNo ratings yet

- Design of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemDocument6 pagesDesign of A Single-Switch DC-DC Converter For PV-Battery Powered Pump SystemRaveendhra IitrNo ratings yet

- A New Single Switch Buck-Boost Type DC-DC ConverterDocument4 pagesA New Single Switch Buck-Boost Type DC-DC ConverterRaveendhra IitrNo ratings yet

- Synthesis and Analysis of A Multiple-Input Parallel SC DC-DC ConverterDocument4 pagesSynthesis and Analysis of A Multiple-Input Parallel SC DC-DC ConverterRaveendhra IitrNo ratings yet

- High Performance DC-DC Converter For Wide Voltage Range OperationDocument8 pagesHigh Performance DC-DC Converter For Wide Voltage Range OperationRaveendhra IitrNo ratings yet

- 0628-1 Course MinhCTaDocument1 page0628-1 Course MinhCTaRaveendhra IitrNo ratings yet

- Design of Robust Digital PID Controller For H-Bridge Soft-Switching Boost ConverterDocument15 pagesDesign of Robust Digital PID Controller For H-Bridge Soft-Switching Boost ConverterRaveendhra IitrNo ratings yet

- Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterDocument9 pagesTwo-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterRaveendhra IitrNo ratings yet

- Based Power Tracking For Nonlinear PV SourcesDocument8 pagesBased Power Tracking For Nonlinear PV SourcesRaveendhra IitrNo ratings yet

- Maximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemDocument10 pagesMaximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemRaveendhra IitrNo ratings yet

- 19-GB 50030-91氧气站设计规范en PDFDocument34 pages19-GB 50030-91氧气站设计规范en PDFyyyy071220No ratings yet

- 1308020EN Electrical EngineeringDocument20 pages1308020EN Electrical EngineeringamrehmaniNo ratings yet

- Lexmark C91x C912 5505 Service ManualDocument492 pagesLexmark C91x C912 5505 Service ManualMichael HanniganNo ratings yet

- Flow Properties and Design Procedures For Coal Storage Bins PDFDocument401 pagesFlow Properties and Design Procedures For Coal Storage Bins PDFEmaVanni100% (2)

- Grid Station PresentationDocument40 pagesGrid Station Presentationranafaizan773750% (2)

- Manual YbportDocument105 pagesManual YbportMan GeekaaNo ratings yet

- Fro 15210C 0510Document36 pagesFro 15210C 0510davisNo ratings yet

- Research Paper On Building MaterialsDocument7 pagesResearch Paper On Building Materialsafnknlsjcpanrs100% (1)

- Ship Power PlantDocument141 pagesShip Power Plantnguyentrunghieu51dltt100% (2)

- BCS 051 Solved AssignmentsDocument11 pagesBCS 051 Solved AssignmentsAmit GuptaNo ratings yet

- ZK - ZK Component Reference - Essential Components - Fileupload - DocumentationDocument5 pagesZK - ZK Component Reference - Essential Components - Fileupload - DocumentationEmerson JoaquimNo ratings yet

- APX Portable Accessory CatalogDocument12 pagesAPX Portable Accessory Catalogcraig_ochsNo ratings yet

- Flight Management and NavigationDocument18 pagesFlight Management and NavigationmohamedNo ratings yet

- Copyright ProtectionDocument6 pagesCopyright ProtectionKamalbir KaurNo ratings yet

- Mve Vapor Shippers (Regular) - Cryogenic Vapor Shippers - Cryo Cube - Cryo Moover - Mini Moover - Cryo Shipper - Cryo Shipper XCDocument9 pagesMve Vapor Shippers (Regular) - Cryogenic Vapor Shippers - Cryo Cube - Cryo Moover - Mini Moover - Cryo Shipper - Cryo Shipper XCPrincestonNo ratings yet

- ZL300 Main Contact Kit: Product-DetailsDocument3 pagesZL300 Main Contact Kit: Product-DetailsMahyar MashayekhiNo ratings yet

- Mte 3152 Electric Drives Mid TermDocument2 pagesMte 3152 Electric Drives Mid TermAjitash TrivediNo ratings yet

- Inf Luence of Tip Clearance On The Flow Field and Aerodynamic Performance of The Centrif Ugal ImpellerDocument6 pagesInf Luence of Tip Clearance On The Flow Field and Aerodynamic Performance of The Centrif Ugal Impellerarm coreNo ratings yet

- The Sproutling Baby Monitor Keep Tabs On Your Newborn With This Smart Ankle BraceletDocument2 pagesThe Sproutling Baby Monitor Keep Tabs On Your Newborn With This Smart Ankle BraceletAllanStevenNo ratings yet

- CV Shanmugaraj.rDocument2 pagesCV Shanmugaraj.rpreanandNo ratings yet

- Pipe Size CalculationDocument42 pagesPipe Size CalculationfelipeNo ratings yet

- Design Planning Records Center of The Future 2004-10Document29 pagesDesign Planning Records Center of The Future 2004-10Talam KeladiNo ratings yet

- Solar Photovoltaic Wire 600V: DescriptionDocument1 pageSolar Photovoltaic Wire 600V: DescriptionAMARENDRA SINo ratings yet

- Coolant Contains Oil: TroubleshootingDocument2 pagesCoolant Contains Oil: TroubleshootingPutra JawaNo ratings yet

- Industrial Automation Technical Interview QuestionsDocument27 pagesIndustrial Automation Technical Interview Questionsanon_680083156100% (1)

- MASTER FLOW p2 - BB - 6000 - NewDocument4 pagesMASTER FLOW p2 - BB - 6000 - NewJosé Daniel ArenasNo ratings yet

- Construction Material Lecture NoteDocument12 pagesConstruction Material Lecture NoteMohamedNo ratings yet

- Tech Paper Performance Analysis of 6 Axis RobotDocument10 pagesTech Paper Performance Analysis of 6 Axis RobotSyahril PabloNo ratings yet

- 2D CFD Transient Analysis of Darrieus H Type Vertical Axis Wind TurbineDocument43 pages2D CFD Transient Analysis of Darrieus H Type Vertical Axis Wind TurbinekaushikNo ratings yet

- Information Gain CalculatorDocument16 pagesInformation Gain CalculatorShashiBhushanSahani0% (1)