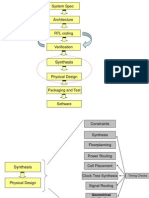

Professional Documents

Culture Documents

Keeping The Clock Pure: Review of Timing Properties of Flip-Flops

Keeping The Clock Pure: Review of Timing Properties of Flip-Flops

Uploaded by

ShwetabhAsthanaCopyright:

Available Formats

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- TTTTT Eeee AsDocument20 pagesTTTTT Eeee AsEric GongNo ratings yet

- Setup1 1210Document32 pagesSetup1 1210Akhila PurushothamanNo ratings yet

- Understanding Sequential Circuit TimingDocument8 pagesUnderstanding Sequential Circuit Timingchuku7No ratings yet

- Clocking Part 2Document4 pagesClocking Part 2Dmitry LeyzerovichNo ratings yet

- What Is STA ?Document13 pagesWhat Is STA ?veeru100% (1)

- Sequential LogicDocument68 pagesSequential LogicbabahussainNo ratings yet

- Exp D - FFDocument5 pagesExp D - FFalokjadhavNo ratings yet

- Notes 326 Set12 PDFDocument17 pagesNotes 326 Set12 PDFEswaran SamyNo ratings yet

- Sequential & Combinational Timing AnalysisDocument8 pagesSequential & Combinational Timing AnalysisSahil SharmaNo ratings yet

- Timing Analysis: Elec 326 Sequential Circuit TimingDocument43 pagesTiming Analysis: Elec 326 Sequential Circuit TimingArpit KapoorNo ratings yet

- Timing AnalysisDocument15 pagesTiming Analysissophieee19No ratings yet

- Clock BuffersDocument29 pagesClock Buffersnaveen silveri100% (2)

- 74HC190 DatasheetDocument14 pages74HC190 Datasheetmym786No ratings yet

- 74HC190Document13 pages74HC190Enzo Paolo D'Angelo0% (1)

- Digital Integrated CircuitsDocument10 pagesDigital Integrated CircuitsshahanisubhashNo ratings yet

- Timing Issues in CircuitsDocument15 pagesTiming Issues in CircuitsNiloy RoyNo ratings yet

- Timing Issues in Digital ASIC DesignDocument101 pagesTiming Issues in Digital ASIC Designnsai_vs1513No ratings yet

- Timing Analysis: Supplementary NotesDocument6 pagesTiming Analysis: Supplementary NotesSRINIKHIL GollaNo ratings yet

- 74 HC 165Document11 pages74 HC 165Negru P. PlantatieNo ratings yet

- Sequential Logic and Memory ComponentsDocument9 pagesSequential Logic and Memory ComponentsShashank MishraNo ratings yet

- HD74HC164PDocument7 pagesHD74HC164Prakzo10No ratings yet

- 74HC165 8-Bit PISO Shift RegisterDocument10 pages74HC165 8-Bit PISO Shift Registeroscar_ceja_02No ratings yet

- ChapterDocument80 pagesChapterAshish VermaNo ratings yet

- STI - FSM - SolutionsDocument6 pagesSTI - FSM - SolutionsAishwarya GajendrulaNo ratings yet

- Static Timing AnalysisDocument32 pagesStatic Timing AnalysisShantanu Sarkar100% (1)

- Timing in Digital Circuits - NotesDocument9 pagesTiming in Digital Circuits - NotesKowshick GuruNo ratings yet

- EE 459/500 - HDL Based Digital Design With Programmable Logic Timing and Clock IssuesDocument23 pagesEE 459/500 - HDL Based Digital Design With Programmable Logic Timing and Clock Issuessneha96669No ratings yet

- Timing Issues in Digital Circuits: Edge-Triggered D Flip FlopDocument4 pagesTiming Issues in Digital Circuits: Edge-Triggered D Flip FlopBinh NguyenNo ratings yet

- Cse477 19 TimingDocument23 pagesCse477 19 TimingMahmoud Abd El LatifNo ratings yet

- Significance of Contamination Delay: Nima Afraz Advisor: DR - Jahanian For The Advanced VLSI CourseDocument7 pagesSignificance of Contamination Delay: Nima Afraz Advisor: DR - Jahanian For The Advanced VLSI CourseNima AfrazNo ratings yet

- Clock Period: 1 Setup and Hold PeriodsDocument8 pagesClock Period: 1 Setup and Hold PeriodslitoduterNo ratings yet

- 6 TimingDocument33 pages6 Timingwqy15902896758No ratings yet

- Synchronous: Sequential LogicDocument67 pagesSynchronous: Sequential LogickenNo ratings yet

- PAGE10Document4 pagesPAGE10praveenmorampudi42No ratings yet

- Lect17 SeqDocument18 pagesLect17 SeqorengeneralNo ratings yet

- Meta StabilityDocument16 pagesMeta StabilitySahil SharmaNo ratings yet

- Data SheetDocument10 pagesData SheetShowPieceNo ratings yet

- E2.11/ISE2.22 - Digital Electronics IIDocument5 pagesE2.11/ISE2.22 - Digital Electronics IIDivya MittalNo ratings yet

- Digital Integrated CircuitsDocument60 pagesDigital Integrated CircuitsSara SaleemNo ratings yet

- CMOS Sequential Circuit Design Lec.-1Document22 pagesCMOS Sequential Circuit Design Lec.-1Parag ParandkarNo ratings yet

- Flip-Flops & Latches: Digital ElectronicsDocument20 pagesFlip-Flops & Latches: Digital ElectronicsGowtham PalanirajanNo ratings yet

- Experiment No. 3.1Document5 pagesExperiment No. 3.1Harshal AmbatkarNo ratings yet

- 74 HC 73Document7 pages74 HC 73Jorge Alberto100% (1)

- Setup and Hold Time CalculationsDocument33 pagesSetup and Hold Time CalculationsRashmi Periwal100% (11)

- 74 HC 163Document12 pages74 HC 163Pablo Petrowitsch CrignolaNo ratings yet

- MIT6004 S 09 Tutor 06Document7 pagesMIT6004 S 09 Tutor 06Abhijith RanguduNo ratings yet

- STA FinalDocument66 pagesSTA FinalgauravkshriNo ratings yet

- Timing Parameters of A Digital CircuitDocument7 pagesTiming Parameters of A Digital CircuitShwetabhAsthanaNo ratings yet

- 74 HC 191Document10 pages74 HC 191Ravi RathodNo ratings yet

- 74LS74 PDFDocument3 pages74LS74 PDFDeni KhanNo ratings yet

- Chapter2 Clocks Resets-04Document8 pagesChapter2 Clocks Resets-04hardeepNo ratings yet

- Setup HoldDocument22 pagesSetup HoldAnuja BagdiNo ratings yet

- FlipflopsDocument80 pagesFlipflopsvikramkolanuNo ratings yet

- Race Hazards, Clock Skew, Cross Simulation & Intra-Assignment DelaysDocument4 pagesRace Hazards, Clock Skew, Cross Simulation & Intra-Assignment Delaysश्रेयस देशमुखNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Instruments and MeasurementsFrom EverandInstruments and MeasurementsBirger QvarnstromNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Chapter 4:ujt: Uni-Junction Transistor G.Venkatasubbaiah Asst., Professor Dept., of ECE VrsecDocument8 pagesChapter 4:ujt: Uni-Junction Transistor G.Venkatasubbaiah Asst., Professor Dept., of ECE VrsecSai RohithNo ratings yet

- Series Voltage RegulatorDocument43 pagesSeries Voltage RegulatorI-A-42 Khushalsingh Dilipsingh BharadwajNo ratings yet

- Introduction - Combinational LogicDocument10 pagesIntroduction - Combinational LogicPriyadarshini NNo ratings yet

- ADC0820 8-Bit High Speed P Compatible A/D Converter With Track/Hold FunctionDocument23 pagesADC0820 8-Bit High Speed P Compatible A/D Converter With Track/Hold Functionjohndone2009No ratings yet

- Can Bus MicrocontrollersDocument28 pagesCan Bus MicrocontrollersFrank CollinsNo ratings yet

- SAED Cell Lib Rev1 4 20 1 PDFDocument100 pagesSAED Cell Lib Rev1 4 20 1 PDFPradeep RoyalNo ratings yet

- IC TesterDocument2 pagesIC TestervaibhavgijareNo ratings yet

- SN74HCS7266 Quadruple 2-Input XNOR Gates With Schmitt-Trigger InputsDocument22 pagesSN74HCS7266 Quadruple 2-Input XNOR Gates With Schmitt-Trigger InputsNicanor Fotsing tenoNo ratings yet

- Time To Digital Converter SlidesDocument12 pagesTime To Digital Converter SlidesburakgonenNo ratings yet

- Arduino Based Pulse Width Modulated Outp PDFDocument5 pagesArduino Based Pulse Width Modulated Outp PDFArif Johar TaufiqNo ratings yet

- Advanced CMOS CircuitsDocument20 pagesAdvanced CMOS CircuitsAnonymous IXvuFdeNo ratings yet

- 7400 FamiliesDocument16 pages7400 FamiliesMini DachshundNo ratings yet

- MX27C1000A: PreliminaryDocument15 pagesMX27C1000A: PreliminaryVictor TruccoNo ratings yet

- BMRDocument5 pagesBMRTaeho James KimNo ratings yet

- Analog & Digital VLSI Design Handout - RevisedDocument3 pagesAnalog & Digital VLSI Design Handout - RevisedB Naresh Kumar ReddyNo ratings yet

- Phys 419 Comm ElectronicsDocument3 pagesPhys 419 Comm ElectronicsJoram MuiruriNo ratings yet

- A New Read Circuit For Multi-Bit Memristor-Based Memories Based On Time To Digital Sensing CircuitDocument5 pagesA New Read Circuit For Multi-Bit Memristor-Based Memories Based On Time To Digital Sensing CircuitHussain Bin AliNo ratings yet

- 74AHC04 74AHCT04: 1. General DescriptionDocument17 pages74AHC04 74AHCT04: 1. General DescriptionalexNo ratings yet

- Student Manual For The Art of Electronics: Thomas C. Hayes Paul HorowitzDocument5 pagesStudent Manual For The Art of Electronics: Thomas C. Hayes Paul Horowitzcokeaddict56No ratings yet

- The Valve Wizard - Tremolo OscillatorDocument3 pagesThe Valve Wizard - Tremolo Oscillatormorag142No ratings yet

- Radio-Frequency Circuits6Document18 pagesRadio-Frequency Circuits6mumtazNo ratings yet

- Chapter 4: Differential AmplifiersDocument60 pagesChapter 4: Differential AmplifiersallachandrahasNo ratings yet

- Electronic Devices and Circuit Theory: Bipolar Junction TransistorsDocument26 pagesElectronic Devices and Circuit Theory: Bipolar Junction TransistorsKavinesh AnanthanNo ratings yet

- Topic 6 Basic Electronics - TransistorDocument66 pagesTopic 6 Basic Electronics - TransistorJENNIFER SERVONo ratings yet

- VLSI Interview Questions - 1Document9 pagesVLSI Interview Questions - 1samNo ratings yet

- Probsolall PDFDocument51 pagesProbsolall PDFnicole deleonNo ratings yet

- lm358 PDFDocument3 pageslm358 PDFerwin2590No ratings yet

- Host-Controlled Multi-Chemistry Battery Charger With System Power Selector, AC Over-Power Protection, and Programmable OVPDocument39 pagesHost-Controlled Multi-Chemistry Battery Charger With System Power Selector, AC Over-Power Protection, and Programmable OVPCaminera TruckNo ratings yet

- Srikant H 2016Document4 pagesSrikant H 2016venkat301485No ratings yet

- R 2 R Ladder DAC PDFDocument3 pagesR 2 R Ladder DAC PDFSudershan DolliNo ratings yet

Keeping The Clock Pure: Review of Timing Properties of Flip-Flops

Keeping The Clock Pure: Review of Timing Properties of Flip-Flops

Uploaded by

ShwetabhAsthanaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Keeping The Clock Pure: Review of Timing Properties of Flip-Flops

Keeping The Clock Pure: Review of Timing Properties of Flip-Flops

Uploaded by

ShwetabhAsthanaCopyright:

Available Formats

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-1

Keeping The Clock Pure

or alternately

Making The Impurities Digestible

Timing is everything.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-2

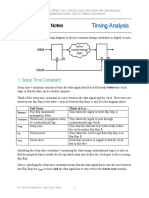

Review of Timing Properties of Flip-Flops

Setup Time and Hold Time

FIG. 4-2 .

The setup time is the interval before the clock where the data must be held stable.

The hold time is the interval after the clock where the data must be held stable.

Most modern ip-ops have a zero or a negative hold time.

A negative hold time means the data can change slightly before the clock edge and

still be properly captured.

D

C

Q

CLOCK

INPUT

INPUT

Q

CLOCK

Hold time

Setup time

Region where data must hold still

Hold time

Setup time

negative

Every ip-op has time regions around the active clock edge in which the input should not change

If the input changes in these restricted regions, the output may be derived from either:

the old input, the new input, or even half-way in between.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-3

Synchronous and Asynchronous Signals

Summary of the Restricted Region

The restricted region:

Time interval near the active clock edge where the D input signal should not change.

Otherwise the ip-ops output,

after the clock edge, may:

1) follow the change in D.

2) not follow D.

3) follow it halfway (go metastable).

Synchronous and Asynchronous Signals

A synchronous signal

One which is constrained so it cannot change in the restricted region.

An asynchronous signal

can and will change anywhere.

D INPUT

Q

CLOCK

Hold time

Setup time

Q followed D

Q did not follow D Q

Q

metastable

Q went

Restricted Region

1)

2)

3)

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-4

Synchronous and Asynchronous Signals

FIG. 4-3 Three different D inputs.

The upper two are synchronous;

they do not change in the restricted region.

The lower one is asynchronous;

it has a transition inside the restricted region.

The Clock-to-Output Propagation Delay, t

CHQV

The time from the active clock edge until the Q output changes.

Another name is t

CHQV

(time from Clock going High to Q becoming Valid).

Any reasonable ip-op will have t

CHQV

> t

HOLD.

This is essential in shift-registers.

1D

C1

Q

CLOCK

D in

D in; Synchronous

CLOCK

Restricted Region

D in; Asynchronous

D in; Synchronous

they dont

become

off stage.

Assume

asynchronous

Q

CLOCK

t

CHQV

Clock High to Q Valid

D

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-5

Synchronous and Asynchronous Signals

The Output Signal From a Clocked Flip-Flop is Always Synchronous

Any signal which passes through a ip-op is synchronous.

The delay t

CHQV,

is enough to move Q changes out of the restricted region.

The Q signal in below is synchronous.

It results from passing signal Din through a D ip-op.

FIG. 4-4 The Q output is always synchronous, even if the input D signal is not.

The internal propagation delay moves any change out of the restricted region.

This assumes t

CHQV

> t

HOLD

D

C

Q

CLOCK

Din

Din; Asynchronous

CLOCK

Restricted Region

Q; Synchronous t

CHQV

t

CHQV

t

HOLD

t

HOLD

Q might not change, but if it does, it

will be a synchronous change.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-6

Maximum and Minimum Delays With a Perfect

Clock-to-Clock Logic Propagation Delays.

Maximum and Minimum Delays With a Perfect Clock

Maximum Logic Propagation Delays

Consider a synchronous circuit made of ip-ops with logic in between them.

FIG. 4-5 One ip-op feeding through logic into another ip-op.

The signal must get from the rst ip-op to the next, in one clock cycle, thus -

t

CLOCK

t

CHQV

+ t

PD

+ t

SETUP

or

D

C

Q

2

The Q

1

signal takes t

CHQV

to get out of the left ip-op.

The propagation delay through the gate(s) is t

PD.

The D

2

signal must arrive at the right ip-op at least t

SETUP

before the second clock edge.

D

C

Q

1 D

2

D

1

tC

H

Q

V

t

SETUP

t

PD

t

CLOCK

t

CHQV

+ t

PD

+ t

SETUP

t

PD

t

CLOCK

- t

SETUP

- t

CHQV

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-7

Maximum and Minimum Delays With a Perfect

FIG. 4-6 The maximum logic delay in a synchronous circuit

D

C

Q

2

D

1

Q

1

CLOCK

Setup time

Region where D

2

may change

Hold time

t

SETUP

The Q

1

signal takes t

CHQV

to get out of the left ip-op.

The D

2

signal must arrive at the right ip-op at least t

SETUP

before the second clock edge.

The gate delay, t

PD,

could take up the rest of the clock cycle.

Call the longest allowable gate delay t

PD(MAX)

t

D

C

Q

1

D

2

Q

2

t

CHQV

t

CLOCK

t

PD(MAX)

t

CLOCK

= t

CHQV

+ t

PD(MAX)

+ t

SETUP

D

2

D

1

t

CHQV

t

SETUP

t

PD

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-8

Maximum and Minimum Delays With a Perfect

Minimum Logic Propagation Delays.

One can have a valid minimum gate propagation delay.

This is when t

CHQV

< t

HOLD

.

Think of two ip-ops clocked on the same edge.

For a long hold time,

one ip-op can ip

within the long hold time,

and send its new output to the next ip-op

fast enough to ip it on the same clock edge.

To avoid double ips:

t

HOLD

t

CHQV

+ t

PD

or

t

PD

t

HOLD

- t

CHQV

The propagation delay of the gate(s)

must be above the minimum allowable,

t

PD(MIN)

= t

HOLD

- t

CHQV

FIG. 4-7 A dynamic ip-op in which t

CHQV

< t

HOLD

.

Q2

D

C

Q1

D2

D1

t

CHQV

t

PD

D

C

D

C

t

CHQV

C

D

SW

C

Q

Q

t

HOLD

Q

SW

SW

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-9

Maximum and Minimum Delays With a Perfect

Minimum Propagation Delay Repeated; Different Pictures.

D

1

Q

1

CLOCK

The minimum delay appears when the ip-op has a hold time longer than t

CHQV

.

Then D

1

can ip Q

1

of the upper ip-op,

travel through the gate and reach the lower ip-op

inside its hold time.

In that case the lower ip-op may change too on the same clock edge!

D

2

Q

2

t

CHQV

t

HOLD

t

PD(MIN)

t

HOLD

= t

CHQV

+ t

PD(MIN)

t

HOLD

D

2

is just a little early, inside the

Q

2

changed, when it should

have waited till the next active

hold time.

Excessively long hold time

clock edge.

D

C

Q2

D

C

Q1

D2

D1

t

CHQV

t

PD

Very small

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-10

Minimum and Maximum Logic Delays With

Minimum and Maximum Logic Delays With Clock Skew.

Clock Skew

Clock skew

is when the clock edge does not reach all the ip-ops at the same time.

Positive skew

Dene skew as positive when

the data and clock are delayed in the same direction.

In most schematics

the right (or bottom) ip-op will receive the delayed clock.

Maximum Logic Delays With Clock Skew

Positive skew increases the time available to get to the right-hand ip-op.

From FIG. 4-8

D

C

Q

2

D

C

Q

1 D

2

D

1

t

PD

t

SKEW

t

CLOCK

+ t

SKEW

= t

CHQV

+ t

PD(MAX)

+ t

SETUP

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-11

Minimum and Maximum Logic Delays With

FIG. 4-8 Positive Clock Skew Increases tPD(MAX)

D

C

Q

2

D

1

Q

1

CLOCK

1

t

SETUP

t

SETUP

If there is a positive skew in the clock, there is more time to get to the right hand ip-op,

and t

PD(MAX)

is increased by the amount of the skew.

D

C

Q

1

D

2

Q

2

t

CHQV

t

CLOCK

+ t

SKEW

t

PD(MAX)

t

CLOCK

+ t

SKEW

= t

CHQV

+ t

PD(MAX)

+ t

SETUP

D

2

D

1

t

CHQV

t

SETUP

t

PD

CLOCK

2

t

SKEW

t

CLOCK

t

SKEW

CLOCK

1

CLOCK

2

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-12

Minimum and Maximum Logic Delays With

Minimum Logic Delays With Clock Skew

See FIG. 4-9

The minimum logic delay t

PD(MIN)

is made worse (increased) by positive skew.

Modern ip-ops have t

HOLD

< t

CHQV,

the minimum allowed prop delay is zero (t

PD(MIN)

= 0).

With skew one may require t

PD(MIN)

> 0.

But shift registers have t

PD

0.

Thus with clock skew, shift registers may fail.

From FIG. 4-9, the limit on minimum delay is -

t

SKEW

+ t

HOLD

= t

CHQV

+ t

PD(MIN)

Thus

t

PD

t

HOLD

+ t

SKEW

- t

CHQV

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-13

Minimum and Maximum Logic Delays With

FIG. 4-9 Minimum propagation delay limit with skew.

D

C

Q

2

D

1

Q

1

CLOCK

1

(a) With positive clock skew, the clock to the lower ip-op is delayed.

The chance of a D

1

change going through both ip-ops in one cycle increases.

The t

SKEW

acts like an increase in the hold time of the lower ip-op.

(b) Waveforms, when skew makes the actual t

PD

< t

PD(MIN)

.

D

C

Q

1

D

2

Q

2

t

CHQV

t

HOLD

t

SKEW

+ t

HOLD

= t

CHQV

+ t

PD(MIN)

D

2

D

1

t

CHQV

t

PD

D

2

is just inside the hold time

Q

2

changed too soon.

t

SKEW

CLOCK

2

t

SKEW

t

PD(MIN)

Gate with

t

PD

<t

PD(MIN)

(a) (b)

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-14

Minimum and Maximum Logic Delays With

PROB 4.1 Maximum Skew For A Shift Register

Find the maximum delay in the clock buffers for the shift register shown.

Thus the delay from CLOCK1 to CLOCK2 may be up to 3 ns.

The delay from CLOCK1 to CLOCK3 may be up to 6 ns

Q

2

1D

C1

Q

1

D

2

D

1

t

CHQV

=2

t

PD

(Q to D) = 0 ns

t

SKEW1-2

CLOCK

1

CLOCK

2

1D

C1

Q

3

D

3

t

SKEW2-3

CLOCK

3

1D

C1

t

CHQV

= 2 ns max

t

HOLD

= -1 ns min

t

PD

t

HOLD

+ t

SKEW

- t

CHQV

t

CHQV

=2

t

PD

=0 t

PD

=0

t

PD

t

HOLD

+ t

SKEW

- t

CHQV

For Q

1

to D

2

For Q

2

to D

3

0 -1 + t

SKEW1-2

- 2 0 -1 + t

SKEW2-3

- 2

t

SKEW1-2

+3 t

SKEW2-3

+3

t

SKEW1-3

= t

SKEW1-2

+ t

SKEW2-3

+6

Solution

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-15

Minimum and Maximum Logic Delays With

PROB 4.2 Maximum Negative Skew For A Shift Register

Find the maximum delay in the clock buffers for the shift-register shown below.

The clock delays now go opposite the data, i.e. t

SKEW

is negative.

This is equivalent to PROB 4.1 with t

SKEW

negative.

Thus

-|t

SKEW1-2

| +3 and -|t

SKEW2-3

| +3

Any negative skews is less than 3 ns,

Thus any negative skew is acceptable.

However watch out if the negative skew approaches a clock period.

Q

2

1D

C1

Q

1

D

2

D

1

t

CHQV

=2 t

PD

(Q to D) = 0 ns

t

SKEW

CLOCK

1

CLOCK

2

1D

C1

Q

3

D

3

t

SKEW

CLOCK

3

1D

C1

t

CHQV

= 2 ns max

t

HOLD

= -1 ns min

t

CHQV

=2

t

PD

=0 t

PD

=0

t

SKEW

= -|t

SKEW

|

t

SKEW

is negative that is

In shift registers, route the clock against the shift.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-16

Minimum and Maximum Logic Delays With

PROB 4.3 Maximum and Minimum Delay With Bounded Skew

Two registers of D ip-ops have a clock skew which is between -3 and 3 ns.

Since we do not know the sign, we must always assume the worst case,

i.e. positive when calculating t

PD(MIN)

and negative when calculating t

PD(MAX)

.

Q

1

is the collective name for any or all outputs of the right-hand register.

D

2

is the same for the inputs of the right-hand register.

Find t

PD (MIN)

and t

PD (MAX)

.

Q

2

1D

C1

Q

1

D

2

D

1

CLOCK

1

CLOCK

2

t

CHQV

= 2 ns max

t

HOLD

= 0 ns min

t

PD

t

HOLD

+ t

SKEW

- t

CHQV

For t

PD(MIN)

t

PD(MIN)

= 0 + 3 - 2

= 1 ns

Solution:

1D

1D

1D

1D

1D

C1

1D

1D

1D

1D

t

PD(MIN)

=?

t

PD(MAX)

=?

COMBINATIONAL

LOGIC

t

SKEW

= t

EDGE-CLOCK2

- t

EDGE-CLOCK2

|t

SKEW

| 3 ns

For t

PD(MAX)

t

PD

t

CLOCK

+ t

SKEW

- t

SETUP

- t

CHQV

t

PD(MAX)

= 20 + (- 3) - 4 - 2

t

SETUP

= 4 ns max

t

CLOCK

= 20 ns

= 11 ns

50 MHz

delay 3

delay 3

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-17

Summary of Simple Propagation Delay Bounds

Summary of Simple Propagation Delay Bounds

Dene positive skew as-

Clock delay in the same direction as data-ow delay, i.e.

t

SKEW

= t

DESTINATION-CLOCK-EDGE

- t

SOURCE-CLOCK-EDGE

then

t

PD(MAX)

= t

CLOCK

+ t

SKEW

- t

CHQV

- t

SETUP

(EQ 1)

t

PD(MIN)

= t

SKEW

+ t

HOLD

- t

CHQV

(EQ 2)

Positive skew:

allows longer logic delays

forces the minimum delay to be longer.

Negative skew:

allows a shorter minimum logic delay

forces the maximum logic delays to be shorter.

Rule of thumb for maximum clock skew

For a modern clock distribution system.

They do not know, or do not have time to examine the logic details.

Assume there may be very fast paths between ip-ops(t

PD(MIN)

=0).

Assume modern ip-ops t

HOLD

0.

Approximate bound on skew, from (EQ 2) is -

(EQ 3)

t

SKEW

t

CHQV

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-18

Summary of Simple Propagation Delay Bounds

Clock Skew Related to Signal Delay

Most circuits do not have a simple structure where one ip-op or register is

the source and another is the destination.

Here we relate clock skew in circuits where the data travels in more complex

paths.

Finding Minimum and Maximum Propagation Delays Given Clock Skew

A register here is a set of edge-triggered simultaneously clocked D ip-ops.

Registers are connected to other registers by combinational logic.

Let the clock skew between registers be known.

We will nd the fast bound t

PD(MIN)

and the slow bound t

PD(MAX)

on the logic

paths between each register pair.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-19

Summary of Simple Propagation Delay Bounds

FIG. 4-10 Figure to establish notation for skew calculations

Q

B

D

B

CLOCK

B

1D

C1

t

PD(MIN)

=?

t

PD(MAX)

=?

COMBINATIONAL

LOGIC

62.5 MHz

Q

A

D

A

CLOCK

A

1D

C1

L

A-B

A B

0 12 34 5 6 7 8 1011121314150 9

0 12 34 5 6 7 8 1011121314150 9

T= 16ns

The registers shown have a common edge-triggered clock input.

The registers bottom block represents one or more ip-ops.

A single line entering or leaving a register, represents 1 or more wires.

The oval L

A-B

represents combinational logic with a source register A and destination register B.

The clock delay for each register is shown by a waveform above the register.

Thus if register-A has the clock edge applied at 0 ns as shown,

then register-B will be clocked at +2 ns.

From the waveforms t

SKEW A-B

= +2 ns.

t

CHQV

= 1 ns max

t

HOLD

= 0 ns min

Period ONE OR MORE

WIRES

t

PD(MIN)

= t

HOLD

+ t

SKEW

- t

CHQV

= 0 + 2 - 1 = 0

t

PD(MAX)

= t

CLOCK

+ t

SKEW

- t

SETUP

- t

CHQV

= 16 + 2 - 3 - 1 = 14

t

SETUP

= 3 ns max

REGISTER

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-20

Summary of Simple Propagation Delay Bounds

FIG. 4-11 More complex interconnections with clock skew.

Q

B D

B

CLOCK

B

1D

C1

62.5 MHz

Q

F D

F

CLOCK

F

1D

C1

Q

E

D

E

CLOCK

E

C1

Q

A D

A

CLOCK

A

1D

C1

LA-B

A B

F

L A-F

L E-F

L F-E

L E-A

L A-E

0 12 34 5 6 7 8 1011121314150 9

L B-F

0 12 34 5 6 7 8 1011121314150 9 0 12 34 5 6 7 8 1011121314150 9

L B-A

0 12 34 5 6 7 8 1011121314150 9

1D

E

T= 16ns

For no clock skew, the propagation delay bounds are

t

PD(MIN)

= t

HOLD

- t

CHQV

= 0 - 1 = -1 (Effectively 0; logic cannot have a negative t

PD)

t

PD(MAX)

= t

CLOCK

- t

SETUP

- t

CHQV

= 16 - 3 - 1 = 12

To add skew, calculate a table of the skew for each logic block, and add it to these base delays.

t

CHQV

= 1 ns max

t

HOLD

= 0 ns min

t

SETUP

= 3 ns max

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-21

Summary of Simple Propagation Delay Bounds

FIG. 4-12 Clock skew, and propagation delay limits assuming no skew.

Source

Reg;

Destination Reg; Clock edge delay

delay A; 0 ns B; 2 ns E; 5 ns F; 3 ns

A; 0 0 2 5 3

B; 2 -2 0 3 1

E; 5 -5 -3 0 -2

F; 3 -3 -1 2 0

Source

Reg;

Destination Reg; Clock edge delay

delay A; 0 ns B; 2 ns E; 5 ns F; 3 ns

A; 0 -1

12

-1

12

-1

12

-1

12

B; 2 -1

12

-1

12

-1

12

-1

12

E; 5 -1

12

-1

12

-1

12

-1

12

F; 3 -1

12

-1

12

-1

12

-1

12

Minimum/maximumt

PD

limits for logic

connected between registers in FIG. 4-11.

No skew.

Table of t

SKEW

between:

source register (listed on the left), and

destination register (listed on the top).

Skew = t

destination

- t

source

t

PD(MIN)

= t

HOLD

- t

CHQV

= -1

t

PD(MAX)

= t

CLOCK

- t

SETUP

- t

CHQV

= 12

No skew

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-22

Summary of Simple Propagation Delay Bounds

FIG. 4-13 Propagation delay limits with skew.

Source

Reg;

Destination Reg; Clock edge delay

delay A; 0 ns B; 2 ns E; 5 ns F; 3 ns

A; 0 -1

12

1

14

4

17

2

14

B; 2 -3

10

-1

12

2

15

0

13

E; 5 -6

7

-4

9

-1

12

-3

10

F; 3 -4

9

-2

11

1

13

-1

12

t

PD(MIN) /

t

PD(MIN)

limits with skews.

This table is the box-by-box sum of the ta-

bles in FIG. 4-12.

Source

Reg;

Destination Reg; Clock edge delay

delay A; 0 ns B; 2 ns E; 5 ns F; 3 ns

A; 0 1

14

4

17

2

14

B; 2 -3

10

0

13

E; 5 -6

7

-3

10

F; 3 1

13

Minimum/maximumprop delays for connections

actually made in FIG. 4-11.

Example: the oval shows L

B-A

has

t

PD(MIN) =

-3 ns

t

PD(MIN)

= 10 ns.

LB-A

-3 < t

PD

<10

0

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-23

Summary of Simple Propagation Delay Bounds

FIG. 4-14 Min/Max Propagation Delays Shown on Schematic

Q

B D

B

CLOCK

B

1D

C1

62.5 MHz

Q

F D

F

CLOCK

F

1D

C1

Q

E

D

E

CLOCK

E

C1

Q

A D

A

CLOCK

A

1D

C1

LA-B

A B

F

L A-F

L E-F

L F-E

L E-A

L A-E

0 12 34 5 6 7 8 1011121314150 9

L B-F

0 12 34 5 6 7 8 1011121314150 9 0 12 34 5 6 7 8 1011121314150 9

L B-A

0 12 34 5 6 7 8 1011121314150 9

1D

E

T= 16ns

0<t

P

<13

0<t

P

<10

2<t

P

<14

0<t

P

<10

1<t

P

<13

0<t

P

<7

4<t

P

<17

1<t

P

<14

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-24

Summary of Simple Propagation Delay Bounds

Example: Using a Ripple Counter in a Supposedly Synchronous Design

Ripple counters are a very simple binary counter.

Unfortunately they have impure clocking.

The clock does not run directly to each ip-ops clock input.

Thus they are not strictly synchronous.

One must check for timing and hazards in ways not necessary for a truly synchro-

nous design.

FIG. 4-15 A 4-bit Binary Ripple Counter.

Consider a circuit using the ripple counter output,

decoded by a blob of combinational logic,

feeding a register.

Calculate t

PD(MAX)

and t

PD(MIN)

for the logic.

Each ip-op output in the counter is delayed by t

CHQV

from the previous stage,

so t

CHQV

is the skew between the counter ip-ops.

Also check the counter outputs for hazards which might trigger the next clock input.

Fortunately signals directly from ip-ops do not glitch.

1D

C1

Q

A

The clocking is not pure.

One master clock does NOT go directly

to all ip-op clock inputs. 1D

C1

1D

C1

1D

C1

Q

B

Q

E Q

F

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-25

Summary of Simple Propagation Delay Bounds

FIG. 4-16 A circuit using a ripple counter.

1D

C1

Q

A

The ripple counter ip-ops have a large clock skew.

Calculate the bounds on t

PD

in the combinational logic.

1D

C1

1D

C1

1D

C1

1D

C1

Q

G D

G

CLOCK

G

1D

1D

1D

1D

0 2 4 6 8 101214 0

t

CHQV

= 1 ns max

t

HOLD

= 0 ns min

t

SETUP

= 2 ns max

0 2 4 6 8 101214 0

0 2 4 6 8 101214 0 0 2 4 6 8 101214 0

Q

B

Q

E Q

F

F E

B A

t

PD(MIN)

= ?

t

PD(MAX)

= ?

COMBINATIONAL

LOGIC

0 2 4 6 8 101214 0

t

PD(MIN)

= t

HOLD

- t

CHQV

= 0 - 1 = -1

t

PD(MAX)

= t

CLOCK

- t

SETUP

- t

CHQV

= 16 - 2 - 3 = 11

With no clock skew

t

CLOCK

= 16 ns

G

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-26

Summary of Simple Propagation Delay Bounds

FIG. 4-17 Clock skew, and propagation delay limits for the circuit.

The four delays applicable to the logic blob are shaded.

The negative (minimum) delays are not needed here.

Note: ip-op output Q

F

to D

G

in register G, has a maximum of 2 ns extra delay.

Note clock G is the same as A. They could have been combined in the table.

Sour

ce

Reg;

Destination Reg; Clock edge

delay

delay

A; 0

ns

B; 3

ns

E; 6

ns

F; 9

ns

G: 0

ns

A; 0 0 3 6 9 0

B; 3 -3 0 3 6 -3

E; 6 -6 -3 0 3 -6

F; 9 -9 -6 -3 0 -9

G: 0 0 3 6 9 0

Source

Reg;

Destination Reg; Clock edge delay

delay A; 0 ns B; 2 ns E; 5 ns F; 3 ns G: 0 ns

A; 0 -1

11

2

14

5

17

8

20

-1

11

B; 2 -4

8

-1

11

2

14

5

17

-4

8

E; 5 -7

5

-4

8

-1

11

2

10

-7

5

F; 3 -10

2

-7

5

-4

8

-1

11

-10

2

G: 0 -1

11

2

14

5

17

8

20

-1

11

Minimum/maximum prop. delay limits.

Limits for t

SKEW

=0 are [-1, 11] as on the diagonal.

The off diagonal limits are the sum of [-1, 11] and the

skew from the table on the right.

Table of t

SKEW

between any register as

source (listed on the left), and any regis-

ter as destination (listed on the top).

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-27

Summary of Simple Propagation Delay Bounds

Gating the Clock

Many designer succumb to the temptation to gate the clock.

It is a simple way to disable a D ip-op or a group of ip-ops.

This may save area or power.

This is a design method has three problems:

1) It will add to the clock skew.

2) It can cause a false clock edge.

3) Full-scan testing will not test it

FIG. 4-18

(a) The approved method of enabling/disabling a D ip-op.

There is no clock skew and no false clock edges.

(b) Gating the clock is the high risk way to enable/disable the ip-op.

However the gate saves power by not clocking nonipping ip-ops.

1D

C

Q

antiQ

CLOCK

INPUT

ENABLE(H)

1

G

1

1

1

M

U

X 1D

C

Q

antiQ

CLOCK

INPUT

ENABLE(H) 1

(a)

(b)

1/1

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-28

Clock Skew From Gating the Clock

Clock Skew From Gating the Clock

Clock skew was just covered.

One can compensate for clock skew with extra work.

False Clock Edges.

FIG. 4-19 shows how false clock edges are generated.

It also shows how changes in EN must be restricted to avoid false clock edges.

FIG. 4-19 False clock edges caused by the EN signal rising while the clock is high.

One has a restricted region during the time the clock is high (

high

)

where the EN signal must not rise.

1D

C

Q

CLK

INPUT

EN

1

(a)

(b)

GCLK

Restricted Region

Proper (though skewed) clock edge

False clock edges

EN

CLK

EN must not rise herein

GCLK

f

high

f

low

No problem Problem edge Problem edge

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-29

False Clock Edges.

The four cases of clock gating

To avoid false clock edges, The clock EN signal must be restricted.

There are 2 groups of 2 cases each.

1) EN must not change in the rst half cycle

Cases (a) and (b) allow EN changes in the last half of the clock cycle.

.

2) EN must not change in the second half cycle

Cases (c) and (d) allow EN changes in the rst half of the clock cycle.

Or one could say

(a) and (d) allow changes only during

low

(b) and (c) allow changes only during

high

Q

CLK

IN

EN

(a)

GCLK

1D

C1

Q

CLK

IN

EN

(b)

GCLK

1D

C1

EN

CLK

No!

Q

CLK

IN

EN

(c)

GCLK

1D

C1

CLK

IN

EN

(d)

GCLK

1D

C

Q

1

CLK

EN

No!

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-30

False Clock Edges.

FIG. 4-20 False clock edges illustrating why the rst half-clock-cycle is restricted

Q

CLK

IN

EN

(a)

GCLK

Restricted Region

OK edge

False

EN

CLK

GCLK

False

No upward transitions

allowed in the restricted

high

region (

high

).

Q

CLK

IN

EN

(b)

GCLK

Restricted Region

OK edge

False

EN

CLK

GCLK

OK

No downward transitions

allowed in the restricted

region (

low

).

1D

C1

1D

C1

low

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-31

False Clock Edges.

FIG. 4-21 False clock edges illustrating why the second half-clock-cycle is restricted

Q

CLK

IN

EN

(c)

GCLK

Restricted Region

OK edge

False

EN

CLK

GCLK

OK

No upward transitions

allowed in the restricted

region (

low

).

CLK

IN

EN

(d)

GCLK

Restricted Region

OK edge

False

EN

CLK

GCLK

False

low

No downward transitions

allowed in the restricted

region (

high

).

1D

C1

1D

C

Q

1

high

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-32

False Clock Edges.

Clock Gating Summary

1) EN must not change in the rst half cycle

EN changes in the last half of the clock cycle.

This allows more time to generate the EN, but

It has both an upper and lower bound on its delay.

It must be glitch free in the rst half cycle before it settles down

This is difcult to design

2) EN must not change in the second half cycle

EN changes in the rst half of the clock cycle.

The EN signal must be generated quickly within 1/2 cycle

It must be glitch free in the last half cycle but there it has settled down.

This is simple to design except for speed requirement.

Q

CLK

IN

EN

(a)

GCLK

1D

C1

Q

CLK

IN

EN

(b)

GCLK

1D

C1

EN

Q

CLK

IN

EN

(c)

GCLK

1D

C1

CLK

IN

EN

(d)

GCLK

1D

C

Q

1

EN

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-33

Safe Clock-Gating Using a Latch. (safe except

Safe Clock-Gating Using a Latch. (safe except for skew!)

Suppose the clock-gating signal EN-RAW has glitches.

EN-RAW is latched and applied to an AND gate.

The AND gate suppresses glitches in the 2st half clock cycle (method (a) above).

Glitches in the 1st half of EN-RAWare stopped because the latch is in store mode.

Glitches in the 2nd half of EN-RAW are stopped by the AND gate (clock is low).

This method is good for shutting down a subcircuit for several cycles.

For example shutting off the oating point unit in a microcomputer.

FIG. 4-22 A clock gating method with no false clock edges.

Q1 and Q2 are enabled for clock cycles when EN-RAW is high.

The latch blocks glitches when the clock is high.

The AND blocks glitches when the clock is low.

1D

C

Q

1

CLK

EN

1

GCLK

1D

C1

EN-RAW

1D

C1

COMB

LOGIC

Q

2

Q

3

TRANSPARENT

LATCH

SHUT

DOWN

LOGIC

GCLK

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-34

Safe Clock-Gating Using a Latch. (safe except

FIG. 4-23 Waveforms for a gated clock with no false edges.

When gating the clock to save power:

One normally gates many ip-ops at once.

For one ip-op, the power for the extra latch may be more than the saving.

One normally shuts off the clock for many cycles at a time.

The clock skew is minimized if an AND is placed in every clock line.

The full-scan test people will make it hard to do this.

Q1 and Q2 are enabled for clock cycles when EN-RAW is high.

The latch ensures the EN will not change in the restricted region for AND type gating.

1D

C

Q

1

CLK

EN

1

G

C

L

K

1D

C1

EN-RAW

1D

C1

COMB

LOGIC

Q

2

EN-RAW

EN

GCLK

CLK

Q

3

LATCH

TRANSPT

LATCH

LATCH

STORES

AND GATE

STOPS

LATCH

GLITCH

1st half

LATCH

STORES

SHUT

DOWN

LOGIC

STOPS

GLITCH

ENABLED

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-35

Why Two Frequencies?

Clock Dividers

Why Two Frequencies?

The Pentium, the DEC Alpha, and other modern microprocessors run internally at a

clock frequency which is too high for the board level circuitry.

Where a system has both slow and fast logic, considerable circuitry and power can

be saved by using a slower clock for part of the logic.

Basic Methods

Clock all ip-ops at high-speed and enable the ip-ops at a lower speed.

Is the safest (easiest) method.

Will not give much power saving.

Gate the high-speed clock with a slower signal.

Will give medium power reduction.

The lower frequency will use less power in the ip-ops,

but charging and discharging the clock line at high speed will waste power.

Gated clock designs are subject to false edges and skew.

Divide the clock

Divider can supply different frequencies to different ip-ops.

There must not be skew between the main and divided clocks.

Many divider/counters give glitches which are poisonous on clock lines.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-36

Binary Counters As Clock Dividers

Binary Counters As Clock Dividers

Many synchronous (not ripple) binary counters acts as a fairly good clock dividers.

The output bits form a natural division chain.

Q1 = divide-by-2,

Q2 = divide-by-4,

--- -------- -- --

Qn = divide-by 2

n

.

Skew

The Flip-op outputs are the counter outputs

so all counter outputs change a ip-op propagation-delay (t

CHQV

) after clock.

If the ip-ops are identical, at the same temperature, and as physically close,

the skew between the divided clocks should be small.

The original clock (CLK) has a larger skew with respect to the divided clocks.

CLK rises (falls) t

CHQV

before the divided clock edges.

One should only use CLK for clocking the divider chain.

Otherwise, resynchronize it (to be discussed).

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-37

Binary Counters As Clock Dividers

FIG. 4-24 Falling-edge clock-divider

A binary counter suitable for a clock divider.

Toggle ip-ops make a simpler counter than D-ip-ops.

This is a falling-edge-triggered up counter.

which makes ip-ops ip together on falling edges.

The divided clocks are suitable for falling-edge-triggered

ip-ops.

1T

C

Q1 = CLK/2

1

Q2 = CLK/4

CLK

COMMON

FALLING EDGE

CLK

1T

C1

Q3 = CLK/8

Q4 = CLK/16

1

1T

C1

1T

C1

CLK/2

CLK/4

CLK/8

CLK/16

COMMON

FALLING EDGE

SKEW

NEGLIGABLE SKEW

NEGLIGABLE SKEW

NEGLIGABLE SKEW

C+

CTRDIV16

[2]

[4]

[8]

[16]

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-38

Binary Counters As Clock Dividers

FIG. 4-25 A clock-divider with common rising-edges

(a) A binary down-counter suitable for a clock divider.

(b) The IEEE symbol for a down counter.

The blocks represent individual ip-ops and associated gates.

These blocks have a common clock which is shown entering the common control block at the top.

The - after the clock input shows it counts down. An up counter would have a +.

(c) The waveforms showing that down-counter ip-ops ip together rising edges.

The divided clocks are suitable for rising-edge-triggered ip-ops.

1T

C

CLK/2

1

CLK/4

CLK

COMMON

RISING EDGE

CLK

1T

C1

CLK/16

CLK/16

0

1T

C1

1T

C1

CLK/2

CLK/4

CLK/8

CLK/16

COMMON

RISING EDGE

C-

CTRDIV16

[2]

[4]

[8]

[16]

Q1

Q2

Q3

Q4

(a)

(b)

(c)

SKEW SKEW

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-39

Resynchronization

Resynchronization

Making all clocks tick together

Necessary for circuits clocked by both divided clocks and the main clock.

Widely distributed divided-clock signals may need local adjustments so their active

edges all change together.

When divided clock signals are used over a large physical area.

It may be easier to resynchronize at each locality,

than to distribute low-skew divided clocks over the large area.

Resynchronizing latches should be physically close together for low skew between

them.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-40

Resynchronization

FIG. 4-26 Examples of where divider resyncronization might be used.

CLK

SYCH

CLK/2

SYCH

CLK/4

SYCH

CLK/8

SYCH

(a) Using one or more divided clocks. and the original clock.

(b) Using one main clock distributed with special care to avoid skew,

and divided clocks which can have skew because they are resynchronized locally.

C-

CTRDIV8

[2]

[4]

[8]

(a)

CLK

SYCH

CLK/2

SYCH

CLK/4

SYCH

CLK/8

SYCH

C-

CTRDIV8

[2]

[4]

[8]

(b)

CLK

SYCH

CLK/2

SYCH

CLK/4

SYCH

CLK/8

SYCH C

L

O

C

K

R

E

G

I

O

N

1

C

L

O

C

K

R

E

G

I

O

N

2

R

E

S

Y

N

C

H

R

O

N

I

Z

E

R

E

S

Y

N

C

H

R

O

N

I

Z

E

R

E

S

Y

N

C

H

R

O

N

I

Z

E

CLK

CLK

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-41

Resynchronization

FIG. 4-27 Examples of where divider resyncronization might be used

((c) Distributing one low-skew main clock,

generating divided clocks as needed in different localities,

and resynchronizing to a reduce skew between regions.

(c)

CLK

SYCH

CLK/4

SYCH

CLK/8

SYCH

CLK

SYCH

CLK/2

SYCH

CLK/8

SYCH

C

L

O

C

K

R

E

G

I

O

N

1

C

L

O

C

K

R

E

G

I

O

N

2

R

E

S

Y

N

C

H

R

O

N

I

Z

E

R

E

S

Y

N

C

H

R

O

N

I

Z

E

C-

CTRDIV8

[2]

[4]

[8]

CLK

GOOD LOW-SKEW CLOCK LINE

C-

CTRDIV8

[2]

[4]

[8]

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-42

Resynchronization

Construction of a resynchronizer

The resynchronizer uses transparent latches,

rather than edge-triggered ip-ops.

A transparent latch:

- acts like a piece of wire when the clock is low,

- stores the last passed Q value when the clock

goes high.

Reason for latches:

Latches are simpler than ip-ops.

Flip-ops cannot synchronize the highest frequency signal, CLK.

All latches must have the same delay t

CLQT

,

(time from clock low to Q transparent)

The resynchronizer input CLK/n signals:

Except for the latchs setup or hold times,

Input signals may rise/fall or glitch anywhere in the store-mode half clock-cycle.

To resynchronize CLK:

Use an inverted advanced clock which rises more than a setup-time before the latch

goes transparent.

This delay is shown as one inverter. It may take three.

The actual delay must be carefully done.

The high duration of CLK

SYNCH

is always under a half cycle.

The shortening of this high pulse is linearly related the advance in ADV-CLK.

CLK

D

Q

TRANS STORE STORE TRANS

1D

C1

1D

C1

LATCH FLIP-

FLOP

t

CHQT

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-43

Resynchronization

FIG. 4-28 Resynchronizer

Resynchronization positions the rising edges of all clocks very close together.

Resynchronization using transparent latches.

The closely-spaced lines show the latches D-to-Q transfer when the latch is transparent.

The arrow shows the value stored when the latch enters stored mode.

To synchronize the original CLK, one needs an inverted clock (ADVN-CLK) which leads CLK.

Note CLK

SYNCH

is not symmetric

1D

C1

CLK

SYNCH

CLK/2

SYNCH

CLK CLK

1D

C1

CLK/4

SYNCH

CLK/8

SYNCH

1D

C1

1D

C1

ADVN-CLK

CLK

SYNCH

CLK/2

SYNCH

CLK/2

C-

CTRDIV16

[2]

[4]

[8]

TRANS STORE

ADVN-CLK

STORE TRANS

CLK/4

CLK/2

CLK

TRANS STORE STORE TRANS

ADVN-CLK

CLK/8

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-44

Example:

Example:

Using a ripple counter as a divider; Then resynchronizing the outputs.

FIG. 4-30 shows a ripple counter used as a clock divider.

The ripple counter outputs are delayed 3, 6, and 9 ns.

When the latches input changes inside the store state of the latch, the synchroniz-

ing latch will wait until CLK makes it transparent before its output will change.

The synchronized signals emerge when all the latches go transparent together.

The ripple counter puts a 9 ns delay in CLK/8.

This is over half a clock cycle and is too much for the synchronizer.

CLK/8 enters its latch after the latch has gone transparent.

Thus CLK/8

SYNCH

is delayed 1ns and is skewed.

Synchronization narrows the CLK

SYNC

pulse by the 4 ns delay of the three inverters.

The one inverter delay would be only be 1.3 ns.

This delay is to short to counteract the D-to-Q delay in the synchronizer

1

.

1. This spec says that a high output will not come out of the latch until a D =1 signal has been applied for

t

DHQH

= 5 ns. This would be 3.7 ns after the active CLK edge in stead of 3 ns, and CLK

SYNC

would rise at

11.7 ns, not 11ns.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-45

Example:

FIG. 4-29 A clock divider circuit using a ripple counter.

1D

C1

Q

E

The ip-ops in the ripple counter have a large clock skew.

The resynchronizer will try synchronize the rising edges.

However the delay in CLK/8 is over half of CLK and is too much to be synchronized.

The shaded blocks show how the clock is delayed at various points.

1D

C1

1D

C1

1D

C1

1D

1D

1D

0 2 4 6 8 101214 0

t

CHQV

= t

CLQT

= 3 ns max for both ip-ops and latches

t

DHQH

= 5 ns max

0 2 4 6 8 101214 0

0 2 4 6 8 101214 0

Q

F

Q

G

CLK

0 2 4 6 8 101214 0

t

CLOCK

CLK

16 ns

-4 -2 0 2 4 6 8 10

RESYNCRONIZING

LATCH

CLK/8

SYNCH

CLK/4

CLK/8

CLK/2

CLK

SYNCH

CLK/2

SYNCH

CLK/4

SYNCH

ADVN-CLK

0 2 4 6 8 101214 0

RIPPLE COUNTER

4 ns

t

PD-INVERTER

= 1.3 ns max

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-46

Example:

FIG. 4-30 The resynchronizer waveforms to scale

The latches are transparent n the shaded areas.

The slope of the grey area represents the latch prop. delay t

CHQT

. Here t

CHQT

= 3 ns.

CLK/8 rises after the latch goes transparent. The shows t

CHQT

, for the rising edge.

It shows CLK/8 will have a 1ns skew.

CLK/8

SYNCH

9 ns delay in

ripple counter

Rises too late. Cannot be synchronized.

ADVN-CLK

CLK

SYNCH

CLK

TRANS

STORE STORE

TRANS

CLK/2

CLK/2

SYNCH

CLK/4

CLK/4

SYNCH

CLK

TRANS

STORE STORE

TRANS

CLK/8

TRANS

STORE

0 2 4 6 8 10 12 14 16 18 20 20 24 26 28 30 32 34 36 3840 42 44 46 48 ns

6 ns delay in

ripple counter

3 ns delay in

ripple counter

-4 ns

t

CHQT

t

CHQT

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-47

Isochronic Regions And Data Signals Between

Data Resynchronization Between Skewed Clocks

Isochronic Regions And Data Signals Between Them

Consider a circuit so large that skew cannot be controlled over the whole circuit.

Within certain regions of the circuit the skew is small and causes no problem.

We call such regions isochronic regions.

The problem to be considered here is synchronizing the data signals that pass be-

tween isochronic regions.

CLOCK

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-48

Isochronic Regions And Data Signals Between

FIG. 4-31 One master clock with isochronic regions

Here the different delays are caused by a different number of clock buffers.

No Engineering graduate from Carleton would design this!

More likely, skew would be caused by:

- grossly different lengths of clock lead,

- a different type of lead to different areas;

perhaps coax to some areas and circuit board track to others,

- or differences in the buffer loadings; perhaps a different number of ip-ops on each buffer.

CLOCK

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

ISOCRONIC REGION 1

REGION 3

REGION 2

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-49

Isochronic Regions And Data Signals Between

Cycle Skipping

FIG. 4-32 Cycle skipping in data owing from an early clock region to a late clock region.

Clock C

1

in Isochronic region 1, leads the clock in region 2.

A Q

1

change clocked by C

1

, will get through to D

3

before C

2

rises.

Then Q

3

will change on the delayed rising-edge of C

2

.

Clearly the designer planned to delay Q

3

as shown by Q

3

(desired).

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

REGION 1

CLOCK

REGION 2

Q

1

D

3

1D

C1

1D

C1

Q

3

C

1

Q

1

=D

3

C

2

Q

3

Q

3 (desired)

C

1

C

2

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-50

Isochronic Regions And Data Signals Between

Adding Delay To Avoid Cycle Skipping

FIG. 4-33 Delaying the data to compensate for clock skew.

Alternately choose a path that has several gates anyway.

Recall t

PD

was the propagation delay for gates between Q

1

and D

3

Make sure t

PD

> t

SKEW

.

Here the clock skew is compensated by a data skew.

The data is delayed by at least as much as the clock.

Then Q

3

will be properly delayed and there will be no cycle skipped.

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

REGION 1

CLOCK

REGION 2

Q

1

D

3

1D

C1

1D

C1

Q

3

C

1

C

2

C

1

Q

1

C

2

Q

3

= Q

3 (desired)

D

3

Alternately

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-51

Resynchronizing The Data Lines To

Resynchronizing The Data Lines To Accommodate Clock Skew

There are two circuits, for resynchronizing data to compensate for clock skew.

They both insert a latch in each data line going between isochronic regions.

In the rst circuit the latch is gated by the region which send the data.

In the second circuit the latch is gated by the region which receives the data.

Latches can be dynamic.

They are recharged every cycle.

REGION 1

CLOCK

1D

C1

Q

2

REGION 2

D

2

REGION 1

CLOCK

1D

C1

Q

2

REGION 2

D

2

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-52

Resynchronizing The Data Lines To

Method 1, for resynchronizing data

FIG. 4-34 Resynchronizing data with a D latch, to compensate for clock skew.

Here the delay is put in by a D latch.

Such a latch delays the signal half a clock period,

that is until the latch t goes transparent.

This allows a more automatic design than inserting gate-delays as in FIG. 4-33.

Half a clock cycle should be more than adequate delay for deskewing.

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

REGION 1

CLOCK

1D

C1

Q

2

REGION 2

Q

1

D

2

D

3

1D

C1

1D

C1

Q

3

C

1

C

2

Q

3

= Q

3 (desired)

Q

2

=D

3

Q

1

=D

2

LATCH

STORING

LATCH

TRANSP

Latch Delay

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-53

Resynchronizing The Data Lines To

Method 1: Analysis of data resynchronization using latches in detail

FIG. 4-35 Resynchronizing data signals.

Timing limitations of using latches in data lines to compensate for clock skew.

The clock feed is changed so the skew might be positive or negative.

Also gates have been inserted in the latch leads.

See the timing diagram in FIG. 4-36.

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

REGION 1

CLOCK

1D

C1

Q

2

REGION 2

Q

1

D

2

D

3 t

P1

t

P2

1D

C1

1D

C1

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-54

Resynchronizing The Data Lines To

FIG. 4-36 Timing diagram for data resyncronization

The timing diagram when there are delays in the circuitry around the latch.

It is used to derive bounds for the amount of skew the circuit can resynchronize.

The dark squares represent the ip-op/latch input-to-output propagation delays.

The lighter gray rectangles represent setup times.

t

CLK

C

1

Q

1

C

2

D

3

Q

3

t

SKEW

t

P2

D

2

Q

2

t

P1

t

CHQV

+ t

P1

+ t

CLQT

+ t

P2

+ t

SETUP

t

CLQT

+ t

P2

+ t

SETUP

< t

CLK/2

+ t

SKEW

t

CHQV

or t

CLQT

t

SETUP

LATCH

STORING

LATCH

TRANSP

t

P1

(max)

t

P2

(max)

< t

CLK

+ t

SKEW

t

DVQV

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-55

Resynchronizing The Data Lines To

Timing details for skew correction with latches in the data paths

Consider the data path Q

1

-> D

2

-> Q

2

-> D

3

in the dashed oval in FIG. 4-36.

The shaded squares represent either a setup or a clock-to-output delay.

The delays along this data path, starting at the rising edge of C

1

, are-

t

CHQV

+ t

P1

+ t

CLQT

+ t

P2

+ t

SETUP

This must happen before the second rising edge of C

2

which is at -

t

CLK

+ t

SKEW

after C

1

rises. Thus

1

t

CHQV

+ t

P1

+ t

CLQT

+ t

P2

+ t

SETUP

< t

CLK

+ t

SKEW

(EQ 4)

The first gate(s) delay, t

P1

, may extend into the transparent half clock cycle.

Thus for t

P2

= 0, and small internal latch/ip-op delays,

.

However, Q

2

can never change before the latch goes transparent, so t

P2

is limited by

t

CLQT

+ t

P2

+ t

SETUP

< t

CLK/2

+ t

SKEW

(EQ 5)

Thus for small internal latch/ip-op delays and t

P1

< t

CLK

/2,

This circuit can accommodate nearly 180 of negative skew (C

1

lagging).

and over 180 of positive skew (C

2

leading).

1. For t

P1

extended into the transparent half of the clock cycle, replace t

CLQT

(Clock Lowto QTransparent) with t

DVQV

(Dinput

data Valid to Q output Valid) in (EQ 4). They are usually about the same.

t

P1

can approach t

CLK

t

P2

can approach t

CLK

/2.

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-56

Resynchronizing The Data Lines To

FIG. 4-37 Timing diagram showing upper positive skew limit.

The diagram is for positive skew over 180.

The upper bound for cycle skipping is shown.

Note that D

3

can rise up to a hold time after clock C

2

and still be captured as Q

3

.

t

CLK

C

1

Q

1

C

2

D

3

Q

3

t

SKEW

t

P2

D

2

Q

2

t

P1

t

CHQV

or t

CLQT

t

HOLD

LATCH

STORING

LATCH

TRANSP

t

SKEW

< t

CLK

/2 + t

CLQT

+ t

P2

- t

HOLD

t

DVQV

t

CLK

/2

t

CLQT

Early Q

3

, Same clock cycle as Q

1

Desired Q

3

, next clock cycle after Q

1

t

SKEW

< t

P1

+ t

DVQV

+ t

P2

- t

HOLD

For t

P1

> t

CLK

/2 (not shown)

For t

P1

< t

CLK

/2

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-57

Resynchronizing The Data Lines To

The range of skew for which correction is possible

FIG. 4-38 Timing diagram showing the meaning of positive and negative skew.

Positive skew of over 180 is a special case.

In this case a positive skew of 360- is not the same as a skew of .

The difference is in which cycle Q

3

is intended to change. See the Q

3

waveforms below.

The restrictions on the skew are stated beside the waveforms.

C

1

Q

1

Q

3

LATCH

STORING

LATCH

TRANSP

C

2

Q

3

C

2

Q

3

C

2

Positive skew under 180

| t

SKEW

| < t

CLK/2

- t

CLQT

- t

SETUP

- t

P2

Negative skew under 180

Positive skew over 180

C

1

clock taken as xed

t

SKEW

< t

CLK

/2 + t

CLQT

+ t

P2

- t

HOLD

t

SKEW

< t

CLK

/2 + t

CLQT

+ t

P2

- t

HOLD

(Same as for over 180)

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-58

Resynchronizing The Data Lines To

FIG. 4-39 When clock skew is a problem

This shows that resynchronization is needed only if the clock and data delay are in the same direction.

If they are in opposite directions, it reduces the propagation delay Q

i

to D

i+1

.

If this is a problem, compensate by slowing the clock period by the amount of the skew.

Q

1

Q

3

Q

1

Q

3

1D

C1

Q

1

Q

3

1D

C1

1D

C1

1D

C1

1D

C1

1D

C1

Q

1

Q

3

1D

C1

1D

C1

Need synchronization or

t

PD

(min) increased.

more delay in data path.

No synchronization needed

t

PD

(max) decreased.

provided data-path delay is

within the reduced bound.

+Skew; Clock Delay In Same Direction as Data Delay

-Skew; Clock Delay In Opposite Direction from Data Delay

Setup-time violation likely

Hold-time violation likely

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-59

Summary: First circuit for resynchronizing on

Summary: First circuit for resynchronizing on the data lines

Positive skew

If the data delay and the clock delay are in the same direction resyncronization is

needed.

It can be omitted if one can guarantee the data delay is larger than the clock delay.

Negative skew

If the data delay and the clock delay are in opposite directions no resyncroniza-

tion is needed.

Setup time violations may become critical

For latch resynchronized data

A negatively gated latch, clocked from the data input circuit clock, can resyn-

chronize for skews of nearly t

CLK

/2.

This latch is useful when the magnitude and sign of the skew are not well con-

trolled.

The logic delay at the latch input t

P1

, can approach t

CLK

. See (EQ 4)

The logic delay at the latch output t

P2

, can approach t

CLK

/2, provided t

P1

is corre-

spondingly reduced. See (EQ 5)

The sum of t

P1

+ t

P2

can approach t

CLK

. See (EQ 4).

1D

C1

Keeping The Clock Pure

John Knight Electronics Department, Carleton University 8/27/96

ClkDst-60

Resynchronizing The Data Lines To

Resynchronizing The Data Lines To Accommodate Clock Skew; Circuit 2

The second resynchronizing circuit is much like the rst.