Professional Documents

Culture Documents

UCC28600 Split 7 PDF

UCC28600 Split 7 PDF

Uploaded by

Hoàng Nam MelOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UCC28600 Split 7 PDF

UCC28600 Split 7 PDF

Uploaded by

Hoàng Nam MelCopyright:

Available Formats

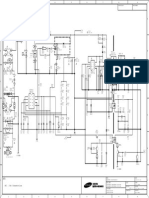

UCC28600

www.ti.com

SLUS646B NOVEMBER 2005 REVISED MAY 2006

ORDERING INFORMATION

TA

PACKAGES

-40C to 105C

(1)

SOIC

(D) (1)

PART NUMBER

UCC28600D

SOIC (D) package is available taped and reeled by adding R to the above part numbers. Reeled quantities for UCC28600DR is 2,500

devices per reel.

DEVICE INFORMATION

UCC28600

D PACKAGE

(TOP VIEW)

SS

FB

CS

GND

STATUS

OVP

VDD

OUT

TERMINAL FUNCTIONS

TERMINAL

NAME

CS

NO.

3

I/O

DESCRIPTION

Current sense input. Also programs power limit, and used to control modulation and activate overcurrent

protection. The CS voltage input originates across a current sense resistor and ground. Power limit is

programmed with an effective series resistance between this pin and the current sense resistor.

FB

Feedback input or control input from the optocoupler to the PWM comparator used to control the peak current

in the power MOSFET. An internal 20-k resistor is between this pin and the internal 5-V regulated voltage.

Connect the collector of the photo-transistor of the feedback optocoupler directly to this pin; connect the

emitter of the photo-transistor to GND. The voltage of this pin controls the mode of operation in one of the

three modes: quasi resonant (QR), frequency foldback mode (FFM) and green mode (GM).

GND

Ground for internal circuitry. Connect a ceramic 0.1-F bypass capacitor between VDD and GND, with the

capacitor as close to these two pins as possible.

OUT

1-A sink (TrueDrive ) and 0.75-A source gate drive output. This output drives the power MOSFET and

switches between GND and the lower of VDD or the 13-V internal output clamp.

OVP

Over voltage protection (OVP) input senses line-OVP, load-OVP and the resonant trough for QR turn-on.

Detect line, load and resonant conditions using the primary bias winding of the transformer, adjust sensitivity

with resistors connected to this pin.

SS

Soft-start programming pin. Program the soft-start rate with a capacitor to ground; the rate is determined by

the capacitance and the internal soft-start charge current. All faults discharge the SS pin to GND through an

internal MOSFET with an RDS(on) of approximately 100 . The internal modulator comparator reacts to the

lowest of the SS voltage, the internal FB voltage and the peak current limit. Typically, TSS = 1.5 ms for CSS =

3.3 nF.

STATUS

ACTIVE HIGH open drain signal that indicates the device has entered standby mode. This pin can be used to

disable the PFC control circuit (high impedance = green mode). STATUS pin is high during UVLO, (VDD <

startup threshold), and softstart, (SS < FB).

VDD

Provides power to the device. Use a ceramic 0.1-F by-pass capacitor for high-frequency filtering of the VDD

pin, as described in the GND pin description. Operating energy is usually delivered from auxiliary winding. To

prevent hiccup operation during start-up, a larger energy storage cap is also needed between VDD and GND.

Submit Documentation Feedback

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 74HC05 PDFDocument9 pages74HC05 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 11 PDFDocument1 pageUCC28600 Split 11 PDFHoàng Nam MelNo ratings yet

- 74HC02 PDFDocument5 pages74HC02 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 18 PDFDocument1 pageUCC28600 Split 18 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 2 PDFDocument1 pageUCC28600 Split 2 PDFHoàng Nam MelNo ratings yet

- Va902 3 PDFDocument74 pagesVa902 3 PDFHoàng Nam MelNo ratings yet

- UCC28061 Split 9 PDFDocument1 pageUCC28061 Split 9 PDFHoàng Nam MelNo ratings yet

- Samsung Power Board Circuit BN44-00353A PDFDocument3 pagesSamsung Power Board Circuit BN44-00353A PDFHoàng Nam MelNo ratings yet

- Pheenix Alpha Product Folder AD12 - 4 PagesDocument3 pagesPheenix Alpha Product Folder AD12 - 4 PagesTramuntana FortaNo ratings yet

- Part Test # 2 NSEJS BatchDocument8 pagesPart Test # 2 NSEJS BatchRA• PLAYZNo ratings yet

- Set C Question Paper 2Document20 pagesSet C Question Paper 2Alyasin FrougaNo ratings yet

- What Does It Mean by Generalized Theory of Electrical MachinesDocument6 pagesWhat Does It Mean by Generalized Theory of Electrical MachinesboumedienNo ratings yet

- RV Series Straight Thru Flow DesignDocument4 pagesRV Series Straight Thru Flow Designmelvin hoferNo ratings yet

- 2005 Mendoza Pranic FacialDocument4 pages2005 Mendoza Pranic FacialRaghu100% (1)

- Council For Technical Education and Vocational Training Korea Nepal Institute of Technology Butwal - 12, TamnagarDocument31 pagesCouncil For Technical Education and Vocational Training Korea Nepal Institute of Technology Butwal - 12, TamnagarYogi Kawar Ganga NathNo ratings yet

- 4" X 3" Ball Valve Manual or On/Off XXXX XXX XXX: Factory Accessment Test ValvesDocument1 page4" X 3" Ball Valve Manual or On/Off XXXX XXX XXX: Factory Accessment Test ValvesSiriepathi SeetharamanNo ratings yet

- Sharp Runtka395wjqz Dac38m011 Power-Inverter SCHDocument7 pagesSharp Runtka395wjqz Dac38m011 Power-Inverter SCHchathush.mihirangaNo ratings yet

- 950H, 962H and IT62H Wheel Loader Hydraulic System: Command Control SteeringDocument2 pages950H, 962H and IT62H Wheel Loader Hydraulic System: Command Control SteeringTeofilo Paredes CosmeNo ratings yet

- 130326-Especificacion SP342CEDocument2 pages130326-Especificacion SP342CELesly LandazabalNo ratings yet

- 25 M Fast Supply Vessel Swe v1Document2 pages25 M Fast Supply Vessel Swe v1Sebastian RentschNo ratings yet

- Bpsu Header FooterDocument20 pagesBpsu Header FooterWilson Domingo Lazarte0% (1)

- Power Supply AgreementDocument29 pagesPower Supply AgreementNicko Samar IndicoNo ratings yet

- Cast Iron Welding - Procedures and Free GuideDocument8 pagesCast Iron Welding - Procedures and Free GuideKhin Aung ShweNo ratings yet

- IEEE Recommended Practice For Sizing Lead-Acid Batteries For Stationary ApplicationsDocument69 pagesIEEE Recommended Practice For Sizing Lead-Acid Batteries For Stationary ApplicationstanerNo ratings yet

- THE AWAKENING - Quantum Mechanics of The Human Brain and ConsciousnessDocument38 pagesTHE AWAKENING - Quantum Mechanics of The Human Brain and ConsciousnessMokhtar MohdNo ratings yet

- Haldiram Factory: Observations On MEP Design Report & DrawingsDocument6 pagesHaldiram Factory: Observations On MEP Design Report & DrawingsVaibhav SharmaNo ratings yet

- Training Couses CatalogueDocument99 pagesTraining Couses CatalogueZ Babar KhanNo ratings yet

- Chemical Reactions and EquationsDocument48 pagesChemical Reactions and EquationsAnimesh AnshNo ratings yet

- Vent Terminals - UpCodesDocument6 pagesVent Terminals - UpCodesXAVIER RUBIONo ratings yet

- 793p 347351Document5 pages793p 347351BobdNo ratings yet

- Fertilizer Policy in IndiaDocument242 pagesFertilizer Policy in IndiaArun D PaulNo ratings yet

- Science: Quarter 3, Week 6 - 7 Module 5Document27 pagesScience: Quarter 3, Week 6 - 7 Module 5NRIZA MAE CACHONo ratings yet

- Multi-Parametric Instrument: Installation ManualDocument38 pagesMulti-Parametric Instrument: Installation ManualPaula SilvaNo ratings yet

- Well Performance SoftwaresDocument3 pagesWell Performance SoftwaresMotaz IbrahimNo ratings yet

- Instrumentation: Method Statement ForDocument8 pagesInstrumentation: Method Statement ForWalid MarhabaNo ratings yet

- Challenging Assumptions On Remote WorkDocument189 pagesChallenging Assumptions On Remote WorkHadi SumartonoNo ratings yet

- Type K Permanent Overband SeparatorDocument2 pagesType K Permanent Overband SeparatorpspsuparingNo ratings yet

- ChaptergtolDocument168 pagesChaptergtolIra Jane LosañezNo ratings yet