Professional Documents

Culture Documents

74HC14 PDF

74HC14 PDF

Uploaded by

Hoàng Nam MelCopyright:

Available Formats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- DFT For Advanced UserDocument151 pagesDFT For Advanced UserAnonymous UeI6DVNo ratings yet

- 18csl37-Ade Lab ManualDocument41 pages18csl37-Ade Lab ManualEragon ShadeSlayerNo ratings yet

- 74HC05 PDFDocument9 pages74HC05 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 11 PDFDocument1 pageUCC28600 Split 11 PDFHoàng Nam MelNo ratings yet

- 74HC02 PDFDocument5 pages74HC02 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 18 PDFDocument1 pageUCC28600 Split 18 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 2 PDFDocument1 pageUCC28600 Split 2 PDFHoàng Nam MelNo ratings yet

- Va902 3 PDFDocument74 pagesVa902 3 PDFHoàng Nam MelNo ratings yet

- UCC28061 Split 9 PDFDocument1 pageUCC28061 Split 9 PDFHoàng Nam MelNo ratings yet

- Samsung Power Board Circuit BN44-00353A PDFDocument3 pagesSamsung Power Board Circuit BN44-00353A PDFHoàng Nam MelNo ratings yet

- Analog and Digital Integrated Circuit Question BankDocument12 pagesAnalog and Digital Integrated Circuit Question BankMATHANKUMAR.S67% (3)

- VLSI Module 3 PDFDocument34 pagesVLSI Module 3 PDFGovind M RoddannavarNo ratings yet

- 4.chapter4 CMOS Multistages Differential AmplifierDocument60 pages4.chapter4 CMOS Multistages Differential Amplifierngoc an nguyenNo ratings yet

- KVDocument2 pagesKVsrilatha sriNo ratings yet

- DatasheetDocument6 pagesDatasheetSunil SuwarnkarNo ratings yet

- Digital LogicDocument6 pagesDigital LogicIS-HAK SULEMAN BAAKONo ratings yet

- Mini Project Presentation1 Final Presentation Parking SensorDocument12 pagesMini Project Presentation1 Final Presentation Parking SensorChethan ReddyNo ratings yet

- An Eight-Octant Bipolar Junction Transistor Analog Multiplier Circuit and Its ApplicationsDocument9 pagesAn Eight-Octant Bipolar Junction Transistor Analog Multiplier Circuit and Its ApplicationsTabark AlaamryNo ratings yet

- EL003 Electronic Projects New Collections Vol 3NDocument238 pagesEL003 Electronic Projects New Collections Vol 3NSoeThihaLwin100% (1)

- Datasheet 2sc3052 SMDDocument1 pageDatasheet 2sc3052 SMDed pwtNo ratings yet

- MultivibratorsDocument22 pagesMultivibratorsNGOUNENo ratings yet

- Analog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesDocument59 pagesAnalog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesKarthik v BhatNo ratings yet

- Tas 5613Document34 pagesTas 5613Antonio Laruta ChoqueNo ratings yet

- Circuit Design For Repeated Binary SequenceDocument5 pagesCircuit Design For Repeated Binary SequenceArsalan JahNo ratings yet

- Logic GatesDocument11 pagesLogic Gatesamit kaushikNo ratings yet

- NTE823 Integrated Circuit Low Voltage Audio Amplifier: DescriptionDocument3 pagesNTE823 Integrated Circuit Low Voltage Audio Amplifier: DescriptionAbel RodriguezNo ratings yet

- t and output resistance of 50Ω. Determine theDocument29 pagest and output resistance of 50Ω. Determine theleelee leeNo ratings yet

- Experiment No. 4-Parallel RC and RL CircuitsDocument9 pagesExperiment No. 4-Parallel RC and RL CircuitsArct John Alfante Zamora100% (1)

- A High-Speed Tree-Based 64-Bit Cmos Binary ComparatorDocument5 pagesA High-Speed Tree-Based 64-Bit Cmos Binary ComparatorInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Final Project Report Sachin Basavarajappa KenchammanagathihalliDocument14 pagesFinal Project Report Sachin Basavarajappa KenchammanagathihalliSachin BkNo ratings yet

- Transistor in Common Base (Continuation) and Common Emitter ConfigurationDocument14 pagesTransistor in Common Base (Continuation) and Common Emitter ConfigurationBangla TweaksNo ratings yet

- Vlsi Lab Question SetDocument4 pagesVlsi Lab Question SetM.S.Anandhi100% (1)

- Sinusoidal Steady State-Mcqs: 1. The Value of Current Through The 1 Farad Capacitor of Figure IsDocument13 pagesSinusoidal Steady State-Mcqs: 1. The Value of Current Through The 1 Farad Capacitor of Figure IsAnonymous lt2LFZHNo ratings yet

- Computer Aided Circuit Simulation and VerificationDocument37 pagesComputer Aided Circuit Simulation and VerificationDusanNo ratings yet

- Ugrd-Ee6100 Midterm QuizDocument7 pagesUgrd-Ee6100 Midterm QuizMER HANNo ratings yet

- A3144 Hall Effect Sensor: 3 January 2018 - 0 CommentsDocument5 pagesA3144 Hall Effect Sensor: 3 January 2018 - 0 CommentsSorin NemesNo ratings yet

- Pspice Tutorial 4Document4 pagesPspice Tutorial 4Asseel FleihanNo ratings yet

74HC14 PDF

74HC14 PDF

Uploaded by

Hoàng Nam MelOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74HC14 PDF

74HC14 PDF

Uploaded by

Hoàng Nam MelCopyright:

Available Formats

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT14

Hex inverting Schmitt trigger

Product specification

File under Integrated Circuits, IC06

September 1993

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

FEATURES

Output capability: standard

ICC category: SSI

GENERAL DESCRIPTION

The 74HC/HCT14 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL).

They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT14 provide six inverting buffers with Schmitt-trigger action. They are capable of transforming slowly

changing input signals into sharply defined, jitter-free output signals.

QUICK REFERENCE DATA

GND = 0 V; Tamb = 25 C; tr = tf = 6 ns

TYPICAL

SYMBOL

PARAMETER

CONDITIONS

UNIT

HC

tPHL/ tPLH

propagation delay nA to nY

CI

input capacitance

CPD

power dissipation capacitance per gate

CL = 15 pF; VCC = 5 V

notes 1 and 2

Notes

1. CPD is used to determine the dynamic power dissipation (PD in W):

PD = CPD VCC2 fi + (CL VCC2 fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

CL = output load capacitance in pF

VCC = supply voltage in V

(CL VCC2 fo) = sum of outputs

2. For HC the condition is VI = GND to VCC

For HCT the condition is VI = GND to VCC 1.5 V

ORDERING INFORMATION

See 74HC/HCT/HCU/HCMOS Logic Package Information.

September 1993

HCT

12

17

ns

3.5

3.5

pF

pF

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

PIN DESCRIPTION

PIN NO.

SYMBOL

NAME AND FUNCTION

1, 3, 5, 9, 11, 13

1A to 6A

data inputs

2, 4, 6, 8, 10, 12

1Y to 6Y

data outputs

GND

ground (0 V)

14

VCC

positive supply voltage

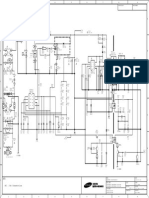

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

FUNCTION TABLE

INPUT

OUTPUT

nA

nY

L

H

H

L

Notes

1. H = HIGH voltage level

L = LOW voltage level

APPLICATIONS

Wave and pulse shapers

Astable multivibrators

Monostable multivibrators

Fig.4 Functional diagram.

September 1993

Fig.5

Logic diagram

(one Schmitt trigger).

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications. Transfer characteristics are

given below.

Output capability: standard

ICC category: SSI

Transfer characteristics for 74HC

Voltages are referenced to GND (ground = 0 V)

Tamb (C)

TEST CONDITIONS

74HC

SYMBOL PARAMETER

40 to +85

+25

min.

typ.

max.

min.

max.

40 to +125

min.

UNIT

VCC

WAVEFORMS

(V)

max.

VT+

positive-going

threshold

0.7

1.7

2.1

1.18

2.38

3.14

1.5

3.15

4.2

0.7

1.7

2.1

1.5

3.15

4.2

0.7

1.7

2.1

1.5

3.15

4.2

2.0

4.5

6.0

Figs 6 and 7

VT

negative-going

threshold

0.3

0.9

1.2

0.52

1.40

1.89

0.90

2.00

2.60

0.3

0.90

1.20

0.90

2.00

2.60

0.30

0.90

1.2

0.90

2.00

2.60

2.0

4.5

6.0

Figs 6 and 7

VH

hysteresis

(VT+ VT)

0.2

0.4

0.6

0.66

0.98

1.25

1.0

1.4

1.6

0.2

0.4

0.6

1.0

1.4

1.6

0.2

0.4

0.6

1.0

1.4

1.6

2.0

4.5

6.0

Figs 6 and 7

AC CHARACTERISTICS FOR 74HC

GND = 0 V; tf = tf = 6 ns; CL = 50 pF

Tamb (C)

TEST CONDITIONS

74HC

SYMBOL PARAMETER

40 to +85

+25

min.

typ.

max.

min.

max.

40 to +125

min.

UNIT

VCC

WAVEFORMS

(V)

max.

tPHL/ tPLH

propagation delay

nA to nY

41

15

12

125

25

21

155

31

26

190

38

32

ns

2.0

4.5

6.0

Fig.8

tTHL/ tTLH

output transition

time

19

7

6

75

15

13

95

19

15

110

22

19

ns

2.0

4.5

6.0

Fig.8

September 1993

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications. Transfer characteristics are

given below.

Output capability: standard

ICC category: SSI

Note to HCT types

The value of additional quiescent supply current (ICC) for a unit load of 1 is given in the family specifications.

To determine ICC per input, multiply this value by the unit load coefficient shown in the table below.

INPUT

UNIT LOAD COEFFICIENT

nA

0.3

Transfer characteristics for 74HCT

Voltages are referenced to GND (ground = 0 V)

Tamb (C)

TEST CONDITIONS

74HCT

SYMBOL PARAMETER

40 to +85

+25

min.

typ.

max.

min.

max.

40 to +125

min.

UNIT

VCC

WAVEFORMS

(V)

max.

VT+

positive-going

threshold

1.2

1.4

1.41

1.59

1.9

2.1

1.2

1.4

1.9

2.1

1.2

1.4

1.9

2.1

4.5

5.5

Figs 6 and 7

VT

negative-going

threshold

0.5

0.6

0.85

0.99

1.2

1.4

0.5

0.6

1.2

1.4

0.5

0.6

1.2

1.4

4.5

5.5

Figs 6 and 7

VH

hysteresis

(VT+ VT)

0.4

0.4

0.56

0.60

0.4

0.4

0.4

0.4

4.5

5.5

Figs 6 and 7

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; tr = tf = 6 ns; CL = 50 pF

Tamb (C)

TEST CONDITIONS

74HCT

SYMBOL PARAMETER

40 to +85

+25

min.

typ.

max.

min.

max.

40 to +125

min.

UNIT

VCC

(V)

WAVEFORMS

max.

tPHL/ tPLH

propagation delay

nA, to nY

20

34

43

51

ns

4.5

Fig.8

tTHL/ tTLH

output transition

time

15

19

22

ns

4.5

Fig.8

September 1993

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

TRANSFER CHARACTERISTIC WAVEFORMS

Fig.7

Fig.6 Transfer characteristic.

Waveforms showing the definition of VT+,

VT and VH; where VT+ and VT are

between limits of 20% and 70%.

Fig.8 Typical HC transfer characteristics; VCC = 2 V.

Fig.9 Typical HC transfer characteristics; VCC = 4.5 V.

Fig.10 Typical HC transfer characteristics; VCC = 6 V.

Fig.11 Typical HCT transfer characteristics; VCC = 4.5 V.

September 1993

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

Fig.12 Typical HCT transfer characteristics; VCC = 5.5 V.

AC WAVEFORMS

(1) HC : VM = 50%; VI = GND to VCC.

HCT: VM = 1.3 V; VI = GND to 3 V.

Fig.13 Waveforms showing the input (nA) to

output (nY) propagation delays and

output transitions times.

September 1993

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC/HCT14

APPLICATION INFORMATION

The slow input rise and fall times cause additional power

dissipation, this can be calculated using the following

formula:

Pad = fi (tr ICCa + tf ICCa) VCC.

Where:

Pad

= additional power dissipation (W)

fi

= input frequency (MHz)

tr

= input rise time (s); 10% 90%

tf

= input fall time (s); 10% 90%

ICCa

= average additional supply current (A)

Average ICCa differs with positive or negative input

transitions, as shown in Figs 14 and 15.

Fig.14 Average ICC for HC Schmitt trigger devices;

linear change of Vi between 0.1 VCC to

0.9 VCC

Fig.15 Average ICC for HCT Schmitt trigger devices;

linear change of Vi between 0.1 VCC to

0.9 VCC.

HC/HCT14 used in a relaxation oscillator circuit, see

Fig.16.

Note to Application information

All values given are typical unless otherwise specified.

PACKAGE OUTLINES

1

1

HC : f = --- ------------------T 0.8 RC

See 74HC/HCT/HCU/HCMOS Logic Package Outlines.

1

1

HCT : f = --- ---------------------T 0.67 RC

Fig.16 Relaxation oscillator using HC/HCT14.

September 1993

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- DFT For Advanced UserDocument151 pagesDFT For Advanced UserAnonymous UeI6DVNo ratings yet

- 18csl37-Ade Lab ManualDocument41 pages18csl37-Ade Lab ManualEragon ShadeSlayerNo ratings yet

- 74HC05 PDFDocument9 pages74HC05 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 11 PDFDocument1 pageUCC28600 Split 11 PDFHoàng Nam MelNo ratings yet

- 74HC02 PDFDocument5 pages74HC02 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 18 PDFDocument1 pageUCC28600 Split 18 PDFHoàng Nam MelNo ratings yet

- UCC28600 Split 2 PDFDocument1 pageUCC28600 Split 2 PDFHoàng Nam MelNo ratings yet

- Va902 3 PDFDocument74 pagesVa902 3 PDFHoàng Nam MelNo ratings yet

- UCC28061 Split 9 PDFDocument1 pageUCC28061 Split 9 PDFHoàng Nam MelNo ratings yet

- Samsung Power Board Circuit BN44-00353A PDFDocument3 pagesSamsung Power Board Circuit BN44-00353A PDFHoàng Nam MelNo ratings yet

- Analog and Digital Integrated Circuit Question BankDocument12 pagesAnalog and Digital Integrated Circuit Question BankMATHANKUMAR.S67% (3)

- VLSI Module 3 PDFDocument34 pagesVLSI Module 3 PDFGovind M RoddannavarNo ratings yet

- 4.chapter4 CMOS Multistages Differential AmplifierDocument60 pages4.chapter4 CMOS Multistages Differential Amplifierngoc an nguyenNo ratings yet

- KVDocument2 pagesKVsrilatha sriNo ratings yet

- DatasheetDocument6 pagesDatasheetSunil SuwarnkarNo ratings yet

- Digital LogicDocument6 pagesDigital LogicIS-HAK SULEMAN BAAKONo ratings yet

- Mini Project Presentation1 Final Presentation Parking SensorDocument12 pagesMini Project Presentation1 Final Presentation Parking SensorChethan ReddyNo ratings yet

- An Eight-Octant Bipolar Junction Transistor Analog Multiplier Circuit and Its ApplicationsDocument9 pagesAn Eight-Octant Bipolar Junction Transistor Analog Multiplier Circuit and Its ApplicationsTabark AlaamryNo ratings yet

- EL003 Electronic Projects New Collections Vol 3NDocument238 pagesEL003 Electronic Projects New Collections Vol 3NSoeThihaLwin100% (1)

- Datasheet 2sc3052 SMDDocument1 pageDatasheet 2sc3052 SMDed pwtNo ratings yet

- MultivibratorsDocument22 pagesMultivibratorsNGOUNENo ratings yet

- Analog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesDocument59 pagesAnalog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesKarthik v BhatNo ratings yet

- Tas 5613Document34 pagesTas 5613Antonio Laruta ChoqueNo ratings yet

- Circuit Design For Repeated Binary SequenceDocument5 pagesCircuit Design For Repeated Binary SequenceArsalan JahNo ratings yet

- Logic GatesDocument11 pagesLogic Gatesamit kaushikNo ratings yet

- NTE823 Integrated Circuit Low Voltage Audio Amplifier: DescriptionDocument3 pagesNTE823 Integrated Circuit Low Voltage Audio Amplifier: DescriptionAbel RodriguezNo ratings yet

- t and output resistance of 50Ω. Determine theDocument29 pagest and output resistance of 50Ω. Determine theleelee leeNo ratings yet

- Experiment No. 4-Parallel RC and RL CircuitsDocument9 pagesExperiment No. 4-Parallel RC and RL CircuitsArct John Alfante Zamora100% (1)

- A High-Speed Tree-Based 64-Bit Cmos Binary ComparatorDocument5 pagesA High-Speed Tree-Based 64-Bit Cmos Binary ComparatorInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Final Project Report Sachin Basavarajappa KenchammanagathihalliDocument14 pagesFinal Project Report Sachin Basavarajappa KenchammanagathihalliSachin BkNo ratings yet

- Transistor in Common Base (Continuation) and Common Emitter ConfigurationDocument14 pagesTransistor in Common Base (Continuation) and Common Emitter ConfigurationBangla TweaksNo ratings yet

- Vlsi Lab Question SetDocument4 pagesVlsi Lab Question SetM.S.Anandhi100% (1)

- Sinusoidal Steady State-Mcqs: 1. The Value of Current Through The 1 Farad Capacitor of Figure IsDocument13 pagesSinusoidal Steady State-Mcqs: 1. The Value of Current Through The 1 Farad Capacitor of Figure IsAnonymous lt2LFZHNo ratings yet

- Computer Aided Circuit Simulation and VerificationDocument37 pagesComputer Aided Circuit Simulation and VerificationDusanNo ratings yet

- Ugrd-Ee6100 Midterm QuizDocument7 pagesUgrd-Ee6100 Midterm QuizMER HANNo ratings yet

- A3144 Hall Effect Sensor: 3 January 2018 - 0 CommentsDocument5 pagesA3144 Hall Effect Sensor: 3 January 2018 - 0 CommentsSorin NemesNo ratings yet

- Pspice Tutorial 4Document4 pagesPspice Tutorial 4Asseel FleihanNo ratings yet