Professional Documents

Culture Documents

Lab 4

Lab 4

Uploaded by

reghouacheCopyright:

Available Formats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5824)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- AC Spindle Motor Aib Series PDFDocument134 pagesAC Spindle Motor Aib Series PDFAttila SchnéNo ratings yet

- ادارة مشروعات للدكتور ابراهيم عبدالرشيد PDFDocument144 pagesادارة مشروعات للدكتور ابراهيم عبدالرشيد PDFreghouacheNo ratings yet

- 99-Planning Sucessful Museum Buildingm Projects PDFDocument303 pages99-Planning Sucessful Museum Buildingm Projects PDFreghouacheNo ratings yet

- Typical ScheduleDocument14 pagesTypical Schedulereghouache100% (1)

- Sky Scraper SampleDocument1 pageSky Scraper SamplereghouacheNo ratings yet

- Typical Bridge Sched MunicipalDocument4 pagesTypical Bridge Sched MunicipalreghouacheNo ratings yet

- 74270Document177 pages74270junaid112No ratings yet

- Contract Manager User GuideDocument454 pagesContract Manager User Guidesayinsoy8644No ratings yet

- Lab 2Document6 pagesLab 2reghouacheNo ratings yet

- Paint Application Standard No. 2: SSPC: The Society For Protective CoatingsDocument7 pagesPaint Application Standard No. 2: SSPC: The Society For Protective CoatingsreghouacheNo ratings yet

- Paint Application Standard No. 2: SSPC: The Society For Protective CoatingsDocument6 pagesPaint Application Standard No. 2: SSPC: The Society For Protective CoatingsreghouacheNo ratings yet

- IRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument12 pagesIRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeSmain BendeddoucheNo ratings yet

- Ansi C84.1Document24 pagesAnsi C84.1jojagucaNo ratings yet

- EV Wireless Power TransferDocument51 pagesEV Wireless Power TransferCammy KohNo ratings yet

- DJM 900 NexusDocument223 pagesDJM 900 NexusDJ MAONo ratings yet

- 02-1 General Electrical N T4 Rev2Document49 pages02-1 General Electrical N T4 Rev2Fútbol y más100% (1)

- ASTM G62 Holiday Test PDFDocument5 pagesASTM G62 Holiday Test PDFNuttaphonNo ratings yet

- IPD-SelectionGuide AV00-0254EN 052919 PDFDocument72 pagesIPD-SelectionGuide AV00-0254EN 052919 PDFMark ManzanasNo ratings yet

- Front Camera DiagramDocument1 pageFront Camera DiagramGilbert Brian Baysic100% (1)

- Eznec 4nec2: Antenna Design For Free Using Mmana-Gal SoftwareDocument8 pagesEznec 4nec2: Antenna Design For Free Using Mmana-Gal SoftwarehumboldtNo ratings yet

- Archivo de ProyectoDocument12 pagesArchivo de ProyectoAnonymous by1DIx6lhNo ratings yet

- 22a Um001e en eDocument108 pages22a Um001e en eNelson ContrerasNo ratings yet

- High-Frequency Model of The Power Transformer Based On Frequency-Response MeasurementsDocument9 pagesHigh-Frequency Model of The Power Transformer Based On Frequency-Response MeasurementsFernando PaezNo ratings yet

- All Subjects List EEEDocument1 pageAll Subjects List EEENishant SaxenaNo ratings yet

- Cxa1691bm (S) PDFDocument11 pagesCxa1691bm (S) PDFbolevidicNo ratings yet

- Paper - Applications of Phasor Measurement Units (PMUs) in Electric Power System Networks Incorporated With FACTS ControllersDocument19 pagesPaper - Applications of Phasor Measurement Units (PMUs) in Electric Power System Networks Incorporated With FACTS ControllersAhmed SeddikNo ratings yet

- Scmitt Trigger by Using Ic-741 AIM: To Study The Operation of Schmitt Trigger Using Op-Amp Using IC-741. Apparatus Required: SNO Apparatus Range QTYDocument35 pagesScmitt Trigger by Using Ic-741 AIM: To Study The Operation of Schmitt Trigger Using Op-Amp Using IC-741. Apparatus Required: SNO Apparatus Range QTYKarthik KolliparaNo ratings yet

- For Protection Against Electric ShockDocument12 pagesFor Protection Against Electric Shockjayapal100% (1)

- 380910-EIE-0009-01 (0) SLD For UPSDB-03 To 05 For TempDocument1 page380910-EIE-0009-01 (0) SLD For UPSDB-03 To 05 For TempNikhil SutharNo ratings yet

- B&C SpeakersDocument1 pageB&C SpeakersDj6693316No ratings yet

- A2SIDocument30 pagesA2SIJF MendozaNo ratings yet

- Motor SiemensDocument15 pagesMotor SiemenshectorNo ratings yet

- Is 1231.1974Document22 pagesIs 1231.1974Jayam Harinatha GupthaNo ratings yet

- Aa5tb Magnetic Loop v1Document9 pagesAa5tb Magnetic Loop v1api-3839541No ratings yet

- Resonant Gravity Field Coil PDFDocument16 pagesResonant Gravity Field Coil PDFClover1897No ratings yet

- 18EE71-Module-5-Part 2 Notes - 2022Document9 pages18EE71-Module-5-Part 2 Notes - 2022siddeshgssiddu345No ratings yet

- Axial Lead PINs DatasheetDocument6 pagesAxial Lead PINs DatasheetBalaji Triplant100% (1)

- Exactly About Nikola Tesla Free Strength Generator..20140501.134857Document13 pagesExactly About Nikola Tesla Free Strength Generator..20140501.134857cherryfine78No ratings yet

- Alarm Annunciator Mbas 9400 PDFDocument1 pageAlarm Annunciator Mbas 9400 PDFAnonymous SDeSP1No ratings yet

- JBL SRX815 Passive SpeakerDocument6 pagesJBL SRX815 Passive SpeakerChristian Velasco100% (1)

Lab 4

Lab 4

Uploaded by

reghouacheOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab 4

Lab 4

Uploaded by

reghouacheCopyright:

Available Formats

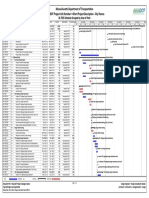

ENGG1203: Introduction to Electrical and Electronic Engineering

Second Semester, 201213

Lab 4

Objective:

To connect the abstract digital logic world to the physical world that

interacts with voltage, current and resistance.

To complete the ball counter with the photo detector and state machine

implemented in FPGA.

Equipment youll need in this lab:

(a) Multi-meter

(b) Wire Kit

(e) Tunnel Connector

(f) FPGA Cable

(c)

Potentiometer

(d) Tunnel

(g) FPGA Connector

(h) Breadboard

Figure 1: Materials for this lab

......................................................................

1 Finding your lab partner

You will be working with a randomly assigned partner for this lab. To find your assigned lab

partner and the assigned table,

1. Log in to Moodle.

2. Select the assignment Lab 4 Partner

Please proceed to your assigned table.

......................................................................

2 Getting the files

Download the files for this lab from

ENGG1203: Introduction to Electrical and Electronic Engineering

Lab 4

http://www.eee.hku.hk/~engg1203/sp13/labs/lab4.zip

......................................................................

3 Safety First

Read the lab safety notes from

http://www.eee.hku.hk/~engg1203/sp13/handouts/lab-safety-regulation.pdf

......................................................................

4 Breaking the Digital Logic Abstraction

In digital logic design, signals take the abstract value TRUE/FALSE, HIGH/LOW, 1/0.

Such definition is useful to abstract the low level details of the circuit such that very complex

systems can be composed easily.

In reality, physical values such as voltage and current are used to represent such discrete logical

values. In particular, any physical values that do not overlap may be used to represent TRUE

and FALSE.

4.1 Interfacing with the FPGA board We will start with determining I/O voltage that are

being used by the FPGA on the Basys2 board to represent the logical value of TRUE and

FALSE. In order to do that, a simple design is created to route several internal signals to I/O

connectors of the Basys2 board.

Load the file testio.xise. Take a look at file testio.sch. At the top part of the schematic, it

has a simple design that directly connects button 1 to the output testout. At the bottom, it has

another signal testin that connects to LED4. The signals testin and testout are connected

to the I/O connector JA on the Basys2 board with the following connection:

Signal

testin

testout

I/O Location

B2

J3

These connections are specified by a user constraint file (ucf).

Open the file lab4.ucf and verify the connection of testin and testout.

Figure 2: Internal connections on a breadboard

4.2 Breadboard A breadboard is a handy tool for constructing simple circuits. Circuit components, such as resistors and integrated circuits (ICs), can be inserted into one of the many tiny

Page 2 of 8

ENGG1203: Introduction to Electrical and Electronic Engineering

Lab 4

sockets, or holes, in the breadboard. The holes are internally connected according to Figure 2.

All the holes in each of the top and bottom two rows are connected. The holes in the middle are

connected vertically in a group of five.

When constructing circuits, the two rows in the top and bottom should be used for distributing

power and ground. Integrated circuits should be inserted in the middle gap. When inserting

wires into the holes, make sure they are securely pushed all the way down. Try to use wires of

appropriate length so there is no loose wire left hanging.

25

30

35

25

30

35

15

15

20

10

10

20

5

5

Pin 1

1

Before you can obtain the FPGA board from our TAs, first make the following connection on

the breadboard:

The FPGA is connected to the breadboard using an FPGA Cable. On each end of the cable

there is an extra dot (See Figure 3(a)) that helps identify the location of Pin 1. When using

the FPGA Cable, make sure it is connected with the correct orientation.

(a) Pin 1 on an FPGA cable

(b) I/O Connector JA on Basys2 Board

Figure 3: FPGA Connections

4.3 Checkoff 1 The other end of the FPGA cable should be connected to the connector JA on

the Basys2 board. The connector is located at the corner of the board as shown in Figure 3(b).

Pin 1 of the FPGA cable should be connected to VCC of connector JA. As a result, Pin 6 will

be connected to the pin labeled as B2 on the same connector.

From the picture in Figure 3(b), answer the following questions before asking your TA/LA to

give you a board.

Page 3 of 8

ENGG1203: Introduction to Electrical and Electronic Engineering

Lab 4

Once you connect the FPGA board to the breadboard, which holes are connected

to VCC of the FPGA board?

Similarly, which holes are connected to testout? Which holes are connected to

testin?

On the breadboard, how do you measure the voltage value of VCC, testout,

and testin?

4.4 Using the FPGA Cable, connect from the I/O connector JA from the Basys2 board to

the breadboard. Also connect the FPGA board to the computer. Turn on the power switch on

the FPGA board.

Measure the voltage of VCC on the breadboard using a DMM. It is the main power source for

the breadboard. What is the value of VCC?

Vcc =

4.5 Output from FPGA Implement the design in testio.xise and download the implemented

testio.bit to the FPGA board. Once downloaded, the value of button 1 will be reflected at

the output testout. Measure the voltage of testout on the breadboard. What is the voltage

(VL ) when button 1 is not pressed? What is the voltage when button 1 is pressed (VH )?

VL =

VH =

4.6 Using a POT Now that we know what voltage level the FPGA outputs to represent TRUE

and FALSE, we want to know what the board expects the outside to put in its input pin to

represent TRUE and FALSE. In other word, we want to determine the threshold voltage that

the FPGA uses to differentiate a TRUE signal from a FALSE signal.

For that, we will use a potentiometer (POT). A POT is a device that allows a user to adjust

its resistance by turning a knob. The POT we are using in this lab can be represented by the

following diagram:

Pin 2

Pin 1

Pin 3

(a) Circuit Diagram

(b) Pin Location

Figure 4: Potentiometer

As can be seen from the diagram above, the resistance between pin 1 and 3 (R13 ) is constant

regardless of the dial position of the POT. The resistance between pin 1 and 2 (R12 ), and pin 2

and 3 (R23 ) varies when the dial of the POT is turned, with R12 + R23 = R13 .

Using a DMM (with the dial switched to measuring resistance, start with 2000), measure R13 .

Also, verify that R12 and R23 varies as the dial is turned. When you have finished, turn the dial

until R12 = R13 /2.

Page 4 of 8

ENGG1203: Introduction to Electrical and Electronic Engineering

Lab 4

R13 =

4.7 Input to FPGA Disconnect the FPGA before you change the circuit on the breadboard. Then, construct the following circuit on the breadboard.

VCC

+

Vtestin

GND

Pin 1

20

15

10

It can be achieved simply by inserting the POT into the FPGA. Make sure the 3 pins of the

POT are inserted on different columns of the board. Your breadboard should look similar to the

following diagram:

Connect pin 2 of the POT to pin 6 on the FPGA connector. Once you have finished constructing

the circuit, double check all the connections are correct. (At the minimum, you should check

if there is any short circuit between the two power rails.) After you have double checked

your connection, reconnect the FPGA, power it on, and configure it with testio.bit again.

4.8 Finding the input threshold Assuming you have set your POT above such that R12 =

R13 /2, read the voltage Vtestin using the DMM, what is the voltage?

Vtestin =

Now slowly turn the dial on the POT. It should change the value Vtestin depending on the

direction you are turning. When Vtestin drops below certain value (VT ), you will find that LED

4 will be turned off. What is the value VT ?

VT =

Page 5 of 8

ENGG1203: Introduction to Electrical and Electronic Engineering

Lab 4

To define a logical interface for input to FPGA, we usually define two values: VIL and VIH .

VIL is the maximum input voltage that the FPGA will regard as logical FALSE, and VIH is the

minimum input voltage that the FPGA will regard as logical TRUE.

Based on the above measurements, make suggestion on the values of VIL and VIH .

VIL =

VIH =

4.9 Checkoff 2

Demonstrate your working connection between the FPGA and the breadboard and

answer the following questions:

What are the values of VL , VH and VT ? What do these values represent?

What happens to the LED when Vtestin VT ?

Explain your choice of VIL and VIH . Can we set VIL = VIH = VT ?.

......................................................................

5 Light at the end of the Tunnel

Last week you have constructed a simple ball counter using digital logic circuits. A button on

the Basys2 board was used to mimic the effect of a ball rolling through a detector. This week,

you will construct the ball detector and connect to the ball counter from last week. This ball

counter will eventually become part of your final project of this class.

5.1 A ball detection tunnel has been constructed using a laser diode and a photo detector.

When a ball rolls through the tunnel, it blocks the laser, thereby changing the resistance of the

photo detector. Your circuit should use this change in resistance to signal if a ball is detected.

When there is a ball blocking the laser, it should produce a logical HIGH signal. When there is

no ball, it should produce a logical LOW signal.

Figure 5(a) shows the internal circuit of the ball tunnel. It should be connected to the breadboard

using the Tunnel Cable, which has a 5 2 pin connector. Pin 1 of the cable is aligned with the

RED wire. Note that every other pins (i.e. 1 & 2, 3 & 4, etc) are connected together for sake of

simplicity.

Cable Connector

R+

Tunnel Cable

Ball Tunnel Internal

2

Rof f Ron

not connected

100

L+

9 10

(a) Tunnel Connection

(b) Pin Numbers

Figure 5: Ball Tunnel Connections

The first step is to determine the characteristics of the photodetector. A photodetector is simply

a resistor with a variable resistance that depends on the amount of light shining on it. When

Page 6 of 8

ENGG1203: Introduction to Electrical and Electronic Engineering

Lab 4

light is shining on the photodetector, it has resistance Ron . When there is no light shining on the

photodetector, it has resistance Rof f . Take a ball tunnel and measure the values Ron and Rof f .

You need to supply power to the laser diode in the tunnel using the FPGA board. Connect L+

to VCC and L to GND.

Rof f =

Ron =

5.2 Potential Divider Design a potential divider circuit in the following space that produces a voltage (Vdin ) to represent the presence/absence of ball through the tunnel. The voltage

signal Vdin will be connected to the din input of the ball counter implemented on the FPGA

board. Your circuit has the following design criteria:

When there is no ball blocking the photodetector, Vdin is at a voltage that represents logic

LOW

When the ball is blocking the photodetector, Vdin should be at a voltage that represents

logic HIGH.

Your potential divider circuit should contain only 2 resistors: (i) the variable resistor representing

the photodetector; and (ii) a reference resistor Rref . Determine the value of Rref using the values

of Rof f , Ron and the input threshold voltage VT obtained above,

5.3 Finding Rref What is the range of valid values for Rref ? What value have you picked?

Rref =

5.4 Achieving Rref using a POT When using only Pin 1 and 2 of a potentiometer, you can

obtain a resistor with variable resistance. Tune your POT such that the resistance between Pin

1 and 2 is the chosen value of Rref above.

5.5 The following diagram will guide you in constructing the circuit in the breadboard. The left

hand side represent the FPGA Cable connection, and the right hand side represent the Tunnel

Cable connection. Connect the dots to implement your potential divider circuit.

Page 7 of 8

ENGG1203: Introduction to Electrical and Electronic Engineering

din

Lab 4

6

1 2

2

1

L+

GND

VCC

R+

L

9 10

5.6 Connect Them All Construct your circuit above on the breadboard. Connect the FPGA

and the Tunnel using the FPGA Cable and the Tunnel Cable respectively. You should keep your

wire straight, and only in vertical and horizontal orientation.

Finally, load the file cnt3.xise, which contains a sample implementation of the ball counter

from the last lab. Implement the design and download the resulting cnt3.bit to the FPGA.

If all things work, you should now be able to count the number of balls rolling through the

tunnel.

5.7 Checkoff 3

Show to your TA a completed circuit connecting the Tunnel to the FPGA. Demonstrate the function of the tunnel.

What happens if the ball rolls too fast? How can you avoid that problem?

What happens if the ball rolls too slowly?

Page 8 of 8

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5824)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- AC Spindle Motor Aib Series PDFDocument134 pagesAC Spindle Motor Aib Series PDFAttila SchnéNo ratings yet

- ادارة مشروعات للدكتور ابراهيم عبدالرشيد PDFDocument144 pagesادارة مشروعات للدكتور ابراهيم عبدالرشيد PDFreghouacheNo ratings yet

- 99-Planning Sucessful Museum Buildingm Projects PDFDocument303 pages99-Planning Sucessful Museum Buildingm Projects PDFreghouacheNo ratings yet

- Typical ScheduleDocument14 pagesTypical Schedulereghouache100% (1)

- Sky Scraper SampleDocument1 pageSky Scraper SamplereghouacheNo ratings yet

- Typical Bridge Sched MunicipalDocument4 pagesTypical Bridge Sched MunicipalreghouacheNo ratings yet

- 74270Document177 pages74270junaid112No ratings yet

- Contract Manager User GuideDocument454 pagesContract Manager User Guidesayinsoy8644No ratings yet

- Lab 2Document6 pagesLab 2reghouacheNo ratings yet

- Paint Application Standard No. 2: SSPC: The Society For Protective CoatingsDocument7 pagesPaint Application Standard No. 2: SSPC: The Society For Protective CoatingsreghouacheNo ratings yet

- Paint Application Standard No. 2: SSPC: The Society For Protective CoatingsDocument6 pagesPaint Application Standard No. 2: SSPC: The Society For Protective CoatingsreghouacheNo ratings yet

- IRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument12 pagesIRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeSmain BendeddoucheNo ratings yet

- Ansi C84.1Document24 pagesAnsi C84.1jojagucaNo ratings yet

- EV Wireless Power TransferDocument51 pagesEV Wireless Power TransferCammy KohNo ratings yet

- DJM 900 NexusDocument223 pagesDJM 900 NexusDJ MAONo ratings yet

- 02-1 General Electrical N T4 Rev2Document49 pages02-1 General Electrical N T4 Rev2Fútbol y más100% (1)

- ASTM G62 Holiday Test PDFDocument5 pagesASTM G62 Holiday Test PDFNuttaphonNo ratings yet

- IPD-SelectionGuide AV00-0254EN 052919 PDFDocument72 pagesIPD-SelectionGuide AV00-0254EN 052919 PDFMark ManzanasNo ratings yet

- Front Camera DiagramDocument1 pageFront Camera DiagramGilbert Brian Baysic100% (1)

- Eznec 4nec2: Antenna Design For Free Using Mmana-Gal SoftwareDocument8 pagesEznec 4nec2: Antenna Design For Free Using Mmana-Gal SoftwarehumboldtNo ratings yet

- Archivo de ProyectoDocument12 pagesArchivo de ProyectoAnonymous by1DIx6lhNo ratings yet

- 22a Um001e en eDocument108 pages22a Um001e en eNelson ContrerasNo ratings yet

- High-Frequency Model of The Power Transformer Based On Frequency-Response MeasurementsDocument9 pagesHigh-Frequency Model of The Power Transformer Based On Frequency-Response MeasurementsFernando PaezNo ratings yet

- All Subjects List EEEDocument1 pageAll Subjects List EEENishant SaxenaNo ratings yet

- Cxa1691bm (S) PDFDocument11 pagesCxa1691bm (S) PDFbolevidicNo ratings yet

- Paper - Applications of Phasor Measurement Units (PMUs) in Electric Power System Networks Incorporated With FACTS ControllersDocument19 pagesPaper - Applications of Phasor Measurement Units (PMUs) in Electric Power System Networks Incorporated With FACTS ControllersAhmed SeddikNo ratings yet

- Scmitt Trigger by Using Ic-741 AIM: To Study The Operation of Schmitt Trigger Using Op-Amp Using IC-741. Apparatus Required: SNO Apparatus Range QTYDocument35 pagesScmitt Trigger by Using Ic-741 AIM: To Study The Operation of Schmitt Trigger Using Op-Amp Using IC-741. Apparatus Required: SNO Apparatus Range QTYKarthik KolliparaNo ratings yet

- For Protection Against Electric ShockDocument12 pagesFor Protection Against Electric Shockjayapal100% (1)

- 380910-EIE-0009-01 (0) SLD For UPSDB-03 To 05 For TempDocument1 page380910-EIE-0009-01 (0) SLD For UPSDB-03 To 05 For TempNikhil SutharNo ratings yet

- B&C SpeakersDocument1 pageB&C SpeakersDj6693316No ratings yet

- A2SIDocument30 pagesA2SIJF MendozaNo ratings yet

- Motor SiemensDocument15 pagesMotor SiemenshectorNo ratings yet

- Is 1231.1974Document22 pagesIs 1231.1974Jayam Harinatha GupthaNo ratings yet

- Aa5tb Magnetic Loop v1Document9 pagesAa5tb Magnetic Loop v1api-3839541No ratings yet

- Resonant Gravity Field Coil PDFDocument16 pagesResonant Gravity Field Coil PDFClover1897No ratings yet

- 18EE71-Module-5-Part 2 Notes - 2022Document9 pages18EE71-Module-5-Part 2 Notes - 2022siddeshgssiddu345No ratings yet

- Axial Lead PINs DatasheetDocument6 pagesAxial Lead PINs DatasheetBalaji Triplant100% (1)

- Exactly About Nikola Tesla Free Strength Generator..20140501.134857Document13 pagesExactly About Nikola Tesla Free Strength Generator..20140501.134857cherryfine78No ratings yet

- Alarm Annunciator Mbas 9400 PDFDocument1 pageAlarm Annunciator Mbas 9400 PDFAnonymous SDeSP1No ratings yet

- JBL SRX815 Passive SpeakerDocument6 pagesJBL SRX815 Passive SpeakerChristian Velasco100% (1)