Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

24 viewsDesignof Mips2part PDF

Designof Mips2part PDF

Uploaded by

doomachaleyThis document discusses the design of a multi-cycle MIPS processor. It explains that a multi-cycle implementation is better than a single-cycle implementation because it allows for faster instructions to execute without being delayed by slower instructions like load and store. The document outlines a 5-stage pipeline for instruction execution, including instruction fetch, instruction decode, execute, memory access, and writeback stages. It notes that intermediate registers are needed to store outputs from one stage for use in later stages of instruction execution.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You might also like

- HW Assignment 5Document3 pagesHW Assignment 5abdul basitNo ratings yet

- Pooja VashisthDocument40 pagesPooja VashisthApurva SinghNo ratings yet

- SMS Firewall Solution Description 2019Document30 pagesSMS Firewall Solution Description 2019Thái Duy Hòa100% (2)

- Riscv BoomDocument85 pagesRiscv BoomMartinNo ratings yet

- Introduction To Computing Systems:: From Bits and Gates To C and BeyondDocument15 pagesIntroduction To Computing Systems:: From Bits and Gates To C and BeyondNirmal GuptaNo ratings yet

- Design of The MIPS ProcessorDocument24 pagesDesign of The MIPS Processorwelcome to my worldNo ratings yet

- Multi-Cycle Implementation of MIPS: Revisit The 1-Cycle VersionDocument10 pagesMulti-Cycle Implementation of MIPS: Revisit The 1-Cycle VersionbigfatdashNo ratings yet

- RISC Instruction Set:: I) Data Manipulation InstructionsDocument8 pagesRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNo ratings yet

- Computer Organization: An Introduction To RISC Hardware: 6.1 An Overview of PipeliningDocument12 pagesComputer Organization: An Introduction To RISC Hardware: 6.1 An Overview of PipeliningAmrendra Kumar MishraNo ratings yet

- Mips ImplementationDocument47 pagesMips ImplementationJEEVANANTHAM GNo ratings yet

- Files 3 Homework Solutions A5 Solution 081Document5 pagesFiles 3 Homework Solutions A5 Solution 081Ivanildo GomesNo ratings yet

- Lab Sheet 6 Single Cycle Datapath FinalDocument3 pagesLab Sheet 6 Single Cycle Datapath FinalSANJEEV MALLICKNo ratings yet

- UNIT-3: MIPS InstructionsDocument15 pagesUNIT-3: MIPS InstructionsMukeshram.B AIDS20No ratings yet

- Computer Organization and ArchitectureDocument108 pagesComputer Organization and ArchitectureMuhammad Zeeshan MughalNo ratings yet

- The Processor - IntroductionDocument10 pagesThe Processor - Introductionsas21-d01-s6-cs15No ratings yet

- Computer Organization-Single CycleDocument23 pagesComputer Organization-Single Cyclev2brotherNo ratings yet

- Execution of InstructionDocument60 pagesExecution of InstructionKr RanjithNo ratings yet

- Multicycle Datapath PDFDocument22 pagesMulticycle Datapath PDFShivam KhandelwalNo ratings yet

- Lectures Section 3 ModifiedDocument73 pagesLectures Section 3 ModifiedcoventryUkNo ratings yet

- The Processor: (Datapath and Pipelining)Document144 pagesThe Processor: (Datapath and Pipelining)paranoid486No ratings yet

- UNIT-5: Pipeline and Vector ProcessingDocument63 pagesUNIT-5: Pipeline and Vector ProcessingAkash KankariaNo ratings yet

- Co Unit2 Part1Document11 pagesCo Unit2 Part1Manjushree N.SNo ratings yet

- Chapter 5Document86 pagesChapter 5Muhammad OmerNo ratings yet

- Introduction To MIPS ArchitectureDocument10 pagesIntroduction To MIPS ArchitectureJahanzaib AwanNo ratings yet

- Draw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerDocument7 pagesDraw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerhayerpaNo ratings yet

- Cyan 2800398239029h09fn0ivj0vcjb0Document16 pagesCyan 2800398239029h09fn0ivj0vcjb0Anonymous zWBss8LKNo ratings yet

- Single Cycle Datapath PDFDocument30 pagesSingle Cycle Datapath PDFShivam KhandelwalNo ratings yet

- CMPEN 335 - Computer Organization and Design, Lab 3: 1. PipeliningDocument5 pagesCMPEN 335 - Computer Organization and Design, Lab 3: 1. PipeliningRoberta AndreeaNo ratings yet

- Unit 4 NotesDocument15 pagesUnit 4 Notesshinyshiny966No ratings yet

- Unit 2 - Embedded SystemDocument75 pagesUnit 2 - Embedded Systemsujith100% (4)

- Chapter Four The Processor: Datapath and ControlDocument45 pagesChapter Four The Processor: Datapath and ControlOsama AlqahtaniNo ratings yet

- L13 Multicycle DatapathDocument62 pagesL13 Multicycle DatapathIsaacNo ratings yet

- Basic Performance EquationDocument42 pagesBasic Performance EquationVishal BasugadeNo ratings yet

- Lecture 4 8405 Computer ArchitectureDocument15 pagesLecture 4 8405 Computer ArchitecturebokadashNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- Chapter1 - Basic Structure of ComputersDocument119 pagesChapter1 - Basic Structure of ComputersAnkit SharmaNo ratings yet

- Chapter 1 - Basic Structure of ComputersDocument33 pagesChapter 1 - Basic Structure of Computersanusrini23No ratings yet

- 5.3 Integer and Floating Point Pipeline StagesDocument12 pages5.3 Integer and Floating Point Pipeline Stagesnehareddy.alla17No ratings yet

- Questions With AnswersDocument22 pagesQuestions With AnswersYuva SathiyamoorthyNo ratings yet

- Pipelined Processor DesignDocument28 pagesPipelined Processor DesignLihau TanNo ratings yet

- CA U3 Sjit PDFDocument95 pagesCA U3 Sjit PDFThe Smart Boy KungFuPawnNo ratings yet

- 06 Programming in 8085Document10 pages06 Programming in 8085Dipak55550% (2)

- FinalDocument26 pagesFinalHứa Đăng KhoaNo ratings yet

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDocument10 pagesCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrNo ratings yet

- Lecture6 ARMDocument50 pagesLecture6 ARMRohith ThurlapatiNo ratings yet

- Fetch-Decode-Execute CycleDocument5 pagesFetch-Decode-Execute CycleIzharSeizerNo ratings yet

- Chapter1 - Basic Structure of ComputersDocument123 pagesChapter1 - Basic Structure of ComputersAlbert AlexNo ratings yet

- Reduced Instruction Set Computer (Risc) Complex Instruction Set Computer (Cisc)Document7 pagesReduced Instruction Set Computer (Risc) Complex Instruction Set Computer (Cisc)Sundari MuthuNo ratings yet

- Assignment QuestionsDocument3 pagesAssignment QuestionsSarbendu PaulNo ratings yet

- Instant Download PDF Computer Organization and Design MIPS Edition 5th Edition Patterson Solutions Manual Full ChapterDocument44 pagesInstant Download PDF Computer Organization and Design MIPS Edition 5th Edition Patterson Solutions Manual Full Chapterhickenthess100% (4)

- Control Unit Design NewDocument31 pagesControl Unit Design NewSabareesh MuralidharanNo ratings yet

- Ebook Computer Organization and Design Mips Edition 5Th Edition Patterson Solutions Manual Full Chapter PDFDocument43 pagesEbook Computer Organization and Design Mips Edition 5Th Edition Patterson Solutions Manual Full Chapter PDFjoanneesparzagwjxmyqont100% (12)

- Register FileDocument6 pagesRegister FilejayaprasadkalluriNo ratings yet

- Computer Architecture MIPS Processor DescriptionDocument41 pagesComputer Architecture MIPS Processor DescriptionAsif HussainNo ratings yet

- Unit1 Addressing Modes and GPRDocument70 pagesUnit1 Addressing Modes and GPRsaumya2213215No ratings yet

- Ca Unit 3 PrabuDocument24 pagesCa Unit 3 Prabu6109 Sathish Kumar J100% (1)

- Basic Processing Unit:: Fundamental ConceptsDocument35 pagesBasic Processing Unit:: Fundamental ConceptsJoseph JohnNo ratings yet

- Multi Cycle Data PathDocument21 pagesMulti Cycle Data PathSushma S MurthyNo ratings yet

- Computer Architecture 16 MarksDocument28 pagesComputer Architecture 16 MarksBalachandar2000100% (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Python Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreFrom EverandPython Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreNo ratings yet

- Chapter 7Document24 pagesChapter 7doomachaleyNo ratings yet

- Chapter 0Document13 pagesChapter 0doomachaleyNo ratings yet

- Testing 11Document18 pagesTesting 11doomachaleyNo ratings yet

- Testing 7Document20 pagesTesting 7doomachaleyNo ratings yet

- A UVM-Based Smart Functional Verification Platform: Concepts, Pros, Cons, and OpportunitiesDocument6 pagesA UVM-Based Smart Functional Verification Platform: Concepts, Pros, Cons, and OpportunitiesdoomachaleyNo ratings yet

- Soc Level Verification Using System VerilogDocument3 pagesSoc Level Verification Using System VerilogdoomachaleyNo ratings yet

- Functional Verification 2003: Technology, Tools and MethodologyDocument5 pagesFunctional Verification 2003: Technology, Tools and MethodologydoomachaleyNo ratings yet

- Verification of AMBA Bus Model Using SystemVerilogDocument5 pagesVerification of AMBA Bus Model Using SystemVerilogdoomachaleyNo ratings yet

- Introduction To Operating SystemDocument59 pagesIntroduction To Operating SystemSAPTARSHI GHOSHNo ratings yet

- Hardware Sep 02Document2 pagesHardware Sep 02Saye IkhwanNo ratings yet

- Embedded System BasicsDocument33 pagesEmbedded System BasicssubburampureNo ratings yet

- SPHE8281DDocument35 pagesSPHE8281Ddiego-tNo ratings yet

- OS First PDFDocument263 pagesOS First PDFEtoos LecturesNo ratings yet

- Peripheral Remote IO Adapter BMXPRA0100 User ManualDocument48 pagesPeripheral Remote IO Adapter BMXPRA0100 User ManualHossam eidNo ratings yet

- Docker CLI Reference DocumentationDocument1,151 pagesDocker CLI Reference DocumentationJony NguyễnNo ratings yet

- Nios 2 ProcessorDocument6 pagesNios 2 ProcessorSoundarya SvsNo ratings yet

- AI Assignment - 2Document6 pagesAI Assignment - 2ERMIAS AmanuelNo ratings yet

- PIC18F4520 Instruction SetDocument4 pagesPIC18F4520 Instruction SetCongtan94No ratings yet

- Canary System OverviewDocument7 pagesCanary System OverviewDmitry SolovovNo ratings yet

- System Programming Unit 1-2Document23 pagesSystem Programming Unit 1-2mojbarNo ratings yet

- Week 4 - Computer Organization & ArchitectureDocument59 pagesWeek 4 - Computer Organization & ArchitecturedindNo ratings yet

- SyllabusDocument57 pagesSyllabusYasin ArslanNo ratings yet

- AAST-CC312-Fall 21-Lec 08Document17 pagesAAST-CC312-Fall 21-Lec 08youssef hossamNo ratings yet

- IMPLEMENTATION OF MACRO PROCESSOR System Software Lab ProgramDocument2 pagesIMPLEMENTATION OF MACRO PROCESSOR System Software Lab ProgramBalaji Shanmugam0% (1)

- Osass 1Document2 pagesOsass 1Saad SiddiquiNo ratings yet

- CE403 - Computer Organization and ArchitectureDocument4 pagesCE403 - Computer Organization and Architecturejon rey lumayagNo ratings yet

- Test GX WORK3Document71 pagesTest GX WORK3มานพ ไทยNo ratings yet

- GSE - 201710 - IBM - Z14-Technical - Overview - Final SUPER GOOD ONEDocument156 pagesGSE - 201710 - IBM - Z14-Technical - Overview - Final SUPER GOOD ONERajeshNo ratings yet

- IT 101 Syllabus ObeDocument11 pagesIT 101 Syllabus ObeJONL IDULSANo ratings yet

- Assignment 1 OsDocument3 pagesAssignment 1 OsAbdul Wajid HanjrahNo ratings yet

- Pre-Requisite Contents MS-Programs FSC-NUCES-ISBDocument2 pagesPre-Requisite Contents MS-Programs FSC-NUCES-ISBHafiz Saddique MalikNo ratings yet

- Module 5 Notes - COADocument6 pagesModule 5 Notes - COAAashu PrasadNo ratings yet

- Low Level Assembly Lang., Machine CodesDocument10 pagesLow Level Assembly Lang., Machine CodessyukzNo ratings yet

- Assembly Language Lecture From Engr GatdulaDocument16 pagesAssembly Language Lecture From Engr GatdulaMary Rose SantiagoNo ratings yet

- AMD Ryzen 3 2200G 35 GHZ Quad-Core AM4 ProcessorDocument5 pagesAMD Ryzen 3 2200G 35 GHZ Quad-Core AM4 ProcessorVictorgotNo ratings yet

Designof Mips2part PDF

Designof Mips2part PDF

Uploaded by

doomachaley0 ratings0% found this document useful (0 votes)

24 views13 pagesThis document discusses the design of a multi-cycle MIPS processor. It explains that a multi-cycle implementation is better than a single-cycle implementation because it allows for faster instructions to execute without being delayed by slower instructions like load and store. The document outlines a 5-stage pipeline for instruction execution, including instruction fetch, instruction decode, execute, memory access, and writeback stages. It notes that intermediate registers are needed to store outputs from one stage for use in later stages of instruction execution.

Original Description:

Original Title

Designof mips2part.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document discusses the design of a multi-cycle MIPS processor. It explains that a multi-cycle implementation is better than a single-cycle implementation because it allows for faster instructions to execute without being delayed by slower instructions like load and store. The document outlines a 5-stage pipeline for instruction execution, including instruction fetch, instruction decode, execute, memory access, and writeback stages. It notes that intermediate registers are needed to store outputs from one stage for use in later stages of instruction execution.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

24 views13 pagesDesignof Mips2part PDF

Designof Mips2part PDF

Uploaded by

doomachaleyThis document discusses the design of a multi-cycle MIPS processor. It explains that a multi-cycle implementation is better than a single-cycle implementation because it allows for faster instructions to execute without being delayed by slower instructions like load and store. The document outlines a 5-stage pipeline for instruction execution, including instruction fetch, instruction decode, execute, memory access, and writeback stages. It notes that intermediate registers are needed to store outputs from one stage for use in later stages of instruction execution.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 13

Design of the MIPS Processor (contd)

First, revisit the datapath for add, sub, lw, sw.

We will augment it to accommodate the beq

and j instructions.

Execution of branch instructions

beq $at, $zero, L

add $v1, $v0, $zero

add $v1, $v1, $v1

j

somewhere

L: add $v1, $v0, $v0

Offset= 3x4=12

The offset must be added to the next PC to

generate the target address for branch.

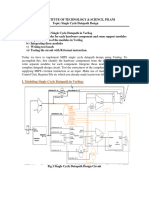

The modified version of MIPS

The final datapath for single cycle MIPS. Find

out which paths the signal follow for lw, sw,

add and beq instructions

Executing R-type instructions

The ALUop will be determined by the value of the

opcode field and the function field of the instruction

word

Executing LW instruction

Executing beq instruction

The branch may

Control signal table

This table summarizes what control signals are

needed to execute an instruction. The set of

control signals vary from one instruction to

another.

How to implement the control unit?

The Control Unit

ALUsrc

I [31-26, 15-0]

MemRead

Control

MemWrite

ALUop

Instruction

Memory

RegDst

Regwrite

All control signals are not shown here

1-cycle implementation is not used

Why? Because the length of the clock cycle will

always be determined by the slowest operation

(lw, sw) even when the data memory is not

used. Practical implementations use multiple

cycles per instruction, which fixes some

shortcomings of the 1-cycle implementation.

Faster instructions are not held back by the slower

instructions

The clock cycle time can be decreased.

Eventually simplifies the implementation of

pipelining, the universal speed-up technique

This requires some changes in the datapath

Multi-cycle implementation of MIPS

!"#$%&'#()"$"%'%*('+,-.-/(')(#$"01''

The multi-cycle version

Note that we have eliminated two adders, and

used only one memory unit (so it is Princeton

architecture) that contains both instructions

and data. It is not essential to have a single

memory unit, but it shows an alternative

design of the datapath.

Intermediate registers are necessary

In each cycle, a fraction of the instruction is

executed

Five stages of instruction execution

Cycle 1. Instruction fetch and PC increment

!"#$%&'(&&)%*+,-.&/012#%/&3204&56%&2%.,/5%2&3,$%&&&

Cycle 3 Performing an ALU computation

Cycle 4 Reading or writing (data) memory

Cycle 5 Storing data back to the register file

Why intermediate registers?

Sometimes we need the output of a

functional unit in a later clock cycle during

the execution of an instruction.

(Example: The instruction word fetched in stage 1

determines the destination of the register write in

stage 5. The ALU result for an address computation

in stage 3 is needed as the memory address for lw or

sw in stage 4.)

These outputs must be stored in

intermediate registers for future use.

Otherwise they will be lost by the next

clock cycle.

(Instruction read in stage 1 is saved in Instruction

register. Register file outputs from stage 2 are saved

in registers A and B. The ALU output will be stored in

a register ALUout. Any data fetched from memory in

stage 4 is kept in the Memory data register MDR.)

The Five Cycles of MIPS

(Instruction Fetch)

IR:= Memory[PC]

PC:= PC+4

(Instruction decode and Register fetch)

A:= Reg[IR[25:21]], B:=Reg[IR[20:16]]

ALUout := PC + sign-extend(IR[15:0]]

(Execute|Memory address|Branch completion)

Memory reference: ALUout:= A+ IR[15:0]

R-type (ALU): ALUout:= A op B

Branch: if A=B then PC := ALUout

(Memory access | R-type completion)

LW: MDR:= Memory[ALUout]

SW: Memory[ALUout]:= B

R-type: Reg[IR[15:11]]:= ALUout

(Writeback)

LW:

Reg[[20:16]]:= MDR

You might also like

- HW Assignment 5Document3 pagesHW Assignment 5abdul basitNo ratings yet

- Pooja VashisthDocument40 pagesPooja VashisthApurva SinghNo ratings yet

- SMS Firewall Solution Description 2019Document30 pagesSMS Firewall Solution Description 2019Thái Duy Hòa100% (2)

- Riscv BoomDocument85 pagesRiscv BoomMartinNo ratings yet

- Introduction To Computing Systems:: From Bits and Gates To C and BeyondDocument15 pagesIntroduction To Computing Systems:: From Bits and Gates To C and BeyondNirmal GuptaNo ratings yet

- Design of The MIPS ProcessorDocument24 pagesDesign of The MIPS Processorwelcome to my worldNo ratings yet

- Multi-Cycle Implementation of MIPS: Revisit The 1-Cycle VersionDocument10 pagesMulti-Cycle Implementation of MIPS: Revisit The 1-Cycle VersionbigfatdashNo ratings yet

- RISC Instruction Set:: I) Data Manipulation InstructionsDocument8 pagesRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNo ratings yet

- Computer Organization: An Introduction To RISC Hardware: 6.1 An Overview of PipeliningDocument12 pagesComputer Organization: An Introduction To RISC Hardware: 6.1 An Overview of PipeliningAmrendra Kumar MishraNo ratings yet

- Mips ImplementationDocument47 pagesMips ImplementationJEEVANANTHAM GNo ratings yet

- Files 3 Homework Solutions A5 Solution 081Document5 pagesFiles 3 Homework Solutions A5 Solution 081Ivanildo GomesNo ratings yet

- Lab Sheet 6 Single Cycle Datapath FinalDocument3 pagesLab Sheet 6 Single Cycle Datapath FinalSANJEEV MALLICKNo ratings yet

- UNIT-3: MIPS InstructionsDocument15 pagesUNIT-3: MIPS InstructionsMukeshram.B AIDS20No ratings yet

- Computer Organization and ArchitectureDocument108 pagesComputer Organization and ArchitectureMuhammad Zeeshan MughalNo ratings yet

- The Processor - IntroductionDocument10 pagesThe Processor - Introductionsas21-d01-s6-cs15No ratings yet

- Computer Organization-Single CycleDocument23 pagesComputer Organization-Single Cyclev2brotherNo ratings yet

- Execution of InstructionDocument60 pagesExecution of InstructionKr RanjithNo ratings yet

- Multicycle Datapath PDFDocument22 pagesMulticycle Datapath PDFShivam KhandelwalNo ratings yet

- Lectures Section 3 ModifiedDocument73 pagesLectures Section 3 ModifiedcoventryUkNo ratings yet

- The Processor: (Datapath and Pipelining)Document144 pagesThe Processor: (Datapath and Pipelining)paranoid486No ratings yet

- UNIT-5: Pipeline and Vector ProcessingDocument63 pagesUNIT-5: Pipeline and Vector ProcessingAkash KankariaNo ratings yet

- Co Unit2 Part1Document11 pagesCo Unit2 Part1Manjushree N.SNo ratings yet

- Chapter 5Document86 pagesChapter 5Muhammad OmerNo ratings yet

- Introduction To MIPS ArchitectureDocument10 pagesIntroduction To MIPS ArchitectureJahanzaib AwanNo ratings yet

- Draw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerDocument7 pagesDraw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerhayerpaNo ratings yet

- Cyan 2800398239029h09fn0ivj0vcjb0Document16 pagesCyan 2800398239029h09fn0ivj0vcjb0Anonymous zWBss8LKNo ratings yet

- Single Cycle Datapath PDFDocument30 pagesSingle Cycle Datapath PDFShivam KhandelwalNo ratings yet

- CMPEN 335 - Computer Organization and Design, Lab 3: 1. PipeliningDocument5 pagesCMPEN 335 - Computer Organization and Design, Lab 3: 1. PipeliningRoberta AndreeaNo ratings yet

- Unit 4 NotesDocument15 pagesUnit 4 Notesshinyshiny966No ratings yet

- Unit 2 - Embedded SystemDocument75 pagesUnit 2 - Embedded Systemsujith100% (4)

- Chapter Four The Processor: Datapath and ControlDocument45 pagesChapter Four The Processor: Datapath and ControlOsama AlqahtaniNo ratings yet

- L13 Multicycle DatapathDocument62 pagesL13 Multicycle DatapathIsaacNo ratings yet

- Basic Performance EquationDocument42 pagesBasic Performance EquationVishal BasugadeNo ratings yet

- Lecture 4 8405 Computer ArchitectureDocument15 pagesLecture 4 8405 Computer ArchitecturebokadashNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- Chapter1 - Basic Structure of ComputersDocument119 pagesChapter1 - Basic Structure of ComputersAnkit SharmaNo ratings yet

- Chapter 1 - Basic Structure of ComputersDocument33 pagesChapter 1 - Basic Structure of Computersanusrini23No ratings yet

- 5.3 Integer and Floating Point Pipeline StagesDocument12 pages5.3 Integer and Floating Point Pipeline Stagesnehareddy.alla17No ratings yet

- Questions With AnswersDocument22 pagesQuestions With AnswersYuva SathiyamoorthyNo ratings yet

- Pipelined Processor DesignDocument28 pagesPipelined Processor DesignLihau TanNo ratings yet

- CA U3 Sjit PDFDocument95 pagesCA U3 Sjit PDFThe Smart Boy KungFuPawnNo ratings yet

- 06 Programming in 8085Document10 pages06 Programming in 8085Dipak55550% (2)

- FinalDocument26 pagesFinalHứa Đăng KhoaNo ratings yet

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDocument10 pagesCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrNo ratings yet

- Lecture6 ARMDocument50 pagesLecture6 ARMRohith ThurlapatiNo ratings yet

- Fetch-Decode-Execute CycleDocument5 pagesFetch-Decode-Execute CycleIzharSeizerNo ratings yet

- Chapter1 - Basic Structure of ComputersDocument123 pagesChapter1 - Basic Structure of ComputersAlbert AlexNo ratings yet

- Reduced Instruction Set Computer (Risc) Complex Instruction Set Computer (Cisc)Document7 pagesReduced Instruction Set Computer (Risc) Complex Instruction Set Computer (Cisc)Sundari MuthuNo ratings yet

- Assignment QuestionsDocument3 pagesAssignment QuestionsSarbendu PaulNo ratings yet

- Instant Download PDF Computer Organization and Design MIPS Edition 5th Edition Patterson Solutions Manual Full ChapterDocument44 pagesInstant Download PDF Computer Organization and Design MIPS Edition 5th Edition Patterson Solutions Manual Full Chapterhickenthess100% (4)

- Control Unit Design NewDocument31 pagesControl Unit Design NewSabareesh MuralidharanNo ratings yet

- Ebook Computer Organization and Design Mips Edition 5Th Edition Patterson Solutions Manual Full Chapter PDFDocument43 pagesEbook Computer Organization and Design Mips Edition 5Th Edition Patterson Solutions Manual Full Chapter PDFjoanneesparzagwjxmyqont100% (12)

- Register FileDocument6 pagesRegister FilejayaprasadkalluriNo ratings yet

- Computer Architecture MIPS Processor DescriptionDocument41 pagesComputer Architecture MIPS Processor DescriptionAsif HussainNo ratings yet

- Unit1 Addressing Modes and GPRDocument70 pagesUnit1 Addressing Modes and GPRsaumya2213215No ratings yet

- Ca Unit 3 PrabuDocument24 pagesCa Unit 3 Prabu6109 Sathish Kumar J100% (1)

- Basic Processing Unit:: Fundamental ConceptsDocument35 pagesBasic Processing Unit:: Fundamental ConceptsJoseph JohnNo ratings yet

- Multi Cycle Data PathDocument21 pagesMulti Cycle Data PathSushma S MurthyNo ratings yet

- Computer Architecture 16 MarksDocument28 pagesComputer Architecture 16 MarksBalachandar2000100% (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Python Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreFrom EverandPython Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreNo ratings yet

- Chapter 7Document24 pagesChapter 7doomachaleyNo ratings yet

- Chapter 0Document13 pagesChapter 0doomachaleyNo ratings yet

- Testing 11Document18 pagesTesting 11doomachaleyNo ratings yet

- Testing 7Document20 pagesTesting 7doomachaleyNo ratings yet

- A UVM-Based Smart Functional Verification Platform: Concepts, Pros, Cons, and OpportunitiesDocument6 pagesA UVM-Based Smart Functional Verification Platform: Concepts, Pros, Cons, and OpportunitiesdoomachaleyNo ratings yet

- Soc Level Verification Using System VerilogDocument3 pagesSoc Level Verification Using System VerilogdoomachaleyNo ratings yet

- Functional Verification 2003: Technology, Tools and MethodologyDocument5 pagesFunctional Verification 2003: Technology, Tools and MethodologydoomachaleyNo ratings yet

- Verification of AMBA Bus Model Using SystemVerilogDocument5 pagesVerification of AMBA Bus Model Using SystemVerilogdoomachaleyNo ratings yet

- Introduction To Operating SystemDocument59 pagesIntroduction To Operating SystemSAPTARSHI GHOSHNo ratings yet

- Hardware Sep 02Document2 pagesHardware Sep 02Saye IkhwanNo ratings yet

- Embedded System BasicsDocument33 pagesEmbedded System BasicssubburampureNo ratings yet

- SPHE8281DDocument35 pagesSPHE8281Ddiego-tNo ratings yet

- OS First PDFDocument263 pagesOS First PDFEtoos LecturesNo ratings yet

- Peripheral Remote IO Adapter BMXPRA0100 User ManualDocument48 pagesPeripheral Remote IO Adapter BMXPRA0100 User ManualHossam eidNo ratings yet

- Docker CLI Reference DocumentationDocument1,151 pagesDocker CLI Reference DocumentationJony NguyễnNo ratings yet

- Nios 2 ProcessorDocument6 pagesNios 2 ProcessorSoundarya SvsNo ratings yet

- AI Assignment - 2Document6 pagesAI Assignment - 2ERMIAS AmanuelNo ratings yet

- PIC18F4520 Instruction SetDocument4 pagesPIC18F4520 Instruction SetCongtan94No ratings yet

- Canary System OverviewDocument7 pagesCanary System OverviewDmitry SolovovNo ratings yet

- System Programming Unit 1-2Document23 pagesSystem Programming Unit 1-2mojbarNo ratings yet

- Week 4 - Computer Organization & ArchitectureDocument59 pagesWeek 4 - Computer Organization & ArchitecturedindNo ratings yet

- SyllabusDocument57 pagesSyllabusYasin ArslanNo ratings yet

- AAST-CC312-Fall 21-Lec 08Document17 pagesAAST-CC312-Fall 21-Lec 08youssef hossamNo ratings yet

- IMPLEMENTATION OF MACRO PROCESSOR System Software Lab ProgramDocument2 pagesIMPLEMENTATION OF MACRO PROCESSOR System Software Lab ProgramBalaji Shanmugam0% (1)

- Osass 1Document2 pagesOsass 1Saad SiddiquiNo ratings yet

- CE403 - Computer Organization and ArchitectureDocument4 pagesCE403 - Computer Organization and Architecturejon rey lumayagNo ratings yet

- Test GX WORK3Document71 pagesTest GX WORK3มานพ ไทยNo ratings yet

- GSE - 201710 - IBM - Z14-Technical - Overview - Final SUPER GOOD ONEDocument156 pagesGSE - 201710 - IBM - Z14-Technical - Overview - Final SUPER GOOD ONERajeshNo ratings yet

- IT 101 Syllabus ObeDocument11 pagesIT 101 Syllabus ObeJONL IDULSANo ratings yet

- Assignment 1 OsDocument3 pagesAssignment 1 OsAbdul Wajid HanjrahNo ratings yet

- Pre-Requisite Contents MS-Programs FSC-NUCES-ISBDocument2 pagesPre-Requisite Contents MS-Programs FSC-NUCES-ISBHafiz Saddique MalikNo ratings yet

- Module 5 Notes - COADocument6 pagesModule 5 Notes - COAAashu PrasadNo ratings yet

- Low Level Assembly Lang., Machine CodesDocument10 pagesLow Level Assembly Lang., Machine CodessyukzNo ratings yet

- Assembly Language Lecture From Engr GatdulaDocument16 pagesAssembly Language Lecture From Engr GatdulaMary Rose SantiagoNo ratings yet

- AMD Ryzen 3 2200G 35 GHZ Quad-Core AM4 ProcessorDocument5 pagesAMD Ryzen 3 2200G 35 GHZ Quad-Core AM4 ProcessorVictorgotNo ratings yet