Professional Documents

Culture Documents

Familia 68 K

Familia 68 K

Uploaded by

Panos BriniasOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Familia 68 K

Familia 68 K

Uploaded by

Panos BriniasCopyright:

Available Formats

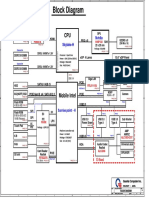

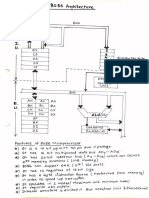

Motorola's 68K Processor Family

68000 Processor Software Model

We have already said that the software model of a processor is used to give programmer

some understanding of the operation, resources and structure of the processor. Motorola's

68K family differs from x86 in many aspects. The most important difference is in the way

memory is accessed. 68000 is also an internal 32-bit machine which means the registers

are 32-bits instead of 16-bits. 68000 has a Program Counter (PC) and it is used to address

the memory space linearly (instead of adding the segment base address with an offset to

obtain the final address).

There are 19 registers in a 68000. 8 of them are general data registers (D0-D7). It has 7

general address registers. It has two stack pointers - one for user and one for the system

(USP and SSP respectively). There is also a processor status word which is 16-bit and a

program counter (32-bit). The 68000 is a general purpose register-based machine and

every data register can be used as an accumulator or as a temp register. 68000 arranges

the data bytes with least-significant byte at the higher address. This approach is called the

big ending approach.

msb

lsb

+---------- +

|B0

|B1

|

+---------- +

|B2

|B3

|

+---------- +

|

|

|

+---------- +

|

|

|

+---------- +

+---------| Word 0

+---------| Word 1

+---------| Word 2

+---------| Word 3

+----------

+

|

+

|

+

|

+

|

+

+---------- +

|LongWord0 H|

+---------- +

|LongWord0 L|

+---------- +

|LongWord1 H|

+---------- +

|LongWord1 L|

+---------- +

Addressing Modes

68000 is a CISC machine and has many addressing modes (14 to be exact). These

addressing modes can be categorized into 6 groups.

Address generation

Assembler Syntax

--------------------------------------------------------------------

(1)Register Direct

Data Register Direct

Address register direct

(2)Address Register Indirect

Register Indirect

Dn

An

(An)

Dn

An

(An)

Postincrement Reg Indirect

Predecrement Reg Indirect

Reg. Indirect with offset

Indexed Reg. Indirect with offset

(3)Absolute Data Register

Absolute Short

Absolute Long

(4)Program Counter Relative

Relative with Offset

Relative with Index and Offset

(5)Immediate Data

Immediate

Quick Immediate

(6)Immplied Addressing

Implied Register

(An); An<-An+N

(An)+

An<-An-N; (An)

-(An)

(An)+ disp16

d(An)

(An)+ (Ri) + disp8 d(An)

(Next Word)

(Next two Word)

(PC)+disp16

(PC)+ (Ri) + disp8

xxxx

xxxxxxxx

d

d(Ri)

DATA = Next Word(s) #xxxx

inherent data

#xx

SR, USP, SSP, PC

68000 Memory

68000 uses linear address to access the memory. Even though it has a 32-bit PC, only the

lower 24 bits are used. With 24-bit address it can directly access up to 16 MB of memory.

68000 Stacks

68000 supports stacks and queues with the address register indirect postinrement and

predecrement addressing modes. That is, with register indirect addressing mode all of the

seven address registers can be used as stack pointers. Subroutine calls, trap and

interrupts use the dedicated stack pointers - USP and SSP. Stacks from high to low

memory are implemented with predecrement mode for PUSH and postincrement mode for

POP. On the other hand, stacks from low to high use postinrement for PUSH and

predecrement for POP. (Note: when address registers is used only 24 bits are valid.)

68020

68020 is a true 32-bit processor and it is object code compatible with 68000. It has many

more registers. Besides the 8-data registers, 7-address registers, 1-PC and 1-SR, there

are 3 SPs instead of 2. There are also 1 16-bit Vector-Based Register (VBR), 2 3-bit

function code registers, 1 32-bit Cache address register (CAAR) and 1 32-bit Cache

COntrol Register (CACR). There is an on-chip instruction cache of size 128 words (16-bit).

The PC is a true 32-bit registers and can address up to 4GB of memory space. There are

new instructions as well as new addressing modes. The new addressing modes are

related to Memory Indirect and Memory INdirect with PC.

68030

68030 is a virtual memory processor based on 68020. That is 68030 has on-chip memory

management unit which performs the paged data memory management. There are four

new instructions for the MMU part of the processor. It also has an on-chip data cache of

size 128 words besides the instruction cache.

68040

68040 is a better implemented 68030. It has larger on-chip data and instruction caches. It

also has an on-chip floating point unit.

Example Assembly Programs for 8086 and 68000

The following two programs implements the summation of multiplying two set of numbers.

This process is described as SUM Xi*Yi for i=1 to 100. In a pseudo language this

calculation is described as:

sum <- 0

for i<- 1 to 100 do

endfor

sum <- sum + X(i) * Y(i)

In 68000 assembly code

; both Xs and Ys are16-bits and the result is 32-bit.

LOOP:

MOVEQ.L #99, D0

; DO is the index i

LEA

P, A0

; Array X starts at P

LEA

Q, A1

; Array Y starts at Q

CLR.L D1

;

MOVE (A0)+, D2 ; get X(i)

MULS (A1)+, D2 ; get Y(i) and dose the multiply X(i)*Y(i)

ADD.L

D2, D1

; sum <- sum + X(i)*Y(i)

DBF

D0, LOOP ; test for zero; decrement and loop

In 8086 assembly code

; this is 8-bit by 8-bit multiply only. TO do 16-bit by 16-bit the code

; will be more complicated.

MOV

MOV

MOV

LEA

LEA

MOV

LOOPA: MOV

IMUL

ADD

INC

INC

LOOP

AX, 2000H ; Setup the data segment register

DS, AX

; load the data segment base

CX, 100

; index i

BX, P

; load X address

SI, Q

; Load Y address

DX, 0000H ; sum <- 0

AL, [BX] ; get X(i)

[SI]

; X(i)*Y(i)

DX, AX

; sum <- sum + X(i)*Y(i)

BX

; next X

SI

; next Y

LOOPA

You might also like

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6From EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6No ratings yet

- Lecture 9 - The Registers and The Memory of The 68000 Intro To 68000 ProgramsDocument23 pagesLecture 9 - The Registers and The Memory of The 68000 Intro To 68000 ProgramsdriNo ratings yet

- Microprocessor LAB IIDocument26 pagesMicroprocessor LAB IISomnath DeyNo ratings yet

- 6800Document11 pages6800Nikola PetrovićNo ratings yet

- The M68000 Educational Computer BoardDocument13 pagesThe M68000 Educational Computer BoardPanos BriniasNo ratings yet

- UNIT-1 Assembly Language ProgrammingDocument30 pagesUNIT-1 Assembly Language ProgrammingIshan Tiwari100% (1)

- 68 XXXDocument20 pages68 XXXRyan John de LaraNo ratings yet

- 8086 Third Term TopicsDocument46 pages8086 Third Term TopicsgandharvsikriNo ratings yet

- Unit 1-1Document49 pagesUnit 1-1vidhya sNo ratings yet

- Part 2Document41 pagesPart 2ah chongNo ratings yet

- Advanced Microprocessor Presentation 4Document21 pagesAdvanced Microprocessor Presentation 4Ubaid SaudagarNo ratings yet

- Study of Architecture of DSP TMS320C6748Document9 pagesStudy of Architecture of DSP TMS320C6748Varssha BNo ratings yet

- Micro ProcessorDocument24 pagesMicro ProcessorPreeti KarkiNo ratings yet

- Introdution To The DsPIC30FDocument17 pagesIntrodution To The DsPIC30Fboyluca100% (1)

- TMS320C4X Digital Signal ProcessingDocument12 pagesTMS320C4X Digital Signal ProcessingRamasubramanian Subramanian100% (1)

- Microprocessor Short Question AnswersDocument50 pagesMicroprocessor Short Question AnswersHamza IqbalNo ratings yet

- 8051 Microcontroller Part 1Document21 pages8051 Microcontroller Part 1Sardar IrfanullahNo ratings yet

- 8086 Notes NITW2020Document76 pages8086 Notes NITW2020ka21ecb0f27No ratings yet

- Internal Architecture 8086Document3 pagesInternal Architecture 8086firoz83% (6)

- Mo MC 3 ChapDocument21 pagesMo MC 3 ChapHarsha MkrNo ratings yet

- A Single Pass Assembler For IBM PCDocument18 pagesA Single Pass Assembler For IBM PCmb_4u67% (3)

- 6800 Internal RegistersDocument3 pages6800 Internal RegistersMANIKANDANNo ratings yet

- Mpi Unit 1Document22 pagesMpi Unit 1sree ramyaNo ratings yet

- Study of Pic16F877A Microcontroller: Equipments RequiredDocument7 pagesStudy of Pic16F877A Microcontroller: Equipments RequiredPriyadharshini TNo ratings yet

- Organization of Intel 8086Document10 pagesOrganization of Intel 8086Ashok ChakriNo ratings yet

- Experiment 1 4 SemesterDocument6 pagesExperiment 1 4 Semesteraman YadavNo ratings yet

- UNIT2 NotesDocument25 pagesUNIT2 Notes4PS19EC071 Lakshmi.MNo ratings yet

- Programmable DSP Lecture1Document19 pagesProgrammable DSP Lecture1Paresh Sawant50% (2)

- Computer Orgn 230428 235533Document10 pagesComputer Orgn 230428 235533Arathi SuryaramananNo ratings yet

- Tutorial On Introduction To 8085 Architecture and ProgrammingDocument23 pagesTutorial On Introduction To 8085 Architecture and ProgrammingDennish KarkiNo ratings yet

- Introduction To Microprocessor and Microcomputer ArchitectureDocument6 pagesIntroduction To Microprocessor and Microcomputer Architecturesri vatsaNo ratings yet

- Microprocessor 8085 ArchitectureDocument8 pagesMicroprocessor 8085 ArchitectureHarjot KaurNo ratings yet

- CSE 2301 Microprocessor and InterfacingDocument10 pagesCSE 2301 Microprocessor and Interfacingminhazul islamNo ratings yet

- User Manual Experiments)Document96 pagesUser Manual Experiments)Rroy JainNo ratings yet

- Unit 1&3Document18 pagesUnit 1&3Sreekanth PagadapalliNo ratings yet

- MPMC Unit 2Document31 pagesMPMC Unit 2nikitaNo ratings yet

- Evolution of MicroprocessorsDocument35 pagesEvolution of MicroprocessorssuhasNo ratings yet

- The Architecture of Pentium MicroprocessorDocument3 pagesThe Architecture of Pentium MicroprocessorLaura Hachi GascaNo ratings yet

- Microprocessor Systems I 1Document28 pagesMicroprocessor Systems I 1Lester Yrwiz V. RamosNo ratings yet

- Microprocessor NotesDocument140 pagesMicroprocessor NotesSaquibh ShaikhNo ratings yet

- Data AnaDocument12 pagesData AnaranjithkumargruNo ratings yet

- 16 Bit Microprocessor 8086Document11 pages16 Bit Microprocessor 8086Yogesh KuteNo ratings yet

- 8086 SoftwareDocument130 pages8086 SoftwareChristopher BakerNo ratings yet

- Arche of 8086Document9 pagesArche of 8086MOHAMMED ASLAM CNo ratings yet

- Microprocessor Laboratory: Text BookDocument35 pagesMicroprocessor Laboratory: Text BookasepNo ratings yet

- cs2304 NolDocument49 pagescs2304 NolAlex DavidNo ratings yet

- Microprocessors and Its Applications Short AnswersDocument15 pagesMicroprocessors and Its Applications Short AnswersVidya MuthukrishnanNo ratings yet

- 8086 PDFDocument261 pages8086 PDFndeshmukh83No ratings yet

- M1 SSCDDocument72 pagesM1 SSCDH3ck AssassinNo ratings yet

- Microprocessor SlideDocument60 pagesMicroprocessor Slideabm wahiduj jamanNo ratings yet

- Night Fall: Meteor Storm: Tribhuvan University Institute ofDocument8 pagesNight Fall: Meteor Storm: Tribhuvan University Institute ofkisan bistaNo ratings yet

- MP Unit-8 VtuDocument10 pagesMP Unit-8 VtuBmvpNo ratings yet

- Experiment No: 1: OBJECTIVE: To Study About The Bus Organization and Programmable Model ofDocument5 pagesExperiment No: 1: OBJECTIVE: To Study About The Bus Organization and Programmable Model ofRutul PrajapatiNo ratings yet

- Architecture of Pentium MicroprocessorDocument3 pagesArchitecture of Pentium MicroprocessorHABISBC50% (2)

- Microprocessor and Assembly Language: LECTURE-3-THE 80X86 MicroprocessorDocument47 pagesMicroprocessor and Assembly Language: LECTURE-3-THE 80X86 MicroprocessorIqraNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3From EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Master System Architecture: Architecture of Consoles: A Practical Analysis, #15From EverandMaster System Architecture: Architecture of Consoles: A Practical Analysis, #15Rating: 2 out of 5 stars2/5 (1)

- Sizemore TalkDocument51 pagesSizemore TalkPanos Brinias100% (1)

- Seminar Quantum InformationDocument3 pagesSeminar Quantum InformationPanos BriniasNo ratings yet

- Newton, Isaac - OpticksDocument376 pagesNewton, Isaac - OpticksGeoff BonningNo ratings yet

- I V Ludwiger The New Worldview of The Physicist Burkhard Heim 160321 PDFDocument91 pagesI V Ludwiger The New Worldview of The Physicist Burkhard Heim 160321 PDFPanos Brinias100% (1)

- FreeRDP Configuration ManualDocument31 pagesFreeRDP Configuration ManualPanos BriniasNo ratings yet

- Actfax Manual enDocument120 pagesActfax Manual enPanos BriniasNo ratings yet

- Asm Lang Prog 68K FamilyDocument256 pagesAsm Lang Prog 68K FamilyPanos BriniasNo ratings yet

- The M68000 Educational Computer BoardDocument13 pagesThe M68000 Educational Computer BoardPanos BriniasNo ratings yet

- Jadwal Ukm 26 Agus 2022Document90 pagesJadwal Ukm 26 Agus 2022Puskesmas LampasiNo ratings yet

- Computer Memory: Prepared By: Avanthika Krishnan, XI DDocument17 pagesComputer Memory: Prepared By: Avanthika Krishnan, XI DAvanthikaNo ratings yet

- Non Inclusive CachesDocument10 pagesNon Inclusive CachesJohnNo ratings yet

- Qualified Vendors List (QVL)Document3 pagesQualified Vendors List (QVL)rohitk225No ratings yet

- FIA Past Papers From 13dec To 25Document211 pagesFIA Past Papers From 13dec To 25sulaiman HaiderNo ratings yet

- 2Gb Ddr3 Sdram: Lead-Free&Halogen-Free (Rohs Compliant)Document34 pages2Gb Ddr3 Sdram: Lead-Free&Halogen-Free (Rohs Compliant)jamesNo ratings yet

- Block-Diagram-Of-8086Document34 pagesBlock-Diagram-Of-8086Piyush KoiralaNo ratings yet

- RTQF Electronic Services L5 PDFDocument514 pagesRTQF Electronic Services L5 PDFDhiraj Khot50% (2)

- Ais160 Final Examination Feb 2023Document17 pagesAis160 Final Examination Feb 2023Adam Haziq100% (3)

- Unit-1 Foc PDF FormatDocument43 pagesUnit-1 Foc PDF FormatPriyanka ChauhanNo ratings yet

- AT29C040A-p (FLASH)Document17 pagesAT29C040A-p (FLASH)abolfazlNo ratings yet

- Digital Electronics Question BankDocument11 pagesDigital Electronics Question BankS.Haribabu SNSNo ratings yet

- IO Terminal Wiring BSI PDFDocument9 pagesIO Terminal Wiring BSI PDFHerman Wessel100% (3)

- Security System Based On Stepper Motor Control Using Micro ControllerDocument6 pagesSecurity System Based On Stepper Motor Control Using Micro ControllerARVINDNo ratings yet

- Adama Science and Technology University: Operating SystemsDocument7 pagesAdama Science and Technology University: Operating SystemsDEABELA GAMING 2No ratings yet

- ST 62Document75 pagesST 62Fam. Esteves MuñoxNo ratings yet

- Buffer OverflowDocument37 pagesBuffer Overflowanon_452184143No ratings yet

- 02 Computer StructureDocument81 pages02 Computer StructureA.Selçuk TunçerNo ratings yet

- DELD - Short Answer Questions and AnswersDocument23 pagesDELD - Short Answer Questions and AnswersPasupuleti Venkata RamanaNo ratings yet

- p8h61-m LX Memory QVLDocument2 pagesp8h61-m LX Memory QVLAdie HastariyadiNo ratings yet

- Systematic Analysis and Simulation of Classical Page Replacement Algorithms A Proposed Novel WSClock-DerivativeDocument8 pagesSystematic Analysis and Simulation of Classical Page Replacement Algorithms A Proposed Novel WSClock-DerivativeTenma InazumaNo ratings yet

- 6T SramDocument10 pages6T SramDeepika kNo ratings yet

- Daam9amb8d0 (Am9a)Document57 pagesDaam9amb8d0 (Am9a)Darcio TolottiNo ratings yet

- MKPROM2 Overview: MKPROM2 Overview Mkprom2 Written by Konrad Eisele May 2013Document12 pagesMKPROM2 Overview: MKPROM2 Overview Mkprom2 Written by Konrad Eisele May 2013Bonnie ThompsonNo ratings yet

- CMP351 - Sheet 1 - UpdatedDocument2 pagesCMP351 - Sheet 1 - UpdatedSheref HeshamNo ratings yet

- MP Unit 1Document17 pagesMP Unit 1Harshit RajputNo ratings yet

- Computer Hardware ThesisDocument7 pagesComputer Hardware Thesisafibykkhxxhdid100% (2)

- Unit 4Document74 pagesUnit 4Apeksha puppalwarNo ratings yet

- Chapter 3Document16 pagesChapter 3fyza emyNo ratings yet

- Sharp LC 22sb280utDocument18 pagesSharp LC 22sb280utGloria ManzanoNo ratings yet