Professional Documents

Culture Documents

CH 02

CH 02

Uploaded by

greeshmaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CH 02

CH 02

Uploaded by

greeshmaCopyright:

Available Formats

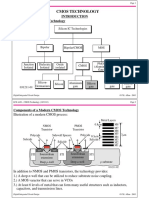

CMOS Technology- Chapter 2

Text Book:

Silicon VLSI Technology

Fundamentals, Practice and

Modeling

g

Authors: J. D. Plummer, M. D. Deal,

and

a

d P. B. G

Griffin

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

CMOS TECHNOLOGY

We will describe a modern CMOS process flow.

Typical CMOS technologies in manufacturing today add

additional steps to implement multiple device VTH, TFT

devices for loads in SRAMs, capacitors for DRAMs etc.

Process described here requires 16 masks

and > 100 process steps.

There are many possible variations on the process flow

described here, some of which are described in Chapter

p

2

in the text. e.g. see the STI section in the text.

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

CMOS Digital Gates

In the simplest CMOS technologies, we need to

realize simply NMOS and PMOS transistors for

circuits like those illustrated below.

+V

+V

IN1

PMOS

IN2

OUTPUT

OUTPUT

INPUT

NMOS

GND

GND

Inverter

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2-input NOR

3

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

2-Level Metal CMOS

D

Sub

Sub

PMOS and NMOS

wafer cross

section after

fabrication

P+

N+

P+

N Well - PMOS Substrate

N+

P Well - NMOS Substrate

PMOS

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

NMOS

4

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Processing Phases

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

Choosing a Substrate

Active Region

g

N and P Well

Gate

Tip or Extension

Source and Drain

C t t and

Contact

d Local

L

l IInterconnect

t

t

Multilevel Metalization

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Choosing a Substrate

1 m

Photoresist

80 nm

40 nm

Si, (100), P Type, 5-50 cm

Substrate selection:

moderately high resistivity

(25-50 ohm-cm)

(100) orientation

P- type.

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

Si3N4

SiO2

Choose the substrate

(type, orientation,

resistivity, wafer size)

Initial processing:

Wafer cleaning

thermal oxidation, H2O

( 40 nm, 15 min. @ 900C)

nitride LPCVD deposition

( 80 nm)

1st Mask Photoresist

spinning and baking

( 0.5 - 1.0 m)

6

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Active Area Definition

Ph

Photolithography

t lith

h

Mask #1 pattern alignment

and UV exposure

y non-pattern

p

PR

Rinse away

Dry etch the Nitride layer

Plasma etch with Fluorine

CF4 or NF4 Plasma

P

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Field Oxide Growth

W

Wett Oxide

O id (thick

(thi k SiO2)

H2O ( 500 nm, 45 min. @

1000C)

LOCOS: Local Oxidation of

Silicon

Birds beak surface feature

Strip Nitride layer

Phosophoric acid or

plasma etch

Instead of Si3N4 use

SiO2/PolySi/Si3N4=

Poly Buffered LOCOS

Results in less birds beak

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

P-well Fabrication

Photolithography

Mask #2 pattern alignment

and UV exposure

Rinse away non-pattern PR

Boron

Ion Implantation

B+ ion bombardment

Penetrate thin SiO2 and field

SiO2

150-200 KeV for 1013 cm-2

Implantation Energy and

total dose adjusted for

depth and concentration

P Implant

PMOS

NMOS

P

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

N-well Fabrication

Photolithography

Mask #3 pattern alignment

and UV exposure

Rinse away non-pattern PR

Phosphorus

N Implant

Ion Implantation

P+ ion bombardment

Penetrate thin SiO2 and field

SiO2

300-400 KeV for 1013 cm-2

Implantation Energy and

total dose adjusted for

depth and concentration

P Implant

PMOS

NMOS

P

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

10

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Thermal Anneal and Diffusion

Thermal Anneal

Repair crystal lattice structure

d

damage

due

d to

t implantation

i l t ti

N Well

N and P Drive-in

Thermal

e a d

diffusion

us o o

of dopa

dopantt to

shallower than desired depth

Drive-in is a cumulative

process!

P Well

2-3 m deep

PMOS

NMOS

Dry Furnace (N2 ambient)

Anneal

30 min @ 800C or

RTA 10 sec @ 1000C

Drive-in

4-6 hours @ 1000 C - 1100 C

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

11

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Threshold Adjustment, P-type NMOS

Photolithography

Mask #4 pattern alignment

and UV exposure

Rinse away non-pattern PR

Boron

Ion Implantation

B+ ion bombardment

50-75KeV for 1-5 x 1012 cm-2

Implantation Energy and

total dose adjusted for

depth and concentration

N Well

P Well

PMOS

NMOS

P

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

12

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Threshold Adjustment, N-type PMOS

Photolithography

Mask #5 pattern alignment

and UV exposure

Rinse away non-pattern PR

Arsenic

N Well

P Well

PMOS

Ion Implantation

As+ ion bombardment

75-100 KeV for 1-5 x 1012 cm-2

Implantation Energy and

total dose adjusted for

depth and concentration

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

Strip Photoresist

13

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Gate Oxide Growth

Remove existing gate region

oxide

HF etch

N Well

Furnace Steps

Thermal Anneal

Dry Furnace (N2 ambient)

30 min @ 800C

800 C

Oxide growth 3-5 nm

O2 ambient

0.5-1 hour @ 800C

P Well

PMOS

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

14

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Polysilicon Gate Deposition

LPCVD Deposition of Si

Silane

P

N Well

Amorphous or polycrystalline

silicon layer results

0.3-0.5 um

P Well

PMOS

IIon Implantation

I l t ti

P+ or As+ (N+) implant dopes

the poly

((typically

yp

y 5 x 1015 cm-2)

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

15

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Gate Patterning

N Well

P Well

PMOS

Ph

Photolithography

t lith

h

Mask #6 pattern alignment

and UV exposure

y non-pattern

p

PR

Rinse away

Plasma Etch

Anisotropic etch

Vertical etch rate high

Lateral etch rate low

Clorine or Bromine based for

SiO2 selectivity

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

16

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Extension (LDD) Formation NMOS

Phosphorus

Photolithography

Mask #7 pattern alignment

and UV exposure

Rinse away non-pattern PR

N - Implant

N Well

P Well

PMOS

Ion Implantation

P+ ion

i

bombardment

b b d

t

50 KeV for 5 x 1013 cm-2

NMOS

P

Strip

p Photoresist

LDD:

Lightly Doped Drain

Reduce short channel effects due to gate voltage

magnitudes and electric fields

Source and Drain must be layered as

NMOS:N+N-P or PMOS: P+P-N

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

17

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Extension (LDD) Formation PMOS

Photolithography

Mask #8 pattern alignment

and UV exposure

Rinse away non-pattern PR

Boron

P - Implant

N - Implant

N Well

P Well

PMOS

Ion Implantation

B+ iion bombardment

b b d

t

50 KeV for 5 x 1013 cm-2

NMOS

P

Strip

p Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

18

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

SiO2 Spacer Deposition

CVD or LPCVD Deposition of

SiO2

Silane and Oxygen

N

P- Implant

N- Implant

N Well

P Well

PMOS

Or

0.5 um

P

Provides

id spacing

i between

b t

gate

t

and source-drain.

Reduce field at gate edge

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

19

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Anisotropic Spacer Etch

P- Implant

N- Implant

N Well

P Well

PMOS

Ph

Photolithography

t lith

h

Mask #6 oversized pattern

alignment and UV exposure

y non-pattern

p

PR

Rinse away

Plasma Etch

Anisotropic etch

Vertical etch rate high

Lateral etch rate low

Flourine based

NMOS

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

20

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

NMOS Source and Drain Implant

Screen Oxide Growth

Thin SiO2 layer ~10 nm to

scatter the implanted ions

Reduce channeling

Arsenic

Photolithography

Mask #9 pattern alignment

and UV exposure

Rinse away non-pattern PR

P

N + Implant

N Well

PMOS

P Well

Ion Implantation

As+

A iion b

bombardment

b d

t

75 KeV for 2-4 x 1015cm-2

NMOS

Strip

p Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

21

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

PMOS Source and Drain Implant

Photolithography

Mask #10 pattern alignment

and UV exposure

Rinse away non-pattern PR

Boron

P + Implant

N + Implant

N Well

P Well

PMOS

Ion Implantation

B+ ion bombardment

1 cm-2

2

5-10 KeV for 1-3 x 1015

NMOS

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

22

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Thermal Annealing

Thermal Anneal

Repair crystal lattice structure

d

damage

due

d to

t implantation

i l t ti

P+

N+

P+

NW

Well

ll

N+

N+ and P+ Drive-in

Thermal

e a d

diffusion

us o of

o dopa

dopantt to

shallower than desired depth

Drive-in is a cumulative

process!

P Well

W ll

PMOS

NMOS

Dry Furnace (N2 ambient)

Anneal

30 min @ 900C or

RTA 60 sec @ 1000 C - 1050 C

Transient Enhanced Diffusion (TED)

Higher than normal diffusivity due to

crystal damage

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

23

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Contact Openings

P+

P+

N+

N Well

P Well

PMOS

NMOS

N+

HF etch to remove thin SiO2

Remove screen oxide from

drain, source and ploy gate

regions

Dip for a few seconds

LDD and Sidewall structure

NMOS: Lateral N+ N- P N- N+

PMOS: Lateral P+ P- N P- P+

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

24

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Contacts and Interconnects

Titanium sputtering local contacts

Conformal Coat with SiO2

Planarization

Tungsten Plug vias

Aluminum Metal Deposition

Repeat

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

Coatt

C

Planarize

Plug

Metal deposition

25

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Titanium Deposition

P+

P+

N+

N Well

N+

P Well

PMOS

NMOS

Ti is deposited by

sputtering

(typically 100 nm).

Ti target hit with

Ar+ ions in a

vacuum chamber

h b

P+

P+

N+

NW

Well

ll

N+

P Well

W ll

PMOS

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

26

Th

The Ti is

i reacted

d in

i an

N2 ambient,

Forms TiSi2 and TiN

(typically 1 min @ 600 700 C).

TiSi2 has excellent

contact characteristics

TiN does

d

not,

t but

b t can

be used for local wiring

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Local TiN Interconnect

P+

P+

N+

N Well

P Well

PMOS

NMOS

Photolithography

Mask #11 pattern alignment

and UV exposure

Rinse away non-pattern PR

N+

TiN etch

NH4OH:H202:H20 (1:1:5)

Strip Photoresist

Thermal Treat in Ar

1 min @ 800 C

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

27

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Conformal Coat and Planarize

P+

P+

N+

N Well

N+

P Well

PMOS

NMOS

Conformal layer of

SiO2 is deposited by

CVD or LPCVD

(typically 1 m)

PSG or BPSG

Surface passivation

Glass reflow

reflo for

partial planarization

P+

P+

N+

N Well

N+

P Well

PMOS

Chemical Mechanical

Polishing (CMP)

Planarize the wafer

surface

Polish with high pH

silica slurry

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

28

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Vias to 1st Metal

P+

P+

N+

N Well

PMOS

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

Photolithography

Mask #12 pattern alignment

and UV exposure

Rinse away non-pattern PR

N+

SiO2 plasma etch

Anisotropic

A i t

i etch

t h

P Well

Strip Photoresist

NMOS

29

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Via Deposition Tungsten Plugs

TiN

P+

P+

N+

N Well

TiN or Ti/TiN barrier layer

Sputtering or CVD

(few tens of nm)

N+

P Well

CVD Tungsten (W)

PMOS

P+

NMOS

P+

N+

N Well

Chemical Mechanical

Polishing (CMP)

Planarize the wafer

surface

Polish with high pH

silica slurry

N+

P Well

PMOS

NMOS

P

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

30

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Damascene Process

Etch Contact Holes or Line Trenches

Fill etched regions

g

Planarize

CMP process

Also

Al removes material

t i l th

thatt overflowed

fl

dh

holes

l or ttrenches

h

Also used in reference to copper line metal layer

deposition

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

31

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Metal #1 Deposition

Photolithography

g p y

Mask #13 pattern alignment

and UV exposure

Rinse away non-pattern PR

P+

P+

N+

N Well

Sputtered Aluminum

Al with small amounts of

Si and Cu

Cu reduces electromigration

N+

P Well

PMOS

NMOS

Anisotropic plasma etch

Strip Photoresist

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

32

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Multiple Metal Layers

P+

P+

N+

N Well

N+

Final passivation layer of

Si3N4 is deposited by

PECVD and patterned with

Mask #16.

P Well

PMOS

Deposits Oxide Layer

CMP

Ph t lith

Photolithography

h M

Mask

k #14

Etch Vias

Deposit via material

CMP

C

Photolithography Mask #15

Deposit Next Metal Layer

NMOS

P

Final anneal and alloy in

forming gas (10% H2 in N2)

30 min @ 400

400-450

450 C

C

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

33

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Intel processor chip

52MB SRAM chips on a 12 wafer

Photos of state-of-the-art CMOS chips (from Intel website).

90 nm technology.

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

2000 by Prentice Hall

Upper Saddle River NJ

CMOS Technology- Chapter 2

Summary of Key ideas

This chapter serves as an introduction to CMOS technology.

It provides a perspective on how individual technologies like oxidation and

ion implantation are actually used.

There are many variations on CMOS process flows used in industry.

The process described here is intended to be representative, although it is

simplified compared to many current process flows.

Some process options are described in Chapter 2 in the text.

Perhaps the most important point is that while individual process steps like

oxidation and ion implantation are usually studied as isolated technologies,

technologies

their actual use is complicated by the fact that IC manufacturing consists of

many sequential steps, each of which must integrate together to make the

whole process flow work in manufacturing.

SILICON VLSI TECHNOLOGY

Fundamentals, Practice and Modeling

By Plummer, Deal & Griffin

35

2000 by Prentice Hall

Upper Saddle River NJ

You might also like

- Yanmar Crawler Excavators Vio40 1 Service Manuals en PDFDocument22 pagesYanmar Crawler Excavators Vio40 1 Service Manuals en PDFmichaelgarza030201fwm100% (65)

- Book 1 - Section C - Steel Framed Wall SystemsDocument57 pagesBook 1 - Section C - Steel Framed Wall SystemsManasi SatbhaiNo ratings yet

- Basic Pecvd Plasma Processes (Sih Based) : Pecvd Sinx: Sih + NH (+H) or Sih + N (+H)Document36 pagesBasic Pecvd Plasma Processes (Sih Based) : Pecvd Sinx: Sih + NH (+H) or Sih + N (+H)Anonymous lidok7lDiNo ratings yet

- Cmos Process FlowDocument29 pagesCmos Process FlowPushparaj Karu100% (1)

- Comphw 1Document5 pagesComphw 1jonix94No ratings yet

- CMOS Process FlowDocument39 pagesCMOS Process FlowYashaswa JainNo ratings yet

- Microsoft Powerpoint - Vlsi Design AspectDocument89 pagesMicrosoft Powerpoint - Vlsi Design AspectAKASHDIP DUTTANo ratings yet

- EBB323 Summary 11 Oct 2010Document4 pagesEBB323 Summary 11 Oct 2010soonvyNo ratings yet

- CMOS/Processing TechnologyDocument15 pagesCMOS/Processing TechnologyYidnekachwe MekuriaNo ratings yet

- Dasar Design CMOS TransistorDocument49 pagesDasar Design CMOS Transistormaqbulloh darojatiNo ratings yet

- CMOS Process FlowDocument35 pagesCMOS Process Flowag21937570No ratings yet

- Ch11 2Document23 pagesCh11 2Abd TashNo ratings yet

- Fabrication Technology: - Planarising Cleaning - Deposition - Patterning Implantation HeatDocument40 pagesFabrication Technology: - Planarising Cleaning - Deposition - Patterning Implantation HeatRavi HosamaniNo ratings yet

- ALD in Semiconductor ProcessingDocument26 pagesALD in Semiconductor ProcessingWeiHsinNo ratings yet

- Vlsi Backend TechnologyDocument39 pagesVlsi Backend TechnologysakthikothandapaniNo ratings yet

- MINOR2 DfinalocxDocument32 pagesMINOR2 DfinalocxVenkatesh KumarNo ratings yet

- Fabrikasi ICDocument47 pagesFabrikasi ICNanamaliamNo ratings yet

- L11a 4345 Sp02Document24 pagesL11a 4345 Sp02Sanjay GargNo ratings yet

- SCTT-3 (Iv) - 4 PecvdDocument43 pagesSCTT-3 (Iv) - 4 PecvdsatyajitNo ratings yet

- Lecture 030 - Deep Submicron (DSM) Cmos TechnologyDocument14 pagesLecture 030 - Deep Submicron (DSM) Cmos TechnologywatelzbuddyNo ratings yet

- 164 981214Document33 pages164 981214Kong1684No ratings yet

- Pmos Nmos CmosDocument58 pagesPmos Nmos Cmosrahulmishra84No ratings yet

- CMOS Process: Material Mainly Taken From UMBC, Kang and CampbellDocument38 pagesCMOS Process: Material Mainly Taken From UMBC, Kang and CampbellSmitha KollerahithluNo ratings yet

- Lecture CMOS NWELL and TwinTub ProcessDocument33 pagesLecture CMOS NWELL and TwinTub Processilias ahmedNo ratings yet

- CMOS Tech-2UP (12 - 11 - 03)Document29 pagesCMOS Tech-2UP (12 - 11 - 03)Mountsinai CscNo ratings yet

- Isolation: CMOS Processing TechnologyDocument15 pagesIsolation: CMOS Processing TechnologyAshwani RanaNo ratings yet

- Basic Process DiffusionDocument104 pagesBasic Process DiffusionBalamurugan Velayutham100% (1)

- C-1 CMOS Processing FlowDocument76 pagesC-1 CMOS Processing FlowKu Ble YanNo ratings yet

- MOSCAP FabricationDocument34 pagesMOSCAP FabricationAnjireddy ThatiparthyNo ratings yet

- Tema 7: Tecnología Y Fabricación de CisDocument21 pagesTema 7: Tecnología Y Fabricación de CisSai SadiqNo ratings yet

- Nexray: A. Dommann, H. Von Känel, P. GröningDocument35 pagesNexray: A. Dommann, H. Von Känel, P. GröningnanoteraCHNo ratings yet

- Cmos Metal GateDocument56 pagesCmos Metal GateSubin AlexNo ratings yet

- Semiconductor Manufacturing Technology: Semiconductor Manufacturing ProcessesDocument34 pagesSemiconductor Manufacturing Technology: Semiconductor Manufacturing ProcessesRajesh PuniaNo ratings yet

- Application Note - 65nm - Microwind-HALDocument21 pagesApplication Note - 65nm - Microwind-HALyeiaNo ratings yet

- Soi ProcessDocument14 pagesSoi ProcessMichael CampbellNo ratings yet

- Lec6w Processintegration Ee143 CTNDocument15 pagesLec6w Processintegration Ee143 CTNstansilawNo ratings yet

- RAPDDocument4 pagesRAPD123vidyaNo ratings yet

- Analog LayoutDocument62 pagesAnalog Layoutcatchmereddy100% (3)

- Topics: Basic Fabrication Steps. Transistor Structures. Basic Transistor Behavior. Latch UpDocument24 pagesTopics: Basic Fabrication Steps. Transistor Structures. Basic Transistor Behavior. Latch Uppra_zara2637No ratings yet

- IC Manufacturing SMT Process FlowDocument41 pagesIC Manufacturing SMT Process FlowAnirban KarNo ratings yet

- Unit 1: IC Fabrication: CMOS ProcessDocument42 pagesUnit 1: IC Fabrication: CMOS Processbadrinarayan2210298No ratings yet

- 06-Klitzke Sidwell Jensen Presentation Part 123Document89 pages06-Klitzke Sidwell Jensen Presentation Part 123Nguyễn Thanh TùngNo ratings yet

- Unit Process Steps VlsiDocument83 pagesUnit Process Steps Vlsis.r.No ratings yet

- CMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AnDocument18 pagesCMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AntmdmurthyNo ratings yet

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamNo ratings yet

- 2 - M N-Well CMOS Process Flow: TCAD: Process and Device SimulationDocument29 pages2 - M N-Well CMOS Process Flow: TCAD: Process and Device Simulationreach_arunpai4249No ratings yet

- Vlsi Design: Prepared Prepared Prepared Prepared by by by byDocument30 pagesVlsi Design: Prepared Prepared Prepared Prepared by by by byVenkata SatishNo ratings yet

- Lecture1 3 CMOS nWELL and TwinTub ProcessDocument33 pagesLecture1 3 CMOS nWELL and TwinTub ProcessSrikanth Soma100% (8)

- Digital Integrated Circuits: A Design PerspectiveDocument21 pagesDigital Integrated Circuits: A Design PerspectiveAhmad ShdifatNo ratings yet

- Chapter 9 Thin Film Deposition - IVDocument49 pagesChapter 9 Thin Film Deposition - IVRashmi RavindranathNo ratings yet

- MP4004 Advanced Manufacturing and Nanotechnology: ContentDocument26 pagesMP4004 Advanced Manufacturing and Nanotechnology: ContentVincent KohNo ratings yet

- Fabrication of Fet: Dr. R. Ramaprabha (Sec A)Document10 pagesFabrication of Fet: Dr. R. Ramaprabha (Sec A)Kapildev KumarNo ratings yet

- Introduction To MOS TechnologiesDocument15 pagesIntroduction To MOS TechnologieslokeshwarrvrjcNo ratings yet

- CMOS Fabrication and LayoutDocument14 pagesCMOS Fabrication and LayoutRose Beth AndayaNo ratings yet

- FinFET History Fundamentals FutureDocument55 pagesFinFET History Fundamentals FutureMurali Shanmuga Sundaram100% (2)

- C-5 Insulation Resistance CalculationsDocument43 pagesC-5 Insulation Resistance Calculationsrober2222No ratings yet

- Introduction To Cmos Circuits: Unit IiDocument48 pagesIntroduction To Cmos Circuits: Unit Iiarun14089No ratings yet

- Seminar Report-Bicmos TechnologyDocument19 pagesSeminar Report-Bicmos Technologymbiswasray_iter0% (1)

- Rapid Thermal Processing: Science and TechnologyFrom EverandRapid Thermal Processing: Science and TechnologyRichard B. FairNo ratings yet

- Millimeter-Wave Receiver Concepts for 77 GHz Automotive Radar in Silicon-Germanium TechnologyFrom EverandMillimeter-Wave Receiver Concepts for 77 GHz Automotive Radar in Silicon-Germanium TechnologyNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- Noise Control Manual (Masoneilan) PDFDocument24 pagesNoise Control Manual (Masoneilan) PDFtxagusNo ratings yet

- ISO 45001 Guide Final - Mar2018Document8 pagesISO 45001 Guide Final - Mar2018Ishumael BurayayiNo ratings yet

- PDFDocument2 pagesPDFrubenpatNo ratings yet

- Microwave Engineering: David M. PozarDocument10 pagesMicrowave Engineering: David M. PozarNguyen HungNo ratings yet

- AL2O3 Atomic Layer Deposited 2019Document10 pagesAL2O3 Atomic Layer Deposited 2019ahmed abusnoubarNo ratings yet

- Access Switching - CursoDocument723 pagesAccess Switching - CursoAlberto Isturiz100% (1)

- ANIKETDocument7 pagesANIKETsky998493No ratings yet

- Estimation of Clarks Instantaneous Unit Hydro Graph in GISDocument9 pagesEstimation of Clarks Instantaneous Unit Hydro Graph in GISSudharsananPRS100% (1)

- Scribe Marking Head mv5 Vu4 by Markator Manfred Borries GMBHDocument16 pagesScribe Marking Head mv5 Vu4 by Markator Manfred Borries GMBHTomislav LoinaNo ratings yet

- Research Proposal - ICTDocument8 pagesResearch Proposal - ICTSuresh Kumar RaiNo ratings yet

- Multistage SamplingDocument20 pagesMultistage Samplingpreetie87100% (1)

- CAPELEC CAP2600 Electronic Headlamp TesterDocument2 pagesCAPELEC CAP2600 Electronic Headlamp TesterCesar GehovannyNo ratings yet

- Unidad Odontologica BelmontDocument72 pagesUnidad Odontologica BelmontLAURA MUÑOZNo ratings yet

- Reloj en Tiempo Real Con Pic 16f628aDocument4 pagesReloj en Tiempo Real Con Pic 16f628adidproelNo ratings yet

- Seru7828-08 3406C Operation ManualDocument180 pagesSeru7828-08 3406C Operation ManualshNo ratings yet

- Six Sigma ToolsDocument15 pagesSix Sigma ToolsmelaniepillayNo ratings yet

- T5140 IlomDocument15 pagesT5140 IlomAkella Ramana KumarNo ratings yet

- Gann Time Price SquareDocument5 pagesGann Time Price Squareanudora0% (1)

- Best Practices For Usable IntranetsDocument21 pagesBest Practices For Usable IntranetsDebasish ParhiNo ratings yet

- ERP Systems: Audit and Control Risks: Jennifer Hahn Deloitte & ToucheDocument37 pagesERP Systems: Audit and Control Risks: Jennifer Hahn Deloitte & Toucheapi-3805445No ratings yet

- Curriculum For Community Radio Training in NigeriaDocument30 pagesCurriculum For Community Radio Training in NigeriaHenry Anibe Agbonika I100% (1)

- Business ResearchDocument49 pagesBusiness ResearchBalaji50% (2)

- Session 4 - LeanStartupDocument32 pagesSession 4 - LeanStartupvinay mouryaNo ratings yet

- Eurocontrol Airial PDFDocument427 pagesEurocontrol Airial PDFyudhiqNo ratings yet

- Finding Top Center Position For No. 1 Piston PDFDocument2 pagesFinding Top Center Position For No. 1 Piston PDFsonjisahuriNo ratings yet

- Class 10th ProjectDocument2 pagesClass 10th ProjectRitik ThakurNo ratings yet

- Product Sheet - KF & KSF (UK)Document2 pagesProduct Sheet - KF & KSF (UK)Danny SundmanNo ratings yet