Professional Documents

Culture Documents

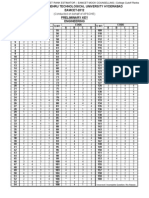

Fts 2007

Fts 2007

Uploaded by

andhracollegesCopyright:

Available Formats

You might also like

- ZXCTN 6300&6200&6100&6110 Single System Commissioning Guide - R1.3Document49 pagesZXCTN 6300&6200&6100&6110 Single System Commissioning Guide - R1.3DavoodNo ratings yet

- MM 2006Document8 pagesMM 2006andhracollegesNo ratings yet

- Eamcet 2010 Medical PaperDocument63 pagesEamcet 2010 Medical PaperandhracollegesNo ratings yet

- 06rr410506 Fault Tolerant SystemsDocument7 pages06rr410506 Fault Tolerant SystemsandhracollegesNo ratings yet

- Set No. 1: Min Max Wmin Max Vmax Vmax Vmin VmaxDocument5 pagesSet No. 1: Min Max Wmin Max Vmax Vmax Vmin VmaxandhracollegesNo ratings yet

- JNTU Old Question Papers 2007Document8 pagesJNTU Old Question Papers 2007Srinivasa Rao GNo ratings yet

- Set No. 1Document5 pagesSet No. 1andhracollegesNo ratings yet

- r07220205 Control SystemsDocument9 pagesr07220205 Control SystemsandhracollegesNo ratings yet

- Co 2007Document4 pagesCo 2007andhracollegesNo ratings yet

- NSC 2007Document5 pagesNSC 2007andhracollegesNo ratings yet

- DicaDocument8 pagesDicaandhracollegesNo ratings yet

- 08 r05310502 Object Oriented Analysis and DesignDocument7 pages08 r05310502 Object Oriented Analysis and DesignandhracollegesNo ratings yet

- Rr410506 Fault Tolerant SystemsDocument8 pagesRr410506 Fault Tolerant Systemsdayas1979No ratings yet

- 08rr410404 Optical CommunicationDocument8 pages08rr410404 Optical CommunicationandhracollegesNo ratings yet

- Nov07 Pulse Digital CircuitsDocument9 pagesNov07 Pulse Digital CircuitsandhracollegesNo ratings yet

- r05220205 Control SystemsDocument9 pagesr05220205 Control SystemsandhracollegesNo ratings yet

- Sr05220205 Control SystemsDocument8 pagesSr05220205 Control SystemsandhracollegesNo ratings yet

- Java 2006Document5 pagesJava 2006andhracollegesNo ratings yet

- Set No. 1Document6 pagesSet No. 1andhracollegesNo ratings yet

- 07 Rr420202 HVDC TransmissionDocument4 pages07 Rr420202 HVDC TransmissionandhracollegesNo ratings yet

- Aca 2005Document5 pagesAca 2005andhracollegesNo ratings yet

- Uml 2006Document8 pagesUml 2006andhracollegesNo ratings yet

- 06N - RR410302 Cad CamDocument4 pages06N - RR410302 Cad CamandhracollegesNo ratings yet

- r05410408 Digital Image ProcessingDocument5 pagesr05410408 Digital Image ProcessingandhracollegesNo ratings yet

- 07N - RR410302 Cad CamDocument6 pages07N - RR410302 Cad CamandhracollegesNo ratings yet

- Ads 2007Document4 pagesAds 2007andhracollegesNo ratings yet

- Rr410203 Computer Methods in Power SystemsDocument9 pagesRr410203 Computer Methods in Power SystemsandhracollegesNo ratings yet

- Rr720507 Neural NetworksDocument5 pagesRr720507 Neural NetworksandhracollegesNo ratings yet

- Rr720303 MicroprocessorsDocument8 pagesRr720303 MicroprocessorsandhracollegesNo ratings yet

- MechatronicsDocument4 pagesMechatronicsandhracollegesNo ratings yet

- C&dsDocument4 pagesC&dsandhracollegesNo ratings yet

- 08 r05310404 Digital CommunicationDocument8 pages08 r05310404 Digital CommunicationandhracollegesNo ratings yet

- 08RR410302 Cad CamDocument5 pages08RR410302 Cad CamandhracollegesNo ratings yet

- Uml M 2006Document8 pagesUml M 2006andhracollegesNo ratings yet

- Examination Paper: May/June 2020 COMP2211-WE01Document6 pagesExamination Paper: May/June 2020 COMP2211-WE01africa threeNo ratings yet

- Neural Networks and Fuzzy Logic PDFDocument9 pagesNeural Networks and Fuzzy Logic PDFbadamsmithNo ratings yet

- TC 2006Document10 pagesTC 2006andhracollegesNo ratings yet

- Dmadwh 2007Document5 pagesDmadwh 2007andhracollegesNo ratings yet

- Summer 2021 AMIIW Question PapersDocument32 pagesSummer 2021 AMIIW Question PapersRiyaz AhmedNo ratings yet

- Dmadwh 2006Document7 pagesDmadwh 2006andhracollegesNo ratings yet

- r05410409 Satellite CommunicationsDocument5 pagesr05410409 Satellite CommunicationsandhracollegesNo ratings yet

- NcseDocument5 pagesNcseandhracollegesNo ratings yet

- Set No. 1Document7 pagesSet No. 1andhracollegesNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- LP 2005Document8 pagesLP 2005andhracollegesNo ratings yet

- Ds 2006Document4 pagesDs 2006andhracollegesNo ratings yet

- Srr320404 Microwave EngineeringDocument7 pagesSrr320404 Microwave EngineeringandhracollegesNo ratings yet

- Rr420402 Radar EngineeringDocument4 pagesRr420402 Radar EngineeringandhracollegesNo ratings yet

- Examination Paper: May/June 201 9 COMP2211-WE01Document6 pagesExamination Paper: May/June 201 9 COMP2211-WE01africa threeNo ratings yet

- Sjr05010201 Applied PhysicsDocument8 pagesSjr05010201 Applied PhysicsandhracollegesNo ratings yet

- Ece361 - Ee 2010 S1Document5 pagesEce361 - Ee 2010 S1Mu'izz KaharNo ratings yet

- r07320204 InstrumentationDocument6 pagesr07320204 InstrumentationandhracollegesNo ratings yet

- March2006 Network Security and CryptographyDocument5 pagesMarch2006 Network Security and CryptographyKeerthi ReddyNo ratings yet

- r05310201 Computer IonDocument5 pagesr05310201 Computer IonskssushNo ratings yet

- R05320506-SOFTWARE-TESTING-METHODOLOGIES May 2008Document5 pagesR05320506-SOFTWARE-TESTING-METHODOLOGIES May 2008api-19718334No ratings yet

- Btech Cse 4 Sem Advance Computer Architecture 2012Document7 pagesBtech Cse 4 Sem Advance Computer Architecture 2012souravnaskar12578954No ratings yet

- Rr720505 RoboticsDocument7 pagesRr720505 RoboticsandhracollegesNo ratings yet

- Mobile Edge Artificial Intelligence: Opportunities and ChallengesFrom EverandMobile Edge Artificial Intelligence: Opportunities and ChallengesNo ratings yet

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocument1 pageEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggNo ratings yet

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocument3 pagesEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2014 Engineering Key SolutionsDocument42 pagesEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocument42 pagesEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2007 Engineering PaperDocument13 pagesEamcet 2007 Engineering Paperandhracolleges100% (1)

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocument62 pagesAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Polycet 2014 Question PaperDocument24 pagesPolycet 2014 Question PaperandhracollegesNo ratings yet

- Eamcet 2001 Engineering PaperDocument14 pagesEamcet 2001 Engineering Paperandhracolleges100% (1)

- Eamcet 2006 Engineering PaperDocument14 pagesEamcet 2006 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2004 Engineering PaperDocument12 pagesEamcet 2004 Engineering PaperandhracollegesNo ratings yet

- EAMCET NotificationDocument3 pagesEAMCET NotificationKeerthiPratheek ReddyNo ratings yet

- EAMCET Engineering Entrance Solved Paper 2000Document13 pagesEAMCET Engineering Entrance Solved Paper 2000Giri NathNo ratings yet

- Icet-2014-Important Instructions BookletDocument3 pagesIcet-2014-Important Instructions BookletandhracollegesNo ratings yet

- Eamcet 2003 Engineering PaperDocument12 pagesEamcet 2003 Engineering Paperandhracolleges100% (1)

- Eamcet 2002 Engineering PaperDocument14 pagesEamcet 2002 Engineering Paperandhracolleges0% (1)

- Eamcet 2009 Engineering Physics PaperDocument19 pagesEamcet 2009 Engineering Physics PaperandhracollegesNo ratings yet

- TS ICET Syllabus and Exam PatternDocument5 pagesTS ICET Syllabus and Exam PatterngayathriNo ratings yet

- FeeDocument34 pagesFeeThanniru VenkateshNo ratings yet

- Eamcet Pharmacy College Fee DetailsDocument14 pagesEamcet Pharmacy College Fee DetailsandhracollegesNo ratings yet

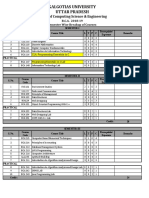

- Galgotias University Uttar Pradesh: School of Computing Science & EngineeringDocument3 pagesGalgotias University Uttar Pradesh: School of Computing Science & EngineeringTushant ChakravartyNo ratings yet

- MINI MCR-SL-PT100-UI (-SP) (-NC) : Configurable Temperature Transducer For PT100Document12 pagesMINI MCR-SL-PT100-UI (-SP) (-NC) : Configurable Temperature Transducer For PT100Sandro CentellasNo ratings yet

- Automatic Seed Sowing Robot: International Research Journal of Engineering and Technology (IRJET)Document3 pagesAutomatic Seed Sowing Robot: International Research Journal of Engineering and Technology (IRJET)Teshome GetachewNo ratings yet

- Protocol Specification For Interfacing To Data Communication NetworksDocument205 pagesProtocol Specification For Interfacing To Data Communication NetworksMovieTube DBNo ratings yet

- UniManager Brochure - 2022 v1Document10 pagesUniManager Brochure - 2022 v1Arvans AGNo ratings yet

- Ijert Ijert: FPGA Implementation of Orthogonal Code Convolution For Efficient Digital CommunicationDocument7 pagesIjert Ijert: FPGA Implementation of Orthogonal Code Convolution For Efficient Digital Communicationtariq76No ratings yet

- Introduction To Database Management SystemDocument20 pagesIntroduction To Database Management SystemRould Christian Ganzon AlertaNo ratings yet

- AsteRx SB3 ProBase Firmware v4.14.4 Reference GuideDocument450 pagesAsteRx SB3 ProBase Firmware v4.14.4 Reference GuideSergiy PogoryelovNo ratings yet

- Digital Control SystemDocument6 pagesDigital Control SystemAlpha100% (1)

- Workshop On Digital Design With FPGA Organized by EiTRADocument4 pagesWorkshop On Digital Design With FPGA Organized by EiTRAmurali036No ratings yet

- Mib & SibDocument14 pagesMib & SibebraoNo ratings yet

- Ranjit Meghwal: ObjectiveDocument3 pagesRanjit Meghwal: ObjectiveRanjit meghwalNo ratings yet

- MP2480 3A LED Driver, Wide 5V To 36V OperatingDocument1 pageMP2480 3A LED Driver, Wide 5V To 36V Operatingjunaid ahmadNo ratings yet

- DOE DPV Website Tutorial: Matthew Rylander Jeff SmithDocument12 pagesDOE DPV Website Tutorial: Matthew Rylander Jeff SmithAli MuhtarNo ratings yet

- Communication Engineering 9781259006869 1259006867 CompressDocument719 pagesCommunication Engineering 9781259006869 1259006867 CompressyogasriNo ratings yet

- OS DPPs A4Document47 pagesOS DPPs A4DeepNo ratings yet

- Student Information System ProjectDocument4 pagesStudent Information System ProjectWuWong TurtleNo ratings yet

- Windows Forensic Artifacts Cheat SheetDocument2 pagesWindows Forensic Artifacts Cheat Sheetprasenjit_boseNo ratings yet

- Circuits SolnDocument5 pagesCircuits Solndwaytikitan28No ratings yet

- Ed A User GuideDocument91 pagesEd A User GuideMarco TomasNo ratings yet

- Kendall Su PDFDocument13 pagesKendall Su PDFFurqan khwaja0% (1)

- SAP UI5 Interview Q&ADocument9 pagesSAP UI5 Interview Q&AARPANANo ratings yet

- OX6 Installation and AdministrationDocument223 pagesOX6 Installation and AdministrationClaudia Cerda AviñaNo ratings yet

- Chapter 1 CoaDocument3 pagesChapter 1 CoaSamuel AdamuNo ratings yet

- Ddos Script (Python)Document2 pagesDdos Script (Python)webwise69No ratings yet

- Recode in VBA Learn To Automate Excel by P - G BLANCODocument60 pagesRecode in VBA Learn To Automate Excel by P - G BLANCOLiviu CristeaNo ratings yet

- Dreamcast Hardware Specification OutlineDocument40 pagesDreamcast Hardware Specification OutlineJoséManuelBenettiNo ratings yet

- Job Board Project PlanDocument47 pagesJob Board Project Plannuhamin zNo ratings yet

- Medium HighVoltageCapacitors 12022ghjkb JJGKGDocument11 pagesMedium HighVoltageCapacitors 12022ghjkb JJGKGKhairil AminNo ratings yet

Fts 2007

Fts 2007

Uploaded by

andhracollegesOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fts 2007

Fts 2007

Uploaded by

andhracollegesCopyright:

Available Formats

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 1

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) How does a feedback briding fault leads the circuit into oscillation. What are

the conditions? [4+4]

(b) What are temporary faults? Differentiate between Transient faults and inter-

mittent faults. Which one is preferrable? [3+2+2+1]

2. (a) A circuit realizes the function.

Z=X1 X4 +X2 X3 +X1 X4

Using Boolean Difference method find the test vectors for SA0, SA1 faults on

all input lines of the circuit.

(b) What are the different properties of Boolean differences? Explain [5+5+6]

3. (a) Construct a seven-bit error correcting code to represent the decimal digit by

augmenting the Excess-3 code and by using add-1 parity check.

(b) Design a redundant circuit for f = a ⊕ b [9+7]

4. (a) What is the mechanism adopted in COPRA a fault Tolerant system. Explain

in detail.

(b) What is meant by Time redundancy? Explain. [4+4+4+4]

www.andhracolleges.com

5. (a) What is the need for self checking circuits

(b) Design a totally self checking checker by using reddy’s partition method for

2out of 5 code. [6+10]

6. Explain in detail about fail-safe sequential circuits design with an example. [16]

7. Write a short notes an [4x4=16]

(a) Controllability

(b) Observability

(c) Positive unate function

(d) Syndrom relations of all types of terminating gates.

8. (a) Discuss the sequential circuit design using nonscan techniques.

(b) i. What is meant by Enhanced controllability?

ii. How is a sequential circuit modified for the above sequential circuit and

enhanced controllability? [6+4+6]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 2

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Distinguish between failures, and faults Explain [2+2]

(b) Explain the different modeling schemes of faults that generally come across in

digital circuits. [3x2=6]

(c) Explain the following terms with respect to digital circuits with suitable ex-

amples.

i. Fault diagnosis.

ii. Fault detection test set.

iii. Test vector generation. [3x2=6]

2. (a) Distinguish between fault detection and fault location [2+2]

(b) Illustrate the principles involved in fault table method of test generation using

the figure1 given below.Verify the above test vector, generated, with the help

of D-algorithm for C SAO fault. [12]

www.andhracolleges.com

so that it becomes hazard free?

Figure 1:

3. (a) Analyze the circuit shown in fig2 below for static hazards. Redesign the circuit

(b) Explain the concept of sift out modular redundancy scheme.

[4+4]

[8]

4. With an example explain :

(a) software redundancy.

(b) time redundancy. [8+8]

5. (a) What is the need for self checking circuits

(b) Design a totally self checking checker by using reddy’s partition method for

2out of 5 code. [6+10]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 2

www.andhracolleges.com Figure 2:

6. Explain in detail about fail-safe sequential circuits design with an example.

7. Explain the technique for designing minimally testable network which produces a

circuit which can be tested by three tests only.Modify the function f = A BC +A

B C into a circuit which has only three tests. [10+6]

8. (a) Draw the logic diagram of Hazard-free polarity hold latch, and explain with

[16]

the help of flow table & excitation table. [2+2+2]

(b) Draw the logic diagram of shift register latch and explain its principle. Using

above latch. [3+7]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 3

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. Define and derive the following terms in a system.

(a) MTTR [2+6]

(b) Hazard rate functions. [2+6]

2. (a) What is a tree like circuit. Give properties of tree like circuits.

(b) For the given tree like circuit find the complete test set using path sensitizing

method as show in figure1. [3+5+8]

www.andhracolleges.com

3. (a) Explain fail soft-operation.

Figure 1:

(b) Explain the 5 MR reconfiguration mechanism and also explain how it care

tolerate single, double and Trible faults in a given system.

4. With an example explain :

(a) software redundancy.

[3x4=12]

[4]

(b) time redundancy. [8+8]

5. (a) What is the need for self checking circuits

(b) Design a totally self checking checker by using reddy’s partition method for

2out of 5 code. [6+10]

6. Explain in detail about fail-safe sequential circuits design with an example. [16]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 3

7. (a) Prove that five tests are sufficient to detect all faults in a combinational logic

circuit by inserting addition control logic to the following function, obtain the

test pattern.

f=(A,B,C,D)=AB+BC+BD

(b) Obtain the ten sequences denoted as P = {xo x1 ......xa } from the basic module

of the above circuit and get the compatable pair from the set P. [8+8]

www.andhracolleges.com

8. (a) Draw the logic diagram of Built-in Logic Block Observer.

(b) Discuss BILBO based BIST architecture. [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 4

IV B.Tech I Semester Supplementary Examinations, February 2007

FAULT TOLERANT SYSTEMS

( Common to Computer Science & Engineering and Electronics &

Computer Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Distinguish between failures, and faults Explain [2+2]

(b) Explain the different modeling schemes of faults that generally come across in

digital circuits. [3x2=6]

(c) Explain the following terms with respect to digital circuits with suitable ex-

amples.

i. Fault diagnosis.

ii. Fault detection test set.

iii. Test vector generation. [3x2=6]

2. (a) What are the goals of Design for testability?

(b) Distinguish between ditermenistic test pattern generation and probabilitstic

test pattern generation methods. [6+5+5]

3. (a) With an example explain sift out modular redundancy technique.

(b) With an example explain self-purging redundancy. [8+8]

www.andhracolleges.com

4. (a) What is the goal of “pluibus” system used in ARPA network. Explain its

working.

(b) What is ment by fail soft operation? What should a system have to achieve

the capability of fail soft operation. [4+4+4+4]

5. Design a totally

(a) self-checking circuit for m out of n codes by translating the code to 1 out of 2.

(b) Verify it for 3 out of 5 code. [8+8]

6. (a) Explain the design consideration of self checking PLA considering stray faults

with suitable example.

(b) How do you implement strong fault service for the functional PLA. [8+8]

7. (a) Prove that five tests are sufficient to detect all faults in a combinational logic

circuit by inserting addition control logic to the following function, obtain the

test pattern.

f=(A,B,C,D)=AB+BC+BD

(b) Obtain the ten sequences denoted as P = {xo x1 ......xa } from the basic module

of the above circuit and get the compatable pair from the set P. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR410506 Set No. 4

8. Explain observability enhancement with neat diagram with suitable examples. [4+2+10]

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

You might also like

- ZXCTN 6300&6200&6100&6110 Single System Commissioning Guide - R1.3Document49 pagesZXCTN 6300&6200&6100&6110 Single System Commissioning Guide - R1.3DavoodNo ratings yet

- MM 2006Document8 pagesMM 2006andhracollegesNo ratings yet

- Eamcet 2010 Medical PaperDocument63 pagesEamcet 2010 Medical PaperandhracollegesNo ratings yet

- 06rr410506 Fault Tolerant SystemsDocument7 pages06rr410506 Fault Tolerant SystemsandhracollegesNo ratings yet

- Set No. 1: Min Max Wmin Max Vmax Vmax Vmin VmaxDocument5 pagesSet No. 1: Min Max Wmin Max Vmax Vmax Vmin VmaxandhracollegesNo ratings yet

- JNTU Old Question Papers 2007Document8 pagesJNTU Old Question Papers 2007Srinivasa Rao GNo ratings yet

- Set No. 1Document5 pagesSet No. 1andhracollegesNo ratings yet

- r07220205 Control SystemsDocument9 pagesr07220205 Control SystemsandhracollegesNo ratings yet

- Co 2007Document4 pagesCo 2007andhracollegesNo ratings yet

- NSC 2007Document5 pagesNSC 2007andhracollegesNo ratings yet

- DicaDocument8 pagesDicaandhracollegesNo ratings yet

- 08 r05310502 Object Oriented Analysis and DesignDocument7 pages08 r05310502 Object Oriented Analysis and DesignandhracollegesNo ratings yet

- Rr410506 Fault Tolerant SystemsDocument8 pagesRr410506 Fault Tolerant Systemsdayas1979No ratings yet

- 08rr410404 Optical CommunicationDocument8 pages08rr410404 Optical CommunicationandhracollegesNo ratings yet

- Nov07 Pulse Digital CircuitsDocument9 pagesNov07 Pulse Digital CircuitsandhracollegesNo ratings yet

- r05220205 Control SystemsDocument9 pagesr05220205 Control SystemsandhracollegesNo ratings yet

- Sr05220205 Control SystemsDocument8 pagesSr05220205 Control SystemsandhracollegesNo ratings yet

- Java 2006Document5 pagesJava 2006andhracollegesNo ratings yet

- Set No. 1Document6 pagesSet No. 1andhracollegesNo ratings yet

- 07 Rr420202 HVDC TransmissionDocument4 pages07 Rr420202 HVDC TransmissionandhracollegesNo ratings yet

- Aca 2005Document5 pagesAca 2005andhracollegesNo ratings yet

- Uml 2006Document8 pagesUml 2006andhracollegesNo ratings yet

- 06N - RR410302 Cad CamDocument4 pages06N - RR410302 Cad CamandhracollegesNo ratings yet

- r05410408 Digital Image ProcessingDocument5 pagesr05410408 Digital Image ProcessingandhracollegesNo ratings yet

- 07N - RR410302 Cad CamDocument6 pages07N - RR410302 Cad CamandhracollegesNo ratings yet

- Ads 2007Document4 pagesAds 2007andhracollegesNo ratings yet

- Rr410203 Computer Methods in Power SystemsDocument9 pagesRr410203 Computer Methods in Power SystemsandhracollegesNo ratings yet

- Rr720507 Neural NetworksDocument5 pagesRr720507 Neural NetworksandhracollegesNo ratings yet

- Rr720303 MicroprocessorsDocument8 pagesRr720303 MicroprocessorsandhracollegesNo ratings yet

- MechatronicsDocument4 pagesMechatronicsandhracollegesNo ratings yet

- C&dsDocument4 pagesC&dsandhracollegesNo ratings yet

- 08 r05310404 Digital CommunicationDocument8 pages08 r05310404 Digital CommunicationandhracollegesNo ratings yet

- 08RR410302 Cad CamDocument5 pages08RR410302 Cad CamandhracollegesNo ratings yet

- Uml M 2006Document8 pagesUml M 2006andhracollegesNo ratings yet

- Examination Paper: May/June 2020 COMP2211-WE01Document6 pagesExamination Paper: May/June 2020 COMP2211-WE01africa threeNo ratings yet

- Neural Networks and Fuzzy Logic PDFDocument9 pagesNeural Networks and Fuzzy Logic PDFbadamsmithNo ratings yet

- TC 2006Document10 pagesTC 2006andhracollegesNo ratings yet

- Dmadwh 2007Document5 pagesDmadwh 2007andhracollegesNo ratings yet

- Summer 2021 AMIIW Question PapersDocument32 pagesSummer 2021 AMIIW Question PapersRiyaz AhmedNo ratings yet

- Dmadwh 2006Document7 pagesDmadwh 2006andhracollegesNo ratings yet

- r05410409 Satellite CommunicationsDocument5 pagesr05410409 Satellite CommunicationsandhracollegesNo ratings yet

- NcseDocument5 pagesNcseandhracollegesNo ratings yet

- Set No. 1Document7 pagesSet No. 1andhracollegesNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- LP 2005Document8 pagesLP 2005andhracollegesNo ratings yet

- Ds 2006Document4 pagesDs 2006andhracollegesNo ratings yet

- Srr320404 Microwave EngineeringDocument7 pagesSrr320404 Microwave EngineeringandhracollegesNo ratings yet

- Rr420402 Radar EngineeringDocument4 pagesRr420402 Radar EngineeringandhracollegesNo ratings yet

- Examination Paper: May/June 201 9 COMP2211-WE01Document6 pagesExamination Paper: May/June 201 9 COMP2211-WE01africa threeNo ratings yet

- Sjr05010201 Applied PhysicsDocument8 pagesSjr05010201 Applied PhysicsandhracollegesNo ratings yet

- Ece361 - Ee 2010 S1Document5 pagesEce361 - Ee 2010 S1Mu'izz KaharNo ratings yet

- r07320204 InstrumentationDocument6 pagesr07320204 InstrumentationandhracollegesNo ratings yet

- March2006 Network Security and CryptographyDocument5 pagesMarch2006 Network Security and CryptographyKeerthi ReddyNo ratings yet

- r05310201 Computer IonDocument5 pagesr05310201 Computer IonskssushNo ratings yet

- R05320506-SOFTWARE-TESTING-METHODOLOGIES May 2008Document5 pagesR05320506-SOFTWARE-TESTING-METHODOLOGIES May 2008api-19718334No ratings yet

- Btech Cse 4 Sem Advance Computer Architecture 2012Document7 pagesBtech Cse 4 Sem Advance Computer Architecture 2012souravnaskar12578954No ratings yet

- Rr720505 RoboticsDocument7 pagesRr720505 RoboticsandhracollegesNo ratings yet

- Mobile Edge Artificial Intelligence: Opportunities and ChallengesFrom EverandMobile Edge Artificial Intelligence: Opportunities and ChallengesNo ratings yet

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocument1 pageEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggNo ratings yet

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocument3 pagesEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2014 Engineering Key SolutionsDocument42 pagesEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocument42 pagesEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2007 Engineering PaperDocument13 pagesEamcet 2007 Engineering Paperandhracolleges100% (1)

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocument62 pagesAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Polycet 2014 Question PaperDocument24 pagesPolycet 2014 Question PaperandhracollegesNo ratings yet

- Eamcet 2001 Engineering PaperDocument14 pagesEamcet 2001 Engineering Paperandhracolleges100% (1)

- Eamcet 2006 Engineering PaperDocument14 pagesEamcet 2006 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2004 Engineering PaperDocument12 pagesEamcet 2004 Engineering PaperandhracollegesNo ratings yet

- EAMCET NotificationDocument3 pagesEAMCET NotificationKeerthiPratheek ReddyNo ratings yet

- EAMCET Engineering Entrance Solved Paper 2000Document13 pagesEAMCET Engineering Entrance Solved Paper 2000Giri NathNo ratings yet

- Icet-2014-Important Instructions BookletDocument3 pagesIcet-2014-Important Instructions BookletandhracollegesNo ratings yet

- Eamcet 2003 Engineering PaperDocument12 pagesEamcet 2003 Engineering Paperandhracolleges100% (1)

- Eamcet 2002 Engineering PaperDocument14 pagesEamcet 2002 Engineering Paperandhracolleges0% (1)

- Eamcet 2009 Engineering Physics PaperDocument19 pagesEamcet 2009 Engineering Physics PaperandhracollegesNo ratings yet

- TS ICET Syllabus and Exam PatternDocument5 pagesTS ICET Syllabus and Exam PatterngayathriNo ratings yet

- FeeDocument34 pagesFeeThanniru VenkateshNo ratings yet

- Eamcet Pharmacy College Fee DetailsDocument14 pagesEamcet Pharmacy College Fee DetailsandhracollegesNo ratings yet

- Galgotias University Uttar Pradesh: School of Computing Science & EngineeringDocument3 pagesGalgotias University Uttar Pradesh: School of Computing Science & EngineeringTushant ChakravartyNo ratings yet

- MINI MCR-SL-PT100-UI (-SP) (-NC) : Configurable Temperature Transducer For PT100Document12 pagesMINI MCR-SL-PT100-UI (-SP) (-NC) : Configurable Temperature Transducer For PT100Sandro CentellasNo ratings yet

- Automatic Seed Sowing Robot: International Research Journal of Engineering and Technology (IRJET)Document3 pagesAutomatic Seed Sowing Robot: International Research Journal of Engineering and Technology (IRJET)Teshome GetachewNo ratings yet

- Protocol Specification For Interfacing To Data Communication NetworksDocument205 pagesProtocol Specification For Interfacing To Data Communication NetworksMovieTube DBNo ratings yet

- UniManager Brochure - 2022 v1Document10 pagesUniManager Brochure - 2022 v1Arvans AGNo ratings yet

- Ijert Ijert: FPGA Implementation of Orthogonal Code Convolution For Efficient Digital CommunicationDocument7 pagesIjert Ijert: FPGA Implementation of Orthogonal Code Convolution For Efficient Digital Communicationtariq76No ratings yet

- Introduction To Database Management SystemDocument20 pagesIntroduction To Database Management SystemRould Christian Ganzon AlertaNo ratings yet

- AsteRx SB3 ProBase Firmware v4.14.4 Reference GuideDocument450 pagesAsteRx SB3 ProBase Firmware v4.14.4 Reference GuideSergiy PogoryelovNo ratings yet

- Digital Control SystemDocument6 pagesDigital Control SystemAlpha100% (1)

- Workshop On Digital Design With FPGA Organized by EiTRADocument4 pagesWorkshop On Digital Design With FPGA Organized by EiTRAmurali036No ratings yet

- Mib & SibDocument14 pagesMib & SibebraoNo ratings yet

- Ranjit Meghwal: ObjectiveDocument3 pagesRanjit Meghwal: ObjectiveRanjit meghwalNo ratings yet

- MP2480 3A LED Driver, Wide 5V To 36V OperatingDocument1 pageMP2480 3A LED Driver, Wide 5V To 36V Operatingjunaid ahmadNo ratings yet

- DOE DPV Website Tutorial: Matthew Rylander Jeff SmithDocument12 pagesDOE DPV Website Tutorial: Matthew Rylander Jeff SmithAli MuhtarNo ratings yet

- Communication Engineering 9781259006869 1259006867 CompressDocument719 pagesCommunication Engineering 9781259006869 1259006867 CompressyogasriNo ratings yet

- OS DPPs A4Document47 pagesOS DPPs A4DeepNo ratings yet

- Student Information System ProjectDocument4 pagesStudent Information System ProjectWuWong TurtleNo ratings yet

- Windows Forensic Artifacts Cheat SheetDocument2 pagesWindows Forensic Artifacts Cheat Sheetprasenjit_boseNo ratings yet

- Circuits SolnDocument5 pagesCircuits Solndwaytikitan28No ratings yet

- Ed A User GuideDocument91 pagesEd A User GuideMarco TomasNo ratings yet

- Kendall Su PDFDocument13 pagesKendall Su PDFFurqan khwaja0% (1)

- SAP UI5 Interview Q&ADocument9 pagesSAP UI5 Interview Q&AARPANANo ratings yet

- OX6 Installation and AdministrationDocument223 pagesOX6 Installation and AdministrationClaudia Cerda AviñaNo ratings yet

- Chapter 1 CoaDocument3 pagesChapter 1 CoaSamuel AdamuNo ratings yet

- Ddos Script (Python)Document2 pagesDdos Script (Python)webwise69No ratings yet

- Recode in VBA Learn To Automate Excel by P - G BLANCODocument60 pagesRecode in VBA Learn To Automate Excel by P - G BLANCOLiviu CristeaNo ratings yet

- Dreamcast Hardware Specification OutlineDocument40 pagesDreamcast Hardware Specification OutlineJoséManuelBenettiNo ratings yet

- Job Board Project PlanDocument47 pagesJob Board Project Plannuhamin zNo ratings yet

- Medium HighVoltageCapacitors 12022ghjkb JJGKGDocument11 pagesMedium HighVoltageCapacitors 12022ghjkb JJGKGKhairil AminNo ratings yet