Professional Documents

Culture Documents

PMCC VCO24-30G Datasheet Rev 2.3

PMCC VCO24-30G Datasheet Rev 2.3

Uploaded by

GbarbarOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PMCC VCO24-30G Datasheet Rev 2.3

PMCC VCO24-30G Datasheet Rev 2.3

Uploaded by

GbarbarCopyright:

Available Formats

20-30GHz VCOs

PMCC_VCO20G/24G/25G/26G/30G

IP MACRO Datasheet Rev 2.3

Process: Jazz Semiconductor SBC18HX

DESCRIPTION FEATURES

The PMCC_VCO20G /24G /25G /26G /30G • Center frequency (GHz): 20, 24, 25, 26, 30

is a set of fully differential high speed VCOs • Tuning range: 10%

covering 20GHz … 30GHz frequency range, • Tuning voltage input: 0 … +3.3V

designed using Jazz SiGe120 (SBC18HX) • Phase noise: -105dBc @ 1MHz offset

process. Differential architecture ensures • Supply voltage: 3.3V ±5%

substrate and power supply noise immunity.

• Power consumption: 90mW

Macro features optional 50 Ohm terminated

• Fully differential architecture

buffers at its output. Built-in power-down mode

enables power saving in case when block is not • Layout area: 220 x 320 um

operated. Operation frequencies, I/O signal

levels, control functions and features can be

customized upon special agreement.

FUNCTIONAL DESCRIPTION

Block diagram of macro is shown on Figure 1. Voltage on TUNE pin defines VCO core oscillation

frequency. VCO output is fed to output driver, isolating active VCO core from driven circuitry. Output driver

provides macro output OUTP/OUTN. PWR_DOWN pin controls macro operating mode: active or power-

down. Negative temperature coefficient biasing is provided to compensate VCO frequency temperature

dependency.

VCC

FRQ DRV

OUTP

TUNE Control OUTN

BIASING

PWR_DOWN

NTC

VEE

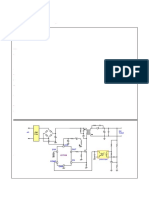

Figure 1. Macro block diagram

PMCC_VCO20G /24G /25G /26G /30G DATASHEET

©2007. Pacific Microchip Corp. Specifications are subject to change without notice. No circuit patents licenses are implied. Page 1 of 3

MACRO SCHEMATIC SYMBOL. PIN DESCRIPTION

Pin Name Description Type

ntune Tune voltage I

cout VCO CML direct output O

ncout VCO CML inverted output O

vcc Positive power supply PWR

vee Ground GND

refp Reference voltage input I

pd Power down input CMOS

Figure 2. Macro schematic symbol

AC/DC ELECTRICAL SPECIFICATIONS

Table 1. Absolute maximum ratings

Description Min Max Units

Tune input voltage (pin: ntune) -0.5 +3.5 V

Power supply (pin vcc) -0.5 +3.5 V

CMOS control input voltage (pin pd) -0.5 +3.5 V

Reference voltage input (pin refp) -0.5 +3.5 V

Junction temperature -25 125 ºC

End Of Life (EOL) 10 years

DC Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Table 2. DC Electrical Characteristics

Parameter Conditions Min Typ Max Units

Positive power supply Vcc 3.1 3.3 3.5 V

Supply current 27 mA

Tjunction=125ºC

Supply current in power down state 0.1 mA

NTUNE input voltage Vtune 0 Vcc V

Power down control input high (Vhi) 1.7 3.5 V

Power down control input low (Vlo) 0.5 V

Table 3. AC Characteristics

Parameter Min Typ Max Units

Center frequency range * 20 30 GHz

Tuning range * 10 %

Phase Noise @ 1MHz offset -105 dBc

* Block is subject for optimization for optimum performance at the customer selected frequency within the

range provided in the table.

PMCC_VCO20G /24G /25G /26G /30G DATASHEET

©2007. Pacific Microchip Corp. Specifications are subject to change without notice. No circuit patents licenses are implied. Page 2 of 3

220µm

MACRO LAYOUT VIEW

VCO macro layout is optimally designed taking symmetry, parasitic

capacitances, inductance and reliability into account. Layout design leverages

all 6 metal layers available in the SBC18HXL process. Compact layout

ensures minimum parasitic capacitance, inductance, device mismatch and

320µm

minimum die area.

Layout considerations for macro integration:

• METAL6 is used for ground connections to minimize “ground

bounce” effects.

• METAL5 is used for VCC connection Figure 3. Macro core layout

• Transmission line structures should be considered for long view. Note: some of the details

interconnections in case of macro direct connection to IC pads and/or layers might be omitted.

(through optional 50 Ohm terminated input buffers)

• Other layout features incorporated by customer into or adjacent to macro can affect macro

performance and should be carefully analyzed.

IP BLOCK TEST STRUCTURE

Test structure consisting of VCO macro, 50 Ohm terminated output and reference voltage generators is

shown on Figure 4. Simulation schematic for test structure is shown on Figure . Test IC layout presented on

Figure 6.

Figure 4. Macro test structure block diagram Figure 5. IP block test structure simulation schematic

Figure 6. VCO macro test chip layout.

PMCC_VCO20G /24G /25G /26G /30G DATASHEET

©2007. Pacific Microchip Corp. Specifications are subject to change without notice. No circuit patents licenses are implied. Page 3 of 3

You might also like

- Volo's Guide To Monsters - 1Document7 pagesVolo's Guide To Monsters - 1Saz100% (1)

- Process Validation ReportDocument4 pagesProcess Validation ReportSUBODHH100% (1)

- PMCC VCO11G Datasheet Rev 2.4Document3 pagesPMCC VCO11G Datasheet Rev 2.4GbarbarNo ratings yet

- SDC7500 enDocument7 pagesSDC7500 enodelaineNo ratings yet

- CT5601 (SOT23-6) EN Rev1.0Document12 pagesCT5601 (SOT23-6) EN Rev1.0Angel Luciano Ramon GomezNo ratings yet

- Ir2175 (S) & (PBF) : Linear Current Sensing IcDocument7 pagesIr2175 (S) & (PBF) : Linear Current Sensing IcDavid CoronadoNo ratings yet

- VB325SP STMicroelectronicsDocument9 pagesVB325SP STMicroelectronicsAigars MulisNo ratings yet

- General Description Features: High Performance Current Mode PWM ControllerDocument11 pagesGeneral Description Features: High Performance Current Mode PWM ControllerPhạm Tấn HảiNo ratings yet

- 1.25Gb 20klm SM 1550nm LC (Cisco Coded)Document7 pages1.25Gb 20klm SM 1550nm LC (Cisco Coded)Sean SerinNo ratings yet

- PWM Controller IC For AC/DC Converter: DatasheetDocument35 pagesPWM Controller IC For AC/DC Converter: DatasheetRaka Satria PradanaNo ratings yet

- Soldadora UTC3843DDocument9 pagesSoldadora UTC3843DChristian ormeñoNo ratings yet

- Circuito en Fuente TV LCD Mustek N3856VGDocument13 pagesCircuito en Fuente TV LCD Mustek N3856VGAntonio ChavezNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- TMR1302 Datasheet EN V1.1Document5 pagesTMR1302 Datasheet EN V1.1shreyas dasNo ratings yet

- datasheet عن الالكترونياتDocument5 pagesdatasheet عن الالكترونياتdkvnsyvkgbNo ratings yet

- DC 2317 AfaDocument10 pagesDC 2317 AfavictorhugoseNo ratings yet

- 1 CL23XX EN Rev.1.0 2641Document11 pages1 CL23XX EN Rev.1.0 2641Sumit SinghNo ratings yet

- 1.25Gb 20klm 1490T-1310R SM (Standard Code)Document6 pages1.25Gb 20klm 1490T-1310R SM (Standard Code)Sean SerinNo ratings yet

- HT2273 Hot ChipDocument11 pagesHT2273 Hot ChipАндрей ШипетунNo ratings yet

- Power Supply Supervisory/ Over and Undervoltage Protection Circuit MC3425Document12 pagesPower Supply Supervisory/ Over and Undervoltage Protection Circuit MC3425Spatar KevinNo ratings yet

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 pagesTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNo ratings yet

- 497 2334 5 DatasheetzDocument17 pages497 2334 5 DatasheetzanandaeizzNo ratings yet

- Driver de Motor Paso A PasoDocument4 pagesDriver de Motor Paso A PasoRoberto GonzalesNo ratings yet

- Contech 2429 PDFDocument5 pagesContech 2429 PDFAntoni MonteroNo ratings yet

- MICRONE Nanjing Micro One Elec ME6213C33M5G - C236666Document10 pagesMICRONE Nanjing Micro One Elec ME6213C33M5G - C236666João CavacoNo ratings yet

- RM6203Document7 pagesRM6203Mario José Gallo AttanasioNo ratings yet

- EM5106 ExcellianceMOSDocument10 pagesEM5106 ExcellianceMOSSib Repair CenterNo ratings yet

- Utc3842 YouwangelectronicsDocument9 pagesUtc3842 YouwangelectronicsMindSet MarcosNo ratings yet

- 1.25Gb 550mtr MM LC (Cisco Coded)Document6 pages1.25Gb 550mtr MM LC (Cisco Coded)Sean SerinNo ratings yet

- 6脚电源IC资料及代换Document7 pages6脚电源IC资料及代换Justin NgNo ratings yet

- CT5503SDocument12 pagesCT5503SSubhash Digambar VisalNo ratings yet

- Pm25cg1ap120 Pm25cg1apl120Document9 pagesPm25cg1ap120 Pm25cg1apl120Abdul KurniadiNo ratings yet

- VB326Document10 pagesVB326NoelNo ratings yet

- Ob 2223 HCDocument11 pagesOb 2223 HCRivaldyNo ratings yet

- Mitsubishi: 7 VCC VCCDocument6 pagesMitsubishi: 7 VCC VCCCharbel TadrosNo ratings yet

- Oscilador de Inverter BD9897FSDocument5 pagesOscilador de Inverter BD9897FSAntonio ChavezNo ratings yet

- Cargador Enercell cr623xDocument11 pagesCargador Enercell cr623xcuco777No ratings yet

- Silicon Monolithic Integrated Circuit LED Driver Control IC: Maximum Junction TemperatureDocument5 pagesSilicon Monolithic Integrated Circuit LED Driver Control IC: Maximum Junction TemperatureVenera Segunda ManoNo ratings yet

- AOZ1267QI-01: General Description FeaturesDocument16 pagesAOZ1267QI-01: General Description Featuresvictory_1410No ratings yet

- UTC7266 Linear Integrated Circuit: 7+7W Dual Bridge AmplifierDocument9 pagesUTC7266 Linear Integrated Circuit: 7+7W Dual Bridge AmplifierledNo ratings yet

- UC3848Document12 pagesUC3848isaiasvaNo ratings yet

- C555 UnisonicTechnologiesDocument4 pagesC555 UnisonicTechnologieskaryadi sbyNo ratings yet

- Reference Design: PR883: A 300-W, Universal Input, Isolated PFC Power Supply For LCD TV ApplicationsDocument23 pagesReference Design: PR883: A 300-W, Universal Input, Isolated PFC Power Supply For LCD TV Applicationsgolu201No ratings yet

- Single Timer: Features DescriptionDocument14 pagesSingle Timer: Features DescriptionAHMED MELIH ULUSOYNo ratings yet

- AD7811/AD7812: Parameter Y Version Units Test Conditions/CommentsDocument1 pageAD7811/AD7812: Parameter Y Version Units Test Conditions/CommentsAntonio HerreraNo ratings yet

- Non-Contact Rotary Position Sensor: FeaturesDocument5 pagesNon-Contact Rotary Position Sensor: FeaturesctdmnNo ratings yet

- Wm-810 Specification SheetDocument5 pagesWm-810 Specification SheetTekno DiéselNo ratings yet

- Hall Effect Sensor IC OH 137Document2 pagesHall Effect Sensor IC OH 137edu178No ratings yet

- DP8600C YwDocument9 pagesDP8600C YwSURESH CHANDRA ROUTNo ratings yet

- RF & Microwave Discrete Low Power Transistors: FeaturesDocument4 pagesRF & Microwave Discrete Low Power Transistors: FeaturesytnateNo ratings yet

- 2scr502u3 HZG: V 30V I 0.5aDocument9 pages2scr502u3 HZG: V 30V I 0.5aprofe321No ratings yet

- NCP7800 1.0 A Positive Voltage Regulators: TO 220 3 T Suffix Case 221abDocument12 pagesNCP7800 1.0 A Positive Voltage Regulators: TO 220 3 T Suffix Case 221abRubén GarciaNo ratings yet

- MRF393Document4 pagesMRF393andreasmonNo ratings yet

- Ir 2121Document16 pagesIr 2121rahi172No ratings yet

- NJM2626 eDocument9 pagesNJM2626 eMuhammad RafiqueNo ratings yet

- MM432Document40 pagesMM432Wellington SantanaNo ratings yet

- DatasheetDocument9 pagesDatasheetJakub PilarskiNo ratings yet

- M62015L, FP M62016L, FP: V C Reset INT GNDDocument4 pagesM62015L, FP M62016L, FP: V C Reset INT GNDJose Ramon ArayNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- An 11.1 Gbps Analog PRML Receiver For Electronic Dispersion Compensation of Fiber Optic CommunicationsDocument16 pagesAn 11.1 Gbps Analog PRML Receiver For Electronic Dispersion Compensation of Fiber Optic CommunicationsGbarbarNo ratings yet

- Start Up Circuit Apparatus and Method Patent Application 20070241738Document13 pagesStart Up Circuit Apparatus and Method Patent Application 20070241738GbarbarNo ratings yet

- RFIC Symposium CDRDocument4 pagesRFIC Symposium CDRGbarbarNo ratings yet

- A Monolithic One-Sample/Bit Partial-Response Maximum Likelihood Sige Receiver For Electronic Dispersion Compensation of 10.7Gb/S Fiber ChannelsDocument3 pagesA Monolithic One-Sample/Bit Partial-Response Maximum Likelihood Sige Receiver For Electronic Dispersion Compensation of 10.7Gb/S Fiber ChannelsGbarbarNo ratings yet

- PMCC VCO11G Datasheet Rev 2.4Document3 pagesPMCC VCO11G Datasheet Rev 2.4GbarbarNo ratings yet

- RFIC09 Symposium PaperDocument4 pagesRFIC09 Symposium PaperGbarbarNo ratings yet

- PMCC DIV60G 60GHz Prescaler Test ReportDocument12 pagesPMCC DIV60G 60GHz Prescaler Test ReportGbarbarNo ratings yet

- A 0.36W 6b Up To 20GSps DAC For UWB Wave Formation SlidesDocument3 pagesA 0.36W 6b Up To 20GSps DAC For UWB Wave Formation SlidesGbarbarNo ratings yet

- An 11.1Gbps Analog PRML Receiver For EDC of Up To 400km-Reach WDM Fiber-Optic LinksDocument4 pagesAn 11.1Gbps Analog PRML Receiver For EDC of Up To 400km-Reach WDM Fiber-Optic LinksGbarbarNo ratings yet

- 1.6 3.2GHz 6th-Order GMC FilterDocument9 pages1.6 3.2GHz 6th-Order GMC FilterGbarbarNo ratings yet

- A 0.36W 6b Up To 20GSps DAC For UWB Wave FormationDocument3 pagesA 0.36W 6b Up To 20GSps DAC For UWB Wave FormationGbarbarNo ratings yet

- The Colometric StructureDocument26 pagesThe Colometric StructureMerletoNo ratings yet

- 2-Altaf Gauhar's VersionDocument13 pages2-Altaf Gauhar's VersionSaptarshi BasuNo ratings yet

- Mark Scheme (Results) : Summer 2018 Pearson Edexcel International GCSE in Further Pure Mathematics (4PM0) Paper 01Document26 pagesMark Scheme (Results) : Summer 2018 Pearson Edexcel International GCSE in Further Pure Mathematics (4PM0) Paper 01Newton JohnNo ratings yet

- ECO Drive Display: Honda Fit GP5 Driving AidsDocument3 pagesECO Drive Display: Honda Fit GP5 Driving Aidsmzee233100% (1)

- We Didnt Start The Fire RubricDocument2 pagesWe Didnt Start The Fire Rubricapi-248613072No ratings yet

- A Concept Paper About LoveDocument5 pagesA Concept Paper About LoveStephen Rivera100% (1)

- Welcome To Fourtower Bridge: A Paths Peculiar Module For Fantasy Roleplaying GamesDocument7 pagesWelcome To Fourtower Bridge: A Paths Peculiar Module For Fantasy Roleplaying GamesTapanco BarerraNo ratings yet

- ITE403 Information Security Worksheet T-2 PUBLIC KEY ENCRYPTION With RSA SPRING2020Document5 pagesITE403 Information Security Worksheet T-2 PUBLIC KEY ENCRYPTION With RSA SPRING2020Aws FaeqNo ratings yet

- Project Management Process GroupsDocument10 pagesProject Management Process GroupsQueen Valle100% (1)

- Chapter 6 Learning English For Specific PurposesDocument19 pagesChapter 6 Learning English For Specific PurposesMaRy ChUy HRNo ratings yet

- Annexure 6.0 Candidate InstructionsDocument8 pagesAnnexure 6.0 Candidate Instructionschiluverushivaprasad02No ratings yet

- PROCEEDINGS of The Numismatic and Antiquarian Society of PhiladelphiaDocument304 pagesPROCEEDINGS of The Numismatic and Antiquarian Society of PhiladelphiaRichard CastorNo ratings yet

- Nâng Cao 1 - 1 BảnDocument4 pagesNâng Cao 1 - 1 BảnThu TàiNo ratings yet

- How Can Apologetics Help Me Defend My Faith?Document16 pagesHow Can Apologetics Help Me Defend My Faith?Regina D. RogersNo ratings yet

- Crecimiento Bajo en Carbono - Carbon-Disclosure-Project-2011Document80 pagesCrecimiento Bajo en Carbono - Carbon-Disclosure-Project-2011Alan Cereceda EscalonaNo ratings yet

- Alter Ego 181 PreviewDocument20 pagesAlter Ego 181 PreviewJohn LloydNo ratings yet

- Ingles De, I PaaaaaaaaaaaaaaaDocument20 pagesIngles De, I PaaaaaaaaaaaaaaaJaz PintoNo ratings yet

- International Journal of Technical Innovation in Modern Engineering & Science (IJTIMES)Document3 pagesInternational Journal of Technical Innovation in Modern Engineering & Science (IJTIMES)Vikunj TilvaNo ratings yet

- Sabaneyev Sonata For Violin, Cello, and Piano, Op. 20Document71 pagesSabaneyev Sonata For Violin, Cello, and Piano, Op. 20Meow MeowNo ratings yet

- Advanced Quality ManualDocument17 pagesAdvanced Quality ManualalexrferreiraNo ratings yet

- Queues: Chapter 6 - Principles of Data Structures Using C by Vinu V DasDocument25 pagesQueues: Chapter 6 - Principles of Data Structures Using C by Vinu V DasAamir ChohanNo ratings yet

- Oh The Tooth That One Ths Was A Story About Place ValueDocument9 pagesOh The Tooth That One Ths Was A Story About Place Valuecagena7907No ratings yet

- Soal Kalimat Prohibition SMP Kelas 7Document3 pagesSoal Kalimat Prohibition SMP Kelas 7yura chanNo ratings yet

- MYCOBIT Control Objective Assessment FormsDocument5 pagesMYCOBIT Control Objective Assessment FormsRafasaxNo ratings yet

- Sexy Book 121Document252 pagesSexy Book 121Irepan Ponce50% (2)

- Angles and Directions SurveyingDocument23 pagesAngles and Directions SurveyingAbel AmmoNo ratings yet

- 1,200 Calorie Diet Menu - 7 Day Lose 20 Pounds Weight Loss Meal Plan PDFDocument14 pages1,200 Calorie Diet Menu - 7 Day Lose 20 Pounds Weight Loss Meal Plan PDFABRAHAN SUPO TITONo ratings yet

- Sep. Gravimetrica - CromitaDocument13 pagesSep. Gravimetrica - Cromitaemerson sennaNo ratings yet