Professional Documents

Culture Documents

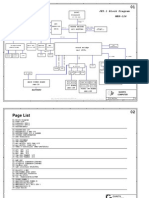

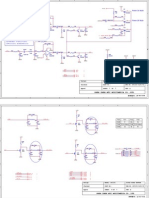

M2Ne PDF

M2Ne PDF

Uploaded by

Adriano MartinsCopyright:

Available Formats

You might also like

- Building Honda K-Series Engine PerformanceFrom EverandBuilding Honda K-Series Engine PerformanceRating: 5 out of 5 stars5/5 (2)

- Baf 1550Document1 pageBaf 1550Steren México75% (4)

- mlt666 Rev2.8l 166Document1 pagemlt666 Rev2.8l 166victoras21No ratings yet

- Stress - The Different Kinds of StressDocument4 pagesStress - The Different Kinds of StressbogdanNo ratings yet

- Msma PDFDocument100 pagesMsma PDFMimi Aireen Harmira HassimNo ratings yet

- Pull Up EbookDocument12 pagesPull Up EbookDanko Kovačević100% (2)

- Adira Nas WoDocument314 pagesAdira Nas Wohengkygunawan485No ratings yet

- Sursa Alimentare (Fsp336-Fsp312)Document12 pagesSursa Alimentare (Fsp336-Fsp312)florea_ctinNo ratings yet

- Diagrama PIC LabPicDocument1 pageDiagrama PIC LabPicAggroBerlin MtzNo ratings yet

- Guiade ImprentaDocument2 pagesGuiade ImprentaLuismarth BandresNo ratings yet

- Samsung Sch-A410 Service ManualDocument30 pagesSamsung Sch-A410 Service Manualsaboor ashraf100% (1)

- Layout 9700Document2 pagesLayout 9700kasriNo ratings yet

- Onyx Refresh POP 31442 002 - Rev1Document2 pagesOnyx Refresh POP 31442 002 - Rev1David ExfannyNo ratings yet

- Diagram ADocument1 pageDiagram AVictor RamirezNo ratings yet

- CLASS-HDocument1 pageCLASS-Hto_netiks100% (1)

- L3 Board Layout XT1063-XT1064-XT1068-XT1069 V1.0Document2 pagesL3 Board Layout XT1063-XT1064-XT1068-XT1069 V1.0José Luiz Scarano JuniorNo ratings yet

- Peavey Valveking 100 212Document12 pagesPeavey Valveking 100 212whitestratNo ratings yet

- Valveking 212 DiagramDocument12 pagesValveking 212 DiagramDan Radu TalpalariuNo ratings yet

- Ak1 MB 1213aDocument30 pagesAk1 MB 1213aAshok JangraNo ratings yet

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocument27 pagesDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisNo ratings yet

- Schema Electrica de Conectare A Procesorului 8086 La 16kW X 16b de Tip 558PP3 Si 16kW X 16b de Tip 537PY10ADocument2 pagesSchema Electrica de Conectare A Procesorului 8086 La 16kW X 16b de Tip 558PP3 Si 16kW X 16b de Tip 537PY10AValeria SerioghinaNo ratings yet

- Acd-28 Sm-6088cd Server SCHDocument1 pageAcd-28 Sm-6088cd Server SCHPaula TonelloNo ratings yet

- Max 038Document1 pageMax 038Javier Pillco100% (1)

- DataDocument920 pagesDataabhijeetNo ratings yet

- W375 L3 V1.2 SchemDocument3 pagesW375 L3 V1.2 SchemAdrian PeterNo ratings yet

- Kx-Tda0103Xj/Kx-Tda0103X L-Type Power Supply Unit (Psu-L) 4/6Document1 pageKx-Tda0103Xj/Kx-Tda0103X L-Type Power Supply Unit (Psu-L) 4/6Hpone HtetNo ratings yet

- Ergo Laptop Motherboard Schematic DiagramDocument52 pagesErgo Laptop Motherboard Schematic DiagrampukymottoNo ratings yet

- VoltmeterDocument1 pageVoltmeterMochammadPraditiaNo ratings yet

- Esque MaDocument1 pageEsque MaAlexander PerdomoNo ratings yet

- mcbstm32c Display Board SchematicsDocument1 pagemcbstm32c Display Board SchematicsMustafa AkdenizNo ratings yet

- NGX Parallel Port JtagDocument1 pageNGX Parallel Port JtagcaracobreNo ratings yet

- 5x5x5 5 FinalDocument1 page5x5x5 5 FinalIngLLimpiNo ratings yet

- DreDocument9 pagesDreFabian RodriguezNo ratings yet

- Sony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICDocument36 pagesSony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICvideoson0% (1)

- C1 Chem Lecture Seating Plan Feb 2014 v2Document4 pagesC1 Chem Lecture Seating Plan Feb 2014 v2Tang Voon HaoNo ratings yet

- Sony Vaio Mbx-126 - Quanta Je5.1Document36 pagesSony Vaio Mbx-126 - Quanta Je5.1nunoq171No ratings yet

- Location of Examination Halls: Venue CodeDocument2 pagesLocation of Examination Halls: Venue Codetaiiq zhouNo ratings yet

- Stok Filter SakuraDocument9 pagesStok Filter Sakuratyo yulianNo ratings yet

- Location of Examination Halls: Venue CodeDocument2 pagesLocation of Examination Halls: Venue Codetaiiq zhouNo ratings yet

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- P+5V P+5V: Power On MuteDocument8 pagesP+5V P+5V: Power On MuteuyrikNo ratings yet

- Iphone 4 Schematic FullDocument32 pagesIphone 4 Schematic FullRommyAnwar100% (1)

- Sym DS21448 BgaDocument1 pageSym DS21448 BgasahabatemanNo ratings yet

- NSCCL CM Ann MFDocument123 pagesNSCCL CM Ann MFSaumith DahagamNo ratings yet

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- Sélecteur Des Articles 880608284 30368910Document414 pagesSélecteur Des Articles 880608284 30368910TallaNiangNo ratings yet

- NSCCL CM Ann MFDocument132 pagesNSCCL CM Ann MFabhijeetNo ratings yet

- COD Nombre: Filtros de Aire KendallDocument34 pagesCOD Nombre: Filtros de Aire KendallMiguel PasteneNo ratings yet

- Osciloscopio Bs11-1Document1 pageOsciloscopio Bs11-1Abelardo PeironeNo ratings yet

- AircraftDocument7 pagesAircraftapi-196295964No ratings yet

- Motronic PinoutsDocument2 pagesMotronic Pinoutsaren_mendoza100% (1)

- Electronic Automotive Transmission Troubleshooter Nissan-Infinity VehiclesFrom EverandElectronic Automotive Transmission Troubleshooter Nissan-Infinity VehiclesNo ratings yet

- Banco Preguntas Prueba SaberDocument21 pagesBanco Preguntas Prueba SaberYulieth Valeria Sanchez CortesNo ratings yet

- Zeiss Erosion ModuleDocument13 pagesZeiss Erosion ModulepakhiddeyasNo ratings yet

- List of Coolers and HeatersDocument2 pagesList of Coolers and HeatersadityasahayNo ratings yet

- Uae CompanyDocument22 pagesUae Companykaushal kumarNo ratings yet

- 2020 - Comprehensive Electrochemical Impedance Spectroscopy Study of Si-BasedDocument12 pages2020 - Comprehensive Electrochemical Impedance Spectroscopy Study of Si-Basedary.engenharia1244No ratings yet

- According To 2021-22 Syllabus: Icse XDocument23 pagesAccording To 2021-22 Syllabus: Icse X39-Varshit TandekarNo ratings yet

- Substation Construction and CommissioningDocument83 pagesSubstation Construction and CommissioningShung Tak ChanNo ratings yet

- Homework 2 SolutionDocument5 pagesHomework 2 SolutiongretabunciNo ratings yet

- GO Price - escalation.GO - Ms.124.2007Document3 pagesGO Price - escalation.GO - Ms.124.2007hussainNo ratings yet

- Atlas FiltriDocument18 pagesAtlas FiltriCristi CicireanNo ratings yet

- DM NafithDocument5 pagesDM NafithialnabahinNo ratings yet

- LNG Easy Pvt. LTD: Pioneers of Small Scale LNG Distribution Through Virtual PipelineDocument49 pagesLNG Easy Pvt. LTD: Pioneers of Small Scale LNG Distribution Through Virtual PipelineAMIRNo ratings yet

- Topic 5: Darkroom Conditions For Radiographic Facilities: X-Ray Facility TipsDocument3 pagesTopic 5: Darkroom Conditions For Radiographic Facilities: X-Ray Facility TipsAmrina RosyadaNo ratings yet

- JannahAnthology Ramadan2023 FINALDocument39 pagesJannahAnthology Ramadan2023 FINALhiba ajuNo ratings yet

- SRF PresentationDocument28 pagesSRF PresentationSajeev KumarNo ratings yet

- Texi Post DD ErsatzteillisteDocument52 pagesTexi Post DD ErsatzteillisteJozsef TomoriNo ratings yet

- VIPER22ADocument21 pagesVIPER22AanawintaNo ratings yet

- ASHRAE-tables Lighting Power Density PDFDocument3 pagesASHRAE-tables Lighting Power Density PDFDan MolloyNo ratings yet

- 33 1rv18cv119 Umar BashirDocument10 pages33 1rv18cv119 Umar BashirUMARNo ratings yet

- Piping Info - Pipe Support Design GuidelinesDocument4 pagesPiping Info - Pipe Support Design GuidelinesSUSHANTBIJAM100% (1)

- Fortran CF DDocument160 pagesFortran CF DLahcen AkerkouchNo ratings yet

- 6-Büşra BahatDocument4 pages6-Büşra BahatAYŞE NURNo ratings yet

- DLL Science 9 JulyDocument10 pagesDLL Science 9 JulyMark Kiven MartinezNo ratings yet

- Test Bank For Chemistry 9th Edition Zumdahl Isbn 10 1133611095 Isbn 13 9781133611097Document17 pagesTest Bank For Chemistry 9th Edition Zumdahl Isbn 10 1133611095 Isbn 13 9781133611097Lynn Higgins100% (38)

- ACS600 MD Lifecycle Status Statement RevBDocument1 pageACS600 MD Lifecycle Status Statement RevBKichin_ANo ratings yet

- Design and Implementation of A Distributed IOT System in AquacultureDocument7 pagesDesign and Implementation of A Distributed IOT System in AquacultureAnun YuserboNo ratings yet

- 3b Domestic Water Meter Installation in Meter Room GuidelinesDocument10 pages3b Domestic Water Meter Installation in Meter Room GuidelinesVinish HARIDAS NAIRNo ratings yet

M2Ne PDF

M2Ne PDF

Uploaded by

Adriano MartinsOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

M2Ne PDF

M2Ne PDF

Uploaded by

Adriano MartinsCopyright:

Available Formats

A

+VCCP

U34A

H_ADSTB#1

18

18

18

H_A20M#

H_FERR#

H_IGNNE#

C2

D3

A3

18

18

5

18

H_STPCLK#

H_INTR

H_NMI

H_SMI#

C6

D1

D4

B4

CONTROL

IERR#

INIT#

RESET#

RS0#

RS1#

RS2#

TRDY#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB#1

HIT#

HITM#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

TCK

TDI

TD0

TMS

TRST#

DBR#

H_ADS#

H_BNR#

H_BPRI#

L4

H2

M2

H_DEFER#

H_DRDY#

H_DBSY#

N4

H_BR0#

H_INIT#

18,41

A4

B5

9

9

9

9

H_IERR#

J2

H_LOCK#

H_RS#0

H_RS#1

H_RS#2

H_RS#[2:0]

H_TRDY#

K3

K4

C8

B8

A9

C9

A10

B10

A13

C12

A12

C11

B13

A7

H_HIT#

9

H_HITM# 9

H_BPM0_ITP#

H_BPM1_ITP#

H_BPM2_ITP#

H_BPM3_ITP#

H_BPM4_PRDY#

H_BPM5_PREQ#

H_TCK

H_TDI

H_TDO

A15

STPCLK#

ITP_CLK1 A16

LINT0

ITP_CLK0 B14

LINT1

BCLK1 B15

SMI#

BCLK0

Banias-Processor-Skt_cooperspur

CLK_ITP_CPU#

CLK_ITP_CPU

CLK_CPUHCLK#

CLK_CPUHCLK

R383 +VCCP

150

5

R390

H_TDO

5

H_TMS

5

H_TRST# 5

TP57

H_PROCHOT#

PM_THRMTRIP#

R388

10K

+VCCP

TP2

TP7

TP5

TP3

TP61

TP58

H_TCK

ITP_DBRESET#

H_THERMDA

H_THERMDC

THERMTRIP#

P lace testpoint

o n H_IERR# with

a GND 0.1" away

H_CPURST#

B11

H1

K1

L2

M3

+VCCP

R382

54.9

C17

PROCHOT#

THERMDA

THERMDC

R379

56

9

9

B17

B18

A18

A20M#

FERR#

IGNNE#

H _ T D I pullup (R8001) must

b e p laced within 300ps of

C P U TDI pin (within 2")

56

U34B

H_D#[63:0]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

4

4

19

6

6

6

6

9

9

9

R387

10K

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

EVMC connections

C O M P 1 , C O M P3 should be routed as Zo=55ohm

t r a c es shorter than 0.5"

+VCCP

R266

Comp0

Comp1

Comp2

Comp3

9

9

9

H_DSTBN#1

H_DSTBP#1

H_DINV#1

1K_1%

R265

TP_GTLREF3

TP_GTLREF2

TP_GTLREF1

TP34

TP6

TP54

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

K24

L24

J26

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

DATA GRP 3

Layout note:

C O M P 0 a n d C OMP2 need to be Zo=27.4ohm traces.

B e s t e s t i m a t e i s 18mil wide trace for outer layers and

1 4 m i l i f o n internal layer. See RDDP of Banias.

T r a c e s s h o u l d b e shorter than 0.5". Refer to latest CS layout

H_DSTBN#0

H_DSTBP#0

H_DINV#0

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

C23

C22

D25

DATA GRP 2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

BR0#

LOCK#

ADDR GROUP1

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

R2

P3

T2

P1

T1

DEFER#

DRDY#

DBSY#

N2

L1

J3

AC1

G1

E26

AD26

GTLREF3

GTLREF2

GTLREF1

GTLREF0

A1

B2

0 .5" max length

NC0

NC1

2K_1%

R243

54.9_1%

R244

27.4_1%

R300

54.9_1%

R299

27.4_1%

TP4

TP59

TP1

R376

C14

C3

AF7

C16

E1

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

DATA GRP 0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

ADS#

BNR#

BPRI#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

DATA GRP 1

H_ADSTB#0

H_REQ#[4:0]

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB#0

ITP SIGNALS

9

9

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

AA3

Y3

AA2

U3

ADDR GROUP0

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

2,3,5,9,10,11,18,19,20,50

+VCCP

THERM

H_A#[31:3]

H CLK

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

PWRGOOD

SLP#

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

W25

W24

T24

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

AE24

AE25

AD20

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

P25

P26

AB2

AB1

B7

C19

E4

A6

H_DSTBN#2

9

H_DSTBP#2

9

H_DINV#2

9

CHK Banias w/ GL,

DPWR? need pull up?

H_DSTBN#3

9

H_DSTBP#3

9

H_DINV#3

9

+VCCP

Comp0

Comp1

Comp2

Comp3

PM_PSI#

330_*

H_DPSLP#

8,18

H_DPWR#

8

H_PWRGD

18

H_CPUSLP#

18

RSVD1

RSVD2 MISC

C5

TEST1

RSVD3

TEST1 F23 TEST2

RSVD4

TEST2

PSI#

Banias-Processor-Skt_cooperspur

PM_PSI#

330

R66

H_DPSLP#

R67

1K_*

44

R63

R380

1K_*

R389

1K_*

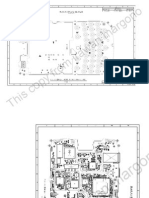

ASUS PROJECT:

A

REVISION

M2Ne

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

1

56

B

DESCRIPTION:

C

Dothan 1 of 2

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

U34D

A2

A5

A8

A11

A14

A17

A20

A23

A26

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

VSS0

VSS97 D15

VSS1

VSS98 D17

VSS2

VSS99 D19

VSS3

VSS100 D21

VSS4

VSS101 D23

VSS5

VSS102 D26

VSS6

VSS103 E3

VSS7

VSS104 E6

VSS8

VSS105 E8

VSS9

VSS106 E10

VSS10

VSS107 E12

VSS11

VSS108 E14

VSS12

VSS109 E16

VSS13

VSS110 E18

VSS14

VSS111 E20

VSS15

VSS112 E22

VSS16

VSS113 E25

VSS17

VSS114 F1

VSS18

VSS115 F4

VSS19

VSS116 F5

VSS20

VSS117 F7

VSS21

VSS118 F9

VSS22

VSS119 F11

VSS23

VSS120 F13

VSS24

VSS121 F15

VSS25

VSS122 F17

VSS26

VSS123 F19

VSS27

VSS124 F21

VSS28

VSS125 F24

VSS29

VSS126 G2

VSS30

VSS127 G6

VSS31

VSS128 G22

VSS32

VSS129 G23

VSS33

VSS130 G26

VSS34

VSS131 H3

VSS35

VSS132 H5

VSS36

VSS133 H21

VSS37

VSS134 H25

VSS38

VSS135 J1

VSS39

VSS136 J4

VSS40

VSS137 J6

VSS41

VSS138 J22

VSS42

VSS139 J24

VSS43

VSS140 K2

VSS44

VSS141 K5

VSS45

VSS142 K21

VSS46

VSS143 K23

VSS47

VSS144 K26

VSS48

VSS145 L3

VSS49

VSS146 L6

VSS50

VSS147 L22

VSS51

VSS148 L25

VSS52

VSS149 M1

VSS53

VSS150 M4

VSS54

VSS151 M5

VSS55

VSS152 M21

VSS56

VSS153 M24

VSS57

VSS154 N3

VSS58

VSS155 N6

VSS59

VSS156 N22

VSS60

VSS157 N23

VSS61

VSS158 N26

VSS62

VSS159 P2

VSS63

VSS160 P5

VSS64

VSS161 P21

VSS65

VSS162 P24

VSS66

VSS163 R1

VSS67

VSS164 R4

VSS68

VSS165 R6

VSS69

VSS166 R22

VSS70

VSS167 R25

VSS71

VSS168 T3

VSS72

VSS169 T5

VSS73

VSS170 T21

VSS74

VSS171 T23

VSS75

VSS172 T26

VSS76

VSS173 U2

VSS77

VSS174 U6

VSS78

VSS175 U22

VSS79

VSS176 U24

VSS80

VSS177 V1

VSS81

VSS178 V4

VSS82

VSS179 V5

VSS83

VSS180 V21

VSS84

VSS181 V25

VSS85

VSS182 W3

VSS86

VSS183 W6

VSS87

VSS184 W22

VSS88

VSS185 W23

VSS89

VSS186 W26

VSS90

VSS187 Y2

VSS91

VSS188 Y5

VSS92

VSS189 Y21

VSS93

VSS190 Y24

VSS94

VSS191

VSS95

VSS96

Banias-Processor-Skt_cooperspur

+VCORE

+VCORE

U34C

AA11

AA13

AA15

AA17

AA19

AA21

AA5

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC9

AD10

AD12

AD14

AD16

AD18

AD8

AE11

AE13

AE15

AE17

AE19

AE9

AF10

AF12

AF14

AF16

AF18

AF8

D18

D20

D22

D6

D8

E17

E19

E21

E5

E7

E9

F18

F20

F22

F6

F8

G21

G5

VCC0

VCC59 H22

VCC1

VCC60 H6

VCC2

VCC61 J21

VCC3

VCC62 J5

VCC4

VCC63 K22

VCC5

VCC64 U5

VCC6

VCC65 V22

VCC7

VCC66 V6

VCC8

VCC67 W21

VCC9

VCC68 W5

VCC10

VCC69 Y22

VCC11

VCC70 Y6

VCC12

VCC71

VCC13

F26

VCC14

VCCA0 B1

VCC15

VCCA1 N1

VCC16

VCCA2 AC26

VCC17

VCCA3

VCC18

D10

VCC19

VCCP0 D12

VCC20

VCCP1 D14

VCC21

VCCP2 D16

VCC22

VCCP3 E11

VCC23

VCCP4 E13

VCC24

VCCP5 E15

VCC25

VCCP6 F10

VCC26

VCCP7 F12

VCC27

VCCP8 F14

VCC28

VCCP9 F16

VCC29

VCCP10 K6

VCC30

VCCP11 L21

VCC31

VCCP12 L5

VCC32

VCCP13 M22

VCC33

VCCP14 M6

VCC34

VCCP15 N21

VCC35

VCCP16 N5

VCC36

VCCP17 P22

VCC37

VCCP18 P6

VCC38

VCCP19 R21

VCC39

VCCP20 R5

VCC40

VCCP21 T22

VCC41

VCCP22 T6

VCC42

VCCP23 U21

VCC43

VCCP24

VCC44

P23

VCC45

VCCQ0 W4

VCC46

VCCQ1

VCC47

E2

VCC48

VID0 F2

VCC49

VID1 F3

VCC50

VID2 G3

VCC51

VID3 G4

VCC52

VID4 H4

VCC53

VID5

VCC54

VCC55

AE7

VCC56

VCCSENSE

VCC57

AF6

VCC58

VSSSENSE

Banias-Processor-Skt_cooperspur

+VCORE

3,39,44

1

+V1.8S_PROC

+V1.8S_PROC_VCCA1

+V1.8S_PROC_VCCA2

+V1.8S_PROC_VCCA3

+VCCP

+VCCP

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

RN18

RN19

RN20

1

3

1

3

1

3

TP_VSSSENSE

VR_VID0

VR_VID1

VR_VID2

VR_VID3

VR_VID4

VR_VID5

44

44

44

44

44

44

R246

54.9_1%_*

54.9_1%_*

F O R B A N I A S BO , NO STUFF VCCA1, VCCA2, VCCA3

+V1.8S

+V1.8S_PROC_VCCA1

51

R401

Banias VID values

VID0 VID1 VID2 VID3 VID4 VID5

0

1

1

0

1

0

0

1

1

0

0

1

0

0

1

1

0

1

0

1

0

0

1

1

0

1

1

0

1

1

0

0

1

1

1

1

0

C401

C395

1.356V

1.100V

1.004V

0.908V

0.844V

0.748V

0805

10U_0805

0.01UF

+V1.8S

R370

+V1.8S_PROC

+V1.8S_PROC_VCCA2

R31

C391

C62

0805

C392

+V1.5S

C75

0805

10U_0805

R371

10U_0805

0.1UF

0.01UF

0_*

+V1.8S_PROC_VCCA3

R283

LAYOUT NOTE: Provide a test point with no

stub to connect differential probe between

VCCSENSE and VSSSENSE at the location

where the two 54.9ohm resistors terminate

the 55ohm tramission lines.

0

C314

C313

8,10,11,16,18,19,20,21,51

0805

10U_0805

0.01UF

REVISION

M2Ne

2 0_2R4P

4

2 0_2R4P

4

2 0_2R4P

4

TP_VCCSENSE

R245

+V1.5S

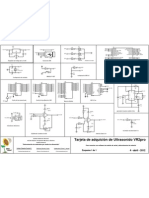

ASUS PROJECT:

1,3,5,9,10,11,18,19,20,50

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

2

56

B

DESCRIPTION:

C

Dothan 2 of 2

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

+VCORE

+VCCP

+VCCP

7343

7343

7343

1,2,5,9,10,11,18,19,20,50

+

+

C94

1uF/10V

C11

470U/4V_7343_*

C293

330U/4V_7343_*

C107

1uF/10V

C95

1uF/10V

C108

1uF/10V

C96

1uF/10V

C109

1uF/10V

C53

1uF/10V

C86

1uF/10V

C87

330U/4V_7343

C49

470U/4V_7343

+VCCP

+V2.5

+V1.35S

+V2.5

C ONNECT GND AND GND_SIGNAL

C497

0.1U

+VCORE

C291

0805

C451

0.1U

C531

0.1U

C529

0.1U

C290

0805

10U_0805

10U_0805

CROSS_POWER_PLANE_BOTH_SIDE

G10

C646

C647

0805

C648

0805

C649

0805

C650

0805

0805

C357

C367

0805

0805

C341

0805

10U_0805

10U_0805

10U_0805

10U_0805

10U_0805

10U_0805

10U_0805

10U_0805

C358

C368

C359

C369

C337

C292

C338

C342

HOLE-D

G3

0805

0805

0805

0805

0805

0805

0805

10U_0805

10U_0805

10U_0805

10U_0805

10U_0805

10U_0805

C286

C56

C47

C325

C285

C283

C42

C90

0805

0805

0805

10U_0805

10U_0805

10U_0805

10U_0805

C330

C331

C82

C41

0805

10U_0805

G6

G5

PTH

PTH

G2

10U_0805

0805

0805

10U_0805

0805

10U_0805

0805

10U_0805

0805

10U_0805

C339

C343

0805

10U_0805

0805

10U_0805

G9

HOLE-A

HOLE-B

G11

HOLE-B

G12

HOLE-B

G17

HOLE-B

G14

HOLE-B

10U_0805

G16

C324

HOLE-A

0805

10U_0805

0805

G8

10U_0805

0805

HOLE-A

0805

10U_0805

0805

G4

HOLE-A

C323

0805

10U_0805

HOLE-B

G15

HOLE-B

G13

HOLE-B

C329

0805

10U_0805

10U_0805

G1

HOLE-B

G7

HOLE-B

G18

PTH

ASUS PROJECT:

A

REVISION

M2Ne

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

3

56

B

DESCRIPTION:

C

CPU-CAP & HOLE

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

+3VS

Route H_THERMDA,

H_THERMDC on same

l ayer, 10 mil width, 5

mil between on a 12

mil spacing

C651

R655

10K_*

R656

10K

FAN_PWM

FAN_SPD

R657

0_402_*

R64

22 OS#_OC

PWMOUT

OS#_OC_C

TACH/AIN

0_402

THERM#

0.1U

U10

VCC

R654

10K_*

SCL

A DM1030

SDA

INT#

D+

FANFAULT#

SMBCK_3S

6,7,14,33

15

SMBDA_3S

6,7,14,33

14

PM_THRM#

19

10

H_THERMDA

H_THERMDC

NC

NC

NC

NC

ADD

GND

D-

16

3

4

11

12

13

5

ADM1030_*

C130

2

2200P

+3VS

SM Bus Address fix at:

1001 100x (98, 99),

Resolution : +/- 1

degree

+5VS

DXP

ALERT#

DXN

OS#_OC_C

H_THERMDA

H_THERMDC

10UF/6.3V_1206

OVERT

SMBDATA

10UF/6.3V_1206

C734

10UF/6.3V_1206

C735

C736

2

PM_THRM#

SMBCLK

SMBDA_3S

GND

SMBCK_3S

VCC

U8

MAX6657

3

R425

100K

(0603)

L68

+5VS

R135

+5VS_FAN

(0402)

47K_402

U42

3

47K_402

6

Q62

R434

1K_402

1

2

5 3

CN-3_FAN

10K_402

R663

0

(0603)

FAN_SPD

37,39

GND_FAN

-A

Q63

5

2N7002

39 FAN_DA1

C420

0603

0.1U

OUTA

CN26

80/2A

+B

OUTB

-B

R658

0_402

V-

V+

1K

1

NDS351NS

(0603)

+5VS

C427

1U

8

0402

(0402)

R443

LMV393

0603

(0402)

R136

+A

10K_402

R442

47K_402

R132

(0402)

R133

(0402)

(0402)

FAN

0805

C426

0.1U_402

+5VS

R659

D22

0_402_*

22 OS#_OC

3

RB717F

D35

(0402)

FAN_PWM

RB717F

0_*

R660

0_402_*

R759

R142

(0402)

19 PM_THRM#

+3VS

Q32

39 WATCHDOG

2N7002

(0402)

1

R764

10K_402

48 OTP#_P

ASUS PROJECT:

A

REVISION

M2Ne

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

4

56

B

DESCRIPTION:

C

FAN & THERMAL SENSOR

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

+5V

PCMCIA DEBUG

PORT

+VCCP

U22

VCC

1,2,3,9,10,11,18,19,20,50

+VCCP

H_TDO

R384

54.9/1%

H_TMS

R381

39.2/1%

H_TRST#

R385

680

H_TCK

R386

27.4/1%

6

CLK_DEBUG

19,41 LFRAME#

19,37,39,41 LAD0

19,37,39,41 LAD1

19,37,39,41 LAD2

19,37,39,41 LAD3

41 D IS_SYSBIOS#_FWH

CBDEBUGEN#

27,43 CBDEBUGEN#

NMI

NMI#/SMI#

3

4

7

8

11

14

17

18

21

22

1

13

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

BEA#

BEB#

3384

B0

B1

B2

B3

B4

B5

B6

B7

B8

B9

GND

24

+5V

2

5

6

9

10

15

16

19

20

23

CLKRUN#/IOIS16#

26,28

C A U D I O/SPKR_IN#/BVD2

CPERR#/A14

26,28

RFU/D2

26,28

RFU/D14

26,28

RFU/A18

26,28

CSERR#/WAIT#

26,28

CBLOCK#/A19

26,28

23,27,29,34,35,39,43,47,51

26,28

12

2

R181

0_402_*

(0402)

+5VS

+5VS

F W H test connector

f o r first version

4 , 1 1 , 1 6 , 2 0,22,23,24,25,29,31,32,33,35,37,38,39,42,43,48,51

R85

10K_*

H_NMI

+3VS

+3VS

C104

0.1uF

41 CLK_DEBUGPCI

2

4

6

8

10

12

1

3

5

7

9

11

2

1

4

3

6

5

8

7

10

9

12

11

CN-12(LPC_DEBUG_*)

+3VS

R84

NMI

DIS_SYSBIOS#

4 , 6 , 7 , 8 , 1 0 , 1 4 , 1 7,20,21,22,23,25,26,31,32,33,35,36,37,38,39,40,41,43,51

NMI

R108

0

1

Q27

2N7002_*

R107

10K_*

LAD0

LAD1

LAD2

LAD3

LFRAME#

10K_*

C105

0.1uF_*

3

CN15

NMI_ICH

18

D IS_SYSBIOS#_FWH

Q26

2N7002_*

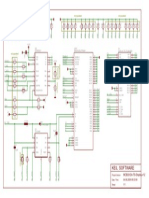

ASUS PROJECT:

A

REVISION

M2Ne

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

5

56

B

DESCRIPTION:

C

DEBUG PORT

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

+3VS

+3VS

L26

80/2A_0805

+3VS_CLK

CT2

0402

C158

CT1

0805

0402

0.01U_402

C142

C146

0402

0.01U_402

0.01U_402

C153

0402

0805

10U_0805

10U_0805

0402

0.01U_402

C388 0402

C143 0402

C154 0402

C148

0.01U_402

0.01U_402

0.01U_402

0.01U_402

X2

1

U39

R347

33

CLK_SIO14

37

R357

33

CLK_ICH14

19

0_402

C127

14.318MHZ_PAD177A

C138

15p

15p

X1_CKGEN

X2_CKGEN

3

4

C131

18

5P_*

CLK_ICHPCI

R360

R367

CLK_DEBUG

33/1%

FS3

33/1%

FS4

TP56

7

8

+3VS_CLK

C141

41

5P_*

R368

10K

CLK_FWHPCI

R372

33/1%

10

29

CLK_LANPCI

R377

33/1%

11

C145

5P_*

26

CLK_CBPCI

R378

33/1%

12

C150

5P_*

39

R395

33/1%

13

C144

5P_*

CLK_KBCPCI

14

15

C149

C152

31

5P_*

37

5P_*

CLK_MINIPCI

CLK_SIOPCI

R394

33/1%

16

R398

33/1%

17

VTT_PWRGD#

7,19,43

18

R112

SUSA#_3

L64

+3VS

L_0603

0_402

19

(0402)

+3VS_CLKA

20

21

19

R114

PCI_STP#_3

0_402

22

(0402)

23

24

C403

5P_*

18 CLK_ICHHUB

C408

5P_*

CLK_MCH66

R405

33/1% CLK_R_ICHHUB

25

R408

33/1%

26

CLK_R_MCH66

27

4,7,14,33

R111

SMBCK_3S

CT9

C394

0.01U

FS0

R74

1K_*

FS1

R69

1K_*

FS2

R113

R100

28

VDDREF

REF0

X1

FS1

X2

FS0

GND

CPU_STOP#

FS3/PCICLK_F0

CPUCLK0/FS6

FS4/PCICLK_F1

CPUCLK0#/FS5

ASEL/PCICLK_F2

VDDCPU

VDDPCI

CPUCLK1

GND

CPUCLK1#

MULTSEL0/PCICLK0

GND

MODE/PCICLK1

VDDCPU

PCICLK2

CPUCLK2

PCICLK3

CPUCLK2#

VDDPCI

IREF

GND

GND

PCICLK4

FS2

PCICLK5

VID5

VTT_PWRGD#

VID4

PD#

VID3

VDDA

VID2

GND

VID1

PCI_STOP#

VID0

VDD3V66

VDD48

GND

GND

3V66_0

48MHZ_0

3V66_1

48MHZ_1

3V66_2

SDATA

SCLK

3V66_3/48MHZ_2

56

55

FS1

R199

54

FS0

R201

(0402)

0_402

(0402)

53

52

CLK_R_ITP_CPU

51

CLK_R_ITP_CPU#

R553

CG_FS1

19

CG_FS0

0_402

19

(0402)

R358

CPU_STP#_3

33/1%

R366

C386

R83

19

33/1% R356

49.9/1%

R361

49.9/1%

50

49

CLK_R_CPUHCLK

R374

33/1%

48

CLK_R_CPUHCLK#

R392

33/1% R369

49.9/1%

R391

49.9/1%

47

10P_*

C387

R89

0_402_*

(0402)

CLK_ITP_CPU

CLK_ITP_CPU#

0_402_*

(0402)

CLK_CPUHCLK

10K_*

19

CG_FS5

19

CLK_CPUHCLK#

45

CLK_R_GMCHHCLK

R397

33/1%

44

CLK_R_GMCHHCLK#

R400

33/1% R396

49.9/1%

CLK_GMCHHCLK

R399

49.9/1%

43

R109

CLK_GMCHHCLK#

475/1%

42

FS2

41

R117

0_402

near CLK Gen.

(0402)

40

39

CG_FS2

19

38

37

36

35

34

33

32

R402

33

CLK_ICH48

19

31

R406

33

CLK_DREF

30

R110

29

R412

22

0_402

C399

SMBDA_3S 4,7,14,33

SSC_CLK_IN

7

(0402)

5P_*

C402

C406

5P_*

5P_*

FS3 Internal Pull-up

FS4,5,6, ASEL Internal

Pull- Down

56PIN TSSOP

+3VS

1K

CG_FS6

1

46

10U_0805

+3VS

10P_*

0805

FS3

FS4

0_402

(0402)

ICS950815

FS4

FS3

FS2

FS1

FS0

0

1

0

0

1

1

1

0

0

0

0

0

100

200

66

66

33

33

133

66

33

66Buf[2:0]

+3VS

PCI_F

R345

10K

R72

1K

VTT_PWRGD#

3

CPU(MHZ)

R649

1K

R344

1K

R75

1K

R70

1K

R115

1K_*

8,19,22,44

VRM_PWRGD

R71

R77

20K

Q58

2N3904

R78

44 CLK_EN#

ASUS PROJECT: M2Ne

A

REVISION

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

6

56

B

DESCRIPTION:

C

CLOCK GEN.

0_*

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

+3VS

C384

0.1U_*

C374

1U_*

U11

T R A CE_LENGH->1"~4"

SSC_CLK_IN

6 SSC_CLK_IN

1

2

R61

0_402

3

(0402)

8

R60

DREFSSCLK

33_*

DREFSSCLK_D

CLKIN

PD#

VDD

SCLK

GND

SDATA

CLKOUT

48MHZ

R106

R105

6

5

R104

R101

0_402_*

(0402)

(0402)

(0402)

SUSA#_3

0_402_*

R510

0_402_*

R511

10K_*

0_402_*

(0402)

0_402_*

(0402)

+3VS

SMBCK_3S

LCLKCTLA

SMBDA_3S

LCLKCTLB

6,19,43

4,6,14,33

8

4,6,14,33

8

3

T R ACE_LENGH->1"~7"

ICS91718_*

R59

10K_*

The distance between CS91718 and Clock

Gen: 1000 mil<L< 4000 mil

ASUS PROJECT: M2Ne

A

REVISION

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

7

56

B

DESCRIPTION:

C

CLOCK GEN.

SCHEMATIC FILE NAME : <Doc>

LIBRARY DATE :

D

DESIGN ENGINEER :

E

SMA_B1

SMA_B2

SMA_B4

SMA_B5

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_BA0

SM_BA1

SM_RAS#

SM_CAS#

SM_WE#

SM_CMDCLK0

SM_CMDCLK#0

SM_CMDCLK1

SM_CMDCLK#1

SM_CMDCLK2

SM_CMDCLK#2

SM_CMDCLK3

SM_CMDCLK#3

SM_CMDCLK4

SM_CMDCLK#4

SM_CMDCLK5

SM_CMDCLK#5

SM_DM0

SM_DM1

SM_DM2

SM_DM3

SM_DM4

SM_DM5

SM_DM6

SM_DM7

SM_DM8

SM_RCVENOUT#

SM_RCVENIN#

SMRCOMP

11,12,13,14

AJ24

SM_VREF_DDR

C463

0.1U

SM_VREF

SMVSWINGL

SMVSWINGH

SM_DQS0

SM_DQS1

SM_DQS2

SM_DQS3

SM_DQS4

SM_DQS5

SM_DQS6

SM_DQS7

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

SM_MAA0

SM_MAA1

SM_MAA2

SM_MAA3

SM_MAA4

SM_MAA5

SM_MAA6

SM_MAA7

SM_MAA8

SM_MAA9

SM_MAA10

SM_MAA11

SM_MAA12

SM_DQS[0:8]

AD16

AC12

AF11

AD10

SM_MAB1

SM_MAB2

SM_MAB4

SM_MAB5

SM_MAB1

SM_MAB2

SM_MAB4

SM_MAB5

12,13,15

12,13,15

12,13,15

12,13,15

AC7

AB7

AC9

AC10

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

14,15

14,15

12,15

13,15

AD23

AD26

AC22

AC25

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

14,15

14,15

12,15

13,15

AD22

AD20

SM_BS0

SM_BS1

SM_BS0

SM_BS1

12,13,15

12,13,15

AC21

AC24

AD25

SM_RAS#

SM_CAS#

SM_WE#

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

R478

R477

R429

R426

R476

R475

R474

R473

R432

R431

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

SM_DM0

SM_DM1

SM_DM2

SM_DM3

SM_DM4

SM_DM5

SM_DM6

SM_DM7

MCH_SMRCOMP

AJ22

AJ19

MCH_SMVSWINGL

MCH_SMVSWINGH

SM_DQS[0:8]

SM_MAA[0:12]

SM_DM[0:8]

SM_DM[0:8]

SM_DQ[0:63]

SM_DQ[0:63]

15

12,13,14,15

15

U43C

15

R3

R5

R6

R4

P6

P5

N5

P2

N2

N3

M1

M5

R454

100K

P3

P4

T6

T5

L2

M2

R450

R453

100K

100K

G2

M3

+V1.5S

K5

K1

K3

K2

J6

J5

H2

H1

H3

H4

H6

G3

+V1.5S

14

14

14

14

14

14

12,13

12,13

12,13

12,13

RP2

5

1

2

3

4

R151

100K

6

7

8

9

2.2K-10P8R

+V1.5S

E5

F5

E3

E2

G5

F4

G6

F6

L7

D5

R148

1K

R447

1K_1%

ADDDETECT

19

DPMS_CLK

F1

NEAR_NB

R146

19,21 AGP_BUSY#

R452

1K_1%

C455

0.1U

R451

40.2_1%

CLK_MCH66

TP73

MONTARA_GMCH_B

C202

5P_*

+V2.5

+V2.5

R471

60.4_1%

+V1.5S

R444

R440

R441

+V2.5

R458

604_1%

MCH_SMRCOMP

J3

J2

K6

L5

L3

H5

K7

N6

N7

M6

P7

T7

10

+V1.5S

TP10

TP9

AB1

3,10,11,12,13,14,49,50

2,10,11,16,18,19,20,21,51

SM_MAA[0:12]

SM_RAS# 12,13,15

SM_CAS# 12,13,15

SM_WE#

12,13,15

0

SM_CLK_DDR0

CLK_DCLK0

0

SM_CLK_DDR#0

CLK_DCLK0#

0

SM_CLK_DDR1

CLK_DCLK1

0

SM_CLK_DDR#1

CLK_DCLK1#

SM_CLK_DDR2

0

CLK_DCLK2

0

SM_CLK_DDR2#

CLK_DCLK2#

0

SM_CLK_DDR3

CLK_DCLK3

0

SM_CLK_DDR#3

CLK_DCLK3#

0

SM_CLK_DDR4

CLK_DCLK4

0

SM_CLK_DDR#4

CLK_DCLK4#

SM_CLK_DDR5

TP74

SM_CLK_DDR#5

TP77

AC15

AC16

+V2.5

+V1.5S

MCH_SMVSWINGL

R462

150_1%

MCH_SMVSWINGH

1K_*

1K_*

1K_*

TP65

+3VS

F7

D1

Y3

AA5

F2

F3

B2

B3

C2

C3

C4

D2

D3

D7

L4

DVOBD0

DVOBD1

DVOBD2

DVOBD3

DVOBD4

DVOBD5

DVOBD6

DVOBD7

DVOBD8

DVOBD9

DVOBD10

DVOBD11

DAC

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

+V2.5

+V1.5S

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

REFSET

DVOBCLK

DVOBCLK#

DVOBHSYNC

DVOBVSYNC

DVOBBLANK#

DVOBFLDSTL

DVOBCINTRB

DVOBCCLKINT

DVOCD0

DVOCD1

DVOCD2

DVOCD3

DVOCD4

DVOCD5

DVOCD6

DVOCD7

DVOCD8

DVOCD9

DVOCD10

DVOCD11

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

HSYNC

VSYNC

DDCACLK

DDCADATA

LVDS

SM_SDQS0

SM_SDQS1

SM_SDQS2

SM_SDQS3

SM_SDQS4

SM_SDQS5

SM_SDQS6

SM_SDQS7

SM_SDQS8

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

LVREFH

LVREFL

MI2CCLK

MI2CDATA

MDVICLK

MDVIDATA

MDDCCLK

MDDCDATA

ADDID0

ADDID1

ADDID2

ADDID3

ADDID4

ADDID5

ADDID6

ADDID7

ADDDETECT

DPMS

GVREF

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM3

IYBP0

IYBP1

IYBP2

IYBP3

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

DVOCCLK

DVOCCLK#

DVOCHSYNC

DVOCVSYNC

DVOCBLANK#

DVOCFLDSTL

LVBG

LIBG

CLKS

SM_SDQ0

SM_SDQ1

SM_SDQ2

SM_SDQ3

SM_SDQ4

SM_SDQ5

SM_SDQ6

SM_SDQ7

SM_SDQ8

SM_SDQ9

SM_SDQ10

SM_SDQ11

SM_SDQ12

SM_SDQ13

SM_SDQ14

SM_SDQ15

SM_SDQ16

SM_SDQ17

SM_SDQ18

SM_SDQ19

SM_SDQ20

SM_SDQ21

SM_SDQ22

SM_SDQ23

SM_SDQ24

SM_SDQ25

SM_SDQ26

SM_SDQ27

SM_SDQ28

SM_SDQ29

SM_SDQ30

SM_SDQ31

SM_SDQ32

SM_SDQ33

SM_SDQ34

SM_SDQ35

SM_SDQ36

SM_SDQ37

SM_SDQ38

SM_SDQ39

SM_SDQ40

SM_SDQ41

SM_SDQ42

SM_SDQ43

SM_SDQ44

SM_SDQ45

SM_SDQ46

SM_SDQ47

SM_SDQ48

SM_SDQ49

SM_SDQ50

SM_SDQ51

SM_SDQ52

SM_SDQ53

SM_SDQ54

SM_SDQ55

SM_SDQ56

SM_SDQ57

SM_SDQ58

SM_SDQ59

SM_SDQ60

SM_SDQ61

SM_SDQ62

SM_SDQ63

SM_SDQ64

SM_SDQ65

SM_SDQ66

SM_SDQ67

SM_SDQ68

SM_SDQ69

SM_SDQ70

SM_SDQ71

DDR SYSTEM MEMORY

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

E8

16

16

16

HSYNC

VSYNC

16

16

DAC_REFSET

R147

137/1%

DDC2BC

16

DDC2BD

16

B6

G9

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

R420

0_*

R418

0_*

R144

0_*

R141

0_*

B4

C5

TP67

TP66

G8

F8

A5

TP72

L1_TX0L1_TX1L1_TX2-

17

17

17

L1_TX0+

L1_TX1+

L1_TX2+

17

17

17

L1_TXACL1_TXAC+

17

17

LCD_ENBACK

LCD_ENVDD

36

17

D12

F12

B12

A10

R428

B7

B17

H9

C6

1.5K_1%

CLK_DREF

6

DREFSSCLK

7

LCLKCTLA 7

LCLKCTLB 7

LCLKCTLB

+3VS

DPWR#

DPSLP#

RSTIN#

PWROK

AGPBUSY#

EXTTS0

MCHDETECTVSS

GRCOMP

66IN

RVSD0

RVSD1

RVSD2

RVSD3

RVSD4

RVSD5

RVSD6

RVSD7

RVSD8

RVSD9

RVSD10

RVSD11

C9

D9

C8

D8

A7

A8

H10

J9

TP64

MISC

U43B

SM_DQ0

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

NC

DVO

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

AA22

Y23

AD28

H_DPWR#

1

H_DPSLP#

1,18

PCIRST#_ICH

18

J11

VRM_PWRGD

R149

6,19,22,44 10K_1%

D6

AJ1

R479

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

TP69

TP79

TP8

TP78

TP62

TP70

TP60

TP63

TP68

TP71

TP75

TP76

MONTARA_GMCH_C

C484

0.1U

R433

R470

60.4_1%

C464

0.1U

R457

150_1%

C465

0.1U

1K_* LCLKCTLB

R461

604_1%

RSVD5,6,7, LCLKCTLB

RESERVE FOR STRAPPING

F or M-GM + Banias mount RA,

For M-GML + P4 no RA

NEAR_NB

NEAR_NB

ASUS PROJECT:

A

REVISION

M2Ne

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

8

56

B

NEAR_NB

DESCRIPTION:

C

SCHEMATIC FILE NAME : <Doc>

Montara-GME (1 of 4) LIBRARY DATE :

D

DESIGN ENGINEER :

E

+VCCP

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

R416

301/1%

R413

150/1%

MCH_HYSWING

R415

150/1%

MCH_HXSWING

C413

0.1U

C409

0.1U

NEAR_NB

M C H _HYSWING, MCH_HXSWING, MCH_HYRCOMP, MCH_HXRCOMP

TRACE: SPACE=10:20

2

1

1

1

1

1

1

1

+VCCP

R138

49.9/1%

R421

49.9/1%

MCH_HCCVREF

R150

49.9/1%

MCH_HAVREF

R139

100/1%

NEAR_NB

R143

100/1%

R424

100/1%

1

1

1

1

1

1

1

1

1

1

1

1

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

J28

C27

E22

D18

K27

D26

E21

E18

J25

E25

B25

G19

H_CPURST#

F15

NEAR_NB

HUB0

HUB1

HUB2

HUB3

HUB4

HUB5

HUB6

HUB7

HUB8

HUB9

HUB10

HUB_PSTRB

HUB_PSTRB#

HUB_HLZCOMP

MCH_PSWING

MCH_LVREF

MCH_HCCVREF

MCH_HAVREF

C419

0.1U

C417

1U

C168

1U

18

C179

0.1U

HUB[0:10]

+V1.35S

NEAR_NB

18 HUB_PSTRB

18 HUB_PSTRB#

+V1.35S

+V1.35S

R455

68.1/1%

R465

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB0#

H_ADSTB1#

37.4/1%

C468

0.1U

R466

287/1%

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HOST

HCLK#

HCLK

HYRCOMP

HYSWING

HXRCOMP

HXSWING

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DINV#0

DINV#1

DINV#2

DINV#3

H_CPURST#

K21

J21

J17

Y28

Y22

C163

0.1U

H_D#[0:63]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AD29

AE29

H28

K28

B20

B18

MCH_HYRCOMP

MCH_HYSWING

MCH_HXRCOMP

MCH_HXSWING

MCH_HDVREF

C162

1U

P23

T25

T28

R27

U23

U24

R24

U28

V28

U27

T27

V27

U25

V26

Y24

V25

V23

W25

Y25

AA27

W24

W23

W27

Y27

AA28

W28

AB27

Y26

AB28

R28

P25

R23

R25

T23

T26

AA26

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

6 CLK_GMCHHCLK#

6 CLK_GMCHHCLK

R410

27.4/1%

R409

27.4/1%

MCH_HDVREF

U43A

H_A#[3:31]

H_A#[3:31]

R414

301/1%

HDVREF0

HDVREF1

HDVREF2

HCCVREF

HAVREF

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HUB_PSTRB

HUB_PSTRB#

HLZCOMP

PSWING

HUB_LVREF

MONTARA_GMCH_A

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BREQ0#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

HUB I/F

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

H_D#[0:63]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

H_RS#0

H_RS#1

H_RS#2

1

1

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

C472

0.01U

NEAR_NB

MCH_PSWING

C467

0.1uF

MCH_LVREF

R460

100/1%

NEAR_NB

ASUS PROJECT:

A

R464

100/1%

C473

0.1uF

REVISION

2.2

+V1.35S

+VCCP

1,2,3,5,10,11,18,19,20,50

+V1.35S

3,10,11,50

5

MCH_PSWING

VOLTAGE=0.8V+-8%

NEAR_NB

M2Ne

+VCCP

MCH_LVREF

VOLTAGE=0.35V+-8%

DATE: Tuesday, January 06, 2004

SHEET

OF

9

56

B

DESCRIPTION:

C

SCHEMATIC FILE NAME : <Doc>

Montara-GME (2 of 4) LIBRARY DATE :

D

DESIGN ENGINEER :

E

VSS

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

T16

AA16

AE16

A17

D17

H17

N17

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

+V1.35S

+VCCP

U43E

J15

P13

T13

N14

R14

U14

P15

T15

AA15

N16

R16

U16

P17

T17

AA17

AA19

W21

H14

+V1.35S

L65

V1

Y1

W5

U6

U8

W8

V7

V9

+V1.2S_HPLL

0.82UH

CT10 3528 +

22uF/10V

C397

0.1U

+V1.35S

D29

Y2

+V1.2S_DPLLA

+V1.2S_DPLLB

C204

0.1U

E1

J1

N1

E4

J4

M4

E6

H7

J8

L8

M8

N8

R8

K9

M9

P9

+V1.35S

L67

10UH_0805

7343

+V1.2S_DPLLA

CT14

220uF/2.5V-7343

A6

B16

C423

0.1U

+V1.5S

+V1.35S

L66

10UH_0805

7343

CT12

220uF/2.5V-7343

A9

B9

B8

+V1.2S_DPLLB

A11

B11

+

C411

0.1U

G13

B14

J13

B15

+V2.5

F9

B10

D10

A12

0805

R422

0-0805

+3VS

A3

A4

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCCHL0

VCCHL1

VCCHL2

VCCHL3

VCCHL4

VCCHL5

VCCHL6

VCCHL7

POWER

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCAHPLL

VCCAGPLL

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCADPLLA

VCCADPLLB

VCCDVO_0

VCCDVO_1

VCCDVO_2

VCCDVO_3

VCCDVO_4

VCCDVO_5

VCCDVO_6

VCCDVO_7

VCCDVO_8

VCCDVO_9

VCCDVO_10

VCCDVO_11

VCCDVO_12

VCCDVO_13

VCCDVO_14

VCCDVO_15

VCCADAC0

VCCADAC1

VSSADAC

VCCALVDS

VSSALVDS

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCDLVDS3

VCCTXLVDS0

VCCTXLVDS1

VCCTXLVDS2

VCCTXLVDS3

VCCQSM0

VCCQSM1

VCCGPIO_0

VCCGPIO_1

VCCASM0

VCCASM1

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

A22

A24

H29

M29

V29

C396

0.1U

C412

0.1U

AC1

AG1

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

C398

0.1U

C405

0.1U

C416

0.1U

+V2.5

C482

0805

10U_0805

C483

0.1U

+V2.5

AJ6

AJ8

+V2.5_QSM

R472

AD1

AF1

+V1.35S

0805

+V1.2S_ASM

0-0805

0805

R486

0-0805

MONTARA_GMCH_E

C424

0.1U

CT19

6032

C493

0.1U

100UF/2V_7343

AJ26

T9

L6

E28

D28

C22

AJ20

AJ18

AJ12

AJ10

AA29

W29

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

C1

G1

L1

U1

AA1

AE1

R2

AG3

AJ3

D4

G4

K4

N4

T4

W4

AA4

AC4

AE4

B5

U5

Y5

Y6

AG6

C7

E7

G7

J7

M7

R7

AA7

AE7

AJ7

H8

K8

P8

T8

V8

Y8

AC8

E9

L9

N9

R9

U9

W9

AB9

AG9

C10

J10

AA10

AE10

D11

F11

H11

AB11

AC11

AJ11

J12

AA12

AG12

A13

D13

F13

H13

N13

R13

U13

AB13

AE13

J14

P14

T14

AA14

AC14

D15

H15

N15

R15

U15

AB15

AG15

F16

J16

P16

MONTARA_GMCH_D

U43D

1

ASUS PROJECT:

A

REVISION

M2Ne

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

10

56

B

DESCRIPTION:

C

SCHEMATIC FILE NAME : <Doc>

Montara-GME (3 of 4) LIBRARY DATE :

D

DESIGN ENGINEER :

E

+V1.35S

C194

C188

0805

0805

10U_0805

+5VS

C171

0805

10U_0805

C176

0.1U

C201

0.1U

C192

0.1U

C180

0.1U

C167

0.1U

C165

0.1U

C166

0.1U

C169

0.1U

C400

0.1U

C164

0.1U

C190

0.1U

10U_0805

+5V

+VCCP

7343

R767

R768

0_*

+ CT11

220uF/2.5V-7343

+V2.5

7343

+ CT17

C200

0.1U

C220

0.1U

C454

0.1U

C469

0.1U

C477

0.1U

C487

0.1U

C474

0.1U

C471

0.1U

C178

0.1U

C195

0.1U

C462

0.1U

C450

0.1U

C418

0.1U

C193

0.1U

C187

0.1U

C422

0.1U

C415

0.1U

C414

0.1U

+V2.5

330uF/4v-7343

U20

R169

10K_1%

1

2

+V2.5_DIV

TLV2471

1OUT

VDD

+V1.5S

GND

1IN+

U-tlv2471

R170

10K_1%

3528

1IN-

R174

+1.25VREF_OP

CT16 3528 +

33uF/10V

3528 +

CT15

33uF/10V

CT13

47uF/6.3V

0

SM_VREF_DDR

8,12,13,14

ASUS PROJECT: M2Ne

A

REVISION

2.2

DATE: Tuesday, January 06, 2004

SHEET

OF

11

56

B

DESCRIPTION:

C

SCHEMATIC FILE NAME : <Doc>

Montara-GME (4 of 4) LIBRARY DATE :

D

DESIGN ENGINEER :

E

8,11,13,14

SM_VREF_DDR

8,15

SM_CS#2

R456

0_402

8,15

49

21

22

23

24

SM_DQS_R0

SM_DQS_R1

51

16

SM_BS0

SM_BS1

26

27

SM_CS#2_OB

(0402)

8,13,15

8,13,15

SM_VREF_DDR

SM_WE#

SM_CAS#

SM_RAS#

SM_BS0

SM_BS1

44

45

46

SM_CKE2

8,13 CLK_DCLK3

8,13 CLK_DCLK3#

SM_DM_R0

SM_DM_R1

R157

47

20

+V2.5

120

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

VREF

WE#

CAS#

RAS#

CS#

UDQS

LDQS

BA0

BA1

CKE

CLK

CLK#

U47

UDM

LDM

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

NC

NC

NC

NC

NC

NC

65

63

62

60

59

57

56

54

13

11

10

8

7

5

4

2

SM_DQ_R0

SM_DQ_R1

SM_DQ_R2

SM_DQ_R3

SM_DQ_R4

SM_DQ_R5

SM_DQ_R6

SM_DQ_R7

SM_DQ_R8

SM_DQ_R9

SM_DQ_R10

SM_DQ_R11

SM_DQ_R12

SM_DQ_R13

SM_DQ_R14

SM_DQ_R15

42

41

28

40

39

38

37

36

35

32

31

30

29

SM_MAA12

SM_MAA11

SM_MAA10

SM_MAA9

SM_MAA8

SM_MAA7

SM_MAA6

SM_MAB5

SM_MAB4

SM_MAA3

SM_MAB2

SM_MAB1

SM_MAA0

SM_WE#

SM_CAS#

SM_RAS#

SM_VREF_DDR

49

SM_WE#

SM_CAS#

SM_RAS#

SM_CS#2_OB

21

22

23

24

SM_DQS_R2

SM_DQS_R3

51

16

SM_BS0

SM_BS1

26

27

SM_CKE2

44

45

46

CLK_DCLK3

CLK_DCLK3#

SM_DM_R2

SM_DM_R3

+V2.5

47

20

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

VREF

WE#

CAS#

RAS#

CS#

UDQS

LDQS

BA0

BA1

CKE

CLK

CLK#

U46

UDM

LDM

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

0.1U

21

22

23

24

SM_DQS_R6

SM_DQS_R7

51

16

SM_BS0

SM_BS1

26

27

SM_CKE2

44

45

46

8,13 CLK_DCLK4

8,13 CLK_DCLK4#

SM_DM_R6

SM_DM_R7

R463

49

SM_WE#

SM_CAS#

SM_RAS#

SM_CS#2_OB

47

20

+V2.5

120

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

VREF

UDQS

LDQS

BA0

BA1

CKE

CLK

CLK#

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

NC

NC

NC

NC

NC

NC

NC

65

63

62

60

59

57

56

54

13

11

10

8

7

5

4

2

SM_DQ_R16

SM_DQ_R17

SM_DQ_R18

SM_DQ_R19

SM_DQ_R20

SM_DQ_R21

SM_DQ_R22

SM_DQ_R23

SM_DQ_R24

SM_DQ_R25

SM_DQ_R26

SM_DQ_R27

SM_DQ_R28

SM_DQ_R29

SM_DQ_R30

SM_DQ_R31

42

41

28

40

39

38

37

36

35

32

31

30

29

SM_MAA12

SM_MAA11

SM_MAA10

SM_MAA9

SM_MAA8

SM_MAA7

SM_MAA6

SM_MAB5

SM_MAB4

SM_MAA3

SM_MAB2

SM_MAB1

SM_MAA0

SM_VREF_DDR

49

SM_WE#

SM_CAS#

SM_RAS#

SM_CS#2_OB

21

22

23

24

SM_DQS_R4

SM_DQS_R5

51

16

SM_BS0

SM_BS1

26

27

SM_CKE2

44

45

46

SM_DM_R4

SM_DM_R5

47

20

+V2.5

1

18

33

3

9

15

55

61

34

48

66

6

12

52

58

64

DDR 4MX4X16

U44

UDM

LDM

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

NC

NC

NC

NC

NC

NC

65

63

62

60

59

57

56

54

13

11

10

8

7

5

4

2

SM_DQ_R53

SM_DQ_R54

SM_DQ_R55

SM_DQ_R52

SM_DQ_R49

SM_DQ_R51

SM_DQ_R50

SM_DQ_R48

SM_DQ_R56

SM_DQ_R57

SM_DQ_R60

SM_DQ_R61

SM_DQ_R59

SM_DQ_R58

SM_DQ_R62

SM_DQ_R63

42

41

28

40

39

38

37

36

35

32

31

30

29

SM_MAA12

SM_MAA11

SM_MAA10

SM_MAA9

SM_MAA8

SM_MAA7

SM_MAA6

SM_MAB5

SM_MAB4

SM_MAA3

SM_MAB2

SM_MAB1

SM_MAA0

SM_DQ_R[63:0]

SM_DQS_R[0:7]

SM_MAB5

SM_MAB4

8,13,15

8,13,15

SM_MAB2

SM_MAB1

8,13,15

8,13,15

13,14,15

SM_MAA[12:0]