Professional Documents

Culture Documents

New Homework To Be Posted This Weekend Project Phase 3 Launched Next We

New Homework To Be Posted This Weekend Project Phase 3 Launched Next We

Uploaded by

Rio CarthiisOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

New Homework To Be Posted This Weekend Project Phase 3 Launched Next We

New Homework To Be Posted This Weekend Project Phase 3 Launched Next We

Uploaded by

Rio CarthiisCopyright:

Available Formats

EE141

EE141

EECS141

Lecture #24

New

homework to be posted this weekend

Last one to be graded

Project

Phase 3 Launched Next We

Some insights today

EE141

EECS141

Lecture #24

EE141

Last

lecture

Adders

Todays

lecture

Multipliers

Introduction to Memory

Reading

(Ch 11)

EE141

EECS141

Lecture #24

EE141

EECS141

Lecture #24

EE141

EE141

EECS141

Lecture #24

EE141

EECS141

Lecture #24

EE141

EE141

EECS141

Lecture #24

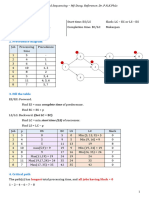

Critical Path 1 & 2

EE141

EECS141

Lecture #24

EE141

Balanced tsum and tcarry

EE141

EECS141

Lecture #24

EE141

EECS141

Lecture #24

10

EE141

EE141

EECS141

Lecture #24

11

EE141

EECS141

Lecture #24

12

EE141

EE141

EECS141

Lecture #24

13

EE141

EECS141

Lecture #24

14

EE141

Optimization

constraints different than in

binary adder

Once again:

Need to identify critical path

And find ways to use parallelism to reduce it

Other

possible techniques

Logarithmic versus linear (Wallace Tree Mult)

Data encoding (Booth)

Pipelining

First glimpse at system level optimization

EE141

EECS141

Lecture #24

15

EE141

EECS141

Lecture #24

16

EE141

Area Dominated by Wiring

EE141

EECS141

Lecture #24

17

Widthbarrel ~ 2 pm M

EE141

EECS141

Lecture #24

18

EE141

EE141

EECS141

Lecture #24

19

Out3

Out2

Out1

EE141

EECS141

Out0

Lecture #24

20

10

EE141

EE141

EECS141

Lecture #24

21

EE141

EECS141

Lecture #24

22

22

11

EE141

Intel 45nm Core 2

EE141

EECS141

23

Lecture #24

Read-Write Memory

Random

Access

Non-Random

Access

SRAM

FIFO

DRAM

LIFO

Non-Volatile

Read-Write

Memory

EPROM

2

E PROM

Read-Only Memory

Mask-Programmed

Programmable (PROM)

FLASH

Shift Register

CAM

EE141

EECS141

Lecture #24

24

12

EE141

STATIC (SRAM)

Data stored as long as supply is applied

Larger (6 transistors/cell)

Fast

Differential (usually)

DYNAMIC (DRAM)

Periodic refresh required

Smaller (1-3 transistors/cell)

Slower

Single Ended

EE141

EECS141

Lecture #24

25

25

Conceptual: linear array

Each box holds some data

But this does not lead to a nice layout shape

Too long and skinny

Create a 2-D array

Decode Row and Column

address to get data

EE141

EECS141

Lecture #24

26

13

EE141

M bits

S0

S1

S2

N

words

SN-2

SN -1

M bits

S0

Word 0

Word 1

Word 2

Storage

cell

A0

A1

A K-1

Word N-2

Word N-1

D

e

c

o

d

e

r

Word 0

Word 1

Word 2

Storage

cell

Word N-2

Word N-1

K = log2N

Input-Output

( M bits)

Input-Output

( M bits)

Intuitive architecture for N x M memory

Too many select signals:

N words == N select signals

Decoder reduces the number of select signals

K = log2N

EE141

EECS141

Lecture #24

27

EE141

EECS141

Lecture #24

28

14

EE141

Collection of 2M complex logic gates

Organized in regular and dense fashion

(N)AND Decoder

NOR Decoder

EE141

EECS141

Lecture #24

29

Look

at decoder for 256x256 memory

block (8KBytes)

EE141

EECS141

Lecture #24

30

15

EE141

Goal:

Build fastest possible decoder with

static CMOS logic

What

we know

Basically need 256 AND

gates, each one of them

drives one word line

N=8

EE141

EECS141

Lecture #24

31

Each

word line has 256 cells connected to it

Total output load is 256*Ccell + Cwire

Assume that decoder input capacitance is

Caddress=4*Ccell

Each

address drives 28/2 AND gates

A0 drives of the gates, A0_b the other of the

gates

Neglecting

Cwire, the fan-out on each one of the

16 address wires is:

B

EE141

EECS141

Lecture #24

32

16

EE141

FB

of at least 213 means that we will want to

use more than log4(213) = 6.5 stages to

implement the AND8

Need

many stages anyways

So what is the best way to implement the AND

gate?

Will see next that its the one with the most stages

and least complicated gates

EE141

EECS141

LE=10/3

1

LE = 10/3

P= 8 + 1

EE141

EECS141

Lecture #24

LE=2

5/3

LE = 10/3

P=4 + 2

33

LE=4/3

5/3

4/3

1

LE = 80/27

P= 2 + 2 + 2 + 1

Lecture #24

34

17

EE141

Using

2-input NAND gates

8-input gate takes 6 stages

Total

LE is (4/3)3 2.4

So PE is 2.4*213 optimal N of ~7.1

EE141

EECS141

256

Lecture #24

35

8-input AND gates

Each built out of

tree of NAND gates

and inverters

Issue:

Every address line has

to drive 128 gates (and

wire) right away

Cant build gates small enough - Forces us

to add buffers just to drive address inputs

EE141

EECS141

Lecture #24

36

18

EE141

EE141

EECS141

Lecture #24

37

Use

a single gate for each of the shared

terms

E.g., from A0, A0, A1, and A1, generate four

signals: A0A1, A0A1, A0A1, A0A1

In

other words, we are decoding smaller

groups of address bits first

And using the predecoded outputs to do

the rest of the decoding

EE141

EECS141

Lecture #24

38

19

EE141

EE141

EECS141

Lecture #24

39

20

You might also like

- ESD QuizDocument10 pagesESD Quizkhurshid darNo ratings yet

- ECEN 248 Lab 5 ReportDocument4 pagesECEN 248 Lab 5 ReportRebecca SontheimerNo ratings yet

- Service Manual Electrical Diagrams 2003B: Maskin: U AC Manual NR: 005973Document61 pagesService Manual Electrical Diagrams 2003B: Maskin: U AC Manual NR: 005973Дмитро СелютинNo ratings yet

- 3 To 8 Decoder in NGSPICEDocument14 pages3 To 8 Decoder in NGSPICEJaydip FadaduNo ratings yet

- 2D Heat Equation Code ReportDocument38 pages2D Heat Equation Code ReportSebastian Torres MontoyaNo ratings yet

- Introduction To Power Electronics - CourseraDocument5 pagesIntroduction To Power Electronics - Courserabvgiri0% (6)

- Combinatorial Optimization: Algorithms and ComplexityFrom EverandCombinatorial Optimization: Algorithms and ComplexityRating: 4 out of 5 stars4/5 (11)

- Lecture5 Memory 2upDocument12 pagesLecture5 Memory 2upPratik TaloleNo ratings yet

- Lecture19 TimingDocument23 pagesLecture19 TimingStefano AlberigoNo ratings yet

- No Lab Next Week Midterm On FR Febr 19 6:30-8pm in Review Session: TBA (Most Likely On TH)Document20 pagesNo Lab Next Week Midterm On FR Febr 19 6:30-8pm in Review Session: TBA (Most Likely On TH)SriramNaiduGorleNo ratings yet

- ECE402 Continues-Time and Discrete-Time Signal Sampling of Analog SignalsDocument25 pagesECE402 Continues-Time and Discrete-Time Signal Sampling of Analog SignalsJayBurdeosNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-4: Data Representations, Memory and Data StructuresDocument22 pagesCPS 104 Computer Organization and Programming Lecture-4: Data Representations, Memory and Data StructuresprachesNo ratings yet

- 5 - Boolean Expression SimplificationDocument5 pages5 - Boolean Expression SimplificationMelody Mae MalaluanNo ratings yet

- 10 11 FVM Convecton DiffusionDocument41 pages10 11 FVM Convecton DiffusionSrivatsan SampathNo ratings yet

- Module1: Numerical Solution of Ordinary Differential EquationsDocument7 pagesModule1: Numerical Solution of Ordinary Differential EquationsPiyooshTripathiNo ratings yet

- CS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariDocument82 pagesCS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariDuncan KingNo ratings yet

- Spline Collocation Methods for Partial Differential Equations: With Applications in RFrom EverandSpline Collocation Methods for Partial Differential Equations: With Applications in RNo ratings yet

- Experiment Title - 1.2Document11 pagesExperiment Title - 1.2Abhishek ReignsNo ratings yet

- 2.0 Computer System: 2.2 Number System and RepresentationDocument34 pages2.0 Computer System: 2.2 Number System and RepresentationshurimzainolNo ratings yet

- 09 Logic DesignDocument14 pages09 Logic DesignAmita Rathee DahiyaNo ratings yet

- Basics of Logic Design: Boolean Algebra, Logic Gates: Computer Science 104Document13 pagesBasics of Logic Design: Boolean Algebra, Logic Gates: Computer Science 104Rakesh SHNo ratings yet

- To Departments 12 11 2014 Database S1 2014-2015Document4 pagesTo Departments 12 11 2014 Database S1 2014-2015Majid HelmyNo ratings yet

- ALU DesingDocument7 pagesALU Desingsachin_bhingareNo ratings yet

- Tugas Desain Eksperimen I Desain Blok Tak Lengkap Acak: Dosen: Enny Supartini, Dra., MSDocument6 pagesTugas Desain Eksperimen I Desain Blok Tak Lengkap Acak: Dosen: Enny Supartini, Dra., MSSalsaNo ratings yet

- Logical Effort: Boris Murmann Center For Integrated Systems Stanford UniversityDocument10 pagesLogical Effort: Boris Murmann Center For Integrated Systems Stanford UniversitysatyajtiNo ratings yet

- ExampleDocument18 pagesExampleSaif AlabdullahNo ratings yet

- Bernoulli PrincipleDocument12 pagesBernoulli PrincipleRoshane Nanayakkara100% (1)

- 29.ECE301 - Logical Effort and Transistor Sizing - IIDocument22 pages29.ECE301 - Logical Effort and Transistor Sizing - IINambisan04No ratings yet

- ECE232testnumber2 Spring2013Document5 pagesECE232testnumber2 Spring2013krzydudNo ratings yet

- Esc101: Fundamentals of Computing Esc101: Fundamentals of ComputingDocument13 pagesEsc101: Fundamentals of Computing Esc101: Fundamentals of ComputingMukesh Kumar DewraNo ratings yet

- Be101-05 Introduction To Computing and Problem Solving Question PaperDocument4 pagesBe101-05 Introduction To Computing and Problem Solving Question PaperAswathy G MenonNo ratings yet

- Res5 Mathsc1revisionplannerDocument4 pagesRes5 Mathsc1revisionplannerTimothy CrittendenNo ratings yet

- CS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariDocument82 pagesCS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariElizabeth AliazNo ratings yet

- DiscussionDocument14 pagesDiscussionYousif OthmanNo ratings yet

- Numerican MethodDocument8 pagesNumerican MethodmsghamiriNo ratings yet

- EE141 - Fall 2003 Digital Integrated CircuitsDocument26 pagesEE141 - Fall 2003 Digital Integrated CircuitscanilreddyNo ratings yet

- Assignment - 7Document11 pagesAssignment - 7YUH 2020No ratings yet

- Topics To Cover in 2: Topics Chapters # of LecturesDocument45 pagesTopics To Cover in 2: Topics Chapters # of LecturesEvelyn KeaneNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-21: Building A DatapathDocument32 pagesCPS 104 Computer Organization and Programming Lecture-21: Building A DatapathprachesNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-18: Memory Elements, Busses, RegistersDocument26 pagesCPS 104 Computer Organization and Programming Lecture-18: Memory Elements, Busses, RegistersprachesNo ratings yet

- CPS 104 Computer Organization and Programming Lecture-2: Data RepresentationsDocument30 pagesCPS 104 Computer Organization and Programming Lecture-2: Data RepresentationsprachesNo ratings yet

- Mae 1202: Aerospace Practicum: Lecture 5: Compressible and Isentropic Flow 1Document57 pagesMae 1202: Aerospace Practicum: Lecture 5: Compressible and Isentropic Flow 1anon_959268562No ratings yet

- Lecture04 Timing Basics 2upDocument11 pagesLecture04 Timing Basics 2uptarungupta79No ratings yet

- Sched Midterm NoteDocument18 pagesSched Midterm NoteVan Anh NguyenNo ratings yet

- Mkchap 4Document9 pagesMkchap 4malmir_sNo ratings yet

- APSC256-Solution To Assignment 2 PDFDocument4 pagesAPSC256-Solution To Assignment 2 PDFmartensd01No ratings yet

- Course Key Elab SEMESTER 1 2020-2021 K23Document6 pagesCourse Key Elab SEMESTER 1 2020-2021 K23tranvi260801No ratings yet

- Distance Learning 66Document3 pagesDistance Learning 66HELPPPPPNo ratings yet

- Lec 04 Pipeline D ProcessorDocument106 pagesLec 04 Pipeline D ProcessorMaheshKotaNo ratings yet

- On A Parallel Decimal Multiplier Based On Hybrid 8421-5421 BCD RecodingDocument4 pagesOn A Parallel Decimal Multiplier Based On Hybrid 8421-5421 BCD RecodingJohn LeonsNo ratings yet

- Addition: Recall Complete The TableDocument15 pagesAddition: Recall Complete The TableMrityunjay Kumar RaiNo ratings yet

- Servo Drive Systems - Chapter 4 - Part1Document20 pagesServo Drive Systems - Chapter 4 - Part1To Ba ThoNo ratings yet

- Fliud Mechanics Exxperiment 4Document2 pagesFliud Mechanics Exxperiment 4Nah Sr AdNo ratings yet

- Inbound 2885546982363080324Document5 pagesInbound 2885546982363080324Melody RubionNo ratings yet

- 18-791 Lecture #17 Introduction To The Fast Fourier Transform AlgorithmDocument22 pages18-791 Lecture #17 Introduction To The Fast Fourier Transform AlgorithmNizar AyubNo ratings yet

- EE3: Introduction To Electrical Engineering Lecture 1: Circuits IDocument28 pagesEE3: Introduction To Electrical Engineering Lecture 1: Circuits IANo ratings yet

- Lecture 3. Boolean Algebra, Logic Gates: Prof. Sin-Min Lee Department of Computer ScienceDocument64 pagesLecture 3. Boolean Algebra, Logic Gates: Prof. Sin-Min Lee Department of Computer ScienceEko Ari Puspita HadimirawanNo ratings yet

- Year 11&12ext1 and Year 12 Ext 2-Scope and Sequences 2015Document4 pagesYear 11&12ext1 and Year 12 Ext 2-Scope and Sequences 2015Dimitri KandilasNo ratings yet

- CH04 SolutionDocument24 pagesCH04 SolutionJonathan ManzakiNo ratings yet

- Bachelor of Science in Electronics EngineeringDocument7 pagesBachelor of Science in Electronics EngineeringDean MoisesNo ratings yet

- SodaPDF Merged Merging ResultDocument9 pagesSodaPDF Merged Merging ResultFarzana Israt Tutul 2013624642No ratings yet

- Complex NumbersDocument25 pagesComplex NumbersRio CarthiisNo ratings yet

- Installation Guide ETAP19.0.1 PDFDocument2 pagesInstallation Guide ETAP19.0.1 PDFRio CarthiisNo ratings yet

- Markdown For Jupyter Notebooks Cheatsheet - IBM Watson Data - MediumDocument3 pagesMarkdown For Jupyter Notebooks Cheatsheet - IBM Watson Data - MediumRio CarthiisNo ratings yet

- Electronics 08 00292 v3 PDFDocument66 pagesElectronics 08 00292 v3 PDFRio CarthiisNo ratings yet

- Perry - EKDocument1 pagePerry - EKRio CarthiisNo ratings yet

- Moderation of Module MarksDocument3 pagesModeration of Module MarksRio CarthiisNo ratings yet

- RT Box ManualDocument48 pagesRT Box ManualRio CarthiisNo ratings yet

- GT Exhaust Systems, Inc. 501-6100 SERIES Slim Line "SLR" Series Super CriticalDocument1 pageGT Exhaust Systems, Inc. 501-6100 SERIES Slim Line "SLR" Series Super CriticalRio CarthiisNo ratings yet

- DRAM (Dynamic Random Access Memory) Leakage Path AnalysisDocument10 pagesDRAM (Dynamic Random Access Memory) Leakage Path AnalysisRio CarthiisNo ratings yet

- Visualizing MotionDocument7 pagesVisualizing MotionRio CarthiisNo ratings yet

- Fabry-Perot Interferomter: E T T e T T' R R e T T' R R e T T' R RDocument4 pagesFabry-Perot Interferomter: E T T e T T' R R e T T' R R e T T' R RRio CarthiisNo ratings yet

- Dokumen - Tips 988b Wheel Loader SN 50w1 Up Caterpillar 988b Wheel Loader Service ManualDocument6 pagesDokumen - Tips 988b Wheel Loader SN 50w1 Up Caterpillar 988b Wheel Loader Service ManualRasoul MozhdehpoorNo ratings yet

- High-Performance PIC24 Microcontroller Family: 16-Bit MicrocontrollersDocument6 pagesHigh-Performance PIC24 Microcontroller Family: 16-Bit MicrocontrollersptkienNo ratings yet

- Project ReportDocument20 pagesProject ReportPiyush GuptaNo ratings yet

- War Field Spying Robot With Night Vision Wireless Camera: Submitted byDocument26 pagesWar Field Spying Robot With Night Vision Wireless Camera: Submitted byankita dhengaleNo ratings yet

- Sony Smart LEDDocument153 pagesSony Smart LEDCadwill100% (2)

- Check Valve DescriptionDocument1 pageCheck Valve DescriptionmoodydoodyNo ratings yet

- Hand Gesture Vocaliser For DeafDocument6 pagesHand Gesture Vocaliser For DeafInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- pcm-9361 DATA SHEETDocument3 pagespcm-9361 DATA SHEETAyman MaezaNo ratings yet

- Thermal Fogger Manual: VectorDocument16 pagesThermal Fogger Manual: VectorLiliana ANo ratings yet

- Light Is Fascination: Quality That Catches The Eye: Original Osram P-Vip Projection LampsDocument2 pagesLight Is Fascination: Quality That Catches The Eye: Original Osram P-Vip Projection LampsTiago BotelhoNo ratings yet

- Intake Manifold PDFDocument7 pagesIntake Manifold PDFjorgeantonio2442@No ratings yet

- Automatic Transmission Fluid Chart: ULV ULVDocument3 pagesAutomatic Transmission Fluid Chart: ULV ULVossoskiNo ratings yet

- 5R55N Seminar InfoDocument18 pages5R55N Seminar InfocarlosNo ratings yet

- 2.1 On - Off Control PDFDocument36 pages2.1 On - Off Control PDFOscar Lob GioNo ratings yet

- Firenet Plus Wiring InstructionsDocument9 pagesFirenet Plus Wiring InstructionsjavedNo ratings yet

- ECD-V4 OutlineDocument4 pagesECD-V4 OutlineВячеслав ГлушакNo ratings yet

- Repair Kits: "N" Version Ø 24mmDocument1 pageRepair Kits: "N" Version Ø 24mmAdan BarbasNo ratings yet

- PT GG Install Rev 2Document28 pagesPT GG Install Rev 2Yassine.G ChipLabNo ratings yet

- Surigao State College of Technology Surigao City-Main Campus College of Engineering and Information TechnologyDocument8 pagesSurigao State College of Technology Surigao City-Main Campus College of Engineering and Information TechnologyKim SomeraNo ratings yet

- RY-6W-K RelayDocument9 pagesRY-6W-K Relayge_bdNo ratings yet

- PE3308 - Technical Summary For Cable1632 Rev DDocument2 pagesPE3308 - Technical Summary For Cable1632 Rev DJohn HallowsNo ratings yet

- SPL PLL - 01 Solar King LED Streetlight 40,60,80,100 (PL)Document13 pagesSPL PLL - 01 Solar King LED Streetlight 40,60,80,100 (PL)Tariq KhurshaidiNo ratings yet

- DVJX 1Document136 pagesDVJX 1Silvinho JúniorNo ratings yet

- KBM255 Series 2018Document4 pagesKBM255 Series 2018Lucian A MUșaNo ratings yet

- TeslaDocument3 pagesTeslaKESH MusicNo ratings yet

- Power Supply 1/4 Schematic Diagram: Caution ! Caution !: ATTENTION: Utiliser Un Fusible de Rechange de MDocument6 pagesPower Supply 1/4 Schematic Diagram: Caution ! Caution !: ATTENTION: Utiliser Un Fusible de Rechange de MErick MoraNo ratings yet

- Q45Document2 pagesQ45Ahmed Baha MahjoubNo ratings yet

- ADL945PCDocument2 pagesADL945PCRaj ManiNo ratings yet