Professional Documents

Culture Documents

Confidential: Sadd - Asm Benchmark and Your New SADD Instruction

Confidential: Sadd - Asm Benchmark and Your New SADD Instruction

Uploaded by

Rajat MehndirattaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Confidential: Sadd - Asm Benchmark and Your New SADD Instruction

Confidential: Sadd - Asm Benchmark and Your New SADD Instruction

Uploaded by

Rajat MehndirattaCopyright:

Available Formats

CONFIDENTIAL

November 29, 2015

240 Student

ECE Consultants, Inc

HH-1105

Pittsburgh, PA 15213

Esteemed Pong Expert,

I seek knowledge about the behavior of the Pong240. Would you please answer the following questions about the

sadd.asm benchmark and your new SADD instruction:

1) Where is the table of numbers stored? Which one is loaded first?

2) Wait, isn't this backwards? When the result is negative, the program loads a positive number. Please explain.

3) Is the timing data dependent? i.e., does it depend on the values being added?

4) How many clock ticks does it take to execute the whole benchmark? You could have the SystemVerilog simulator

print this information.

5) Have the simulator print out the information for the following table. How many clock ticks does it take to execute

from "add R3,R2" to "bra CKEND" (inclusive) assuming that the brv is taken? You'll need to add some rows here -or attach a listing.

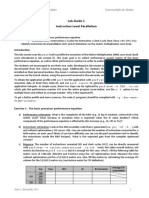

CLOCK R0

TICK

i

i+1

i+2

i+3

i+4

:

:

R1

R2

R3

IR

PC

MAR

MDR

INSTRUCTIO

N

CONFIDENTIAL

6.) How many Logic Elements does the original processor and memory occupy?

Second week questions:

1.) Now using your new design (week 2) and new benchmark program with the new instruction in it, trace through

the execution of the SADD instruction (only). Yes, a bunch of assembly code went away when compared to the

original benchmark. Simulate your new SystemVerilog and have it print out the information for this table.

CLOCK R0

TICK

R1

R2

R3

IR

PC

MAR

MDR

INSTRUCTIO

N

i

i+1

i+2

i+3

i+4

:

:

2) How many clock ticks does it take to run the whole new SADD benchmark?

3) How many Logic Elements does the new processor design and memory occupy?

4) How long (approximately) did it take to synthesize the original design, including place and route?

Sincerely yours,

Mr. Ping

PingsPong, Inc.

Page 2

You might also like

- 5 6061978178002355489Document25 pages5 6061978178002355489YashashwiniNo ratings yet

- Interview Questions for IBM Mainframe DevelopersFrom EverandInterview Questions for IBM Mainframe DevelopersRating: 1 out of 5 stars1/5 (1)

- National University of Computer and Emerging Sciences, Lahore CampusDocument4 pagesNational University of Computer and Emerging Sciences, Lahore CampusxxxNo ratings yet

- 131179009679888042Document7 pages131179009679888042Ali AsgharNo ratings yet

- HPCDocument7 pagesHPCSmita ShresthaNo ratings yet

- Lab Project: Shift-and-Add Multiplication Circuit With StorageDocument5 pagesLab Project: Shift-and-Add Multiplication Circuit With StoragesneophNo ratings yet

- CS416-Final-Spring 2020Document5 pagesCS416-Final-Spring 2020abdurahman saeedNo ratings yet

- Question Paper3Document12 pagesQuestion Paper3Divya KakumanuNo ratings yet

- Lec 02 - Intro Algorithms PDFDocument70 pagesLec 02 - Intro Algorithms PDFShoyab AhamedNo ratings yet

- Lab10 CompletoDocument10 pagesLab10 CompletoLuis Fernando Ramos OlandaNo ratings yet

- Samsung Interview ExpDocument18 pagesSamsung Interview ExpMohit SinghNo ratings yet

- Basis QuestionDocument72 pagesBasis Questionmhku1No ratings yet

- Threads Locks UsageDocument16 pagesThreads Locks UsagesimlulirduNo ratings yet

- Artillery - API FreightingDocument6 pagesArtillery - API FreightingkashyapNo ratings yet

- C++ Optimization Strategies and Techniques: Pete IsenseeDocument38 pagesC++ Optimization Strategies and Techniques: Pete IsenseelinnhtooNo ratings yet

- SAP MM Interview QuestionsDocument8 pagesSAP MM Interview QuestionsTara Panda100% (2)

- Midterm1 With SolsDocument5 pagesMidterm1 With SolsĐạt ViếtNo ratings yet

- TESTDocument44 pagesTESTForward BiasNo ratings yet

- Python ODC-17032022Document8 pagesPython ODC-17032022Pawan MishraNo ratings yet

- ECE3073 2014 Lab 3Document5 pagesECE3073 2014 Lab 3Andrew WalleyNo ratings yet

- Basis QuestionsDocument7 pagesBasis QuestionsChandu ManikantaNo ratings yet

- CIS DumpDocument22 pagesCIS DumpspandanaNo ratings yet

- 200 125update PDFDocument235 pages200 125update PDFMurtaxa KhanNo ratings yet

- Insert, Update Ordering in InformaticaDocument6 pagesInsert, Update Ordering in InformaticaUr's GopinathNo ratings yet

- Assignment 2Document4 pagesAssignment 2Mohamed WaseemNo ratings yet

- CS224 - Spring 2021 - Lab #5 Implementing The MIPS Processor With Pipelined MicroarchitectureDocument5 pagesCS224 - Spring 2021 - Lab #5 Implementing The MIPS Processor With Pipelined MicroarchitectureArda Barış ÖrtlekNo ratings yet

- BDC Part3Document8 pagesBDC Part3Latha JujariNo ratings yet

- Previous Year Coding Questions Solution (Free)Document6 pagesPrevious Year Coding Questions Solution (Free)priyasNo ratings yet

- hw1 Problem SetDocument8 pageshw1 Problem SetBilly bobNo ratings yet

- Ii. TechnicalDocument20 pagesIi. TechnicalTriveni_maneshNo ratings yet

- PL01 GuiaoDocument3 pagesPL01 GuiaoJoão LourençoNo ratings yet

- Sap BW Int QuestionsDocument48 pagesSap BW Int QuestionssureshNo ratings yet

- Midterm1 s15 SolDocument26 pagesMidterm1 s15 SolGABRIEL, FRANCIS CESAR II, SNo ratings yet

- ECE 341 2014 Midterm Take HomeDocument7 pagesECE 341 2014 Midterm Take HomeLukeLiNo ratings yet

- Cso AssignmtDocument8 pagesCso AssignmtBenedict MelvinNo ratings yet

- Problem StatementDocument8 pagesProblem StatementKarthikeyaNo ratings yet

- 10Document5 pages10srsecondarycomputerscienceteacher1No ratings yet

- Quiz 1Document12 pagesQuiz 1RexChandu100% (1)

- CS232 Operating Systems Assignment 01: Simulate A Scheduler Due: 20th September, 2020Document3 pagesCS232 Operating Systems Assignment 01: Simulate A Scheduler Due: 20th September, 2020Sam5127No ratings yet

- Scan ChainDocument10 pagesScan ChainRaunakRajGuptaNo ratings yet

- Cmpe242 SPRING 2012-2013 FINALDocument7 pagesCmpe242 SPRING 2012-2013 FINALMaaz qureshi 1No ratings yet

- MX009 - Proportional Integral Derivative Control PDFDocument5 pagesMX009 - Proportional Integral Derivative Control PDFjorgemdp5No ratings yet

- Sas Interview QuestionsDocument79 pagesSas Interview QuestionsRohan BIradarNo ratings yet

- CS61: Systems Programming and Machine Organization Section NotesDocument9 pagesCS61: Systems Programming and Machine Organization Section NotesDevendra KumarNo ratings yet

- Ca Final Fa19 BCS 087Document6 pagesCa Final Fa19 BCS 087ahmad razaNo ratings yet

- ECE 264 Advanced C Programming 2009/01/16: ReminderDocument14 pagesECE 264 Advanced C Programming 2009/01/16: Remindertruongvinhlan19895148No ratings yet

- Q & ADocument6 pagesQ & ARaf PortaelNo ratings yet

- PDF 1Document17 pagesPDF 1Nivedita Acharyya 2035No ratings yet

- PLC Counters... Timers Vikas M SampathDocument57 pagesPLC Counters... Timers Vikas M SampathVikas M SampathNo ratings yet

- Tutorial Sheet2014Document7 pagesTutorial Sheet2014Julia DanielNo ratings yet

- A.P.T PortfolioDocument3 pagesA.P.T PortfolioPulak MehtaNo ratings yet

- Cloud Computing End Term Special QPDocument3 pagesCloud Computing End Term Special QPರಾಘವೇಂದ್ರ ಟಿ ಎಸ್No ratings yet

- Study MaterialDocument26 pagesStudy MaterialshardapatelNo ratings yet

- WWW Indiabix Com Placement Papers CSC 494Document21 pagesWWW Indiabix Com Placement Papers CSC 494Ratul Chopra0% (1)

- HappayDocument21 pagesHappaypvnath04No ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- AP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceFrom EverandAP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceNo ratings yet

- Deep Belief Nets in C++ and CUDA C: Volume 3: Convolutional NetsFrom EverandDeep Belief Nets in C++ and CUDA C: Volume 3: Convolutional NetsNo ratings yet