Professional Documents

Culture Documents

AIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 Schematic

AIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 Schematic

Uploaded by

Roshni Khurana0 ratings0% found this document useful (0 votes)

22 views4 pagesThe document describes an experiment to implement and verify the functionality of 2-input NAND and NOR gates using S-Edit simulation software. It includes the schematics, T-Spice code, and output for both gates. The experiment verifies that the output of the 2-input NAND gate and NOR gate match their respective truth tables.

Original Description:

Original Title

3.docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document describes an experiment to implement and verify the functionality of 2-input NAND and NOR gates using S-Edit simulation software. It includes the schematics, T-Spice code, and output for both gates. The experiment verifies that the output of the 2-input NAND gate and NOR gate match their respective truth tables.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

22 views4 pagesAIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 Schematic

AIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 Schematic

Uploaded by

Roshni KhuranaThe document describes an experiment to implement and verify the functionality of 2-input NAND and NOR gates using S-Edit simulation software. It includes the schematics, T-Spice code, and output for both gates. The experiment verifies that the output of the 2-input NAND gate and NOR gate match their respective truth tables.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 4

EXPERIMENT-3

AIM- To implement and verify the functionality of 2 input NAND and NOR gate using S-Edit.

TOOLS REQUIRED- S-Edit Tanner Tool, T-Spice 12..6

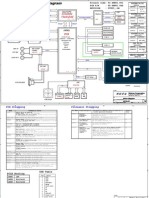

SCHEMATICa) NAND gate

Schematic for 2 input NAND gate

T-SPICE CODEa) NAND gate

.model nmos nmos

.model pmos pmos

vdd vdd gnd 5v

.tran 1n 100n

VIn In gnd PULSE(0 5 0 1n 1n 10n 20n)

VIn2 In2 gnd PULSE(0 5 0 1n 1n 10n 20n)

.print v(Out) v(In) v(In2)

.end

OUTPUT- a) NAND gate

Output of 2 input NAND gate

SCHEMATICb) NOR gate

Schematic for 2 input NOR gate

T-SPICE CODEb) NOR gate

.model nmos nmos

.model pmos pmos

vdd vdd gnd 5v

.tran 1n 100n

VIn In gnd PULSE(0 5 0 1n 1n 10n 20n)

VIn2 In2 gnd PULSE(0 5 0 1n 1n 10n 20n)

.print v(Out) v(In) v(In2)

.end

OUTPUT- b) NOR gate

Output of 2 input NOR gate

RESULT-

The truth table for 2 input NAND gate is as follows:

A

0

0

1

1

B

0

1

0

1

C=(AB)

1

1

1

0

The truth table for 2 input NOR gate is as follows:

A

0

0

1

1

0

1

0

1

The above mentioned truth tables are verified.

C=(A+B)

1

0

0

0

You might also like

- Huanyang InverterDocument1 pageHuanyang InverterTombongNo ratings yet

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNo ratings yet

- AIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 SchematicDocument4 pagesAIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 SchematicRoshni KhuranaNo ratings yet

- Assignment 2: M12497296 Harshavardhan MedasaniDocument48 pagesAssignment 2: M12497296 Harshavardhan MedasanidoffNo ratings yet

- MBI6024 Datasheet VA.00-EnDocument39 pagesMBI6024 Datasheet VA.00-Enastral projectNo ratings yet

- DICD Lecture 16 Ver3 Class Room-1Document25 pagesDICD Lecture 16 Ver3 Class Room-1janapaneni ramadeviNo ratings yet

- Vlsi Lab ReportDocument26 pagesVlsi Lab ReportSathvick BatchuNo ratings yet

- 10.709 Gbps Laser Diode Driver Chipset: A To 1200 ADocument12 pages10.709 Gbps Laser Diode Driver Chipset: A To 1200 ABanyugeaNo ratings yet

- Lab 1Document8 pagesLab 1abc abcNo ratings yet

- CAD For VLSI Design - II: V. Kamakoti and Shankar BalachandranDocument18 pagesCAD For VLSI Design - II: V. Kamakoti and Shankar BalachandranAjaya HsNo ratings yet

- 10-To-20 Pos JTAG AdapterDocument1 page10-To-20 Pos JTAG Adapterpesccia6224No ratings yet

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDocument16 pagesChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- ASRG08 QC DatasheetDocument37 pagesASRG08 QC DatasheetJose Benavides100% (1)

- Config v.3.1 Revised)Document6 pagesConfig v.3.1 Revised)Andri Purnawan100% (1)

- cdp1802 CosmacDocument27 pagescdp1802 Cosmacrebirth90No ratings yet

- ID-3LA-LP ID-12LA-LP ID-20LA-LP RFID Reader Modules Low Power - Micro Power 125khz LFDocument20 pagesID-3LA-LP ID-12LA-LP ID-20LA-LP RFID Reader Modules Low Power - Micro Power 125khz LFAbleIDLtdNo ratings yet

- Adam26p16 AbovDocument37 pagesAdam26p16 Abovwilson de jesus miranda noreñaNo ratings yet

- Ts A300dDocument42 pagesTs A300dEvgeniy KotNo ratings yet

- Shenzhen Sunmoon Micro SM2255E - C881537Document12 pagesShenzhen Sunmoon Micro SM2255E - C881537Technical sidhuNo ratings yet

- AVR Force+SensorDocument3 pagesAVR Force+SensorMC. Rene Solis R.No ratings yet

- TBoxLITE Installation ManualDocument7 pagesTBoxLITE Installation ManualbrettmayNo ratings yet

- ¡ Semiconductor: General DescriptionDocument17 pages¡ Semiconductor: General DescriptionNguyễn Thành LinhNo ratings yet

- STA013 STA013B STA013T: Mpeg 2.5 Layer Iii Audio DecoderDocument38 pagesSTA013 STA013B STA013T: Mpeg 2.5 Layer Iii Audio DecoderSandesh PatiNo ratings yet

- DLA001Document36 pagesDLA001Rogerio GuimarãesNo ratings yet

- MakerBot MightyBoard REVE SchematicDocument1 pageMakerBot MightyBoard REVE SchematicblablablouNo ratings yet

- Wiring DiagramDocument8 pagesWiring DiagramChirita ElenaNo ratings yet

- A SemiconductoresDocument19 pagesA Semiconductoresajcl_1987No ratings yet

- 20ec016 VlsiDocument33 pages20ec016 Vlsi20EC016 NANDINI DHOLAKIANo ratings yet

- Top-Level Diagram: SHEET 13-18Document21 pagesTop-Level Diagram: SHEET 13-18Aref MGHNo ratings yet

- BT21ECE102 DMLAB Assignment-03Document17 pagesBT21ECE102 DMLAB Assignment-03S075 Abhishek DeshmukhNo ratings yet

- ObjectivesDocument3 pagesObjectivesSonet HosainNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- Ppaf 1022Document3 pagesPpaf 1022motocelNo ratings yet

- Adapt 5Document4 pagesAdapt 5sohail nasirNo ratings yet

- Features: Low Cost Very High Performance SMD GPS ModuleDocument13 pagesFeatures: Low Cost Very High Performance SMD GPS ModulemauriceNo ratings yet

- Backup Transodulador VMH 03-11-2023Document88 pagesBackup Transodulador VMH 03-11-2023meltelecom376No ratings yet

- Delay in VLSIDocument27 pagesDelay in VLSIlevan100% (1)

- R1162x SERIES: 3-Mode 150ma Ldo Regulator OutlineDocument32 pagesR1162x SERIES: 3-Mode 150ma Ldo Regulator OutlineZak zsNo ratings yet

- Afe 7070Document44 pagesAfe 7070Srinagesh V MandapakaNo ratings yet

- A6/A7/A6C User Manual: GSM/GPRS quad-band+GPS+AGPSDocument21 pagesA6/A7/A6C User Manual: GSM/GPRS quad-band+GPS+AGPSRosmanNo ratings yet

- Starchips Starchips Starchips Starchips: TechnologyDocument15 pagesStarchips Starchips Starchips Starchips: TechnologyXFact0r100% (1)

- 08.wiring DiagramDocument8 pages08.wiring Diagramconnectingeurope8479No ratings yet

- DatasheetDocument13 pagesDatasheetbitanjungNo ratings yet

- HP Probook 4510s Wistron S-Class Intel Rev Pv-01 SCHDocument62 pagesHP Probook 4510s Wistron S-Class Intel Rev Pv-01 SCHCristian ValentinNo ratings yet

- SYCDocument113 pagesSYCwintermacNo ratings yet

- Vlsi Laboratory: List of ExperimentsDocument49 pagesVlsi Laboratory: List of ExperimentssantoshNo ratings yet

- Note: All Text Detalis (And Circuit) Are For Your Write Up in Your RecordDocument4 pagesNote: All Text Detalis (And Circuit) Are For Your Write Up in Your RecordAmbica SreeNo ratings yet

- SN 65 HVD 256Document28 pagesSN 65 HVD 256jaysenghaniNo ratings yet

- Learn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.From EverandLearn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.No ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Broadband Technologies and Applications: A Tutorial: Dale N. HatfieldDocument40 pagesBroadband Technologies and Applications: A Tutorial: Dale N. HatfieldRoshni KhuranaNo ratings yet

- 6.2 Elements of Transport Protocols PDFDocument12 pages6.2 Elements of Transport Protocols PDFRoshni KhuranaNo ratings yet

- C Pointers Questions PDFDocument30 pagesC Pointers Questions PDFRoshni Khurana0% (2)

- Mody Institute of Technology and Science: Major ProjectDocument1 pageMody Institute of Technology and Science: Major ProjectRoshni KhuranaNo ratings yet

- Embedded System Lab File: IndexDocument2 pagesEmbedded System Lab File: IndexRoshni KhuranaNo ratings yet

- AIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 SchematicDocument4 pagesAIM-To Implement and Verify The Functionality of 2 Input NAND and NOR Gate Using S-Edit. TOOLS REQUIRED - S-Edit Tanner Tool, T-Spice 12..6 SchematicRoshni KhuranaNo ratings yet