Professional Documents

Culture Documents

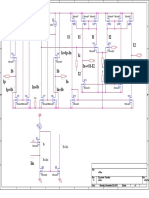

SR Latch Differential Input Latch: VDD M2 M1 M6 M5 CLK CLK VDD

SR Latch Differential Input Latch: VDD M2 M1 M6 M5 CLK CLK VDD

Uploaded by

Harshal AmbatkarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SR Latch Differential Input Latch: VDD M2 M1 M6 M5 CLK CLK VDD

SR Latch Differential Input Latch: VDD M2 M1 M6 M5 CLK CLK VDD

Uploaded by

Harshal AmbatkarCopyright:

Available Formats

VDD

M2

M1

M6

M5

CLK

VDD

O+

M6

M3

M7

M7

M5

M4

VDD

SR1

VDD

CLK

out+

OUT+

SR

out-

OUT-

VDD

O-

O+

OUT-

M2

OUT+

M0

R

M3

VDD

M8

M4

M0

M1

IN+

IN-

O-

VDD

IN+

IN-

V_in+

V_in-

V_CLK

val0=0.0

val1=1.2

val0=1.2

val1=0

val0=0.0

val1=1.2

M9

gnd

gnd

CLK

gnd

gnd

SR Latch

CLK

Differential Input Latch

Date/Time Run: 4/28/2016 3:59:58 PM

1.2

1

0.8

V

0.6

0.4

0.2

SEL>>

-0.106

OUT+

1.2

1

0.8

0.6

0.4

0.2

0

OUT1.2

1

0.8

0.6

0.4

0.2

0

R

1.2

1

0.8

0.6

0.4

0.2

0

0

10n

20n

30n

40n

50n

S

SymSpice

time, s

60n

70n

80n

90n

100n

Date/Time Run: 4/28/2016 10:05:39 AM

1.9

1.6

V

1.2

0.8

0.4

0

CLK

1.9

1.6

V

1.2

0.8

SEL>>

-0.1

IN+

1.9

1.6

V

1.2

0.8

0.4

0

IN2

1.6

V

1.2

0.8

0.4

0

out+

2

1.6

V

1.2

0.8

0.4

0

0

0.5n

1n

1.5n

2n

2.5n

outSymSpice

time, s

3n

3.5n

4n

4.5n

5n

M10

M11

VDD

M8

A

VDD

M0

M3

A

M1

VDD

IN

OUT

IN

Abar

M1

Bbar

M5

M6

M1

Bbar

M7

B

OUT

M0

M1

B

A

out

VDD

M9

Abar

M0

M0

out

M2

Abar

M3

A

A

M2

gnd

Transmission Gate

Bbar

XOR Gate

CLK

Vdd

CLKbar

M8

M3

VDD

M5

Vdd

Vdd

Q

M4

Data

gnd

gnd

M7

M2

gnd

gnd

CLK

CLKbar

gnd

Vdd

M15

CLKbar

PHIbar

Vdd

CLK

Vdd

PHI

M14

gnd

Vdd

M17

CLK

CLKbar

M16

M1

M9

M0

M6

gnd

Regular FF

gnd

M4

B

gnd

NOR Gate

M11

Inverter

gnd

M10

gnd

Vdd

INV

IN

Data

Vdd

CLK

OUT

I2

IN

OUT

IN

PHIbar

I3

INV

regular_FF

PHI

OUT

IN

INV

VDD

I0

TG

PHIbar

VDD

VDD

Vdd

PHIbar

Vdd

I1

PHI

OUT

VDD

I4

VDD

VDD

Vdd

Data

out

out

I5

XOR

I6

Vdd

VDD

VDD

INV

VDD

IN

Vdd

VDD

OUT

I1

Vdd

PHIbar

NOR

B

PHI

PHIbar

CLK

VDD

Clock Gating Circuit

gnd

V_Data

V_CLK

val0=0.0

val1=1.1

val0=0.0

val1=1.1

gnd

gnd

CLK

clk_gatin_ckt

D

Q

Self Gating Flip-Flop

I0

Date/Time Run: 4/28/2016 9:48:26 AM

1.2

0.8

0.4

SEL>>

-0.1

CLK

1.2

0.8

0.4

0

D

1.2

0.8

0.4

0

Q

1.2

0.8

0.4

0

PHI

1.2

0.8

0.4

0

0

10n

20n

30n

40n

50n

PHIbar

SymSpice

time, s

60n

70n

80n

90n

100n

Date/Time Run: 4/28/2016 9:58:41 AM

1.2

1

0.8

0.6

0.4

0.2

SEL>>

-0.1

CLK

1.2

1

0.8

0.6

0.4

0.2

0

-0.1

Data

1.2

1

0.8

0.6

0.4

0.2

0

-0.121

0

10n

20n

30n

40n

50n

Q

SymSpice

time, s

60n

70n

80n

90n

100n

You might also like

- All LVDS PDFDocument20 pagesAll LVDS PDFNicolas Gandolfo92% (13)

- Transistores SustitutosDocument10 pagesTransistores Sustitutosrubl770622s98No ratings yet

- Transistor Sizing - TSPC and C2MOSDocument7 pagesTransistor Sizing - TSPC and C2MOSHarshal AmbatkarNo ratings yet

- RK-10161 144Document1 pageRK-10161 144Hady PrastyoNo ratings yet

- Test ACIER AudeDocument1,286 pagesTest ACIER AudeYoann RIZKINo ratings yet

- KPC S4594VDocument13 pagesKPC S4594VJohn Walter Ticona Quispe0% (1)

- Z28J60 KyokosaDocument1 pageZ28J60 KyokosamarcozizuoNo ratings yet

- SE431 Adjustable Shunt RegulatorDocument8 pagesSE431 Adjustable Shunt RegulatorFady HachemNo ratings yet

- MT8888Document1 pageMT8888Dan Nguyen VanNo ratings yet

- Rekap Oil AnalysisDocument46 pagesRekap Oil AnalysisSatya SentosaNo ratings yet

- Flender Coupling N-BWNDocument1 pageFlender Coupling N-BWNCharles ChengNo ratings yet

- Jtronics Atmega328 GRBL Controller SchematicDocument1 pageJtronics Atmega328 GRBL Controller SchematicanhxcoNo ratings yet

- Ppaf 1022Document3 pagesPpaf 1022motocelNo ratings yet

- Wits CodesDocument7 pagesWits CodesPablo MartinezNo ratings yet

- Arduino Ethernet SchematicDocument1 pageArduino Ethernet SchematicCostel CostescuNo ratings yet

- Staad 2Document10 pagesStaad 2Norlan BagaNo ratings yet

- B089/B093 Point To Point Diagram: MC 2 MC 4 MC 5 MC 1 MC 3 X2 X6 X4Document15 pagesB089/B093 Point To Point Diagram: MC 2 MC 4 MC 5 MC 1 MC 3 X2 X6 X4Fernando GironNo ratings yet

- HF Waveform Generator Using MAX038Document4 pagesHF Waveform Generator Using MAX038budituxNo ratings yet

- IO Door Board SchematicDocument2 pagesIO Door Board Schematicvilla1960No ratings yet

- CECL08D Datasheet Mp3-PlayerDocument1 pageCECL08D Datasheet Mp3-PlayerGlauber CostaNo ratings yet

- MC 14521Document12 pagesMC 14521rrebollarNo ratings yet

- Pro 1018Document5 pagesPro 1018Phat HoangNo ratings yet

- Noblex - RCD - 138Document8 pagesNoblex - RCD - 138pablo190381No ratings yet

- Arduino Ethernet R3 SchematicDocument1 pageArduino Ethernet R3 SchematicMuchammad Ichiya' Ulumuddin100% (1)

- VA1-5SA: 5) O.O0775) T (2) O.o0283) (0.S) (AD)Document12 pagesVA1-5SA: 5) O.O0775) T (2) O.o0283) (0.S) (AD)Hamzah EizNo ratings yet

- Pepper Mill Power BoardDocument2 pagesPepper Mill Power BoardDaniel DunnNo ratings yet

- My IR2092 V2Document1 pageMy IR2092 V2Jose Marcio CarvalhoNo ratings yet

- ¡ Semiconductor: MSM80C88A-10RS/GS/JSDocument37 pages¡ Semiconductor: MSM80C88A-10RS/GS/JSZarate BismkNo ratings yet

- Arduino Wifi Shield SchematicDocument1 pageArduino Wifi Shield SchematicgetmicrosNo ratings yet

- CD4541 Programmable TimerDocument7 pagesCD4541 Programmable TimerluisNo ratings yet

- 07 Schematic Diagram EDocument6 pages07 Schematic Diagram EGiovanni Mendoza100% (1)

- Eddslfpg PDF 1672217840 PDFDocument48 pagesEddslfpg PDF 1672217840 PDFBarbarosTVNo ratings yet

- LY5A-L2A v4: 8051 Starter KitDocument1 pageLY5A-L2A v4: 8051 Starter KitPrabakaran RamamurthyNo ratings yet

- Product Specifications: Displaytech LTDDocument17 pagesProduct Specifications: Displaytech LTDCarlos Lara CastroNo ratings yet

- Conversor RS232 RS485Document1 pageConversor RS232 RS485Feyyaz Kurt100% (2)

- Servo Part ListDocument2 pagesServo Part ListahmetNo ratings yet

- JAL872 RJCC-RJBB (30-Nov-2023) #1Document16 pagesJAL872 RJCC-RJBB (30-Nov-2023) #1Vrishabh SehgalNo ratings yet

- Friday, March 13, 2020, 03:12 PM: Page 1 of 7 C:/Users/agsamosam - eljoy/Documents/MEPF/MEPF - AnlDocument7 pagesFriday, March 13, 2020, 03:12 PM: Page 1 of 7 C:/Users/agsamosam - eljoy/Documents/MEPF/MEPF - AnlEljoy C. AgsamosamNo ratings yet

- Encapsulado de TransistorDocument2 pagesEncapsulado de TransistorOptimusTronic100% (3)

- Ekchlkpr PDF 1685822894Document30 pagesEkchlkpr PDF 1685822894Emir DurakovicNo ratings yet

- Tecnico Mvd-V5x Cl23300-307 enDocument105 pagesTecnico Mvd-V5x Cl23300-307 enmquaiottiNo ratings yet

- LGSRLGMK PDF 1590577091Document59 pagesLGSRLGMK PDF 1590577091Emerald GrNo ratings yet

- Element o longitu d E (T/cm2) area (cm2) angul o angulo (rad) cos (α) sen (α) (cos (α) ) 2 (sen (α) ) 2 cos (α) *sen (α)Document9 pagesElement o longitu d E (T/cm2) area (cm2) angul o angulo (rad) cos (α) sen (α) (cos (α) ) 2 (sen (α) ) 2 cos (α) *sen (α)Edwin DavidNo ratings yet

- Smartwatch Ram (Ds1216B/C/D/H) Smartwatch Rom (Ds1216E/F) : General Description FeaturesDocument15 pagesSmartwatch Ram (Ds1216B/C/D/H) Smartwatch Rom (Ds1216E/F) : General Description Featuresjoao victorNo ratings yet

- 1216 Overall Wiring Diagram: DB Heater (Option)Document5 pages1216 Overall Wiring Diagram: DB Heater (Option)newionNo ratings yet

- TLV 320 Aic 3101Document95 pagesTLV 320 Aic 3101Amit VajaNo ratings yet

- Andy Mp3 Player SchematicsDocument1 pageAndy Mp3 Player SchematicsSiddhant UtekarNo ratings yet

- PN3687 CentralSemiconductorCorp. Elenota - PLDocument1 pagePN3687 CentralSemiconductorCorp. Elenota - PLbsgkumarNo ratings yet

- 2 N 5556Document1 page2 N 5556Mohaiyedin IdrisNo ratings yet

- Mosfet PDFDocument2 pagesMosfet PDFDiman WardimanNo ratings yet

- 4-5 Conectores Sistema Eléctrico PDFDocument17 pages4-5 Conectores Sistema Eléctrico PDFlevinton jose tobias genesNo ratings yet

- 4-5 Conectores Sistema Eléctrico PDFDocument17 pages4-5 Conectores Sistema Eléctrico PDFlevinton jose tobias genesNo ratings yet

- GATE Agricultural Engineering Paper Answers 2018Document4 pagesGATE Agricultural Engineering Paper Answers 2018kanthaNo ratings yet

- SAVCSAZS PDF 24may18Document32 pagesSAVCSAZS PDF 24may18Fernando CarrizoNo ratings yet

- Cddita - Page11Document1 pageCddita - Page11Harshal AmbatkarNo ratings yet

- Cddita - Page10Document1 pageCddita - Page10Harshal AmbatkarNo ratings yet

- TSMC 180nmDocument2 pagesTSMC 180nmHarshal Ambatkar100% (1)

- Microprocessor FileDocument93 pagesMicroprocessor FileHarshal AmbatkarNo ratings yet

- 8085Document21 pages8085Harshal AmbatkarNo ratings yet

- Power Dissipation DerivationDocument11 pagesPower Dissipation DerivationHarshal AmbatkarNo ratings yet

- Ieee Ieee STD - LOGIC - 1164: Library Use ALLDocument2 pagesIeee Ieee STD - LOGIC - 1164: Library Use ALLHarshal AmbatkarNo ratings yet

- Bidirectional BusDocument1 pageBidirectional BusHarshal AmbatkarNo ratings yet

- RTL Synthesis: Choice-1: Target Expression-1 Choice-2: Target Expression-2 Choice-N: Target Expression-NDocument2 pagesRTL Synthesis: Choice-1: Target Expression-1 Choice-2: Target Expression-2 Choice-N: Target Expression-NHarshal AmbatkarNo ratings yet

- RTL inDocument1 pageRTL inHarshal AmbatkarNo ratings yet

- Pages From Digital Design - An Embedded Systems Approach Using VerilogDocument2 pagesPages From Digital Design - An Embedded Systems Approach Using VerilogHarshal AmbatkarNo ratings yet

- Backup of Final Protel SchematicDocument10 pagesBackup of Final Protel SchematicHarshal AmbatkarNo ratings yet

- LibrariesDocument3 pagesLibrariesHarshal Ambatkar100% (1)

- Void Main Int I WhileDocument1 pageVoid Main Int I WhileHarshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 6Document1 pageAFD Assignment (2k15VLS02) Harshal 6Harshal AmbatkarNo ratings yet