Professional Documents

Culture Documents

X L Sri Xerox: Cell

X L Sri Xerox: Cell

Uploaded by

maheshboobalanOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

X L Sri Xerox: Cell

X L Sri Xerox: Cell

Uploaded by

maheshboobalanCopyright:

Available Formats

ExCEl sri Xerox

CELL;

NAME

98427 21891

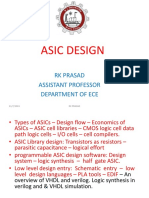

11VL202 APPLICATION SPECIFIC INTEGRATED

CIRCUITS

MODULE - I

15

Introduction to ASICs and Programmable ASICs: Types of ASICs Design flow - CMOS transistors CMOS Design rules -Combinational Logic

Cell Sequential logic cell - Data path logic cell - Transistors as Resistors Transistor Parasitic Capacitance- Logical effort Library cell design -Library

architecture. Programmable ASICs: Anti fuse - static RAM - EPROM and

EEPROM technology - PREP benchmarks- Actel ACT - Xilinx LCA Altera

FLEX.

MODULE - II

15

Interconnects and Design Tools, Logic Synthesis: Altera MAX DC & AC

inputs and outputs -Clock & Power inputs - Xilinx I/O blocks.Actel ACT

-Xilinx LCA - Xilinx EPLD - Altera MAX 5000 and 7000 - Altera

MAX9000 - Altera FLEX Design systems - Logic Synthesis - Half gate

ASIC Schematic entry - Low level design language - PLA tools -EDIF- CFI

design representation.Logic Synthesis: Verilog and logic Synthesis-VHDL

and logic Synthesis.

MODULE III

15

Simulation, Testing and Physical Design: Simulation and Testing: Types of

simulation boundary scan test - fault simulation - automatic test pattern

generation. System partition - FPGA partitioning - partitioning methods floor planning -placement - physical design flow global routing - detailed

routing - special routing -circuit extraction - DRC.

TOTAL: 45

You might also like

- Asic Design: RK Prasad Assistant Professor Department of EceDocument107 pagesAsic Design: RK Prasad Assistant Professor Department of EceSri JalakamNo ratings yet

- METMEL 43 PP2 MNAI SmolaDocument32 pagesMETMEL 43 PP2 MNAI SmolaSrinivas CherukuNo ratings yet

- Application Specific Integrated Circuits (ASIC) : Beit Vii UET TaxilaDocument30 pagesApplication Specific Integrated Circuits (ASIC) : Beit Vii UET TaxilaAsif MahmoodNo ratings yet

- Fpga Based System DesignDocument30 pagesFpga Based System DesignKrishna Kumar100% (1)

- How Does FPGA Work: OutlineDocument17 pagesHow Does FPGA Work: OutlinehariharankalyanNo ratings yet

- Ap7202 Asic and Fpga DesignDocument2 pagesAp7202 Asic and Fpga DesignRajalingam BossNo ratings yet

- Asic Design Cadence DR D Gracia Nirmala RaniDocument291 pagesAsic Design Cadence DR D Gracia Nirmala RaniAdline RiniNo ratings yet

- Module I-ASIC NBBDocument49 pagesModule I-ASIC NBB20D076 SHRIN BNo ratings yet

- Comparison Between ASIC TechnologyDocument12 pagesComparison Between ASIC Technologyasifpatel1234No ratings yet

- Lecture 4Document40 pagesLecture 4Mustjab HussainNo ratings yet

- Introduction To Asics: Ni Logic Pvt. LTD., PuneDocument84 pagesIntroduction To Asics: Ni Logic Pvt. LTD., PuneankurNo ratings yet

- Introduction To Asics: Ni Logic Pvt. LTD., PuneDocument25 pagesIntroduction To Asics: Ni Logic Pvt. LTD., PuneRAJKUMARNo ratings yet

- Product CatalogDocument92 pagesProduct Catalogphani_abkNo ratings yet

- All About Xilinx Xc4020xl-09ht176c FpgaDocument5 pagesAll About Xilinx Xc4020xl-09ht176c FpgajackNo ratings yet

- ASIC 1st Module NOTESDocument29 pagesASIC 1st Module NOTESmanjunathanaikv100% (2)

- Eecs150 - Digital Design: Lecture 3 - Field Programmable Gate Arrays (Fpgas)Document23 pagesEecs150 - Digital Design: Lecture 3 - Field Programmable Gate Arrays (Fpgas)mridul_teotiaNo ratings yet

- Introducción A VHDL: Sistemas Digitales UTM-2009 JjvsDocument48 pagesIntroducción A VHDL: Sistemas Digitales UTM-2009 JjvsAle KeyNo ratings yet

- Introduction To ASIC TechnologyDocument6 pagesIntroduction To ASIC Technologyrpa projectNo ratings yet

- FPGA Architecture and ImplementationDocument59 pagesFPGA Architecture and ImplementationManas BhattNo ratings yet

- ECE 448 - FPGA and ASIC Design With VHDL: George Mason UniversityDocument76 pagesECE 448 - FPGA and ASIC Design With VHDL: George Mason Universityerdvk100% (1)

- 16EC454 ASIC Design SyllabusDocument2 pages16EC454 ASIC Design SyllabusGautami SumanNo ratings yet

- Evolution of Implementation Technologies: Trend Toward Higher Levels of IntegrationDocument18 pagesEvolution of Implementation Technologies: Trend Toward Higher Levels of IntegrationmahmoudNo ratings yet

- Lecture 9Document29 pagesLecture 9Ram MurthyNo ratings yet

- ECE448 Lecture15 ASIC DesignDocument17 pagesECE448 Lecture15 ASIC DesignSunil PandeyNo ratings yet

- AsicDocument2 pagesAsicImmanuel VinothNo ratings yet

- Vlsi Chapter TwoDocument36 pagesVlsi Chapter TwoLemi RajesaNo ratings yet

- AsicDocument1 pageAsicwalternampimadomNo ratings yet

- Unit 5Document62 pagesUnit 5bhupendra1977No ratings yet

- ASIC Design Classification DetailsDocument27 pagesASIC Design Classification Detailsnaveenchand_a6No ratings yet

- Application - Specific.IC DesignFlowDocument8 pagesApplication - Specific.IC DesignFlowNandagopal SivakumarNo ratings yet

- Eecs150 - Digital Design: Lecture 6 - Field Programmable Gate Arrays (Fpgas)Document25 pagesEecs150 - Digital Design: Lecture 6 - Field Programmable Gate Arrays (Fpgas)lambajituNo ratings yet

- Fpga ArchitectureDocument98 pagesFpga ArchitectureKavya Vimal100% (1)

- 11.VLSI DesignDocument44 pages11.VLSI DesignNilesh VermaNo ratings yet

- 14EC770 ASIC DESIGN K.Kalyani PDFDocument270 pages14EC770 ASIC DESIGN K.Kalyani PDFsayooj kNo ratings yet

- Vlsi/Fpga Design and Test CAD Tool Flow in Mentor GraphicsDocument20 pagesVlsi/Fpga Design and Test CAD Tool Flow in Mentor GraphicsaltisinNo ratings yet

- Unit 5Document59 pagesUnit 5Niharika KorukondaNo ratings yet

- Nikhil B. ShahDocument2 pagesNikhil B. ShahnikhilshahbNo ratings yet

- Mr. A. B. Shinde: Assistant Professor, Electronics Engineering, PVPIT, BudhgaonDocument34 pagesMr. A. B. Shinde: Assistant Professor, Electronics Engineering, PVPIT, BudhgaonpremkumarNo ratings yet

- Nelson s09Document47 pagesNelson s09YUE shenNo ratings yet

- Cmos Chip Design OptionsDocument38 pagesCmos Chip Design OptionsAnandhi SrinivasanNo ratings yet

- Asic PPT CompleteDocument504 pagesAsic PPT CompleteSwaroop SNo ratings yet

- Asic Cad SeminarDocument72 pagesAsic Cad Seminarkhoanamhust_24581642No ratings yet

- Integrated Circuits (Ics) Some Applications of IcsDocument3 pagesIntegrated Circuits (Ics) Some Applications of IcsVijay PreethamNo ratings yet

- Programmable Logic Devices: Workshop OnDocument69 pagesProgrammable Logic Devices: Workshop Onshiraz_78678No ratings yet

- ASIC Layout - 2 Standard Cell FlowDocument25 pagesASIC Layout - 2 Standard Cell Flowdiva9jobsNo ratings yet

- LDIC SyllabusDocument3 pagesLDIC SyllabusKumar KeshamoniNo ratings yet

- Soc - Design ASIC+FPGADocument33 pagesSoc - Design ASIC+FPGAUtsav ParasharNo ratings yet

- Unit-1 Op - AmpDocument10 pagesUnit-1 Op - AmpDr A Pradeep Kumar asst.Prof(ECE)No ratings yet

- Spartan-3E: Presentation By: Nilesh A. Shah (P08ec913)Document24 pagesSpartan-3E: Presentation By: Nilesh A. Shah (P08ec913)api-19772070No ratings yet

- Quartus II Training 2Document91 pagesQuartus II Training 2bojan 2No ratings yet

- CPLD and Fpga Architecture and Applications Unit 1Document1 pageCPLD and Fpga Architecture and Applications Unit 1dnachegariNo ratings yet

- Asic and Fpga DesignDocument24 pagesAsic and Fpga DesignGiri ReddyNo ratings yet

- Field-Programmable Gate ArraysDocument14 pagesField-Programmable Gate Arraysநட்ராஜ் நாதன்No ratings yet

- Mentor GraphicsDocument66 pagesMentor Graphicslhari_04No ratings yet

- Vlsi Vlsid Vlsisd Vlsi Me Ece PDFDocument18 pagesVlsi Vlsid Vlsisd Vlsi Me Ece PDFramanaidu1No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- PLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsFrom EverandPLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsRating: 5 out of 5 stars5/5 (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Scheme For Young Scientists and TechnologistsDocument15 pagesScheme For Young Scientists and TechnologistsmaheshboobalanNo ratings yet

- Hybrid Additive Manufacturing TechnologiesDocument11 pagesHybrid Additive Manufacturing TechnologiesmaheshboobalanNo ratings yet

- PLC QPDocument1 pagePLC QPmaheshboobalanNo ratings yet

- LISTnet SharonyDocument100 pagesLISTnet SharonymaheshboobalanNo ratings yet

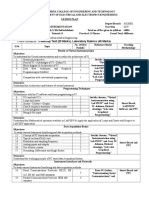

- 3 Monthly Test (20 Marks), Laboratory Rubrics (40 Marks)Document2 pages3 Monthly Test (20 Marks), Laboratory Rubrics (40 Marks)maheshboobalanNo ratings yet

- Presented by S.Keerthi Vasan G.Dinakaran 3rd YEAR - MCT 'A'Document16 pagesPresented by S.Keerthi Vasan G.Dinakaran 3rd YEAR - MCT 'A'maheshboobalanNo ratings yet

- Mechanism Design For Sustainable Virtual Power Plant FormationDocument6 pagesMechanism Design For Sustainable Virtual Power Plant FormationmaheshboobalanNo ratings yet

- IotDocument3 pagesIotmaheshboobalanNo ratings yet

- Measurements and InstrumentationsDocument2 pagesMeasurements and InstrumentationsmaheshboobalanNo ratings yet

- Technical Club ActivityDocument1 pageTechnical Club ActivitymaheshboobalanNo ratings yet

- Forest EcosystemDocument21 pagesForest Ecosystemmaheshboobalan0% (1)

- 3 Monthly Test (20 Marks), Laboratory Rubrics (40 Marks)Document2 pages3 Monthly Test (20 Marks), Laboratory Rubrics (40 Marks)maheshboobalanNo ratings yet

- Bionic LegDocument2 pagesBionic LegmaheshboobalanNo ratings yet

- WWW - Universityquestions.in: Department of Electrical and Electronics EngineeringDocument12 pagesWWW - Universityquestions.in: Department of Electrical and Electronics EngineeringmaheshboobalanNo ratings yet

- Special News 04.12.2016Document3 pagesSpecial News 04.12.2016maheshboobalanNo ratings yet

- Know Yourself:: Tibetan Personality TestDocument24 pagesKnow Yourself:: Tibetan Personality TestmaheshboobalanNo ratings yet

- The Times of India / Cbe /5.12.2016 /P1Document3 pagesThe Times of India / Cbe /5.12.2016 /P1maheshboobalanNo ratings yet

- The Hindu Business Line /cbe /3.12.2016 / P 1 /P1Document1 pageThe Hindu Business Line /cbe /3.12.2016 / P 1 /P1maheshboobalanNo ratings yet

- Chronicle 3.12.2016Document1 pageChronicle 3.12.2016maheshboobalanNo ratings yet

- Hindu 2Document1 pageHindu 2maheshboobalanNo ratings yet

- The Hindu 8.12.2016Document3 pagesThe Hindu 8.12.2016maheshboobalanNo ratings yet

- Lib News 04.12.2016Document2 pagesLib News 04.12.2016maheshboobalanNo ratings yet

- The Times of India 8.12.2016Document1 pageThe Times of India 8.12.2016maheshboobalanNo ratings yet