Professional Documents

Culture Documents

3939 Ijet Ijens

3939 Ijet Ijens

Uploaded by

GarudaOzoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

3939 Ijet Ijens

3939 Ijet Ijens

Uploaded by

GarudaOzoCopyright:

Available Formats

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

SoftSwitched Interleaved Boost Converter with

Quadratic Voltage Gain for Renewable Energy

Applications

Joo Dallamuta, Marcelo Fiori, Mikael Oliveira, Aziz Demian and Lcio R. Barbosa

Universidade Estadual de Londrina, Londrina Paran, Brazil

e-mail: lbarbosa@uel.br

Abstract An efficient soft switching interleaved boost

converter with quadratic voltage gain is presented. Two boostquadratic-topology switching cells are interleaved to minimize

EMI while operating at lower switching frequency and soft

switching to minimize losses. The result is a system with high

conversion efficiency, able to operate in a pulse-widthmodulation (PWM) way. Seven transition states of the soft

switching converter in one switching period are described. In

order to illustrate the operational principle key implementation

details, including simulations, are described. The validity of this

converter is guaranteed by the obtained results.

Index Term Interleaved, Quadratic, Soft-Switched,.

I. INTRODUCTION

The demand of efficient step-up dc-dc converters has been

rising due to the increase of battery powered applications and

low voltage storage elements. Typical applications are

embedded systems, renewable energy systems, fuel cells,

mobility applications and uninterrupted power supply (UPS)

[1], [2] and [3]. These applications demand high step-up static

gain, high efficiency and reduced weight, volume and cost.

Buck, boost, buck-boost, cuk, sepic and zeta are the basic

single-switch topologies that can be used in non-isolated, high

frequency, switch-mode power converters. They are used

mainly in dc-dc converters [4], but sometimes in ac-dc

converters, and are effective in converting the supplied input

voltage to the required output voltage. There are, however,

applications where none of the basic converter topologies are

suitable and alternative topologies need to be considered.

Topologies with different values of voltage gain ((G) can

be produced if basic converters are cascaded with each other.

It is an attractive solution for extreme voltage gain

applications [5], [6]. Nevertheless, it is complex and the cost

is high because two sets of power devices, magnetic cores and

control circuits are required. The system stability with cascade

structure is a big issue and the control circuit should be

designed carefully [7], [8]. The rectifier reverse-recovery

problem is serious in the high voltage side because a high

voltage level should be sustained for the rectifier used in the

high voltage side [9]. Therefore, the efficiency is not high and

the electromagnetic interference (EMI) noise problem is

serious.

It was shown in [10] that such cascaded converters can be

implemented with only a single switch and thus single switch

converters with non-standard conversion ratios can be

synthesized. These converters are frequently referred to as

quadratic converters as G(D) is related to the square of D

(duty cycle).

How to avoid the extreme duty cycle and how to minimize

the current ripple are the major considerations in these

applications. In order to minimize the current ripple, reduce

the passive component size; improve the transient response

and increase the power level, the interleaved structure is

applied in many large current and high power density

applications.

The concept of interleaving several switching cells is not

new, and was originally used as a method for overcoming the

limitations of ordinary power conversion techniques and

device technologies [11]. Recognition of the general merits of

interleaved conversion has prompted a diverse variety of

subsequent investigations, as reflected in the literature.

A number of quadratic converters have been proposed in

the power electronics literature [12-15]. In order to maintain

high switching frequency operation while maximizing the

converter efficiency, soft switching cells are introduced to the

converters.

Most recent development in high frequency converter

configuration is a hybrid of resonant soft switching and pulsewidth-modulation (PWM) control. This group of converters is

called soft switching PWM converters, an example of these

converters are presented in [16]. In the soft switching PWM

converters, the switches operate in resonant mode only during

switching transitions and then, return to PWM operation for

the rest of a switching period.

A comparison of soft switching methods for PWM

converters had shown that passive method has better

efficiency in the high power operation region, while active

method outperforms the passive method in the low power

regions [17]. However, this small improvement in efficiency is

partially countered by higher gate drive losses, higher control

complexity, and lower reliability compared to the passive

method.

In this article, the interleaved power conversion refers to

the strategic interconnection of two switching cells for which

the conversion frequency is identical, but for which the

internal switching instants are sequentially phased over equal

fractions of a switching period. This arrangement applied to

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

quadratic boost converter[18] shown in Fig. 1, combined with

the soft switching technique to lower the switching losses in

the approach proposed in [19-21], can reduce the net ripple

amplitude and raises the effective ripple frequency of the

overall converter without increasing switching losses.

I LB1

I LB 2

10

Vi

(3)

Vi

(4)

1 D 4 R

1 D 3 R

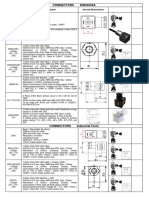

Fig. 1. Quadratic Boost Topology.

The main goal of this system can therefore realize a savings

in filtration and energy storage requirements, resulting in

greatly improved power conversion densities without

sacrificing efficiency.

The features of the proposed converter are discussed in this

paper and the principle of operation, simulation and

experimental results are presented to validate the proposed

solution.

II. PROPOSED STRUCTURE

A. Circuit Description

A configuration of the proposed structure is shown in Fig.

2. This quadratic converter is based on the interleaved Boost

converter, integrated with the proposed soft switching

auxiliary circuit. The quadratic boost converter with a single

active switch is shown in Fig. 1 where Vi is the input voltage,

Vo the output voltage and D the nominal duty ratio. This

converter contains two LC filters, one active switch and three

passive switches. This converter uses only one control circuit

instead of two control circuits required when two basic boost

converters are connected in cascade. In this converter, the DC

voltage gain is a quadratic function of the nominal duty ratio

D, i.e., Vo/Vi = 1/(1-D)2.

As the proposed structure is derived from the quadratic

boost converter, there are two filter inductors for each stage

connected in parallel. The input current ripple is reduced by

the parallel stages operating with different phases. The diodes

DA1 and DA2 are the output diodes and operate like the output

diodes of the interleaved boost converter. The output filter and

load are represented by Co and Ro.

The steady-state operating conditions in continuous

conduction mode can be derived from the ON and OFF

operating conditions of the active switch and diodes.

Continuous conduction mode assumes that the peak inductor

current ripple is smaller than the DC component of the

inductor current; therefore, the total current is always positive.

When all losses are neglected, the steady-state operating

conditions [19] are given by:

VC1 [Vi / (1 D)]

(1)

Vo [Vi / (1 D) ]

(2)

Fig. 2. Proposed Interleaved Boost Converter.

However, the above equations change when interleaving

technique is applied as:

I LB1 I LB 3

I LB 2 I LB 4

Vi

(5)

Vi

(6)

1 D 4 2 R

1 D 3 2 R

The benefits of interleaving can be understood intuitively

using a simple graphical analysis to show how the output

power is shared between two boost switching cells connected

in parallel.

For simultaneous synchronous operation (wherein the

commutation instances of the two controlled switches are

identical), the circuit performance is equivalent to a single

boost converter with equal total energy storage and equal total

semiconductor die area. The inductor and diode ripple current

waveforms that result are shown in Fig. 3 as solid ones.

If these same converter cells are interleaved, such that the

commutation instances of the second switch are delayed

relative to those of the first switch by half a switching period,

the resultant ripple waveforms are those shown as dashed lines

in Fig. 3. Compared to the non-interleaved case with equal

energy storage, the interleaved ripple waveforms have smaller

amplitudes and increased frequencies, reducing the filtration

requirements, as in [19].

In order to simplify the description and the explanation of

the proposed converter, filter inductances LB1, LB2, LB3 and

LB4 are assumed large enough to be considered as ideal current

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

sources. The voltage across Co present no ripple, all

components are treated as being ideal, and the input current

flows through freewheeling diodes DA1 and DA2 until switch

S1 or S2 are turned on at time to. According to its working

cycle, operations modes are described as follows.

11

B. Topological States and Mathematical Analysis

The operation of the circuit will be described considering

the branch 1 (S1), since the branch 2 (S2) operates in the same

way. Based on these assumptions, circuit operations in one

switching cycle can be divided into ten stages. The ten

dynamic equivalent circuits of the new converter during one

switching period is shown in Fig. 4 where the main switch S1

starts conducting at t=t0 and turns off at the time interval t4.

Fig. 3. Dual boost converter ripple waveforms.

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

12

Fig. 4. Topology modes.

In this section, the analytical expressions describing the

operation of the proposed converter are presented. The

following definitions are assumed

o 1 /

LR C R

LR

CR

(8)

I LB1

VC1

LR

CR

(9)

(17)

t 2 (t ) 2 / o

(18)

CR

sin(o )t

LR

iLR1 (t ) I LB 4 Vo

vCR1 (t ) Vo cos(o t )

(7)

I

1 LB 2

Vo

iLR 2 (t ) (VC1 / LR )t

t 2

(19)

(20)

cos (VC1 / Vo )

o

1

(21)

At the end of this stage iLr1 is equal to:

iLR1 (t 2 ) I LB 4

G1 Vo / VC1

(10)

G2 VC1 / Vi

(11)

(12)

G Vo / Vi

The resonant components are assumed to be with the same

values: LR1=LR2=LR3=LR and CR1=CR2=CR.

1) First Mode [t0, t1], Fig. 4(a): Before t=t0, the main

switch S1 maintains turn-off state, the current I LB1 flows

through DB1 and ILB2 through DA1. This stage begins when S1

turns on with ZCS at t=t0. The resonant inductor LR1

discharges linearly due to output voltage Vo from ILB2 + ILB4 to

ILB4. The stage ends when diode DA1 turns off at t=t1. The

resonant iLR1(t), iLR2(t) and vCR1(t) can be respectively

described as:

(13)

iLR1 (t ) I LB 2 I LB 4 (Vo / LR )t

vCR1 (t ) Vo

(14)

iLR 2 (t ) 0

t1 1 / o

(15)

(16)

2) Second Mode [t1, t2], Fig. 4(b): In this stage, the

resonance begins when DR1 turns on at t=t1. The resonant

route proceeds by way of LR1, CR1, S1 and DR1. The resonant

current iLR1(t) decreases and the resonant voltage vCR1(t) also

decreases via the resonance of LR1 and CR1. The resonant

inductor LR2 charges linearly from zero to ILB1. This state ends

when the voltage vCR1(t) reaches capacitor C1 voltage VC1 at

t=t2. The resonant iLR1(t) and vCR1(t) can be respectively

described as:

I LB 2

1

G12

(22)

3) Third Mode [t2, t3], Fig. 4(c): In this mode iLR1(t)

becomes ILB4 due to capacitor voltage VC1. The expression for

iLR1(t) and vCR1(t) are:

iLR1 (t )

VC1

I

1

t I LB 4 LB 2 1 2

LR

1

G1

t3

(23)

vCR1 (t ) VC1

(24)

cos (VC1 / Vo )

o

(25)

4) Fourth Mode [t3, t4], Fig. 4(d): The main switch is

conducting and the currents ILB1 and ILB2 flow through the

power switch. All branch 1 diodes are blocked and the

inductors LB1 and LB2 store energy. The equations that

describe this mode are:

iLR1 (t ) I LB 4

vCR1 (t ) VC1

(26)

(27)

t 4 t5 t 4

(28)

5) Fifth Mode [t4, t5], Fig. 4(e): At the instant t4, switch

S1 is turned-off in a ZVS way and the energy stored in the

inductors LB1 and LB2 is transferred to the resonant capacitor

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

CR1 through the diode DR2. In this time interval, CR1 linearly

charges to zero voltage. The resonant iLR1(t), iLr2(t) and vCR1(t)

can be respectively described as:

iLR1 (t ) I LB 4

iLR 2 (t ) I LB1

vCR1 (t ) VC1 [( I LB1 I LB 2 ) / CR ]t

(29)

(30)

(31)

t5 1 /( 2o 1o G1 )

(32)

6) Sixth Mode [t5, t6], Fig. 4(f): In this stage, the

resonance begins when DB1 turns on at t=t5. The resonant

route proceeds by way of LR2, CR1, DR1, DB2 and DB1. The

resonant current iLR2(t) decreases and the resonant voltage

vCR1(t) increases. This state ends when the current iLR2(t)

reaches zero at t=t6. The resonant iLR2(t) and vCR1(t) can be

respectively described as:

iLR 2 (t ) I LB1 cos(o t )

vCR1 (t ) I LB1

LR

sin(o )t

CR

t 6 /( 2o )

(33)

(34)

13

At the end of this stage, iLR1 is equal to:

1

iLR1 (t8 ) I LB 4 I LLB 2 1 1

1G1

(42)

9) Ninth Mode [t8, t9], Fig. 4(i): When capacitor CR1

voltage becomes Vo diode DR1 is turned on and LR1 current

increases linearly. This stage finishes when the LR1 current

becomes equal to ILB2 +ILB4.

VC1

t

LR

(43)

(1G1 ) 2 1

(44)

iLR1 (t ) iLR1 (t8 )

t9

10) Tenth Mode [t9, t0], Fig. 4(j): During this stage

transference of energy from source to load occurs through

diode DA1, starting another switching cycle.

(35)

7) Seventh Mode [t6, t7], Fig. 4(g): At the instant t7,

switch DB2 is turned-off and the energy stored in the inductor

LB2 is transferred to the resonant capacitor CR1 through the

diode DR2. In this time interval, CR1 linearly discharges to VoVC1. The resonant capacitor voltage vCR1(t) can be described

as:

iLR 2 (t ) 0

vCR1 (t ) 2VC1 ( I LB 2 / CR )t

(36)

(37)

t7 (G1 1 2 ) /(1o G1 )

(38)

iLR1 (t ) I LB 2 I LB 4

vCR1 (t ) Vo

(45)

(46)

iLR 2 (t ) 0

(47)

B. Main Waveforms and Static Gain

The ideal relevant waveforms of the proposed converter is

shown in Fig. 5.

8) Eighth Mode [t7, t8], Fig. 4(h): In this stage, the

resonance begins when DA1 turns on at t=t7. The resonant

route proceeds by way of LR1, C1, DR2, CR1, DA1 and Co. The

resonant current iLR1(t) increases and the resonant voltage

vCR1(t) also increases via the resonance of LR1 and CR1. This

state ends when the voltage vCR1(t) reaches output voltage Vo

at t=t8. The resonant iLR1(t) and vCR1(t) can be respectively

described as:

iLR1 (t ) I LB 4 I LB 2 (1 cos(o t ))

vCR1 (t ) Vo VC1 I LB 2

t8

LR

sin(o t )

CR

sin 1

o

1G1

1

(39)

(40)

(41)

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

14

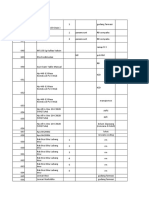

Fig. 6. Static gain curves.

III. DESIGN PROCEDURE

Design of conventional quadratic and interleaved PWM

converters have been well presented in literatures. Thus, it is

more significant to focus on design procedures of the auxiliary

circuit [20]. The resonant inductors and resonant capacitor are

the most important components when designing the auxiliary

circuit. The proposed auxiliary resonant circuit provides softswitching conditions for the main switch. The following

design procedure is developed considering procedures such as

those presented previously in [12-16].

Snubber inductor LR1 is selected to allow its current

decreases from the maximum current (I LB2+ILB4) to ILB4 within

tr time periods, during the turn-on of the main switch. In this

case, from (13), it can be written:

LR1 (Vo / I LB 2 max )t r

(51)

Fig. 5. Ideal relevant waveforms of the topology.

The static gain, which represents the ratio between the

output and the input voltages as function of the duty cycle, can

be obtained by analyzing the voltage waveforms of the

inductor LB1 and/or LB2 observing the time intervals.

After the mathematical analyses, the expression of the static

gain can be obtained:

G2

VC1

1

1 / 1 D

Vi

T

so

G2

VC1

1

1 / 1 D

Vi

T

so

(48)

1

2

2 2 (1 G1 )

(49)

1

2

2 2 (1 G1 )

(50)

G Vo / Vi G1G2

Snubber inductor LR2 is selected to permit its current to rise

up to at most the maximum input current within tr time

periods, during the turn-on of the main switch. In this case,

from (17), it can be written:

LR 2 (VC1 / I LB1 max )tr

where:

tr

- the switching period.

Theses equations provide ZCS turn-on for the transistor.

Snubber capacitor Cr is selected to be discharged from VC1

to zero with the maximum LB1 and LB2 currents over at least

the time period tf during the turn-off of the transistor. For this

state, according to (25) it is obttained

CR [( I LB1max I LB 2 max ) / VC1 ]t r

where:

S - the switching period.

The expression of the static gain is illustrated in Fig. 6.

According to the expressions, it appears clearly that total static

gain G (Fig. 8, when 1=2=) is always higher compared to

the conventional boost converter. Thus, it seems more

appropriate to develop the new quadratic converter, which has

high conversion ratio in a large range of duty cycle.

(52)

(53)

where:

tf

- the fall time of the transistor.

IV. SIMULATION AND EXPERIMENTAL RESULTS

The converter was simulated using simulation software

ORCAD. Figure 7 (a-d) shows the simulation results of the

proposed converter. A prototype of the proposed converter, as

shown in Fig. 2, has been built in the laboratory. The

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

15

experimental waveforms obtained in laboratory are shown

from Fig. 8 (a-d) and were acquired using a THS720

Tektronix oscilloscope and a Tm 502A Tektronix current

gauge The newly proposed converter operates with an input

voltage Vi=50V, output voltage Vo=150V, output power of

400W and a switching frequency of 100KHz. The major

parameters and components are given in Table I.

TABLE I

Components Used in the Proposed Converter

Parameters

Component

Main switches (S1 and S2)

Diodes

Resonant inductor (LR1)

Resonant inductors (LR2 and LR3)

Resonant capacitors (CR1 and CR2)

Filter inductors (LB1 and LB3)

Filter inductors (LB2 and LB4)

Filter capacitor C1and C2

Output capacitor Co

Simulation

Ideal

Ideal

15 H

3.5 H

20.4 nF

450 H

545 H

330 F

330 F

Experimental

SK 60 GAL 125

APT 30D100B

15 H

3.5 H

20.4 nF

450 H

545 H

330 F

330 F

(b)

(c)

Fig. 7. Simulation results.

It is noted from Figures 7(a) and 8(a) that the main switches

are turned on under ZCS. The main switches take the load

current and the charging current of the resonant capacitor. The

resonant capacitor starts to transfer its stored energy to

resonant inductor LR1 during the turn-on period of main

switch. The converter has not exceeded the voltage limits;

however, the current stress is slightly higher for a very short

period. The main switches also turn off under ZVS. The

current and voltage wave shapes are similar to theoretical

waveforms.

It can be seen in Figures 7(b) and 8(b) that after switches

are turned off under ZVS; capacitors CR1 and CR2 are charged.

As soon resonant capacitors reach (Vo-Vc1), the resonance

starts between resonant capacitors and LR1. Figures 7(c) and

8(c) shows the currents in the two input inductors, LB1 and

LB3. In this figure can be verified the delay of half operation

period among the command of these devices. This delay is

responsible by minimization of the input current ripple.

(a)

(a)

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

16

Fig. 10 shows the voltage step up obtained with the

proposed circuit. As expected, one can see that input voltage

increases in the converter.

The efficiency of the power circuit reached at nominal load

is equal to 88%, as shown in Fig. 11. These values were

obtained using a Yokogawa WT230 Digital Power Meter. To

provide a comparative analysis about the efficiency levels

achieved with the laboratory prototype, a converter without

the proposed soft-commutation cell was also built in the

laboratory using the same layout and the same components.

Thus, in this situation, one can conclude that significant

efficiency improvements can be achieved with the application

of the proposed soft commutation cell.

(b)

Fig. 10. Output voltage (Vo) and capacitors voltage (VC1 and VC2).

(c)

Fig. 8. Experimental results.

Fig. 9 shows the current in filter inductor LB1 and input

current Ii. The small oscillation is due to the inductance value.

Fig. 11. Curve of efficiency versus output power.

IV. CONCLUSIONS

The design and performance of a highly efficient

interleaved quadratic boost converter have been described.

Due to the use of standard components, converter can be

considered a viable product prototype for applications where a

high voltage ratio is necessary, what can be the case of fuel

cell applications, but only when transformer isolation is not

required.

Fig. 9. Current in filter inductor ILB1 and input current Ii.

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

International Journal of Engineering & Technology IJET-IJENS Vol:16 No:03

The use of interleaving permits the reduction of conduction

losses in the switches, maintaining a good quality of the input

current, resulting in higher conversion efficiency compared to

non-interleaved quadratic converters. A method for combining

interleaved and quadratic converters to predict ripple

amplitudes has been demonstrated and applied as a design

tool; the use of the auxiliary commutation circuit providing

soft switching of the main switches enable optimization of the

conversion efficiency.

ACKNOWLEDGMENT

This Project was financed by the CNPq (150627/2010-6

process).

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

17

[18] L. Barbosa, E. Coelho, L. Freitas, J. Vieira, and V. Farias. Analysis of a

soft-switched quadratic boost converter. Brazilian Journal of Power

Electronics, Campo Grande, v. 18, n.3, p.1047-1054, jun./aug. 2013.

[19] L. Barbosa, E. Coelho, L. Freitas, J. Vieira, and V. Farias, PWM SoftSwitched Converters with a Single Active Switch Trans. of IEEJ, Inc.

(Industry Applications society), vol. 117-D, no11, pp. 1305-1310,

November 1997.

[20] L. Barbosa, A zero-voltage-transition interleaved boost converter and

its application to pfc Advances in Power Electronics, vol. 2011, pp. 110.

[21] L. Barbosa, E. Coelho, L. Freitas, J. Vieira, and V. Farias. Analysis of a

soft-switched quadratic boost converter. Brazilian Journal of Power

Electronics, Campo Grande, v. 18, n.3, p.1047-1054, jun./aug. 2013

Q. Zhao and F. Lee, High-efficiency, high step-up dc-dc converters,,

IEEE Trans. on Power Electron.., vol. 18, n 1, pp. 65-73, Jan. 2003.

R. Wai and R. Duan, High step-up converter with coupled-inductor

IEEE Trans. on Power Electron., vol. 20, n. 5, pp. 1025-1035, Sep.

2005.

R. Wai and R. Duan, High-efficiency power conversion for low power

fuel cell generation system. IEEE Trans. on Power Electron., vol. 20,

pp. 847-856, Jul. 2005.

D. Maksimovic and S. Cuk, General properties and synthesis of PWM

dc-dc converters, in IEEE Power Electronics Specialists Conference,

pp. 515-525, 1989.

L. Huber and M. Jovanovic, A design approach for server power

supplies for networking, in Proc. IEEE APEC00, 2000, pp. 11631169.

Y. Ren, M. Xu, K. Yao, Y. Meng, and F. Lee, Two-stage approach for

12-V VR, IEEE Trans. Power Electron, vol. 19, no 6, pp. 1498-1506,

Nov, 2001.

X. Feng, J. Liu, and F. Lee, Impedance specifications for stable dc

distributed power systems, IEEE Trans. Power Electron., vol.17, no 2,

pp. 157-162, Mar. 2002.

C. Wildrick, F. Lee, B. Cho, and B. Choi, A method of defining the

load impedance specification for a stable distributed power system

IEEE Trans. Power Electron., vol. 10, no 3, pp. 280-285, May 1995.

W. Li and X. He, A family of interleaved dc-dc converters deduced

from a basic cell with winding-cross-coupled inductors (WCCIs) for

High step-up or step-down conversions IEEE Trans. Power Electron.,

vol. 23, no 4, July 2008.

D. Maksimovic and S. Cuk, Switching converters with wide DC

conversion range, IEEE Transactions on Power Electronics, vol. 6, no.

1, pp. 151-157, Jan. 1991.

D. Garth, W. Muldoon, G. Benson, and E. Costague, Multi-phase, 2

Kilowatt, High Voltage, Regulated Power Supply, IEEE Power

Conditioning Specialists Conference Record, pp. 110-116, 1971.

L. Barreto, E. Coelho, V. Farias, L. Freitas, and J. B. Vieira, A quasiresonant quadratic boost converter using a single resonant network, in

IEEE 2003 Power Electronics Specialists Conference, pp. 595-599,

2003.

L. Barbosa, J. Vieira, L. Freitas, M. Vilela, and V. Farias, A buck

quadratic PWM sof-switching converter using a single active switch,

IEEE Transactions on Power Electronics, vol. 14, pp. 445-453, May

1999.

V. Pacheco, A. Nascimento, V. Farias, J. Vieira, and L. Freitas, A

quadratic buck converter with lossless commutation, IEEE

Transactions on Industrial Electronics, vol. 47, pp. 264-272, April 2000.

A. Pereira, L. Barbosa, J. Rossi, and M. Almeida, A stressless buck

quadratic PWM soft-switched converter, in IEEE International

Telecommunications Energy Conference, pp. 150-155, 2002.

J. Lambert, L. Barbosa, E. Coelho, L. Freitas, J. Vieira, and V. Farias,

A Boost PWM Soft-single-switched converter with low voltage and

current stresses, IEEE Transactions on Power Electronics, vol. 13, no.

1, pp. 16-35, Jan. 1998.

I. Matsuura, K. Smith, and K. Smedley, A comparison of active and

passive soft switching methods for PWM converters, in IEEE 1998

Power Electronics Specialists Conference, pp. 94-100, 1998.

161603-3939-IJET-IJENS June 2016 IJENS

IJENS

You might also like

- Design and Analysis of Algorithms MCQ With Answers PDFDocument21 pagesDesign and Analysis of Algorithms MCQ With Answers PDFTekilu Yewubdar50% (2)

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Cracking Paintshop Pro 8.10 Try&Buy PDFDocument9 pagesCracking Paintshop Pro 8.10 Try&Buy PDFg8117285No ratings yet

- Bidirectional LLC Resonant Converter For Energy Storage ApplicationsDocument7 pagesBidirectional LLC Resonant Converter For Energy Storage ApplicationsRodrigo MesquitaNo ratings yet

- Wide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial ApplicationsDocument14 pagesWide Range Soft Switching PWM Three-Level DC-DC Converters Suitable For Industrial Applicationsstrngr06No ratings yet

- High-Efficient Multilevel Half-Bridge ConverterDocument9 pagesHigh-Efficient Multilevel Half-Bridge Converter'Mantas PuhtėjavasNo ratings yet

- BuckConverter Design Jpe10Document13 pagesBuckConverter Design Jpe10joviflocasNo ratings yet

- High-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniqueDocument9 pagesHigh-Efficiency Active-Clamp Forward Converter With Transient Current Build-Up (TCB) ZVS TechniquekerblaNo ratings yet

- DocumentsDAB EfficiencyDocument6 pagesDocumentsDAB EfficiencyPiyush MenghaniNo ratings yet

- DC Microgrid Nov 30Document9 pagesDC Microgrid Nov 30Ramesh NaiduNo ratings yet

- Digital Two-Loop Controller Design For Fourth Order Split-Inductor ConverterDocument6 pagesDigital Two-Loop Controller Design For Fourth Order Split-Inductor ConverterRaveendhra IitrNo ratings yet

- IET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsDocument10 pagesIET Power Electronics - 2018 - Blinov - Bidirectional Soft Switching DC DC Converter For Battery Energy Storage SystemsHsekum RamukNo ratings yet

- Research Article: On The Development of High Power DC-DC Step-Down Converter With Energy Recovery SnubberDocument10 pagesResearch Article: On The Development of High Power DC-DC Step-Down Converter With Energy Recovery SnubberefremofeNo ratings yet

- A New Single Switch Buck-Boost Type DC-DC ConverterDocument4 pagesA New Single Switch Buck-Boost Type DC-DC ConverterRaveendhra IitrNo ratings yet

- Constant and Green Mode Operation Technique in Flyback and Push-Pull DC-DC ConverterDocument13 pagesConstant and Green Mode Operation Technique in Flyback and Push-Pull DC-DC ConverterIJRASETPublicationsNo ratings yet

- International Journal of Engineering Research and Development (IJERD)Document13 pagesInternational Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- AC/DC Converter With Active Power Factor Correction Applied To DC Motor DriveDocument9 pagesAC/DC Converter With Active Power Factor Correction Applied To DC Motor DriveIJERDNo ratings yet

- Non Isolated Bidirectional DC DC ConverterDocument6 pagesNon Isolated Bidirectional DC DC ConverterAnuja VargheseNo ratings yet

- Conference-201410-Shahzad-LLC Series Resonant Converter With PID Controller For Battery Charging ApplicationDocument6 pagesConference-201410-Shahzad-LLC Series Resonant Converter With PID Controller For Battery Charging ApplicationTocean DuongNo ratings yet

- A Fixed-Frequency Soft-Switched Interleaved 3-Phase AC-to-DC ConverterDocument6 pagesA Fixed-Frequency Soft-Switched Interleaved 3-Phase AC-to-DC ConvertersasikalaNo ratings yet

- Switched Inductor Z-Source Matrix Converter Operation and AnalysisDocument9 pagesSwitched Inductor Z-Source Matrix Converter Operation and AnalysisA'Platinum EngNo ratings yet

- I J Seas 20160123Document10 pagesI J Seas 20160123Eugin RajNo ratings yet

- Analysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesDocument6 pagesAnalysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesPrema Vinod PatilNo ratings yet

- 9.eee Ijeee Two Phase Interleaved DC SumalathaDocument16 pages9.eee Ijeee Two Phase Interleaved DC Sumalathaiaset123No ratings yet

- A State Space Modeling of Non-Isolated BidirectionDocument11 pagesA State Space Modeling of Non-Isolated BidirectionabdullahshahidNo ratings yet

- Two-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterDocument9 pagesTwo-Loop Voltage-Mode Control of Coupled Inductor Step-Down Buck ConverterRaveendhra IitrNo ratings yet

- Design and Simulation of Single Phase Z-Source Buck Boost Matrix ConverterDocument7 pagesDesign and Simulation of Single Phase Z-Source Buck Boost Matrix Convertervinay kumarNo ratings yet

- Single Phase To Three Phase SystemDocument57 pagesSingle Phase To Three Phase SystemASK projects100% (1)

- Design of Transformer-Less DC To AC Converter Using PWM TechniqueDocument6 pagesDesign of Transformer-Less DC To AC Converter Using PWM TechniqueHariesh WaranNo ratings yet

- Step Down PSIMDocument6 pagesStep Down PSIMAnonymous W44hzJ9roNo ratings yet

- An Improved Soft-Switching Buck Converter With Coupled InductorDocument7 pagesAn Improved Soft-Switching Buck Converter With Coupled InductorSanthosh GuduruNo ratings yet

- 1) A Three-Phase Soft-Switched High-Power-Density DC-DC ConverterDocument11 pages1) A Three-Phase Soft-Switched High-Power-Density DC-DC Converteralberfilba2No ratings yet

- A Single Stage CCM Zeta Microinverter For Solar Photovoltaic AC ModuleDocument9 pagesA Single Stage CCM Zeta Microinverter For Solar Photovoltaic AC ModuleChristian EmenikeNo ratings yet

- Soft Switched High Step-Up DC-DC Converter For Automotive ApplicationDocument4 pagesSoft Switched High Step-Up DC-DC Converter For Automotive Applicationkarthi.r.tNo ratings yet

- Predictive Current Controlled 5-kW Single-Phase Bidirectional Inverter With Wide Inductance Variation For DC-Microgrid ApplicationsDocument9 pagesPredictive Current Controlled 5-kW Single-Phase Bidirectional Inverter With Wide Inductance Variation For DC-Microgrid ApplicationsJitender KaushalNo ratings yet

- 1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - KheraluwalaDocument8 pages1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - Kheraluwalahafizabu123No ratings yet

- Comparative AnalysisDocument6 pagesComparative AnalysisDrVikas Singh BhadoriaNo ratings yet

- Modelling and Control of A Novel Zero-Current-Switching Inverter With Sinusoidal Current OutputDocument11 pagesModelling and Control of A Novel Zero-Current-Switching Inverter With Sinusoidal Current OutputSuresh KumarNo ratings yet

- Design of Step-Up Converter For A Constant Output in A High Power DesignDocument5 pagesDesign of Step-Up Converter For A Constant Output in A High Power DesignshaheerdurraniNo ratings yet

- Analytical Model of The Half-Bridge Series Resonant Inverter For Improved Power Conversion Efficiency and PerformanceDocument4 pagesAnalytical Model of The Half-Bridge Series Resonant Inverter For Improved Power Conversion Efficiency and PerformanceMaruthi JacsNo ratings yet

- Two-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingDocument8 pagesTwo-Stage H-Bridge Transformer Coupled DC-DC Converter With Zero Voltage SwitchingRakeshconclaveNo ratings yet

- Electrical AnalyzerDocument8 pagesElectrical AnalyzerrhusheinNo ratings yet

- A Two Stage Buck Boost Converter With SoDocument7 pagesA Two Stage Buck Boost Converter With Sodd1663No ratings yet

- A New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarDocument7 pagesA New Method For DC-AC Conversion Using Simplified Multilevel Inverter - Design and Analysis Using PSIM 1. V.Gowri Shankar, 2.C.UdhayashankarraghuevmNo ratings yet

- Ijert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterDocument9 pagesIjert: Power Stress Reduction in Single-Stage Power Factor Correction by AC/DC Fly Back ConverterAnjali SharmaNo ratings yet

- A New Single-Phase Single-Stage Three-LevelDocument12 pagesA New Single-Phase Single-Stage Three-LevelGururaj BandaNo ratings yet

- Ripple Current Reduction Technique For DC To DC Converter Using Tapped InductorDocument6 pagesRipple Current Reduction Technique For DC To DC Converter Using Tapped InductorInternational Journal of Latest Research in Engineering and TechnologyNo ratings yet

- Soft Switching DC DC ConvertersDocument114 pagesSoft Switching DC DC ConvertersRAJESHNo ratings yet

- 6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFDocument12 pages6high Power Full-Bridge DC-DC Converter Using A Center-Tapped Transformer and A Full-Wave Type Rectifier PDFmajidNo ratings yet

- A High-Efficiency Step-Up Current-Fed PushPull Quasi-Resonant Converter With Fewer Components For Fuel Cell ApplicationDocument10 pagesA High-Efficiency Step-Up Current-Fed PushPull Quasi-Resonant Converter With Fewer Components For Fuel Cell ApplicationManuel DíazNo ratings yet

- Topic Assignment14Document6 pagesTopic Assignment14cuongakamarineNo ratings yet

- High Efficiency and High Power Factor Single-Stage Balanced Forward-Flyback ConverterDocument6 pagesHigh Efficiency and High Power Factor Single-Stage Balanced Forward-Flyback ConverterKarthik KumarNo ratings yet

- Nonisolated High Step-Up Boost Converter Integrated With Sepic ConverterDocument10 pagesNonisolated High Step-Up Boost Converter Integrated With Sepic ConverterShirlyNo ratings yet

- Ircuit Onfiguration and Perating OdesDocument3 pagesIrcuit Onfiguration and Perating OdesMukul DasNo ratings yet

- Analysis and Comparison of DC-DC Boost Converters With High Voltage Conversion RatioDocument10 pagesAnalysis and Comparison of DC-DC Boost Converters With High Voltage Conversion RatioKrishnaveni Subramani SNo ratings yet

- Analysis of High Frequency Multi-Phase Multi-Stage Boost ConverterDocument7 pagesAnalysis of High Frequency Multi-Phase Multi-Stage Boost ConverterKaruna MudliyarNo ratings yet

- A Novel Soft-Switching Synchronous Buck Converter For Portable ApplicationsDocument8 pagesA Novel Soft-Switching Synchronous Buck Converter For Portable ApplicationsPavan Kumar MaddukuriNo ratings yet

- Implementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerDocument6 pagesImplementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerAlonso CoradoNo ratings yet

- 135264ijsetr6989 1453Document8 pages135264ijsetr6989 1453wasabikikkomanNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Geomatics in Civil EngineeringDocument2 pagesGeomatics in Civil EngineeringGarudaOzoNo ratings yet

- A Not-To-Be-Missed Community Engagement Event! Join The Who's Who of The Engagement World!Document9 pagesA Not-To-Be-Missed Community Engagement Event! Join The Who's Who of The Engagement World!GarudaOzoNo ratings yet

- A Perfect Venue For Your AND: MeetingsDocument14 pagesA Perfect Venue For Your AND: MeetingsGarudaOzoNo ratings yet

- Hip Dips WorkoutDocument1 pageHip Dips WorkoutGarudaOzoNo ratings yet

- Killer Legs WorkoutDocument1 pageKiller Legs WorkoutGarudaOzoNo ratings yet

- Neural Network Implementation of Nonlinear Receding-Horizon ControlDocument7 pagesNeural Network Implementation of Nonlinear Receding-Horizon ControlGarudaOzoNo ratings yet

- The Construction of Regular Semigroups With Medial IdempotentDocument4 pagesThe Construction of Regular Semigroups With Medial IdempotentGarudaOzoNo ratings yet

- 3939 Ijmme IjensDocument6 pages3939 Ijmme IjensGarudaOzoNo ratings yet

- Greens TheoremDocument16 pagesGreens TheoremGarudaOzo100% (1)

- In Depth Study For Developing Efficient Direct Somatic Embryogenesis of Jatropha Curcas L.: Morphology and UltrastructureDocument9 pagesIn Depth Study For Developing Efficient Direct Somatic Embryogenesis of Jatropha Curcas L.: Morphology and UltrastructureGarudaOzoNo ratings yet

- 5959 Ijmme Ijens PDFDocument5 pages5959 Ijmme Ijens PDFGarudaOzoNo ratings yet

- Network Analysis On Safety Culture and Worker S Behaviour: A Forest of All Minimum Spanning TreesDocument9 pagesNetwork Analysis On Safety Culture and Worker S Behaviour: A Forest of All Minimum Spanning TreesGarudaOzoNo ratings yet

- 1604 2525 Ijmme IjensDocument6 pages1604 2525 Ijmme IjensGarudaOzoNo ratings yet

- ISO 27001 Controls ListDocument4 pagesISO 27001 Controls ListIlkontisa HalimaNo ratings yet

- Low Power and Area-Efficient Carry Select Adder: K.SaranyaDocument4 pagesLow Power and Area-Efficient Carry Select Adder: K.Saranyapraba821No ratings yet

- 04.licenciamiento Del MicroSCADADocument10 pages04.licenciamiento Del MicroSCADALiz Victoria Bautista CardenasNo ratings yet

- The Best Web HostingDocument14 pagesThe Best Web HostingVladan GolubovicNo ratings yet

- Thesis Engineering ExampleDocument6 pagesThesis Engineering Examplebsr22d1d100% (2)

- MMC (8051)Document95 pagesMMC (8051)vinit kumarNo ratings yet

- When Technology and Humanity Cross MACUGAY EVA BDocument13 pagesWhen Technology and Humanity Cross MACUGAY EVA BAika GonzalesNo ratings yet

- Assembly Instructions MX 401Document15 pagesAssembly Instructions MX 401Gabriel GarciaNo ratings yet

- BA6209Document9 pagesBA6209sontuyet82No ratings yet

- Solenoid Valve Cable PlugDocument1 pageSolenoid Valve Cable Plugstenio augustoNo ratings yet

- ThermalDocument15 pagesThermalJulián MoranNo ratings yet

- Roadmap ICT For The Top Sectors Revised March 20Document65 pagesRoadmap ICT For The Top Sectors Revised March 20trainingmomentNo ratings yet

- Admit Card: West Bengal Joint Entrance Examinations Board WBJEE-2021Document1 pageAdmit Card: West Bengal Joint Entrance Examinations Board WBJEE-2021Vibhu SinghNo ratings yet

- Plotly TutorialDocument95 pagesPlotly TutorialWeijie Chen100% (1)

- Electronics Workbench: Multimcu Microcontroller Co-SimulationDocument48 pagesElectronics Workbench: Multimcu Microcontroller Co-SimulationShyamal Jyoti BuragohainNo ratings yet

- Asmodian Leveling Guide by CinereaDocument67 pagesAsmodian Leveling Guide by CinereaDavid AntonioNo ratings yet

- Aset Sem 1 Tahun 2018 LaporDocument81 pagesAset Sem 1 Tahun 2018 LaporARISSUPARDINo ratings yet

- HikCentral V1.3.2 - FAQ - 20190131Document51 pagesHikCentral V1.3.2 - FAQ - 20190131giorgiNo ratings yet

- DSm735 DSm745 BrochureDocument6 pagesDSm735 DSm745 BrochurepuiutdragonNo ratings yet

- BAHrain Lib SystemDocument15 pagesBAHrain Lib Systembgtes123No ratings yet

- Schema ExamplesDocument18 pagesSchema ExamplesPatel VaidikNo ratings yet

- BDM TaherDocument4 pagesBDM TaherTaher El HassanNo ratings yet

- Mehra 1970Document10 pagesMehra 1970Imane IdrissiNo ratings yet

- ANSI-IsA S84.01 (1996) Application of Safety Instrumented Systems For The Process IndustriesDocument110 pagesANSI-IsA S84.01 (1996) Application of Safety Instrumented Systems For The Process IndustriesEsteban TobarNo ratings yet

- Inter Company Invoicing ProcessDocument1 pageInter Company Invoicing Processaj9055537No ratings yet

- Multibranch Forging Algorithms: Tails Switching Effect and Chain MeasuresDocument15 pagesMultibranch Forging Algorithms: Tails Switching Effect and Chain MeasuresandruimanNo ratings yet

- Magelis GXO - HMIGXO3502Document6 pagesMagelis GXO - HMIGXO3502enkzNo ratings yet

- Assembly Language Coding (ALC) Part 3Document80 pagesAssembly Language Coding (ALC) Part 3Krystal Meeth100% (3)