Professional Documents

Culture Documents

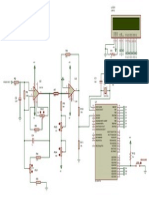

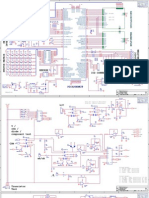

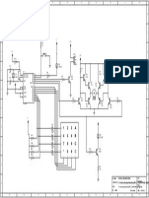

UChip PIC16F72 Based Relay TIMER Board Circuit

UChip PIC16F72 Based Relay TIMER Board Circuit

Uploaded by

shalu29Copyright:

Available Formats

You might also like

- k150 SchematicDocument1 pagek150 SchematicRogelio Badachi Rivera67% (3)

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaNo ratings yet

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesNo ratings yet

- Vin IC2Document1 pageVin IC2Harish Kumar MNo ratings yet

- Noblex - RCD - 138Document8 pagesNoblex - RCD - 138pablo190381No ratings yet

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- ScaleDocument1 pageScaleMarc Justin Cardenas ChanNo ratings yet

- PH METER WITH PIC PDFDocument1 pagePH METER WITH PIC PDFk_n_sreekumar100% (2)

- CAN DemoDocument1 pageCAN DemoTrí Nguyễn100% (1)

- Schematic 13Document1 pageSchematic 13api-203437529No ratings yet

- DFR0063 v1.2 SchematicDocument1 pageDFR0063 v1.2 SchematicVasi ValiNo ratings yet

- Week 8Document1 pageWeek 8zzzsamuraizzzNo ratings yet

- Two Serial + LCDDocument1 pageTwo Serial + LCDsajitsukumaran5719100% (3)

- SCH Code Access Sys k639Document1 pageSCH Code Access Sys k639Gaurav SharmaNo ratings yet

- Mach Nguyen LyDocument1 pageMach Nguyen LyQuyết CherryNo ratings yet

- Cpu Logic DiagramDocument0 pagesCpu Logic DiagramMauricio RaúlNo ratings yet

- PIC18LF4550 STK1 Rev3aDocument1 pagePIC18LF4550 STK1 Rev3aEmilio Escalante100% (1)

- MMB0 RevC SchematicDocument1 pageMMB0 RevC SchematicbiotekyNo ratings yet

- 16f887 DoublemeternosimDocument1 page16f887 DoublemeternosimSan Lug Oma100% (1)

- Phan CungDocument1 pagePhan CungNguyen Anh Tuan100% (1)

- Vh-2C Programador de Pics Realizado Por: Víctor Hugo CaizaDocument1 pageVh-2C Programador de Pics Realizado Por: Víctor Hugo CaizaJuan Luis Carr100% (1)

- FPP3Document1 pageFPP3uzunku100% (1)

- Schematic PrintsDocument1 pageSchematic PrintsQuỳnh Quỷ QuyệtNo ratings yet

- DOP7Document1 pageDOP7Mor Se100% (1)

- Automatic HandbrakeDocument1 pageAutomatic HandbrakeMidhun ViswamNo ratings yet

- CidfrDocument3 pagesCidfrRey LuckytronicNo ratings yet

- Q9T4 FP91G Interface BDDocument5 pagesQ9T4 FP91G Interface BDax63naNo ratings yet

- SCH CpuDocument1 pageSCH CpuWilliams Giorgio Sicsu100% (2)

- VCC 12V: PR14 SchematicDocument1 pageVCC 12V: PR14 SchematicHazmi HanifNo ratings yet

- Coma SchematicsDocument3 pagesComa SchematicsvacsaaNo ratings yet

- Driver StepDocument1 pageDriver StepTam Phuong NguyenNo ratings yet

- PDF Created With Pdffactory Pro Trial Version: Rtd2660 Rtd2660Document7 pagesPDF Created With Pdffactory Pro Trial Version: Rtd2660 Rtd2660kvp61327No ratings yet

- Schem AnticDocument1 pageSchem Anticthanhv_25100% (1)

- Nguyen LyDocument1 pageNguyen LynguyentuandangNo ratings yet

- User Manual (89v51rd2)Document4 pagesUser Manual (89v51rd2)rahul_kumbhar05No ratings yet

- Schematic - Pic ModuleDocument1 pageSchematic - Pic ModuleDuc Le100% (1)

- Nguyen Ly PDFDocument1 pageNguyen Ly PDFPhạmLãiNo ratings yet

- PIC Micro Project BoardDocument1 pagePIC Micro Project BoardOkiPetrus Hutauruk LumbanBaringinNo ratings yet

- 8 Led Array 16X2 LCD Display Connector Push Botton SwitchDocument1 page8 Led Array 16X2 LCD Display Connector Push Botton SwitchHarsh BoradNo ratings yet

- LCD LCD: MCLR Led1 Led2 Led3 Led4 RXD MCLRDocument1 pageLCD LCD: MCLR Led1 Led2 Led3 Led4 RXD MCLRChu Trọng Khanh100% (1)

- Pass DooorDocument1 pagePass DooorSHAHID_71No ratings yet

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- 1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency CounterDocument1 page1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency Counteredosvirac100% (1)

- Mach Ngly Sim300czDocument2 pagesMach Ngly Sim300czViet Bui QuocNo ratings yet

- Circuito PICDocument1 pageCircuito PICEuber Chaia100% (1)

- Schematic1 - PagepicDocument1 pageSchematic1 - PagepicSói Ăn RauNo ratings yet

- (Codientu - Org) Sodomach-NguyenlyDocument1 page(Codientu - Org) Sodomach-NguyenlyQuy Nhơn Điện tửNo ratings yet

- K12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz PredmetaDocument1 pageK12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz Predmetammmmm1900100% (2)

- Programming Section Extention Section: Port B1 J17Document2 pagesProgramming Section Extention Section: Port B1 J17prateekgupta900No ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Schema 151Document4 pagesSchema 151bubu tymonNo ratings yet

- GLCD TestDocument1 pageGLCD TestTran Chi QuyetNo ratings yet

- Battery Charger Vanson V 6988Document1 pageBattery Charger Vanson V 6988Mcmu Adalah WDkuNo ratings yet

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocument27 pagesDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisNo ratings yet

- Reflow Toaster v2 SchematicDocument1 pageReflow Toaster v2 SchematicBest PC BoxNo ratings yet

- Poxi - Hardware Schematics PDFDocument1 pagePoxi - Hardware Schematics PDFsheshanth_asNo ratings yet

- TL866 Schematic DiagramDocument4 pagesTL866 Schematic Diagramradioman_35100% (5)

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Servo Stabilizer ControllerDocument39 pagesServo Stabilizer Controllershalu29No ratings yet

- Selecting Laboratory Tests To Predict Effectiveness of Retention and Drainage Aid ProgrammesDocument14 pagesSelecting Laboratory Tests To Predict Effectiveness of Retention and Drainage Aid Programmesshalu29No ratings yet

- Sinewave Inverter DC Capacitor Ripple CurrentDocument6 pagesSinewave Inverter DC Capacitor Ripple Currentshalu29No ratings yet

- Chemical Details For Paper IndustriesDocument2 pagesChemical Details For Paper Industriesshalu29No ratings yet

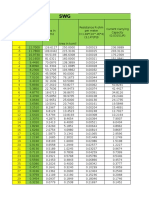

- SWG & MM ConversionDocument70 pagesSWG & MM Conversionshalu2980% (10)

UChip PIC16F72 Based Relay TIMER Board Circuit

UChip PIC16F72 Based Relay TIMER Board Circuit

Uploaded by

shalu29Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UChip PIC16F72 Based Relay TIMER Board Circuit

UChip PIC16F72 Based Relay TIMER Board Circuit

Uploaded by

shalu29Copyright:

Available Formats

1

1

2

3

JP6

JST3

VDD

R14

RA5

1K

MCLR

JP3

JP1

Vin

3

2

1

VDD

1

Q2

2

4.7K

BUZ 3

+ C5

RS (LCD) 4

47uF/63V

En (LCD) 5

6

RA5

7

GND 8

OSC1 9

OSC2 10

Q8

11

X1

Q9

12

XTAL

Q7

13

14

P3

CPU3/3.96

C

JP2

C8

RB7

RB6

GND

VDD

MCLR

5

4

3

2

1

33pF

Vin

RELAY8

RELAY9

RELAY1

RELAY2

U?

R4

C9

MCLR/VPP

RB7/PGD

RA0

RB6/PGC

RA1

RB5

RA2

RB4

RA3

RB3

RA4

RB2

RA5

RB1

PIC16F72

GND

RB0

OSC1

VDD

OSC2

GND

RC0

RC7

RC1

RC6

RC2

RC5

RC3

RC4

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RB7

RB6

Q4

Q5

D7 (LCD)

D6 (LCD)

D5 (LCD)

D4 (LCD)

VDD

GND

Q1

Q6

P1

P2

1

2

3

4

5

CPU5/5.96

C

C7

100nF

+ C6

10uF/63V

JP7

Vin

RELAY4

RELAY5

RELAY6

RELAY7

JST5

33pF

1

2

3

4

5

CPU5/5.96

J?

GND

P1

P2

P3

VDD

220K

2.2K

2.2K

R13

R9

R7

R6

CON4

D1,2,3,4,4,5,6,7,8

1N4007

VDD

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

BUZ

Vin

2.7K

- (LCD)

+ (LCD)

D7 (LCD)

D6 (LCD)

D5 (LCD)

D4 (LCD)

D3 (LCD)

D2 (LCD)

D1 (LCD)

D0 (LCD)

En (LCD)

R/W

RS (LCD)

CONTRAST

VDD

GND

4

3

2

1

Q1

JP5 REL16

Q1,2,4,5,6,7,8,9

BD139

R3,2,5,10,11,12,15,16

2.2K

5V

Q3

R8

BUZ

470E

NPN

A

Title

Size

Number

Revision

B

Date:

File:

1

8-Oct-2016

Sheet of

D:\Water Level Complete\Circuits\FINAL CIRCUIT\WATER

Drawn By:

LEVEL CIRCUIT.ddb

6

You might also like

- k150 SchematicDocument1 pagek150 SchematicRogelio Badachi Rivera67% (3)

- LAB-X1 SchematicDocument2 pagesLAB-X1 SchematicRenato MirandaNo ratings yet

- Labx 1 SCHDocument2 pagesLabx 1 SCHercervantesNo ratings yet

- Vin IC2Document1 pageVin IC2Harish Kumar MNo ratings yet

- Noblex - RCD - 138Document8 pagesNoblex - RCD - 138pablo190381No ratings yet

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- ScaleDocument1 pageScaleMarc Justin Cardenas ChanNo ratings yet

- PH METER WITH PIC PDFDocument1 pagePH METER WITH PIC PDFk_n_sreekumar100% (2)

- CAN DemoDocument1 pageCAN DemoTrí Nguyễn100% (1)

- Schematic 13Document1 pageSchematic 13api-203437529No ratings yet

- DFR0063 v1.2 SchematicDocument1 pageDFR0063 v1.2 SchematicVasi ValiNo ratings yet

- Week 8Document1 pageWeek 8zzzsamuraizzzNo ratings yet

- Two Serial + LCDDocument1 pageTwo Serial + LCDsajitsukumaran5719100% (3)

- SCH Code Access Sys k639Document1 pageSCH Code Access Sys k639Gaurav SharmaNo ratings yet

- Mach Nguyen LyDocument1 pageMach Nguyen LyQuyết CherryNo ratings yet

- Cpu Logic DiagramDocument0 pagesCpu Logic DiagramMauricio RaúlNo ratings yet

- PIC18LF4550 STK1 Rev3aDocument1 pagePIC18LF4550 STK1 Rev3aEmilio Escalante100% (1)

- MMB0 RevC SchematicDocument1 pageMMB0 RevC SchematicbiotekyNo ratings yet

- 16f887 DoublemeternosimDocument1 page16f887 DoublemeternosimSan Lug Oma100% (1)

- Phan CungDocument1 pagePhan CungNguyen Anh Tuan100% (1)

- Vh-2C Programador de Pics Realizado Por: Víctor Hugo CaizaDocument1 pageVh-2C Programador de Pics Realizado Por: Víctor Hugo CaizaJuan Luis Carr100% (1)

- FPP3Document1 pageFPP3uzunku100% (1)

- Schematic PrintsDocument1 pageSchematic PrintsQuỳnh Quỷ QuyệtNo ratings yet

- DOP7Document1 pageDOP7Mor Se100% (1)

- Automatic HandbrakeDocument1 pageAutomatic HandbrakeMidhun ViswamNo ratings yet

- CidfrDocument3 pagesCidfrRey LuckytronicNo ratings yet

- Q9T4 FP91G Interface BDDocument5 pagesQ9T4 FP91G Interface BDax63naNo ratings yet

- SCH CpuDocument1 pageSCH CpuWilliams Giorgio Sicsu100% (2)

- VCC 12V: PR14 SchematicDocument1 pageVCC 12V: PR14 SchematicHazmi HanifNo ratings yet

- Coma SchematicsDocument3 pagesComa SchematicsvacsaaNo ratings yet

- Driver StepDocument1 pageDriver StepTam Phuong NguyenNo ratings yet

- PDF Created With Pdffactory Pro Trial Version: Rtd2660 Rtd2660Document7 pagesPDF Created With Pdffactory Pro Trial Version: Rtd2660 Rtd2660kvp61327No ratings yet

- Schem AnticDocument1 pageSchem Anticthanhv_25100% (1)

- Nguyen LyDocument1 pageNguyen LynguyentuandangNo ratings yet

- User Manual (89v51rd2)Document4 pagesUser Manual (89v51rd2)rahul_kumbhar05No ratings yet

- Schematic - Pic ModuleDocument1 pageSchematic - Pic ModuleDuc Le100% (1)

- Nguyen Ly PDFDocument1 pageNguyen Ly PDFPhạmLãiNo ratings yet

- PIC Micro Project BoardDocument1 pagePIC Micro Project BoardOkiPetrus Hutauruk LumbanBaringinNo ratings yet

- 8 Led Array 16X2 LCD Display Connector Push Botton SwitchDocument1 page8 Led Array 16X2 LCD Display Connector Push Botton SwitchHarsh BoradNo ratings yet

- LCD LCD: MCLR Led1 Led2 Led3 Led4 RXD MCLRDocument1 pageLCD LCD: MCLR Led1 Led2 Led3 Led4 RXD MCLRChu Trọng Khanh100% (1)

- Pass DooorDocument1 pagePass DooorSHAHID_71No ratings yet

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- 1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency CounterDocument1 page1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency Counter 1,3Ghz Frequency Counteredosvirac100% (1)

- Mach Ngly Sim300czDocument2 pagesMach Ngly Sim300czViet Bui QuocNo ratings yet

- Circuito PICDocument1 pageCircuito PICEuber Chaia100% (1)

- Schematic1 - PagepicDocument1 pageSchematic1 - PagepicSói Ăn RauNo ratings yet

- (Codientu - Org) Sodomach-NguyenlyDocument1 page(Codientu - Org) Sodomach-NguyenlyQuy Nhơn Điện tửNo ratings yet

- K12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz PredmetaDocument1 pageK12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz Predmetammmmm1900100% (2)

- Programming Section Extention Section: Port B1 J17Document2 pagesProgramming Section Extention Section: Port B1 J17prateekgupta900No ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Schema 151Document4 pagesSchema 151bubu tymonNo ratings yet

- GLCD TestDocument1 pageGLCD TestTran Chi QuyetNo ratings yet

- Battery Charger Vanson V 6988Document1 pageBattery Charger Vanson V 6988Mcmu Adalah WDkuNo ratings yet

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocument27 pagesDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisNo ratings yet

- Reflow Toaster v2 SchematicDocument1 pageReflow Toaster v2 SchematicBest PC BoxNo ratings yet

- Poxi - Hardware Schematics PDFDocument1 pagePoxi - Hardware Schematics PDFsheshanth_asNo ratings yet

- TL866 Schematic DiagramDocument4 pagesTL866 Schematic Diagramradioman_35100% (5)

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Servo Stabilizer ControllerDocument39 pagesServo Stabilizer Controllershalu29No ratings yet

- Selecting Laboratory Tests To Predict Effectiveness of Retention and Drainage Aid ProgrammesDocument14 pagesSelecting Laboratory Tests To Predict Effectiveness of Retention and Drainage Aid Programmesshalu29No ratings yet

- Sinewave Inverter DC Capacitor Ripple CurrentDocument6 pagesSinewave Inverter DC Capacitor Ripple Currentshalu29No ratings yet

- Chemical Details For Paper IndustriesDocument2 pagesChemical Details For Paper Industriesshalu29No ratings yet

- SWG & MM ConversionDocument70 pagesSWG & MM Conversionshalu2980% (10)