Professional Documents

Culture Documents

Fault Tolerance & Reliability CDA 5140 Chapter 2 - Cyclic Polynomial Codes

Fault Tolerance & Reliability CDA 5140 Chapter 2 - Cyclic Polynomial Codes

Uploaded by

RiazAhmadCopyright:

Available Formats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5825)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Explain Memory-Reference Instructions. Ans. Memory Reference InstructionsDocument23 pagesExplain Memory-Reference Instructions. Ans. Memory Reference Instructionsshikha100% (1)

- CalculusDocument38 pagesCalculuspranit100% (1)

- Band Gap - PVEducationDocument3 pagesBand Gap - PVEducationRiazAhmadNo ratings yet

- Basic Equations - PVEducationDocument3 pagesBasic Equations - PVEducationRiazAhmadNo ratings yet

- Base Resistance - PVEducationDocument2 pagesBase Resistance - PVEducationRiazAhmadNo ratings yet

- Simulation of Layer Thickness PDFDocument5 pagesSimulation of Layer Thickness PDFRiazAhmadNo ratings yet

- Evolution of Energy Policies in Pakistan and Future PerspectsDocument22 pagesEvolution of Energy Policies in Pakistan and Future PerspectsRiazAhmadNo ratings yet

- Absorption Coefficient - PVEducationDocument3 pagesAbsorption Coefficient - PVEducationRiazAhmadNo ratings yet

- ModelDocument1 pageModelRiazAhmadNo ratings yet

- Applied PV Engineering - Lecture 10Document18 pagesApplied PV Engineering - Lecture 10RiazAhmadNo ratings yet

- M.SC Renewable Energy Engineering Spring 2019 (2Nd Merit) Admission Dates For Selected Candidates: 28-2-2019 TO 4-3-2019Document1 pageM.SC Renewable Energy Engineering Spring 2019 (2Nd Merit) Admission Dates For Selected Candidates: 28-2-2019 TO 4-3-2019RiazAhmadNo ratings yet

- ModelDocument1 pageModelRiazAhmadNo ratings yet

- Student Manual Google Classroom: University of Engineering and Technology, PeshawarDocument17 pagesStudent Manual Google Classroom: University of Engineering and Technology, PeshawarRiazAhmadNo ratings yet

- Renewable Energy Engineering - USPCAS-E (P) : Class Schedule (Spring - 2019)Document1 pageRenewable Energy Engineering - USPCAS-E (P) : Class Schedule (Spring - 2019)RiazAhmadNo ratings yet

- Job Opportunities: SR # Name of Post Age Limit No. of Posts Contract Emoluments Qualification & ExperienceDocument2 pagesJob Opportunities: SR # Name of Post Age Limit No. of Posts Contract Emoluments Qualification & ExperienceRiazAhmadNo ratings yet

- Bonafide CertifucateDocument1 pageBonafide CertifucateRiazAhmadNo ratings yet

- University of Engineering & Technology Bannu Campus, PakistanDocument1 pageUniversity of Engineering & Technology Bannu Campus, PakistanRiazAhmadNo ratings yet

- 06 - Activity - Going in CirclesDocument3 pages06 - Activity - Going in CirclesMateo LobatoNo ratings yet

- Technical Analysis of Stocks: by Richard D. MarcusDocument18 pagesTechnical Analysis of Stocks: by Richard D. Marcuskalyani gorNo ratings yet

- Gen Ed MathematicsDocument28 pagesGen Ed MathematicsVe Jay Angela Guimte0% (1)

- Biostatistics & Research Methodology PDFDocument19 pagesBiostatistics & Research Methodology PDFhadin khanNo ratings yet

- 18CS06 Structural Dynamics: Duhamel'S IntegralDocument29 pages18CS06 Structural Dynamics: Duhamel'S Integral20MC06 - SORNAMUGI KNo ratings yet

- ANSYS Mechanical APDL Modeling and Meshing GuideDocument244 pagesANSYS Mechanical APDL Modeling and Meshing GuidejozNo ratings yet

- Applications of Lie Groups To Differential Equations - Peter J. OlverDocument524 pagesApplications of Lie Groups To Differential Equations - Peter J. OlverflashescapesNo ratings yet

- Structural Health Monitoring With Statistical Methods During Progressive Damage Test of S101 BridgeDocument11 pagesStructural Health Monitoring With Statistical Methods During Progressive Damage Test of S101 BridgeNagesh ThotaNo ratings yet

- 2.0 - P34x - EN - MD - J76Document184 pages2.0 - P34x - EN - MD - J76Diana Vanessa VelCruzNo ratings yet

- ExampleDocument8 pagesExamplesalehnaib0% (1)

- Nsep Solved 2007Document10 pagesNsep Solved 2007Mahalingam NanjappanNo ratings yet

- Notes Phys300Document311 pagesNotes Phys300armagandgstnNo ratings yet

- Cam DrawingDocument12 pagesCam DrawingПараг ТамбеNo ratings yet

- DXF FormatDocument208 pagesDXF Formatthigopal100% (1)

- Bayes TheoremDocument8 pagesBayes TheoremHaseeb TariqNo ratings yet

- Impact LoadDocument10 pagesImpact LoadAtish Kumar100% (2)

- AASHTO T324 Hamburg Wheel Tracking Test For HMADocument26 pagesAASHTO T324 Hamburg Wheel Tracking Test For HMAĐức Trung TrầnNo ratings yet

- Taguchi Method Lecture 02Document39 pagesTaguchi Method Lecture 02DrMohamed MansourNo ratings yet

- Analytic GeometryDocument2 pagesAnalytic Geometryngekakolangto100% (1)

- Group Actions: Patrick J. MorandiDocument9 pagesGroup Actions: Patrick J. Morandisaikat bankNo ratings yet

- GitmanAWE IM Ch08Document27 pagesGitmanAWE IM Ch08Somera Abdul QadirNo ratings yet

- Minimum Variance Unbiased EstimatorsDocument4 pagesMinimum Variance Unbiased EstimatorsOIBNo ratings yet

- 1 The Hiring Problem and Basic ProbabilityDocument6 pages1 The Hiring Problem and Basic ProbabilityAditya BhutraNo ratings yet

- The Hidden Symmetry of The Coulomb Problem in Relativistic Quantum Mechanics - From Pauli To Dirac (2006)Document5 pagesThe Hidden Symmetry of The Coulomb Problem in Relativistic Quantum Mechanics - From Pauli To Dirac (2006)Rivera ValdezNo ratings yet

- Lesson 3. Mathematical Language and SymbolsDocument12 pagesLesson 3. Mathematical Language and SymbolsRegine SeldaNo ratings yet

- Risk and Return: All Rights ReservedDocument52 pagesRisk and Return: All Rights ReservedArif SharifNo ratings yet

- Predicting The Hydrate FormationDocument10 pagesPredicting The Hydrate FormationmviteazuNo ratings yet

- Final Year Project ReportDocument44 pagesFinal Year Project ReportBABAI GHOSHNo ratings yet

Fault Tolerance & Reliability CDA 5140 Chapter 2 - Cyclic Polynomial Codes

Fault Tolerance & Reliability CDA 5140 Chapter 2 - Cyclic Polynomial Codes

Uploaded by

RiazAhmadOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fault Tolerance & Reliability CDA 5140 Chapter 2 - Cyclic Polynomial Codes

Fault Tolerance & Reliability CDA 5140 Chapter 2 - Cyclic Polynomial Codes

Uploaded by

RiazAhmadCopyright:

Available Formats

Fault Tolerance & Reliability

CDA 5140

Chapter 2 Cyclic Polynomial Codes

cylic code: special type of parity check code such that every cyclic shift

of codeword is a codeword

for example, if (cn-1, cn-2, . . . c0) is a codeword so is (cn-2, cn-3, . . . c0, cn-1)

cyclic property best captured using polynomial algebra over a finite field, in

particular binary finite field

for code word c(X) = (cn-1, cn-2, . . . c0) represent it as polynomial

cn-1Xn-1 + cn-2Xn-2 + . . . + c1X1 + c0

two most important concepts are use of polynomial division and the

operation of modulo a polynomial

for f(X) and g(X) two polynomials with the latter of at least degree 1, then

the Euclid division algorithm states that there are two polynomials q(x), the

quotient, and r(x), the remainder such that

f(X) = q(X)g(X) + r(X)

and degree of r(x) is less than degree of g(X)

and further state that r(x) is congruent to f(X) modulo g(x), i.e.

r(X) = f(X) [mod g(X)]

for cyclic codes most important modulus is Xn 1 which implies that

1 = Xn [mod Xn 1]

thus Xc(x) [mod Xn 1] is a code word since

Xc(X) = cn-1Xn + cn-2Xn-1 + . . . + c1X2 + c0X

and reducing mod Xn 1, then Xn = 1

giving Xc(X) = cn-2Xn-1 + cn-3Xn-2 + . . . + c1X2 + c0X + cn-1

consequently for c(X) a codeword, so is Xi c(X)

- thus

i Xi c(X) = f(X) c(X)

where f(X) has binary coefficients

- just as can generate any (n,m) parity-check code using the generator matrix G,

can also generate the code words for (n,m) cyclic code by the generator

polynomial g(X) with the following properties:

- g(X) is unique lowest-degree nonzero code polynomial with coefficient 1

in highest-degree term

- degree of g(X) is n m

- each of the 2m code words of binary cyclic code is multiple of g(X) of

form

i Xi g(X), 0 < i < m-1

- set of code polynomials g(X), Xg(X), . . . Xm-1g(X) is a linearly

independent set and all 2m code words can be generated from these m

code words

- g(X) must be a factor of Xn 1

Example:

-

consider the (7,4) cyclic code with generating polynomial

g(X) = X3 + X + 1

has 3 check digits and the four linearly independent code words are:

polynomials

7-tuples

X3 + X + 1

X4 + X2 + X

X5 + X3 + X2

X6 + X4 + X3

0001011

0010110

0101100

1011000

and all 16 codewords are linear combinations of these

for a data polynomial, of degree m-1,

d(X) = dm-1Xm-1 + dm-2Xm-2 + . . . + d1X1 + d0

the data digits are dm-1, dm-2, . . . d0

the code words can be generated by

c(X) = d(X) g(X)

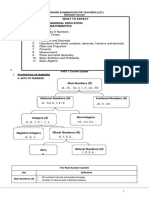

which can be done by means of the following shift register circuit where

the register cells are initialized to all zeroes:

d(X)

g2

gn-m

g1

g0

c(X)

Nonsystematic Encoding using Shift Register

digit dm-1 is fed in first, then dm-2 and so on until d0 followed by (n-m)

zeroes

the circled gi represent multiplication by gi (either 0 or 1) and the + is

modulo 2 addition (XOR), and the gi are coefficients of g(X)

code digits come out in the order of cn-1 until finally c0

as an example, consider for n = 7, m = 4

g(X) = X3 + X + 1

and

d(X) = X2 + 1

use the above circuit to generate c(X) and verify using polynomial

multiplication that the resulting c(X) is g(X) times d(X)

note that above circuit generates a non-systematic code word

can generate a systematic code by applying the following and creating the

corresponding circuit

multiplying d(X) by Xn-m we have

Xn-m d(X) = dm-1Xn-1 + dm-2Xn-2 + . . . + d0Xn-m

= q(X)g(X) + r(X)

for g(X) the degree n-m generator polynomial, and r(X) the unique

remainder polynomial of degree less than n-m

then, adding r(X) to each side gives

dm-1Xn-1 + dm-2Xn-2 + . . . + d0Xn-m + r(X) = q(X)g(x)

thus the LHS must be a multiple of g(X) and hence a code polynomial

and if we write r(X) as

r(X) = pn-m-1Xn-m-1 + pn-m-2Xn-m-2 + . . . + p1X + p0

the coefficients of the code polynomial are:

dm-1, dm-2, . . . d0, pn-m-1, pn-m--2, . . . p0

which is systematic

then need to design a feedback shift register to divide Xn-m d(X) by g(X) to

determine r(X)

the following circuit does so, where the register is initialized to all zeroes,

and with dm-1 fed in first, and then dm-2, . . . d0 sequentially in that order

until dm-1 reaches the furthest right position

then perform m right shifts which then leaves the digits of r(X) in the

register with pn-m-1 in the furthest right position

note in the following figure, since the coefficient of Xn-m must be 1 there is

no corresponding multiplication needed as for the other positions; and,

the first cell simply holds the bit before the clock pulse, while the

remaining cells hold the results

d(X)

g0

g1

+

+

+

+

g2

g n-m-2

gn-m-1

Feedback Shift Register for Systematic Encoding

for the original d(X) = X2 + 1 and g(X) = X3 + X + 1, draw the FSR and

perform the division, give the resulting r(X) and c(X), and show, using

polynomial division that c(X) is a multiple of g(X)

-

of interest is that this same feedback shift register can be used for

encoding and error detection

if the received polynomial is y(X) and the error polynomial is e(X), then

y(X) = c(X) + e(X)

-

if y(X) is a code word and it is divided by g(X), the remainder is 0

if y(X) is not a code word, then dividing by g(X) will give a remainder

which is referred to as a syndrome (polynomial) s(X) and indicates an

error

is y(X) = X5 + X2 + X + 1 a codeword for the above circuit?

is y(X) = X6 + X4 + X2 a codeword for the above circuit?

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5825)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Explain Memory-Reference Instructions. Ans. Memory Reference InstructionsDocument23 pagesExplain Memory-Reference Instructions. Ans. Memory Reference Instructionsshikha100% (1)

- CalculusDocument38 pagesCalculuspranit100% (1)

- Band Gap - PVEducationDocument3 pagesBand Gap - PVEducationRiazAhmadNo ratings yet

- Basic Equations - PVEducationDocument3 pagesBasic Equations - PVEducationRiazAhmadNo ratings yet

- Base Resistance - PVEducationDocument2 pagesBase Resistance - PVEducationRiazAhmadNo ratings yet

- Simulation of Layer Thickness PDFDocument5 pagesSimulation of Layer Thickness PDFRiazAhmadNo ratings yet

- Evolution of Energy Policies in Pakistan and Future PerspectsDocument22 pagesEvolution of Energy Policies in Pakistan and Future PerspectsRiazAhmadNo ratings yet

- Absorption Coefficient - PVEducationDocument3 pagesAbsorption Coefficient - PVEducationRiazAhmadNo ratings yet

- ModelDocument1 pageModelRiazAhmadNo ratings yet

- Applied PV Engineering - Lecture 10Document18 pagesApplied PV Engineering - Lecture 10RiazAhmadNo ratings yet

- M.SC Renewable Energy Engineering Spring 2019 (2Nd Merit) Admission Dates For Selected Candidates: 28-2-2019 TO 4-3-2019Document1 pageM.SC Renewable Energy Engineering Spring 2019 (2Nd Merit) Admission Dates For Selected Candidates: 28-2-2019 TO 4-3-2019RiazAhmadNo ratings yet

- ModelDocument1 pageModelRiazAhmadNo ratings yet

- Student Manual Google Classroom: University of Engineering and Technology, PeshawarDocument17 pagesStudent Manual Google Classroom: University of Engineering and Technology, PeshawarRiazAhmadNo ratings yet

- Renewable Energy Engineering - USPCAS-E (P) : Class Schedule (Spring - 2019)Document1 pageRenewable Energy Engineering - USPCAS-E (P) : Class Schedule (Spring - 2019)RiazAhmadNo ratings yet

- Job Opportunities: SR # Name of Post Age Limit No. of Posts Contract Emoluments Qualification & ExperienceDocument2 pagesJob Opportunities: SR # Name of Post Age Limit No. of Posts Contract Emoluments Qualification & ExperienceRiazAhmadNo ratings yet

- Bonafide CertifucateDocument1 pageBonafide CertifucateRiazAhmadNo ratings yet

- University of Engineering & Technology Bannu Campus, PakistanDocument1 pageUniversity of Engineering & Technology Bannu Campus, PakistanRiazAhmadNo ratings yet

- 06 - Activity - Going in CirclesDocument3 pages06 - Activity - Going in CirclesMateo LobatoNo ratings yet

- Technical Analysis of Stocks: by Richard D. MarcusDocument18 pagesTechnical Analysis of Stocks: by Richard D. Marcuskalyani gorNo ratings yet

- Gen Ed MathematicsDocument28 pagesGen Ed MathematicsVe Jay Angela Guimte0% (1)

- Biostatistics & Research Methodology PDFDocument19 pagesBiostatistics & Research Methodology PDFhadin khanNo ratings yet

- 18CS06 Structural Dynamics: Duhamel'S IntegralDocument29 pages18CS06 Structural Dynamics: Duhamel'S Integral20MC06 - SORNAMUGI KNo ratings yet

- ANSYS Mechanical APDL Modeling and Meshing GuideDocument244 pagesANSYS Mechanical APDL Modeling and Meshing GuidejozNo ratings yet

- Applications of Lie Groups To Differential Equations - Peter J. OlverDocument524 pagesApplications of Lie Groups To Differential Equations - Peter J. OlverflashescapesNo ratings yet

- Structural Health Monitoring With Statistical Methods During Progressive Damage Test of S101 BridgeDocument11 pagesStructural Health Monitoring With Statistical Methods During Progressive Damage Test of S101 BridgeNagesh ThotaNo ratings yet

- 2.0 - P34x - EN - MD - J76Document184 pages2.0 - P34x - EN - MD - J76Diana Vanessa VelCruzNo ratings yet

- ExampleDocument8 pagesExamplesalehnaib0% (1)

- Nsep Solved 2007Document10 pagesNsep Solved 2007Mahalingam NanjappanNo ratings yet

- Notes Phys300Document311 pagesNotes Phys300armagandgstnNo ratings yet

- Cam DrawingDocument12 pagesCam DrawingПараг ТамбеNo ratings yet

- DXF FormatDocument208 pagesDXF Formatthigopal100% (1)

- Bayes TheoremDocument8 pagesBayes TheoremHaseeb TariqNo ratings yet

- Impact LoadDocument10 pagesImpact LoadAtish Kumar100% (2)

- AASHTO T324 Hamburg Wheel Tracking Test For HMADocument26 pagesAASHTO T324 Hamburg Wheel Tracking Test For HMAĐức Trung TrầnNo ratings yet

- Taguchi Method Lecture 02Document39 pagesTaguchi Method Lecture 02DrMohamed MansourNo ratings yet

- Analytic GeometryDocument2 pagesAnalytic Geometryngekakolangto100% (1)

- Group Actions: Patrick J. MorandiDocument9 pagesGroup Actions: Patrick J. Morandisaikat bankNo ratings yet

- GitmanAWE IM Ch08Document27 pagesGitmanAWE IM Ch08Somera Abdul QadirNo ratings yet

- Minimum Variance Unbiased EstimatorsDocument4 pagesMinimum Variance Unbiased EstimatorsOIBNo ratings yet

- 1 The Hiring Problem and Basic ProbabilityDocument6 pages1 The Hiring Problem and Basic ProbabilityAditya BhutraNo ratings yet

- The Hidden Symmetry of The Coulomb Problem in Relativistic Quantum Mechanics - From Pauli To Dirac (2006)Document5 pagesThe Hidden Symmetry of The Coulomb Problem in Relativistic Quantum Mechanics - From Pauli To Dirac (2006)Rivera ValdezNo ratings yet

- Lesson 3. Mathematical Language and SymbolsDocument12 pagesLesson 3. Mathematical Language and SymbolsRegine SeldaNo ratings yet

- Risk and Return: All Rights ReservedDocument52 pagesRisk and Return: All Rights ReservedArif SharifNo ratings yet

- Predicting The Hydrate FormationDocument10 pagesPredicting The Hydrate FormationmviteazuNo ratings yet

- Final Year Project ReportDocument44 pagesFinal Year Project ReportBABAI GHOSHNo ratings yet