Professional Documents

Culture Documents

Multilevel Power Optimization For ICA Processor

Multilevel Power Optimization For ICA Processor

Uploaded by

IJSTEOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Multilevel Power Optimization For ICA Processor

Multilevel Power Optimization For ICA Processor

Uploaded by

IJSTECopyright:

Available Formats

IJSTE - International Journal of Science Technology & Engineering | Volume 3 | Issue 01 | July 2016

ISSN (online): 2349-784X

Multilevel Power Optimization for ICA Processor

Jini Kuriakose

Assistant Professor

Department of Electronics & Communication Engineering

MA College of Engineering, Kothamangalam

Jayan K George

Assistant Professor

Department of Electronics & Communication Engineering

MA College of Engineering, Kothamangalam

Abstract

This paper presents a 16- channel ICA implementation in FPGA for biomedical application. Independent component analysis

(ICA) is a statistical signal processing technique having emerging new practical applications. Infomax ICA is a common method

to identify artifacts and interference from their mixtures such as electroencephalogram (EEG), magneto encephalography

(MEG), and electrocardiogram (EEG). Multilevel power optimization approach is using for reducing the power dissipation of the

ICA processor.

Keywords: Independent component analysis (ICA), Infomax, Multilevel Power optimization

_______________________________________________________________________________________________________

I.

INTRODUCTION

The EEG recorded from the scalp provides important information about the health of the central nervous system [1]. The

measured EEG is often contaminated by artifacts and electric noise. This problem can be solved by the independent component

analysis (ICA) algorithm [2]. The main bottle neck of multi-channel ICA is the computation complexity and hardware cost. The

purpose of this study is to propose 16- channel ICA architecture with real time separation of EEG signals.

ICA recovers independent source signals from their mixed signals by finding a linear transformation that maximizes the

mutual independence of mixtures. To improve the efficiency of ICA, Extended Infomax algorithm is proposed. Infomax ICA

measures non-Gaussianity using kurtosis to find the independent sources from their mixtures [3]. However, most of the

publications focused on offline signal processing using FastICA algorithm.It cannot be applied to real-time applications such as

speech signal enhancement [4] and EEG/MEG essential features extraction for brain computer interface (BCI) [5]. In order to

realize the real-time signal processing, the FastICA algorithm can be implemented on a fieldprogrammable gate array (FPGA) to

speed up the computation involving vector multiplications, matrix multiplications, and matrix inverses.

For portable and longtime monitoring applications, the power consumption is an important design trade-off consideration

[6].One of the most critical design requirements for portable biomedical devices is the capability to operate with minimal energy,

in order to maximize battery operating time. This paper focuses on the multilevel power optimization for ICA processor.

In this paper a low power ICA processor is proposed. In order to minimize the power consumption, the multilevel power

optimization methodology is used. The rest of the paper is organized as follows: section II briefly introduces the short description

of the independent component analysis theory. Simulation result is provided in section III and finally a conclusion is given in

section IV.

II. INDEPENDENT COMPONENT ANALYSIS

Independent component analysis (ICA)[7] is a well-known method of finding latent structure in data. ICA is a statistical method

that expresses a set of multidimensional observations as a combination of unknown latent variables. These underlying latent

variables are called sources or independent components and they are assumed to be statistically independent of each other. The

ICA model is

x = f (, s)

(1)

where x = (x1, . . . , xm) is an observed vector and f is a general unknown function with parameters that operates on

statistically independent latent variables listed in the vector s = (s1, . . . , sn ).A special case of (2.1) is obtained when the

function is linear, and we can write

x = As

(2)

where A is an unknown mn mixing matrix. In Formulae (1) and (2) we consider x and s as random vectors. When a sample

of observations X = (x1, . . . , xN) becomes available, we write X = AS where the matrix X has observations x as its columns and

similarly the matrix S has latent variable vectors s as its columns. The mixing matrix A is constant for all observations.

If both the original sources S and the way the sources were mixed are all unkown, and only mixed signals or mixtures X can

be measured and observed, then the estimation of A and S is known as blind source separation (BSS) problem.

The linear model (2) is identifiable under the following fundamental restrictions: the sources (i.e. the components of S) are

statistically independent, at most one of the independent components sj may be Gaussian, and the mixing matrix A must be of

full column rank. The identifiability of the model is proved in the case n = m and for those source densities whose variance is

defined.

All rights reserved by www.ijste.org

392

Multilevel Power Optimization for ICA Processor

(IJSTE/ Volume 3 / Issue 01 / 069)

ICA Definition: Independent Component Analysis (ICA) is a method for finding underlying factors or components from

multivariate (multi-dimensional) statistical data. What distinguishes ICA from other methods is that it looks for components that

are both statistically independent and non-Gaussian.

III. SYSTEM OVERVIEW AND ARCHITECTURE

FPGA technology is very suitable to implement the digital signal processing algorithm for quickly verifying the algorithm in

hardware. For real-time implementation of the FastICA algorithm, it requires high volume of mathematical operations in a very

short time interval. Currently, most FPGAs have on-chip hardware multipliers and memory blocks, and are suitable for such

application. In this paper, the hardware ICA is implemented by hand coding VHSIC hardware description language (VHDL). To

increase the feasibility in the implementation of higher dimensions of ICA, the design of implementation of ICA is based on the

concept of modules.

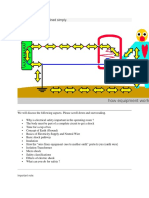

The block diagram of the pipelined ICA with its peripherals is illustrated in Fig.2. It includes five module boards: 1) mixed

signals amplifier and filter module; 2) ADC circuit module; 3) FPGA chip containing pipelined ICA algorithm hardware; 4)

DAC circuit module; and 5) the signal output processing module of estimated independent component signal. Each module board

has dual channel signal processing capability. Both ADC and DAC have 24bit resolution. Moreover, ADC and DAC chips

select 8-pin dual in-line package (DIP) with serial control interface to reduce the FPGAs input/output (I/O) ports expense.

The ICA engine is a chip implementation of the Infomax ICA [8] algorithm as shown in Fig.1. The EEG sample input

buffering and calculation unit implementing the data windowing and operation schedule scheme. An ICA computation unit for

unmixing the independent source signals from the multichannel EEG input. An ICA training unit for calculating the unmixing

weight matrix for use in the ICA computation unit. A preprocessing whitening unit for reducing the number of training iterations

and accelerating convergence in the ICA training unit. Reduction in computation complexity and chip power consumption are

achieved through the introduction of the whitening operation at the algorithm level.

Fig. 1: Hardware Architecture of ICA engine

With ongoing trend of increasing integration synthesized digital circuit and custom analog circuit, power dissipation from

both types of circuit blocks must be considered in order to achieve an overall low power dissipation of VLSI systems [9]. The

focus of this paper is to demonstrate a design approach that minimizes power dissipation of analog mixed-signal building blocks.

Multilevel power optimization technique is using for the minimizes the power dissipation. Pipelined analog to digital converter, a

popular ADC architecture [10] for medium to high resolutions, is one such building block that are commonly used in modern

mixed signal ICs. To minimize the power dissipation, a number of approaches have been proposed from a wide range of

perspectives. At the circuit level, device types and supply voltages are jointly optimized for the residue amplifier of a pipeline

stage to minimize power. At the architecture level, a non-linearity contribution from stage gain error is optimally distributed to

further minimize combined power dissipation.

The proposed pipelined ICA focuses on 16 channels in this paper. It had been verified. A n dimensional ICA architecture

based on the proposed hardware modules is illustrated in Fig.3. The size of the submemory is 32 by m , where is the number of

time samples.

IV. SIMULATION RESULTS

A VLSI architecture for 16-channel real time ICA was presented. Test signals are fed to the chip through a Xilinx FPGA

verification suite and channel outputs are matched against MATLAB ICA simulation.

All rights reserved by www.ijste.org

393

Multilevel Power Optimization for ICA Processor

(IJSTE/ Volume 3 / Issue 01 / 069)

Fig. 2: Block diagram of pipelined ICA

Fig. 3: The n-dimensional ICA architecture

V. CONCLUSION

VLSI implementation of ICA algorithm offers many features such as high processing speed, which is extremely desired in many

applications. In order to reduce the complexity, the Fast ICA block is divided into several sub modules and each of the sub

modules are developed by HDL coding.

All rights reserved by www.ijste.org

394

Multilevel Power Optimization for ICA Processor

(IJSTE/ Volume 3 / Issue 01 / 069)

REFERENCES

Luke Rankine,Nathan Strevenson, Mostefa Mesbah, and Boualem Boashash, A Nonstationary Model of Newborn EEG, IEEE Trans. Biomed. Eng.,

VOL. 54, NO.1,JANUARY 2007

[2] National Institute of Neurological disorders and Stroke, Seizures and Epilepsy:Hope through Research, Publication date May 2004.

[3] A. Hyvrinen and E. Oja, Independent component analysis: Algorithms and applications, Neural Netw., vol. 13, pp. 411430, May 2000.

[4] J. T. Chien and B. C. Chen, A new independent component analysi for speech recognition and separation, IEEE Trans. Speech Audio Process., vol. 14,

no. 4, pp. 12451254, Jul. 2006.

[5] L. Tian, D. Erdogmus, A. Adami, M. Pavel, and S. Mathan, Salient EEG channel selection in brain computer interfaces by mutual information

maximization, in Proc. IEEE Annu. Int. Conf. Eng. Med. Biol.Soc., 2005, pp. 70647067.

[6] R.Vigario; J.Sarela; V.Jousmaki; M. Hamalanien; E.Oja , Independent Component aaproach to the analysis of EEG and MEG recordings, IEEE Trans.

Bimed. Eng, Vol 47 no.5, pp. 589-593 May 2000. .

[7] P. Comon, Indepenent component analysis ,a new concept?, Signal process ., vol. 36, pp. 287-314, 1994.

[8] A.J Bell and T.J Sejnowski, An Information- Maximization Approach to Blind separation and Blind Deconvolutiion,Neural computing, 1995,7:pp11291159.

[9] M. Horowitz, E.Alon, D.Patil, S.Naffziger, and R.Kumar, Scaling, power, and the future of CMOS, in proc. IEEEInt. Electron Devices Meet., 2005, pp.

7-15.

[10] Jintae Kim, Sotirios Limotyrakis, Chih-Kong Ken Yang, Multilevel Power Optimization of Pipelined A/D Converters, VLSI systems. Vol 19 May 2011.

on-line EEG signal separation , Biomedical Circuits and Systems Conferenc, 2008.BioCAS2008. IEEE, pp.65-6,20-22Nov.2008

[1]

All rights reserved by www.ijste.org

395

You might also like

- Gates Flexiva 1kwDocument142 pagesGates Flexiva 1kwJuan perezNo ratings yet

- Ganapati UpanishadDocument4 pagesGanapati UpanishadNeha SharmaNo ratings yet

- Ncstudio V9 Programming Manual-R5.1Document102 pagesNcstudio V9 Programming Manual-R5.1beanib83No ratings yet

- Xiaoyan Cheng, and Haigang Yang: A Cmos Field Programmable Analog Array For Intelligent Sensory ApplicationDocument4 pagesXiaoyan Cheng, and Haigang Yang: A Cmos Field Programmable Analog Array For Intelligent Sensory ApplicationashishmanyanNo ratings yet

- Fpga Implementation of A Multilayer Perceptron Neural Network Using VHDLDocument4 pagesFpga Implementation of A Multilayer Perceptron Neural Network Using VHDLminoramixNo ratings yet

- A High-Speed/Low-Power Multiplier Using An Advanced Spurious Power Suppression TechniqueDocument4 pagesA High-Speed/Low-Power Multiplier Using An Advanced Spurious Power Suppression TechniqueBappy DebnathNo ratings yet

- Circuit Analysis and Simulations Through Internet: NtroductionDocument9 pagesCircuit Analysis and Simulations Through Internet: NtroductionAline RochaNo ratings yet

- Dokumen - Tips - Advanced Energy MeterDocument7 pagesDokumen - Tips - Advanced Energy Metergurrala rajkumarNo ratings yet

- VLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueDocument11 pagesVLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueSivanantham SadhasivamNo ratings yet

- VHDL Implementation of 8-Bit ALU: Suchita Kamble, Prof .N. N. MhalaDocument5 pagesVHDL Implementation of 8-Bit ALU: Suchita Kamble, Prof .N. N. MhalaInternational Organization of Scientific Research (IOSR)No ratings yet

- Design and Implementation of Low-Power Digital Signal Processing Using Approximate AddersDocument7 pagesDesign and Implementation of Low-Power Digital Signal Processing Using Approximate AddersijsretNo ratings yet

- Performance Analysis of MAC Unit Using Booth, Wallace Tree, Array and Vedic MultipliersDocument8 pagesPerformance Analysis of MAC Unit Using Booth, Wallace Tree, Array and Vedic MultipliersSanchariniNo ratings yet

- Design and Analysis of A 32-Bit Pipelined Mips Risc ProcessorDocument18 pagesDesign and Analysis of A 32-Bit Pipelined Mips Risc ProcessorAnonymous e4UpOQEPNo ratings yet

- A Mixed-Signal Sensor Interface MicroinstrumentDocument12 pagesA Mixed-Signal Sensor Interface MicroinstrumentPhạm Ngọc HòaNo ratings yet

- CONIT2023 Paper0346Document8 pagesCONIT2023 Paper0346sriNo ratings yet

- Viterbi Decoder Based On Speed Optimization of A FPGA: M A, J. MDocument4 pagesViterbi Decoder Based On Speed Optimization of A FPGA: M A, J. Mfaithlife2977 kancherlaNo ratings yet

- Implementation of MAC Unit Using Booth Multiplier & Ripple Carry AdderDocument3 pagesImplementation of MAC Unit Using Booth Multiplier & Ripple Carry AdderVijay KulkarniNo ratings yet

- Fpga Control Motor AsincronDocument7 pagesFpga Control Motor AsincronVasileSpireaNo ratings yet

- ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA DownlinkDocument5 pagesASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA DownlinkMunish JassiNo ratings yet

- Direct Self Control of Induction Motor Based On Neural NetworkDocument9 pagesDirect Self Control of Induction Motor Based On Neural NetworksethukumarkNo ratings yet

- Priyanka - 50300 16 130Document4 pagesPriyanka - 50300 16 130Aravind GopaganiNo ratings yet

- VlsiDocument32 pagesVlsibalasaravanan0408No ratings yet

- The Development of The Digital Oscilloscope Based On FPGA PDFDocument8 pagesThe Development of The Digital Oscilloscope Based On FPGA PDFivy_publisherNo ratings yet

- Karthiga Phase II Report-11Document59 pagesKarthiga Phase II Report-11Karthiga MuruganNo ratings yet

- Design of Low Power / High Speed Multiplier Using Spurious Power Suppression Technique (SPST)Document5 pagesDesign of Low Power / High Speed Multiplier Using Spurious Power Suppression Technique (SPST)anji.guvvalaNo ratings yet

- (IJCST-V9I2P10) :DR - Shine N DasDocument6 pages(IJCST-V9I2P10) :DR - Shine N DasEighthSenseGroupNo ratings yet

- 4th Process TomograpgyDocument6 pages4th Process TomograpgyEmmanuel Abdias Romano CastilloNo ratings yet

- Low-Energy Embedded FPGA StructureDocument6 pagesLow-Energy Embedded FPGA Structuremossaied2No ratings yet

- Design and Implementation of Traffic Controller Using VHDL: Interim Project ReportDocument21 pagesDesign and Implementation of Traffic Controller Using VHDL: Interim Project ReportAugusto Germano da SilvaNo ratings yet

- Lei Wang 2008Document4 pagesLei Wang 2008201901363No ratings yet

- The Cascade Carry Array Multiplier - A Novel Structure of Digital Unsigned Multipliers For Low-Power Consumption and Ultra-Fast ApplicationsDocument9 pagesThe Cascade Carry Array Multiplier - A Novel Structure of Digital Unsigned Multipliers For Low-Power Consumption and Ultra-Fast Applicationsvenkat301485No ratings yet

- RTL Design Techniques To Reduce The Power Consumption of FPGA Based CircuitsDocument6 pagesRTL Design Techniques To Reduce The Power Consumption of FPGA Based Circuitsraees74No ratings yet

- Adaptive Multi Sensor Interface System On ChipDocument4 pagesAdaptive Multi Sensor Interface System On ChipSaurabh AnmadwarNo ratings yet

- Efficient Design of Majority-Logic-Based Approximate Arithmetic CircuitsDocument13 pagesEfficient Design of Majority-Logic-Based Approximate Arithmetic Circuitspes1ug20ec108No ratings yet

- A 1-V Programmable DSP For Wireless CommunicationsDocument11 pagesA 1-V Programmable DSP For Wireless CommunicationssciwanderNo ratings yet

- Comparative Analysis of Multiplier in Quaternary Logic: Shweta Hajare, Dr.P.K.DakholeDocument6 pagesComparative Analysis of Multiplier in Quaternary Logic: Shweta Hajare, Dr.P.K.DakholeDivya MokaraNo ratings yet

- Optimization of Delay IIN Pipeline Mac Unit Using Wallace Tree MultiplierDocument9 pagesOptimization of Delay IIN Pipeline Mac Unit Using Wallace Tree MultiplierIJRASETPublicationsNo ratings yet

- Desigine and Implimentation of Application Specific Low Power MultipliersDocument7 pagesDesigine and Implimentation of Application Specific Low Power MultipliersSaiKishoreNo ratings yet

- Design of Power-E Cient FPGA Convolutional Cores With Approximate Log MultiplierDocument6 pagesDesign of Power-E Cient FPGA Convolutional Cores With Approximate Log MultiplierKneedyoulNo ratings yet

- Mixed NeuromorphicDocument4 pagesMixed NeuromorphicPeter Wagih ZakiNo ratings yet

- The Cascade Carry Array Multiplier - A Novel Structure of Digital Unsigned Multipliers For Low-Power Consumption and Ultra-Fast ApplicationsDocument9 pagesThe Cascade Carry Array Multiplier - A Novel Structure of Digital Unsigned Multipliers For Low-Power Consumption and Ultra-Fast Applicationsvenkat301485No ratings yet

- A Cluster of Fpaas To Recognize Images Using Neural NetworksDocument5 pagesA Cluster of Fpaas To Recognize Images Using Neural NetworksSoumya Shatakshi PandaNo ratings yet

- A Micropower Biomedical Signal Processor For Mobile Healthcare ApplicationsDocument4 pagesA Micropower Biomedical Signal Processor For Mobile Healthcare ApplicationsSanthos KumarNo ratings yet

- Design and Implementation of 4-Bit Arithmetic and Logic Unit Chip With The Constraint of Power ConsumptionDocument8 pagesDesign and Implementation of 4-Bit Arithmetic and Logic Unit Chip With The Constraint of Power ConsumptionRaja ArslanNo ratings yet

- FPGA and ASIC Vedic MultiplierDocument4 pagesFPGA and ASIC Vedic MultiplierJagannath KbNo ratings yet

- International Journal of Computational Engineering Research (IJCER)Document11 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- Hardware/Software Structure For The Contact Resistance Estimation in The Case of An Elementary ContactDocument4 pagesHardware/Software Structure For The Contact Resistance Estimation in The Case of An Elementary ContactAhmed58seribegawanNo ratings yet

- PDFDocument4 pagesPDFchaitanya sNo ratings yet

- Preferential Design En-Eff Robust Implant Neural Signal BhuniaDocument4 pagesPreferential Design En-Eff Robust Implant Neural Signal BhuniaAlex WongNo ratings yet

- Tam MetinDocument4 pagesTam MetinerkandumanNo ratings yet

- 1 s2.0 S0026269219309346 MainDocument9 pages1 s2.0 S0026269219309346 MainShylu SamNo ratings yet

- LUT Optimization Using Combined APC-OMS Technique For Memory-Based ComputationDocument9 pagesLUT Optimization Using Combined APC-OMS Technique For Memory-Based ComputationRaj PrabhasNo ratings yet

- A New Vlsi Architecture For Modi EdDocument6 pagesA New Vlsi Architecture For Modi Edsatishcoimbato12No ratings yet

- FPGA Based Notch Filter To Remove PLI Noise From ECGDocument5 pagesFPGA Based Notch Filter To Remove PLI Noise From ECGEditor IJRITCCNo ratings yet

- A Low-Voltage Micropower Asynchronous Multiplier With Shift-Add Multiplication ApproachDocument11 pagesA Low-Voltage Micropower Asynchronous Multiplier With Shift-Add Multiplication ApproachPradeep ChandraNo ratings yet

- Development of A Fully Implantable Recording System For Ecog SignalsDocument6 pagesDevelopment of A Fully Implantable Recording System For Ecog SignalsGeneration GenerationNo ratings yet

- The Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberDocument6 pagesThe Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberMishi AggNo ratings yet

- SIS: A System For Sequential Circuit SynthesisDocument45 pagesSIS: A System For Sequential Circuit Synthesisrajat835No ratings yet

- FPGA-Based Multi-Level Approximate Multipliers For High-Performance Error-Resilient ApplicationsDocument17 pagesFPGA-Based Multi-Level Approximate Multipliers For High-Performance Error-Resilient ApplicationspskumarvlsipdNo ratings yet

- 2346 ArticleTextinPDFFormat 6324 2 10 20180410Document7 pages2346 ArticleTextinPDFFormat 6324 2 10 20180410kimemma063No ratings yet

- Trancated Multiplier PeprDocument5 pagesTrancated Multiplier PeprJagannath KbNo ratings yet

- FPGA Implimentation of Adaptive Noise Cancellation Project Report With VHDL ProgramDocument26 pagesFPGA Implimentation of Adaptive Noise Cancellation Project Report With VHDL ProgramJerin AntonyNo ratings yet

- Using Artificial Neural Networks for Analog Integrated Circuit Design AutomationFrom EverandUsing Artificial Neural Networks for Analog Integrated Circuit Design AutomationNo ratings yet

- Design and Analysis of Magneto Repulsive Wind TurbineDocument7 pagesDesign and Analysis of Magneto Repulsive Wind TurbineIJSTENo ratings yet

- An Implementation and Design A Customized Advanced Image Editor Using Image Processing in MatlabDocument5 pagesAn Implementation and Design A Customized Advanced Image Editor Using Image Processing in MatlabIJSTENo ratings yet

- Partial Replacement of Fine Aggregate With Iron Ore Tailings and Glass PowderDocument7 pagesPartial Replacement of Fine Aggregate With Iron Ore Tailings and Glass PowderIJSTENo ratings yet

- Effect of RIB Orientation in Isogrid Structures: Aerospace ApplicationsDocument9 pagesEffect of RIB Orientation in Isogrid Structures: Aerospace ApplicationsIJSTENo ratings yet

- Development of Relationship Between Saturation Flow and Capacity of Mid Block Section of Urban Road - A Case Study of Ahmedabad CityDocument6 pagesDevelopment of Relationship Between Saturation Flow and Capacity of Mid Block Section of Urban Road - A Case Study of Ahmedabad CityIJSTENo ratings yet

- Onerider The Bike TaxiDocument3 pagesOnerider The Bike TaxiIJSTENo ratings yet

- A Mixture of Experts Model For ExtubationDocument4 pagesA Mixture of Experts Model For ExtubationIJSTENo ratings yet

- Wireless Information Process and Power Transfer in Single-User OFDM SystemDocument6 pagesWireless Information Process and Power Transfer in Single-User OFDM SystemIJSTENo ratings yet

- Technology Advancement For Abled PersonDocument9 pagesTechnology Advancement For Abled PersonIJSTENo ratings yet

- Using The Touch-Screen Images For Password-Based Authentication of IlliteratesDocument6 pagesUsing The Touch-Screen Images For Password-Based Authentication of IlliteratesIJSTENo ratings yet

- Duplicate Detection Using AlgorithmsDocument3 pagesDuplicate Detection Using AlgorithmsIJSTENo ratings yet

- Research On Storage Privacy Via Black Box and Sanitizable SignatureDocument6 pagesResearch On Storage Privacy Via Black Box and Sanitizable SignatureIJSTENo ratings yet

- Study On The Properties of Aerated Concrete Incorporating Fly Ash and Rubber PowderDocument6 pagesStudy On The Properties of Aerated Concrete Incorporating Fly Ash and Rubber PowderIJSTENo ratings yet

- An Implementation of Maximum Power Point Tracking Algorithms For Photovoltaic Systems Using Matlab and Arduino Based RTOS SystemDocument5 pagesAn Implementation of Maximum Power Point Tracking Algorithms For Photovoltaic Systems Using Matlab and Arduino Based RTOS SystemIJSTENo ratings yet

- An Implementation of Matlab Based Platform For The Evaluation of Modulation Techniques Using Multiuser MIMO-OFDM For Visible Light Communications Using MatlabDocument5 pagesAn Implementation of Matlab Based Platform For The Evaluation of Modulation Techniques Using Multiuser MIMO-OFDM For Visible Light Communications Using MatlabIJSTENo ratings yet

- Privacy Preserving: Slicer Based SchemeDocument3 pagesPrivacy Preserving: Slicer Based SchemeIJSTENo ratings yet

- Coupled Shear Wall: A ReviewDocument2 pagesCoupled Shear Wall: A ReviewIJSTE100% (1)

- 4.1 Basic Physics and Band Diagrams For MOS CapacitorsDocument5 pages4.1 Basic Physics and Band Diagrams For MOS CapacitorsvinodNo ratings yet

- Machine Design Final Coaching ProblemsDocument63 pagesMachine Design Final Coaching ProblemsasapamoreNo ratings yet

- Forensicballistic Final-ExamDocument7 pagesForensicballistic Final-ExamJonel BallesterosNo ratings yet

- Approval Material Spek Jadwal Passenger Lift FUJI - DPRD BANGLI - 10 Agustus 22Document6 pagesApproval Material Spek Jadwal Passenger Lift FUJI - DPRD BANGLI - 10 Agustus 22budy1234No ratings yet

- Design Process in ElectrochemistryDocument92 pagesDesign Process in ElectrochemistryWulan SariNo ratings yet

- A7D/A7DP: Ultra-Small, Low-Cost, Push-Operated SwitchesDocument5 pagesA7D/A7DP: Ultra-Small, Low-Cost, Push-Operated SwitchesHerbitus DuininhoNo ratings yet

- Swecs External 22072013 - Product - v1Document20 pagesSwecs External 22072013 - Product - v1Amir Asyraf SuhailiNo ratings yet

- Practice 2Document2 pagesPractice 2beebrwNo ratings yet

- Merkur Non-Heated Spray Packages: Instructions/PartsDocument58 pagesMerkur Non-Heated Spray Packages: Instructions/PartsFranklin LewisNo ratings yet

- Skin Cancer: Mikias Woldetensay Dermatology & Venereology October 2021Document76 pagesSkin Cancer: Mikias Woldetensay Dermatology & Venereology October 2021CHALIE MEQU100% (1)

- Ecg Machine Contec Type 1200gDocument3 pagesEcg Machine Contec Type 1200gFeliciaSetiawanNo ratings yet

- 3.4 - Ferrara, Alessandro - Concept. Objections To The Notion of Phronesis. Concluding Remarks (En)Document23 pages3.4 - Ferrara, Alessandro - Concept. Objections To The Notion of Phronesis. Concluding Remarks (En)Johann Vessant Roig100% (1)

- Field Artillery Journal - Jul 1917Document174 pagesField Artillery Journal - Jul 1917CAP History LibraryNo ratings yet

- EVS Level A - Workbook 202108041859159269Document50 pagesEVS Level A - Workbook 202108041859159269Nabhasvit HegdeNo ratings yet

- Homemade Doughnuts - Techniques and RecipesDocument179 pagesHomemade Doughnuts - Techniques and RecipesDennis BilangNo ratings yet

- Electrical Safety Explained SimplyDocument175 pagesElectrical Safety Explained SimplyAndi TakwaNo ratings yet

- Equipment Maintenance Log Template 03Document2 pagesEquipment Maintenance Log Template 03Thoni LacknerNo ratings yet

- Compression Asphyxia and Other Clinicopathological Findings From The Hillsborough Stadium DisasterDocument5 pagesCompression Asphyxia and Other Clinicopathological Findings From The Hillsborough Stadium Disasterdr. Ayu Nabila Kusuma PradanaNo ratings yet

- Estimated Service Life of Wood PolesDocument6 pagesEstimated Service Life of Wood Poleshalel111No ratings yet

- (Revisi) Case Report - Ellita Audreylia (201906010123)Document45 pages(Revisi) Case Report - Ellita Audreylia (201906010123)Jonathan MarkNo ratings yet

- Worksheet 3 Metals and Reactivity: Danielle AkinlaluDocument5 pagesWorksheet 3 Metals and Reactivity: Danielle AkinlaludanielleNo ratings yet

- NCR 7403 Uzivatelska PriruckaDocument149 pagesNCR 7403 Uzivatelska Priruckadukindonutz123No ratings yet

- Sri VidyameditationDocument24 pagesSri VidyameditationClaudia ShanNo ratings yet

- Official Ncm0200 Baird Parker Agar Base Technical Specifications en UsDocument3 pagesOfficial Ncm0200 Baird Parker Agar Base Technical Specifications en UsBty SaGNo ratings yet

- Chapter 17 Plane Motion of Rigid Bodies: Energy and Momentum MethodsDocument11 pagesChapter 17 Plane Motion of Rigid Bodies: Energy and Momentum MethodsAnonymous ANo ratings yet

- Como Orar en InglesDocument2 pagesComo Orar en InglesLeo MoltoNo ratings yet