Professional Documents

Culture Documents

Modelsim Xe Iii 6.4B Xilinx Ise 10.1

Modelsim Xe Iii 6.4B Xilinx Ise 10.1

Uploaded by

gkkumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Modelsim Xe Iii 6.4B Xilinx Ise 10.1

Modelsim Xe Iii 6.4B Xilinx Ise 10.1

Uploaded by

gkkumarCopyright:

Available Formats

ABSTRACT

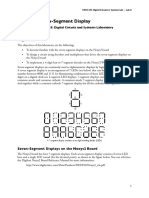

Designing a digital clock, using VHDL/Verilog, to keep track of time in the form of

HH:MM:SS. The circuit should produce 6 separate four bit digital outputs (2 four bit

outputs for the HH, 2 for the MM, 2 for the SS). The HH can just be a 2 digit number

in the range 00 to 99 i.e. its not a clock, it just a counter for hours even though 99

hour tapes dont exist. The time is to be displayed on the 6 right most 7 segment

display. We have to design a 7 segment decoder and driver, so that can be used to

convert each 4 bit output into a 7 bit signal for each the 7-segment display. The

circuit should have the following single bit inputs: A Clock, an increment, a

decrement and a reset. The increment/decrement inputs should cause the tape

counter to add or subtract 1 second from the tape time on the next rising edge of

the clock signal. If neither the increment or decrement inputs are present, the tape

counter does not change. The reset is synchronous to the clock (to avoid glitches

accidentally resetting it). The increment and decrement signals are all active high

signals (i.e. a logic 1), the reset is active low (logic 0).

Tape counter should handle full hour, minute and second roll over, e.g. if the

counter is showing 9:59:59, then the next increment should make it display

10:00:00 and vice versa when decrement is present.

TOOLS USED:

ModelSim XE III 6.4b

Xilinx ISE 10.1

You might also like

- Digital Clock Using JK Flip FlopDocument15 pagesDigital Clock Using JK Flip FlopSaqib Aslam Ganatra81% (21)

- Digital Clock Design Using Verilog DHLDocument7 pagesDigital Clock Design Using Verilog DHLbenazirthambi100% (1)

- Assembly Language CodeDocument23 pagesAssembly Language CodeHorace RoyalNo ratings yet

- ALU ReportDocument11 pagesALU ReportAzad Kiyal100% (2)

- L-14 PLC - 3Document70 pagesL-14 PLC - 3S M Jawad FakhirNo ratings yet

- Lab 8Document8 pagesLab 8Anonymous yG7oj20% (1)

- 2 Digit CounterDocument12 pages2 Digit Counterरघुनंदन भगीरथ चरखाNo ratings yet

- DLD ProjectDocument4 pagesDLD ProjectMengistu TarkoNo ratings yet

- LDST Project ReportDocument8 pagesLDST Project ReportUmair ArifNo ratings yet

- 8254 Programmable Interval TimerDocument4 pages8254 Programmable Interval Timerapi-26100966100% (1)

- Digital Pulse Counter - Two Digits: DescriptionDocument7 pagesDigital Pulse Counter - Two Digits: DescriptionAsgher KhattakNo ratings yet

- Digital Electronics: UNIT V Design of Hazard Free Digital CircuitsDocument6 pagesDigital Electronics: UNIT V Design of Hazard Free Digital CircuitsadithyaChoudhryNo ratings yet

- AVR242: 8-Bit Microcontroller Multiplexing LED Drive and A 4 X 4 KeypadDocument26 pagesAVR242: 8-Bit Microcontroller Multiplexing LED Drive and A 4 X 4 KeypadDemeter Robert Es IzabellaNo ratings yet

- Vga VHDLDocument18 pagesVga VHDLDaveNo ratings yet

- Interfacing The Keyboard To 8051 Micro Controller 11Document10 pagesInterfacing The Keyboard To 8051 Micro Controller 11rajinikanth100% (1)

- Digital Dice Using At89C51: A Report Submitt Ed To MSRIT Bangalore, For Partial Requirement of Award of Degree ofDocument21 pagesDigital Dice Using At89C51: A Report Submitt Ed To MSRIT Bangalore, For Partial Requirement of Award of Degree ofHimica KhuranaNo ratings yet

- Micrex-Sx SPB Leh984cDocument24 pagesMicrex-Sx SPB Leh984cwanahNo ratings yet

- Up down counterDocument10 pagesUp down counterSusilo WibowoNo ratings yet

- VGA Signal Generation With The XS BoardDocument12 pagesVGA Signal Generation With The XS BoardMassimoBegliominiNo ratings yet

- Arduino - ATmega328 - PWM Signal.cDocument3 pagesArduino - ATmega328 - PWM Signal.cvackyvipin100% (1)

- Rotary EncoderDocument6 pagesRotary EncoderalesysNo ratings yet

- EC49001 Microcontroller Systems Lab: Assignment 3Document14 pagesEC49001 Microcontroller Systems Lab: Assignment 3Rudrajyoti RoyNo ratings yet

- Using Quadrature Encoders With E Series DAQ Boards: Application Note 084Document11 pagesUsing Quadrature Encoders With E Series DAQ Boards: Application Note 084Heriberto Flores AmpieNo ratings yet

- Heart Rate MonitorDocument8 pagesHeart Rate MonitorVedant KumarNo ratings yet

- Digital Assignment 2Document20 pagesDigital Assignment 2Anup PatelNo ratings yet

- KyoPal X7083-X7043-X7023Document70 pagesKyoPal X7083-X7043-X7023kristechnikNo ratings yet

- Lab 1+2 Timer and StopwatchDocument14 pagesLab 1+2 Timer and StopwatchMuhd Ikram ShabryNo ratings yet

- Encoder 2Document5 pagesEncoder 2mohamedsamimorsiNo ratings yet

- Avr ArchitectureDocument29 pagesAvr ArchitectureOdoch HerbertNo ratings yet

- Group 6 ReportDocument9 pagesGroup 6 ReportQuốc Thái NguyễnNo ratings yet

- ProjectDocument8 pagesProjectHarshit JainNo ratings yet

- TMS320F2812-Analogue To Digital ConverterDocument26 pagesTMS320F2812-Analogue To Digital ConverterPantech ProLabs India Pvt LtdNo ratings yet

- Arithmetic Coprocessor Coprocessor BasicDocument83 pagesArithmetic Coprocessor Coprocessor Basicprachi pandey100% (6)

- Adt 856 PciDocument2 pagesAdt 856 PciWagner PeresNo ratings yet

- Thermometer Designed Using AT89C51 For Displaying Digital RecordsDocument4 pagesThermometer Designed Using AT89C51 For Displaying Digital RecordsEditor IJRITCCNo ratings yet

- TTL Digital ClockDocument5 pagesTTL Digital Clockyampire100% (1)

- ECE222 DP1 Binary MultiplierDocument8 pagesECE222 DP1 Binary Multiplierprasad357No ratings yet

- Blick Propeller Clock: Ònoblinkó Main Program OverviewDocument9 pagesBlick Propeller Clock: Ònoblinkó Main Program OverviewOpLight TranNo ratings yet

- Hun Wie CounterDocument19 pagesHun Wie CounterlvsaruNo ratings yet

- 8254 TimerDocument12 pages8254 TimerPRIYANKA CHOUDHARINo ratings yet

- LNP ProjectDocument12 pagesLNP ProjectbugyourselfNo ratings yet

- PDF For Talking CalculatorDocument6 pagesPDF For Talking Calculatorsharad501kaleNo ratings yet

- HY TB4DV K Series Three Axis ManualDocument20 pagesHY TB4DV K Series Three Axis ManualP BNo ratings yet

- Contador Rapido para ProcesosDocument30 pagesContador Rapido para ProcesosJuan Antonio Chuc AkeNo ratings yet

- Atmel 42059 Joystick Game Controller Reference Design Application Note At01095Document16 pagesAtmel 42059 Joystick Game Controller Reference Design Application Note At01095kjnuhbbbhNo ratings yet

- Asynchronous CounterDocument5 pagesAsynchronous CounterJose GarciaNo ratings yet

- Programmable DSP Lecture2Document10 pagesProgrammable DSP Lecture2Paresh Sawant100% (1)

- CMPS03Document7 pagesCMPS03Đặng Xuân HồngNo ratings yet

- University of Tehran Electrical and Computer Engineering Department ECE 517-3586 Logic Design, Test # 2 Spring Semester 1376-1377 Week of Lecture 32Document7 pagesUniversity of Tehran Electrical and Computer Engineering Department ECE 517-3586 Logic Design, Test # 2 Spring Semester 1376-1377 Week of Lecture 32Joly SinhaNo ratings yet

- Coa SaurabhDocument13 pagesCoa SaurabhHarshu VagadiyaNo ratings yet

- Safari - 13 Mai 2023 À 09:40Document1 pageSafari - 13 Mai 2023 À 09:40Paréto BessanhNo ratings yet

- Review: MULTIPLY HARDWARE Version 1: °64-Bit Multiplicand Reg, 64-Bit ALU, 64-Bit Product RegDocument6 pagesReview: MULTIPLY HARDWARE Version 1: °64-Bit Multiplicand Reg, 64-Bit ALU, 64-Bit Product RegNarender KumarNo ratings yet

- Cmps 03Document12 pagesCmps 03yofianajNo ratings yet

- Adc0808 CodeDocument3 pagesAdc0808 CodebalabooksNo ratings yet

- Digital Clock Written ReportDocument9 pagesDigital Clock Written ReportmultisporkyNo ratings yet

- PCF8583Document37 pagesPCF8583lady_iuNo ratings yet

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3From EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet