Professional Documents

Culture Documents

II. Bias Circuit II. Bias Circuit: Outline

II. Bias Circuit II. Bias Circuit: Outline

Uploaded by

Phil OwusuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

II. Bias Circuit II. Bias Circuit: Outline

II. Bias Circuit II. Bias Circuit: Outline

Uploaded by

Phil OwusuCopyright:

Available Formats

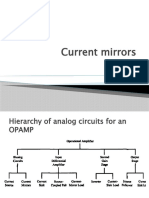

II Bias circuit

II. Bias circuit

II. Bias circuit

Introduction

Outline

Active devices (transistors) have to be properly biased to

process the signal

In an analog signal processing circuit there are two

fundamental parts:

CMOS current mirrors

Definitions

Basic stage for current mirrors

Simple current mirror

Wilson current mirror

Improved Wilson current mirror

Cascode current mirror

Modified cascode current mirror

High-compliance current mirrors (I - II)

Regulated cascode current mirror

Low-voltage current mirrors

Processing part

Bias circuit

The processing part is devoted to elaborate the signal

Dynamic requirement

Current references

The bias circuit is devoted to supply currents and/or

voltages to the processing one in order to allow it to

properly operate

Static requirement (Low-frequency, immunity to VDD noise,

temperature, and technology spread)

Introduction

Simple current reference

Current references based on a built-in voltage

Current references based on a reference voltage

Voltage references

Introduction

Supply dividers

Voltage references based on a built-in voltage

Voltage references based on the band-gap voltage

Voltage references based on MOS VTH difference

A. Baschirotto - Bias circuit

II 2

II Bias circuit

II Bias circuit

CMOS current mirrors

CMOS current mirrors

Definitions

A current mirror reads a current entering in a read-node and

mirror this current (with a suitable gain factor) to an

output node (nodes)

Applications

Bias

VDD

RL

Circuit

no. 1

Ire

f

Iout = kIRef

Iref

Circuit

no. 2

Iout

k current gain

Read

section

Current Mirror

M1

M2

Ibias

Ibias

Current mirror

Signal path

Current mirror non-idealities

Current mirror

Current gain error

VDD

Output impedance (rout)

=> reduces the output current Iout

RL

= kIRef R L + r

out

Saturation voltage (VCM)

=> for Vo<VCM the current mirror

doesn't operate correctly

Read

section

RL

Iout

Iref

Iout

Current Mirror

VCM

Isignal

2Isignal

Isignal

Isignal

rout

Vi+

Q1

=> reduces the output voltage

dynamic range

Basic trade-off:

Vi-

Ibias

dynamic range <=> precision

- Differential-to-Single Ended transformation

- Frequency behaviour

Frequency behaviour

A. Baschirotto - Bias circuit

Q2

II 3

A. Baschirotto - Bias circuit

II 4

II Bias circuit

II Bias circuit

Simple Current Mirror

Simple Current Mirror

Current gain

Output impedance (rout)

Iref

VDD

Iref

Iout

M1

M1

M2

M1

M2

Iref

M2

Iout

PMOS

NMOS

Iout

M1 operates in saturation

k' W

IRef = I1 = 2 L (VGS1 - VTH)2 (1 + VDS1)

Insert

Vtest

Evaluate

Itest

Calculate

Vtest

rout = Itest

Itest

VDS1 = VGS1 = VGS2

G

S

If M2 operates in saturation

D

vgs

gmvgs

rds

G

S

rout = rds2 =

Iout = IRef

W

L

(1 + V DS2 )

(1 + V D S 1 )

gmvgs

rds

M2

M1

k' W

Iout = I2 = 2 L (VGS2 - VTH)2 (1 + VDS2)

W

L

Vtest

vgs

1

I2

Use of long device (large L) to increase rout

Use of large (VGS VTH) for good matching (small

importance of VTH mismatch)

A. Baschirotto - Bias circuit

II 5

A. Baschirotto - Bias circuit

II 6

II Bias circuit

II Bias circuit

Simple Current Mirror

Frequency behaviour

Simple Current Mirror

Output swing

Iref

Iout

M1

Iref

M2

Iout

VDSsat2

M1

M2

Small signalequivalent circuit

The output swing in the Simple current mirror is limited to

Iin

Iout

G

Vout,min = VDSsat,2

Cgs2

Cgs1

vgs1

gm1vgs1

rds1

vgs2

M1

gm2vgs2

rds2

M2

i out

gm2/gm1

iin = 1+s(Cgs1+Cgs2)/gm1

k = gm2/gm1 = Cgs2/Cgs1

i out

k

iin = 1+s(1+k)Cgs1/gm1

fT = gm1/Cgs1

pole = (gm1/Cgs1)/(1+k) = fT/(1+k)

A. Baschirotto - Bias circuit

II 7

A. Baschirotto - Bias circuit

II 8

II Bias circuit

II Bias circuit

Simple Current Mirror

Simple Current Mirror

Factors affecting the mirror accuracy

Factors affecting the mirror accuracy

Channel length modulation ()

Channel length modulation ()

W

L

1 + VD S 2

Iout

1

IRef = W 1 + V D S 1

L

Threshold offset

Id

Parasitic resistances

Imperfect geometrical matching and current mobility

variation

VGS1=VGS2

VDS

It can be improved by increasing the output resistance.

- use of large L (typically current mirrors are not realized with

th eminimum technological L. This can results in a large

capacitance at the output node)

A. Baschirotto - Bias circuit

II 9

A. Baschirotto - Bias circuit

II 10

II Bias circuit

II Bias circuit

Simple Current Mirror

Simple Current Mirror

Factors affecting the mirror accuracy

Factors affecting the mirror accuracy

Iref

M1

Imperfect geometrical matching and current mobility

variation

Iout

M2

I 2

I

Threshold offset

Threshold of MOS transistors in close proximity can differ by

4 mV. For transistors hundred of m apart, the threshold

difference VTh can be 40 mV

k'

Cox

k' and C

are minimized with closed and centroid

ox

common structures

VTH

' = I 1 + 2

Iout

out

V G S - V T H

k' 2

Cox 2

W 2 L 2

= k' + C + W + L

ox

W 2

W +

L 2

depends on the lithographyc process

For large W a good strategy is to have W not much larger

than L and to put equal transistors in parallel

Use large (VGS VTH) to improve matching

Parasitic resistances

A parasitic resistance in series with the source determines a

voltage drop

AA

AAA

AAA

A

AA

A

AAA

A

AA

AAA

AAA

Iout

Iref

The metal resistance is of the order of 20-50 /q, with 10

squares it results 0.2-0.5 . If the current is 10 mA it

results an equivalent offset of 2-5 mV.

M1

W=W/n

I 2

I

A. Baschirotto - Bias circuit

II 11

A. Baschirotto - Bias circuit

M2

L 2

1 W'2

= ..... + n W' + L

II 12

II Bias circuit

II Bias circuit

Simple Current Mirror

Simple Current Mirror

Factors affecting the mirror accuracy

Design example

With the following technological parameter design a simple

current mirror in order that it drives to the output node

1mA and it requires 400mV

Imperfect geometrical matching and current mobility

variation

Lmin = 0.5m; ; nCox = 60A/V2 ; pCox = 30A/V2 ;

n = 0.1 V1 ; p = 0.2 V1 ; = 0 ; VTHN = VTHN = 0.7V

Example:

Circuit scheme

Iref

Which is the expected output impedance ?

Iout

M2

M1

Layout solution

M2

M2

M1

M1

M2

M2

M1

M1

I Ref

GND

I Out

A. Baschirotto - Bias circuit

II 13

A. Baschirotto - Bias circuit

II 14

II Bias circuit

II Bias circuit

Wilson current mirror

Wilson current mirror

Output swing

Increases the output resistance

Iref

Iref

Iout

M3

M3

M1

Iout

M1

M2

M2

VDSsat3

VGS2

The output swing in the Wilson current mirror is limited to

VGS1 = VGS2

I1 I2

Vout,min = VGS2 + VDSsat,3 > VTh + 2VDSsat

W

Iout L 1 1 + V D S 2

IRef = W 1 + V D S 1

L

W

L

1 + VD S 2

Iout

1

IRef = W 1 + (V D S 2 + V G S 3 )

L

2

There is a sistematic error since VDS1 = VDS2 + VGS3

A. Baschirotto - Bias circuit

II 15

A. Baschirotto - Bias circuit

II 16

II Bias circuit

II Bias circuit

Wilson current mirror

Improved Wilson current mirror

Output impedance

Iref

Current gain

Iout

M3

M1

Iref

M2

Iout

M4

M3

M1

M2

Small signal equivalent circuit

g

G3

g

R

m 3 gs3

ix

G2

S3

r ds3

m 1 g2

1/g

ds1

m2

vx

VDS1 = VDS2 + VGS3 - VGS4

vg2 = vs3 = ix/gm2

vg3 = - gm1 vg2 rT

VDS1 = VDS2

if

VGS3 = VGS4

(rT = RL //rds1)

W

L

vx = ix/gm2 + (ix - gm3 vgs3) rds3

Iout

1

IRef = W

L

vx

1

gm 3 gm 3

rout = i = g + rds3 1 + g + g

gm 1 rT

x

m2

m2

m2

W

1 + V D S 2 L 1

=

1 + V D S 1 W

L

gm3

rout rds3 g gm1rT

m2

Higher voltage for the sensing branch (M1-M4)

RL (i.e. Iref current generator impedance) must be large

A. Baschirotto - Bias circuit

No sistematic error in the current gain

II 17

A. Baschirotto - Bias circuit

II 18

II Bias circuit

Improved Wilson current mirror

II Bias circuit

Cascode Current Mirror

Current gain

Iref

Iout

M4

M3

M1

M2

Iref

Iout

M4

M3

M1

M2

Small signal equivalent circuit

VDS1 = VDS2 + VGS3 - VGS4

g m 3 vgs3

1/g

m4

G3

g

R

r ds3

m 1 g2

1/g

ds1

VDS1 = VDS2

ix

G2

S3

m2

W

L

if

VGS3 = VGS4

W

L

1 + VD S 2

Iout

1

1

IRef = W 1 + V D S 1 = W

L

L

Same equations with:

R L gm 4

vg3 = - gm1 vg2 r'T 1 + R g

L

m4

The current gain is accurate

rT' = rds1 //(RL + 1/gm4)

For large current ( i.e. with (W/L)M2 large) it allows to

decrease the output capacitance using (W/L)M3 small.

gm3

R g

gm1 r'T 1 + LR mg4

rout rds3 g

m2

L

m4

The output swing in the Wilson and improved Wilson

schemes is limited to

Vout,min = VGS2 + VDSsat,3 > VTh + 2VDSsat

A. Baschirotto - Bias circuit

II 19

A. Baschirotto - Bias circuit

II 20

II Bias circuit

II Bias circuit

Cascode Current Mirror

Output impedance

Cascode Current Mirror

Output swing

The output resistance is increased without feedback.

Small signal equivalent circuit

Iref

M4

VGS4

M3

G3

Iout

1/g

VDS3

R

VGS3

m4

VGS1

M1

m1

M2

ix

S3

1/g

m 3 gs3

r ds2

r ds3

ix= gm3 vGS3+ (vx vS3)/rds3

VGS3 = VGS4

ix= vS3/rds2

The output swing is limited to:

ix= gm3 ( vS3) + (vx vS3)/rds3

Vout,min = VGS1 + VGS4 VGS3 + VDSsat,3

ix= vS3/rds2

Vout,min = VGS2 + VDSsat,3 > VTH + 2VDSsat

rout = rds2 + rds3 + rds3 gm3 rds2 rds3 gm3 rds2

A. Baschirotto - Bias circuit

II 21

A. Baschirotto - Bias circuit

II 22

II Bias circuit

Multiple-Cascode Current Mirror

II Bias circuit

Modified Cascode Current Mirror

I Out

I Ref

M9

M8

M5

M6

M4

M3

M1

M2

Increase the output swing with the cascode output

impedance

I Ref

V

M1

I Out

M3

M2

M4 shifts the voltage VDS1 of the amount enough to bias the

gate of M3 without operating M2 out of saturation.

More cascode stage can be stacked to increase output

impedance.

For n stages

+ Output impedance

rout (rds gm )n-1rds

BUT:

- The saturation voltage increses to:

Vout,min = (n-1)VTH +nVDSsat

+ The current gain is accurate (VDS1= VDS2)

A. Baschirotto - Bias circuit

II 23

A. Baschirotto - Bias circuit

II 24

II Bias circuit

Modified Cascode Current Mirror

II Bias circuit

High-compliance current mirrors

(I)

Possible implementation

I Out

I Ref

M4

M5

I Ref

I Out

I Ref

M3

M3

M4

M1

M6

VTH+V

VTH+2V

M2

M1

M2

VTH+V

M4 is matched with M3 to get VDS1 = VDS2 (at the cost of the

output swing limitation).

The output swing is improved by the use of a level shift VSat

< V < VTH

2 L

k'W IRef -

V = VGS4 - VGS5 =

2 L

IRef 1k'W

L L

W W

L L

W W

I = I1 = I2 = I3 = I4 (current scaling is possible)

1=2=3=

=>

I4 = 4(Vov)2;

2 L

k'W I5 =

All transistors operate in saturation

Vov1 = Vov2 =Vov3 =Vov

I2 = (Vov)2;

Vov=V

=>

I3 = (Vov)2

VDS2 = Vov

VGS3 = VTH + Vov

VGS4 = VTH +2Vov

V is fixed by he geometrical dimensions of M1, M6, M4, M5

and by Vov,4.

Vov4 =

Vov4 = 2Vov

I

;

4

=>

The output swing is:

Vov =

I

= 2

4

= 44

Vout,min = VDS2 + VDS3 = 2VDSsat

Sistematic error in the current gain (VDS1 VDS2)

W

L M1

A. Baschirotto - Bias circuit

II 25

W

L M2

W

= L

M3

W

= 4 L

M4

A. Baschirotto - Bias circuit

II 26

II Bias circuit

High-compliance current mirrors

(I)

I Ref

II Bias circuit

High-compliance current mirrors

(II)

I Out

I Ref

IBias

I Ref

M3

M4

M4

M5

VTH+V

VTH+2V

M1

M2

I Out

M3

VTH+V

M1

M2

Current gain

Sistematic error due to VDS1VDS2

Sistematic error due to body effect on M3

M1=M2; M3=M4 =>

Output swing

Iout=IRef

VDSsat4>VTH to properly work

Vout,min = 2VDSsat

Output impedance

rout = rds4 gm2 rds2

The scheme can be stacked for multiple cascode

A. Baschirotto - Bias circuit

II 27

A. Baschirotto - Bias circuit

II 28

II Bias circuit

High-compliance current mirrors

(II)

IBias

I Ref

M4

M5

II Bias circuit

Regulated-cascode current mirror

I Out

I Out

M3

I Ref

M3

M1

M1

M2

M2

Vbias

Output impedance

rout = (gm3ro3)ro2A

Possible implementation

It is also possible to enter at the drain of M1

IOut

Ibias

IBias

I Bias2

M4

M5

M3

IRef

I Out

M3

M1

M2

I Ref

M1

MA

Output impedance

M2

rout = (gm3ro3)ro2(gmAroA)

Output swing

Vout,min = VGSA+ VDSsat3

Iout = IBias2 + IRef

Vout,min = VTH + 2VDSsat

Sistematic error since IrefIbias

(Solution proposed by Zeki, et al., IEE El. Letters, 5th June 1997, pp. 1042)

A. Baschirotto - Bias circuit

II 29

A. Baschirotto - Bias circuit

II 30

II Bias circuit

II Bias circuit

Low-voltage current mirror

Output swing

for different current mirrors

For low-voltage application the dc voltage drops must be

minimized in order to:

- give the maximum room for the signal swing

- not to limit the supply minimization with bias circuits

Comparison

This valid both for the input stage (reading the current) and for

the output stage (sinking the current)

1

Simple

Id

For the simple current mirror

Cascode & Wilson

2

High-compliance

Regulated Cascode

I Ref

I Out

M1

Triple Cascode

M2

VDSsat2

2VTH+3VDSsat

VTH+2VDSsat

2VDSsat

VDSsat

The output stage (M2) requires

Vout,min = VDSsat

VDS

This is minimum, thus staked-device topologies are avoided

Output impedance is increased with large L

The input stage (M1) requires

Vout,min = VTH + Vov + V(IRef)

The slope (1, 2, or 3) indicates the output impedance (rout)

A. Baschirotto - Bias circuit

II 31

This value can be reduced

A. Baschirotto - Bias circuit

II 32

II Bias circuit

II Bias circuit

Low-voltage current mirror

Low-voltage current mirror

Application

The input stage voltage requirement can be reduced by using

the low-voltage current mirror

Operational amplifier

VDD

Mb

M4

Iout

Iref

Vi-

M3

Vi+

Vo

Ibias

M2

M1

M2

Low-voltage

current mirror

The drain of M1 is fixed to be VDD - VGS3

M1

This is fixed to be equal to VDSsat

The current mirror requires one VDSsat to operate.

Iout = IM3 + Iref

A. Baschirotto - Bias circuit

II 33

A. Baschirotto - Bias circuit

II 34

II Bias circuit

II Bias circuit

CMOS current mirrors

Exercise

Comparison Table

1-

DC analysis of Simple CM

2-

AC analysis of Simple CM

- Transfer function

Configuration

Current gain

Output swing

rout

Simple

1 + VD S 2

1 + VD S 1

VDSsat

rds

Wilson

1 + VD S 2

1 + VD S 1

VTH + 2VDSsat

2

gmrds

Improved Wilson

VTH + 2VDSsat

gmrds

Cascode

VTH + 2VDSsat

gmrds

Triple Cascode

2VTH + 3VDSsat g2 r3

m ds

- Evaluate the output impedance (AC)

Triple Cascode

2VTH + 3VDSsat g2 r3

m ds

- Evaluate the signal swing (DC)

Check the sistematic error in Wilson CM (different VDS)

- Check the signal swing (DC sim.)

4-

2VDSsat

High-compliance II

2VDSsat

Regulated-cascode

1 + VD S 2

1 + VD S 1

VTH + 2VDSsat

A. Baschirotto - Bias circuit

3-

- Improve by using large L (with same W/L)

1 + VD S 2

1 + VD S 1

High-compliance I

- Output impedance (for different L, with same W/L)

Cascode CM

- Evaluate the output impedance (AC)

- Evaluate the signal swing (DC)

2

gmrds

5-

6-

Large dynamic Cascode CM

- Evaluate the output impedance (AC)

- Evaluate the signal swing (DC)

gmrds

Multiple Cascode CM

7-

Low-voltage CM operation

2 3

gm

rds

II 35

A. Baschirotto - Bias circuit

II 36

II Bias circuit

Current references

II Bias circuit

Simple current reference

(supply depedent)

Introduction

It allows to generte on-chip (no external components) a

current reference

IREF

Necessary for biasing analog subcircuits.

PMOS

NMOS

VDD

VDD

RL

M1

VB

The generated current reference is mirrored where

required, with a suitable scaling factor.

Typically the reference current in the reference current

generator is much smaller than the current level in the

main circuit (i.e. the scale factor is larger than one) in

order to reduce power consumption in the current

reference generator

IREF

M1

Voltage VB is used to bias a current mirror

For the NMOS case:

IREF =

|Vov1| =

Possible current reference generators

Simple current reference (supply depedent)

Current references based on a built-in voltage (supply

indepedent)

Current references based on a reference voltage (supply

indepedent)

IREF =

V DD V DS1

RL

A. Baschirotto - Bias circuit

2

I REF

k' (W/L)1

V DD |VTH1| |Vov1|

RL

V DD |VTH1|

IREF =

Features for a reference current

Supply dependence

Temperature dependence

Technology dependence

VB

RL

2

IREF

k' (W/L)1

RL

Supply dependence

IREF depends on supply voltage VDD

Temperature dependence

positive temperature coefficient (TC)

R 1:

|VTH|: negative temperature coefficient

|Vov|: positive temperature coefficient

II 37

A. Baschirotto - Bias circuit

II 38

II Bias circuit

Typically the sum (VGS1=|VTH| + |Vov|) has a negative TC

II Bias circuit

Current references

based on a built-in voltage

Basic principle

The current is obtained by "extracting" a built-in voltage

(Vbi) to be applied to a given resistor

VDD

VBIAS

Built-in

Voltage

(Vbi)

generator

I=0

IREF

Vbi

R

1

Vbi

IREF = R1

The dependence of the built-in voltage on temperature and

other parameters will affect the generated reference

current.

The generated current is substantially independent from

supply voltage.

Micropower current reference based on this principle are

also available.

A. Baschirotto - Bias circuit

II 39

A. Baschirotto - Bias circuit

II 40

II Bias circuit

II Bias circuit

Self-biased current reference

Self-biased current reference

(V TH + Vov )-based

(V TH + Vov )-based

Start-up circuit

VDD

IREF

M4

M3

VDD

Built-in voltage:

VB

Vbi = VGS1 = VTH + Vov

M1

IREF

M4

M3

M2

RI1

VGS1

VTH

VB

M2

M1

I1

R

W

L

W

=L

(i.e. current mirror)

I1 = I2 (for M3-M4 mirror)

V GS1

k' W

2

R1 = 2 L (V GS1 V T H)

k' W

I1 = I2 = 2 L (V GS1 V T H)2

1

RI2 = RI1 = VGS1 =

Two operating points are possible (A, B) : only one (A) is the

desired one

2I1 L

k' W + VTH

1

Typically Vov is designed to be much smaller than VTH in

order to have:

VTH

I1 R1

Low currents can be generated using large resistor

(VTH+Vov in the range of 1 V)

It is necessary to use a startup circuitry to set the desired

operating point (i.e. to ensure I 0 at the start-up)

Possible start-up circuit solution

VDD

M

4

M

3

I

Temperature dependence

R 1:

positive TC

VTH: negative TC

Vov:

positive TC (|(VTH) + |Vov|: negative TC)

VBIAS

I

START-UP

Signal

M

2

M

1

At start-up, MS is turned

on, thus forcing M4 in

the saturation region.

Then it is definitively

turned off.

VR1

R

1

Complementary structure is always possible

A. Baschirotto - Bias circuit

II 41

A. Baschirotto - Bias circuit

II 42

II Bias circuit

II Bias circuit

Self-biased

low-current reference generator

Self-biased

low-current reference generator

Vov-based

Vov-based

VDD

VDD

IREF

M4

M3

M3

VB

M1

IREF

M4

VB

M2

M1

Temperature dependence:

R 1:

positive TC

Vov: positive TC.

M2

R

Built-in voltage: Vov = Vov1 Vov2

L

W

L

L

L

= W ; W = m W

I1=I3

; m>1

slope k

I3=I4

I1=f(I2)

M3-M4 is an ideal current mirror => I3 = I4 = I1 = I2 = IREF

VTH1 = VTH2

Also for this circuit a startup circuit is necessary

2IREF L

k' W =

1

IREF = R1

2IREF L

k' W + RIREF

2

1

k' (W/L)

I2=I4

Complementary structure also available:

M3, M4 n-channel transistors (source connected to VSS);

M1, M2 p-channel transistors (source of M1 connected to

VDD);

R1 connected between source of M2 and VDD;

in n-well processes, M1 and M2 in the same well.

Vov generally ranges from tens to hundreds mV

Small currents can be obtained with not very large R

For m=10, VR 60 mV if it is required I = 1 A

=> R = 60k

A. Baschirotto - Bias circuit

II 43

A. Baschirotto - Bias circuit

II 44

II Bias circuit

II Bias circuit

VBE-based current reference

VT-based current reference

VDD

(VBE-based current reference)

M

4

M

3

Built-in voltage:

VEB = VEB1 VEB2 = VT ln(n)

Vbias

M

1

A

VDD

M

2

VREF

R

1

I

Q1

Q1 is a substrate BJT

M1 to M4 operate in saturation region (improved Wilson

current mirror)

M

3

M

4

M

1

M

2

Q1

Vbias

AQ2 = nAQ1 n > 1

L

W

R

1

I REF

1

Q1, Q2: substrate BJT with

different emitter areas:

I2

VEB2 = VT ln nISS

VS1 = VS2 =>

VREF = VEB

R1IREF = VEB1 VEB2 = VTR1 ln(n)

VT

IREF = R1 ln(n)

VEB

I = R1

To generate low currents, a large R1 is needed (VEB in the

range of 0.6 V)

Start-up circuitry is needed

Use the complementary structure for p-well processes

Temperature dependence:

R 1:

positive TC

VEB: negative TC

Small currents can be obtained with small R1

Temperature dependence:

R 1:

positive TC

V T:

positive TC

Start-up circuitry is needed

Complementary structure available only in a p-well

processes

A. Baschirotto - Bias circuit

II 45

A. Baschirotto - Bias circuit

II 46

II Bias circuit

II Bias circuit

Voltage references

Current references

based on a reference voltage

VREF

I1

VEB1 = VT ln IS S

I1 = I2 = IREF = I

VGS1 = VGS2 =>

I1 = I2 = IREF ; VA = VB

Q

2

(W/L)3 = (W/L)4, (W/L)1 = (W/L)2

L

L

L

= W ; W = W

Introduction

Voltage references are required in a number of analog

applications (e.g. signal processing, A/D converters, D/A

converters, ...).

VDD

Vbias

Different voltage references

M1

I REF

Supply voltage dividers

R

1

Voltage references based on a built-in voltage

Voltage references based on the band-gap voltage

Voltage references based on MOS threshold voltage

difference

Useful when a reference voltage is available.

This circuit has to operate at low-frequency (dc). The

opamp gain can be extremely large.

VREF

IREF = R1

(the last two types are actually special kinds of voltage

references based on a built-in voltage).

In the following, all voltages will be referred to GND

M1 in saturation region, for current mirror

Temperature dependence:

R 1:

positive TC

VREF: depends on the kind of voltage reference used

Features for a reference current

Supply dependence

Temperature dependence

Technology dependence

It is difficult to obtain a stable VREF with a small value.

=> Low reference currents need large R1

A. Baschirotto - Bias circuit

II 47

A. Baschirotto - Bias circuit

II 48

II Bias circuit

II Bias circuit

Supply voltage divider

Supply voltage divider

Resistive dividers

Diode-connected NMOS transistors

Analog circuits normally have only two dc voltage supplies

(VDD and ground)

In order to obtain dc-bias voltages, voltage dividers can be

used

Resistive or capacitive dividers are complex or silicon area

consuming

MOS in the diode configuration (i.e. operwting in saturation

region) can be used

VDD

VDD

M2 V1

R1

VREF

M1

R2

k' W

2 k' W

2

2 L (VDS1 VTH1) = 2 L (VDS2 VTH2)

1

VDS1 + VDS2 = VDD

R2

VREF = R + R VDD = VDD

1

2

Large power dissipation (small resistors) or large silicon

area occupation (large resistors).

1 =

W

L

2 =

;

1

W

L

It results a voltage division of VDD plus an offset.

VREF depends on supply voltage.

To obtain good matching, R1 and/or R2 area realized by

means of a suitable number of unity resistors

A. Baschirotto - Bias circuit

1V TH1 2V TH2

2

VDD +

1 + 2

1 + 2

V1 = VDS1 =

with < 1

II 49

Body effect on M2 can affect the operation (VTH1VTH2)

A. Baschirotto - Bias circuit

II 50

II Bias circuit

II Bias circuit

MOS Supply voltage divider

Disturbs on the supply

Supply voltage divider

If a signal vdd (usually undesired and so a disturb) is

superposed to VDD , the small signal equivalent circuit

must be considered.

Diode-connected PMOS transistors

vdd

VDD

gmbvbs2

1/gm2

1/gm1

1/gds1

C2

1/gds2

C2 = Cgs2

v1

M1

VREF

C1

1 gm1+gm2

fp = 2 C1+C2

M2

C1 = Cgs1 + Cdb1 + Csb2

1 gm2

fz = 2 C2

At low frequency (assuming gm2 >> gds2 and gm1 >> gds1)

there is a resistive partition (no capacitance effect):

Body of M2 connected to source of M2 to avoid threshold

voltage mismatches due to body effect

Assuming VTH1 = VTH2 VTH

1

VDD +

|VTH|

1 +

1 +

At high frequency there is a capacitive partition (no resistance

effect)

C2

v1hf = vdd C 1 + C 2

Several diode-connected transistors can be connected in

series, if allowed by the supply voltage ("diode chain") to

reduce current level for a given VTH

Vo/VDDnoise

VREF = VDS2 =

gmb

1/g m1 + gm1gm2

v1lf = vdd 1/g m1 + 1/g m2 + g mb /(g m1 g m2 )

fp

fp

II

fz

fz

Frequency

One of the two lines is

valid depending if

v1lf > v1hf (line I)

or

v1lf < v1hf (line II)

It results a noise injection from the power supply (VDD)

A. Baschirotto - Bias circuit

II 51

A. Baschirotto - Bias circuit

II 52

II Bias circuit

Voltage references

based on a built-in voltage

II Bias circuit

(VTH+Vov)-based voltage reference

VDD

M

4

M

3

Basic principle

I R1

Extraction of the chosen built-in voltage Vbi

R

1

Generation of the reference voltage VREF forcing IR 2

across a resistor R2, matched with R1

R2

VREF = R2IR2 = R2kIR1 = k R1 Vbi

AA

A

AA

A

AAAAAAA

Built-in voltage: Vth + Vov

M1 to M5 in saturation region

current

mirror

IR1

R

1

Vbi

R2

(W/L)3 = (W/L)4 I3 = I4 = I1 = I2 = IR1

VDD

I=0

VREF

VR1

Generation of a mirrored current IR2 = kIR1

Built-in

Voltage

(Vbi)

generator

I R2

M

2

M

1

Generation of a current IR1 = Vbi/R1

M5

(W/L)5 = k (W/L)4 IR2 = k IR1

VREF

IR2

R2

R2

VREF = k R1 VR1 = k R1 (VTH + Vov)

R2

Generally Vov is made much smaller than VTH

Temperature dependence:

VTH: negative TC

Vov:

positive TC (|(VTH) + |Vov|: negative TC)

Extraction of the bult-in voltage as in current references

based on a built-in voltage

Temperature dependence of VREF : it is a function of the

temperature dependence of Vbi

A. Baschirotto - Bias circuit

II 53

Start-up circuitry needed

Complementary structure available

A. Baschirotto - Bias circuit

II 54

II Bias circuit

VBE-based voltage reference

Voltage references

based on the band-gap voltage

VDD

VDD

M

4

M

3

I R1

M

1

VEB

Q1

II Bias circuit

M

2

M5

VBE

Q1

I R2

VREF=VBE+mVT

VREF

VT

Generation VT x m mVT

VR1

R

1

R2

Basic principle

VREF =VBE + mVT

Built-in voltage: VBE

where VT = kT/q is the thermal voltage.

M1 to M5 in saturation region

Suitable choice of m to have zero TC at the desired

operating temperature.

(W/L)3 = (W/L)4 => I3 = I4 = IR1

(W/L)1 = (W/L)2 => VR1 = VEB

At room temperature (T = 300 K):

VBE: temperature dependence = ~2.2 mV/C

VT: temperature dependence = ~+0.086 mV/C.

(W/L)5 = k (W/L)4 => IR2 = k IR1

R

R

VREF = k R2 VR1 = k R2 VEB

1

1

If m = ~25.6 we have zero TC for VREF

Temperature dependence:

VBE: negative TC.

At T = 300 K we have:

VREF = VBE + 25.6VT = ~1.26 V

(silicon band-gap)

Start-up circuitry needed.

Complementary structure for p-well processes.

A. Baschirotto - Bias circuit

II 55

A. Baschirotto - Bias circuit

II 56

II Bias circuit

II Bias circuit

Band-gap voltage reference

Band-gap voltage reference

Compensation of temperature dependence

R 2 VDD

R3

Q1, Q2: substrate BJT

with different emitter

areas

VREF

R

1

VR1

1

AQ2=nAQ1

n>1

Q1

first-order

small temperature range.

Q

2

Ref

[V]

-1.24

-1.25

VA = VB

R2 = R3 => IR2 = IR3 = I = IQ1 = IQ2

VR1 = VEB1 VEB2 = VT ln(n)

V

ln(n)

I = RR1 = VT R

1

1

R2

VREF = VEB1 + R VT ln(n)

1

VREF = VEB1 + mVT

-1.26

-60 -40 -20 0

Scheme sensitive to offset voff of the operational amplifier:

R 2

R2

voff

VREF = VEB1 + 1 + R1 voff + R1 VT lnn1 + I2R2

R

R

A

m = R2 ln(n) = R2 lnAQ2

60 80 100 120 140 T [C]

For better compensation, more complex schemes are used.

where

1

20 40

Q1

For ambient temperature:

m = ~25.6.

Different (but matched) resistors R2 and R3 can also be

used:

R

A

R

m = R2 lnR3 AQ 2

1

Q1

2

Example:

n = 8 => AQ2 = 8AQ1 (easy to obtain in layout)

R2 = R3 = ~12.3 R1

Generally, start-up circuitry is required.

Similar configuration for p-well processes

A. Baschirotto - Bias circuit

II 57

A. Baschirotto - Bias circuit

II 58

II Bias circuit

Band-gap voltage reference

II Bias circuit

Voltage references based on MOS

threshold voltage difference

Band-gap voltage multiplier

VDD

VBG

VDD

VREF

RA

M3

M4

D3

D4

RB

M1

M2

VSS

M1 to M4 in saturation region

R A

VREF = VBG 1 + RB

VD3 = VD4

where VBG is the band-gap voltage.

The multiplier can be included in the feedback loop.

It follows that:

R3

Q1

VDD

k'3 = k'4

I3 = I4 = I1 = I2 I

R2

R1

+

(W/L)3 = (W/L)4

(W/L)1 = (W/L)2 Vov1 = Vov2

VDD

VDD

Q2

both enhancement

transistors with

different VTH

one enhancement

and the other

depletion transistor

VREF

To be used when VREF > 1.26 V is required

M1 and M2:

transistors with

equal k' and

different threshold

voltages, e. g.:

VREF

VREF = VGS2 + VGS1 = VTH2 Vov2 + VTH1 + Vov1

RA

VREF = VTH1 VTH2 VTH

R2

RA

R3

V

VBG

VSS

Q1

R

1

VR1

1

REF

RB

VBG

Q

2

VTH is generally small. A voltage multiplier is required.

RB

For p-well processes.

Spread in threshold voltages, hence in VTH

R A

VREF = VBG 1 + RB

A. Baschirotto - Bias circuit

Offset of the operational amplifier affects VREF

II 59

A. Baschirotto - Bias circuit

II 60

You might also like

- Assignment On Current MirrorsDocument5 pagesAssignment On Current MirrorsanjugaduNo ratings yet

- Current MirrorsDocument15 pagesCurrent Mirrorsashok815No ratings yet

- EE42 100 Wb-Lecture19 080713-FDocument37 pagesEE42 100 Wb-Lecture19 080713-FozanistzNo ratings yet

- Ecen 607 CMFB-2011Document44 pagesEcen 607 CMFB-2011Girish K NathNo ratings yet

- Devices and Circuits Ii: Lecture GoalsDocument6 pagesDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNo ratings yet

- Fold-Cascode OPDocument11 pagesFold-Cascode OPLinAm AmatariyakulNo ratings yet

- Current MirrorsDocument76 pagesCurrent MirrorsSHRIDHAR N100% (1)

- Wide Swing Cascode Current MirrorDocument4 pagesWide Swing Cascode Current MirrorSunil M. PaiNo ratings yet

- Lect 07 Differential AmpDocument36 pagesLect 07 Differential AmpRogerZhangNo ratings yet

- 9.2 Schmitt TriggerDocument11 pages9.2 Schmitt TriggerlvsaruNo ratings yet

- Cur Mir 2 PDFDocument3 pagesCur Mir 2 PDFamiglaniNo ratings yet

- 2.diode Clipper and ClamperDocument12 pages2.diode Clipper and ClamperMounika AllagaddaNo ratings yet

- 2019S Lec Ch9 CascodeStage&CurrentMirrors RevDocument29 pages2019S Lec Ch9 CascodeStage&CurrentMirrors Revp.비둘기폴더의비밀No ratings yet

- Power Lab Manual 7th Sem 2011 - BGSDocument109 pagesPower Lab Manual 7th Sem 2011 - BGSSumanth Sathyanarayana100% (1)

- IGCT TrainingDocument57 pagesIGCT TrainingVivek KumarNo ratings yet

- Differential and Multistage AmplifiersDocument85 pagesDifferential and Multistage AmplifiersShino JosephNo ratings yet

- EEEB273 N10 - Simplified Opamp x6Document3 pagesEEEB273 N10 - Simplified Opamp x6gahbi7No ratings yet

- LDODocument7 pagesLDOSavio SNo ratings yet

- Chap05 (7 5 06)Document60 pagesChap05 (7 5 06)Amar NathNo ratings yet

- XR 2206 V 1Document16 pagesXR 2206 V 1Leon F AceroNo ratings yet

- Lec17 MOSFET IVDocument49 pagesLec17 MOSFET IVBlanca MeLendezNo ratings yet

- 4 Study of Characteristics of SCR, MOSFET & IGBTDocument12 pages4 Study of Characteristics of SCR, MOSFET & IGBTSeminars BRECWNo ratings yet

- Multi Stage Amplifier (L 1)Document21 pagesMulti Stage Amplifier (L 1)SauravAbidRahmanNo ratings yet

- Power Electronics Slides and Notes DC ConvertersDocument40 pagesPower Electronics Slides and Notes DC ConvertersAnoop MathewNo ratings yet

- Data Sheet: Silicon MMIC AmplifierDocument13 pagesData Sheet: Silicon MMIC AmplifierjohnysonycumNo ratings yet

- ICMOSFETDocument96 pagesICMOSFETthamy_15No ratings yet

- Lab 10Document9 pagesLab 10amngreenNo ratings yet

- Lecture17 Fully Diff Amps CMFBDocument28 pagesLecture17 Fully Diff Amps CMFBmohamedNo ratings yet

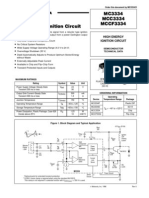

- Datasheet MC3334Document6 pagesDatasheet MC3334odipasNo ratings yet

- Microwave Engineering Microwave Networks What Are Microwaves 589Document26 pagesMicrowave Engineering Microwave Networks What Are Microwaves 589nigaar1242100% (1)

- Why Use Differential Amplifiers?: EECS 105 Fall 1998Document10 pagesWhy Use Differential Amplifiers?: EECS 105 Fall 1998Nishant GhoshNo ratings yet

- EC410 Fall 2012 FinalDocument8 pagesEC410 Fall 2012 FinalRabee Adil JamshedNo ratings yet

- A Low Voltage High Performance OTA in 0.18 Micron With High LinearityDocument10 pagesA Low Voltage High Performance OTA in 0.18 Micron With High LinearitymohsenparsauniNo ratings yet

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- Irams 06 Up 60 ADocument18 pagesIrams 06 Up 60 AAndré Roberto EvangelistaNo ratings yet

- Data Sheet: BF998 BF998RDocument12 pagesData Sheet: BF998 BF998Rachew911No ratings yet

- 2 - Design of ConverterDocument125 pages2 - Design of ConverterDevendra DhoreNo ratings yet

- DEPT. of Computer Science Engineering SRM IST, Kattankulathur - 603 203Document6 pagesDEPT. of Computer Science Engineering SRM IST, Kattankulathur - 603 203yash rawat (RA1911031010029)No ratings yet

- Mitsubishi SemiconductorDocument8 pagesMitsubishi Semiconductoredgardo2004No ratings yet

- EE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignDocument39 pagesEE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignBharat Kumar100% (1)

- 1Document43 pages1Adithya ChandrasekaranNo ratings yet

- Electronics Circuit Design LabDocument34 pagesElectronics Circuit Design Labsrvdhar100% (1)

- Design 4 SpaceDocument27 pagesDesign 4 SpacepodericofNo ratings yet

- Electric Power and Power ElectronicsDocument144 pagesElectric Power and Power ElectronicsmnamkyNo ratings yet

- 1diode PN SKDocument37 pages1diode PN SKKurma RaoNo ratings yet

- Smps For CRT Monitors With The L6565: AN1657 Application NoteDocument9 pagesSmps For CRT Monitors With The L6565: AN1657 Application Noterdc02271No ratings yet

- Current MirrorDocument7 pagesCurrent MirrorSatyasheel SinghNo ratings yet

- L060 Push Pull (2UP)Document10 pagesL060 Push Pull (2UP)srikanthkmsNo ratings yet

- 1 To 5 ManualDocument30 pages1 To 5 ManualRoshan DodiyaNo ratings yet

- L330 LowPowerOpAmps 2UPDocument7 pagesL330 LowPowerOpAmps 2UPVan Nguyen Huu VanNo ratings yet

- Super Source FollowerDocument27 pagesSuper Source Followerkhlsakfn100% (2)

- 607 ACM Extraction ParametersDocument23 pages607 ACM Extraction ParametersAMSA84No ratings yet

- TLP250 Mosfet Gate DriverDocument38 pagesTLP250 Mosfet Gate DriverKien Trung50% (2)

- ADC Power Scaling: Design Issues: Amit Tripathi Faculty of Deptt. of EN NIET, Gr. NoidaDocument17 pagesADC Power Scaling: Design Issues: Amit Tripathi Faculty of Deptt. of EN NIET, Gr. Noidaer_amittripathiNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Session-04-Current Mirror and Single Stage AmplifierDocument68 pagesSession-04-Current Mirror and Single Stage Amplifieraravind787750% (2)

- Comparison of Current Mirror Circuits Using Pspice Simulation ToolDocument4 pagesComparison of Current Mirror Circuits Using Pspice Simulation Toolsuyash_4376No ratings yet

- II. Bias Circuit II. Bias Circuit: OutlineDocument15 pagesII. Bias Circuit II. Bias Circuit: OutlineRaghu McNo ratings yet

- Comparison of CMOS Current Mirror SourcesDocument5 pagesComparison of CMOS Current Mirror SourcesidescitationNo ratings yet

- WIDLAR CURRENT SOURCE and WILSON CURRENT MIRRORDocument5 pagesWIDLAR CURRENT SOURCE and WILSON CURRENT MIRRORsurbhi100% (1)

- Multistage Transistor CircuitsDocument58 pagesMultistage Transistor CircuitsAhmad MohidNo ratings yet

- Formula Sheet - Final ExamDocument2 pagesFormula Sheet - Final ExamSABINA MISHRANo ratings yet

- Wilson Current MirrorDocument3 pagesWilson Current MirrorAnisha AgarwalNo ratings yet

- ECC508 Electronics Engineering Lab - II - VLSIDocument40 pagesECC508 Electronics Engineering Lab - II - VLSIRAJA RAMALINGAMNo ratings yet

- Current MirrorDocument13 pagesCurrent Mirrorakshaykamath123No ratings yet

- Comparative Analysis of Different Current Mirror Using 0.35 M and Its ApplicationDocument5 pagesComparative Analysis of Different Current Mirror Using 0.35 M and Its ApplicationaliNo ratings yet

- Current MirrorsDocument76 pagesCurrent MirrorsSHRIDHAR N100% (1)

- Analog Vls I ProjectDocument8 pagesAnalog Vls I ProjectLakshmi Sri Ram GannavarapuNo ratings yet

- Note 5: Current Mirrors: 1 The Diode-Connected TransistorDocument12 pagesNote 5: Current Mirrors: 1 The Diode-Connected Transistormohana valliNo ratings yet

- Building Blocks of Integrated Circuit Amplifiers:: ECE 3120 Microelectronics II Dr. Suketu NaikDocument54 pagesBuilding Blocks of Integrated Circuit Amplifiers:: ECE 3120 Microelectronics II Dr. Suketu NaikDavid JordanNo ratings yet

- Current MirrorsDocument15 pagesCurrent Mirrorsashok815No ratings yet

- A Tutorial For Electronic Circuit ...Document5 pagesA Tutorial For Electronic Circuit ...Chito June TumolvaNo ratings yet

- Lab3 BJT Current MirrorsDocument5 pagesLab3 BJT Current MirrorsaublysodonNo ratings yet

- EEEB273 N04 - CurrentSources MOSFET x6 PDFDocument10 pagesEEEB273 N04 - CurrentSources MOSFET x6 PDFKaelan LockhartNo ratings yet

- Analysis of Low Voltage Bulk-Driven High Swing Cascode Current Mirrors For Low Voltage ApplicationsDocument10 pagesAnalysis of Low Voltage Bulk-Driven High Swing Cascode Current Mirrors For Low Voltage ApplicationsIJRASETPublicationsNo ratings yet

- Current Mode Sar Adc in 180nm Cmos TechnologyDocument83 pagesCurrent Mode Sar Adc in 180nm Cmos TechnologyKasi BandlaNo ratings yet

- Layout and Analysis of Different Current Mirror Using 45nm TechnologyDocument5 pagesLayout and Analysis of Different Current Mirror Using 45nm TechnologyEditor IJRITCCNo ratings yet

- Current and Voltage Sources: Analog Design For CMOS VLSI SystemsDocument37 pagesCurrent and Voltage Sources: Analog Design For CMOS VLSI SystemsKaelan LockhartNo ratings yet

- Integrated CircuitDocument160 pagesIntegrated Circuitpcjoshi02No ratings yet

- Wilson Current Sourc1Document4 pagesWilson Current Sourc1prinxesparrowNo ratings yet

- Chapter - 01 Differential and Multistage AmplifiersDocument93 pagesChapter - 01 Differential and Multistage AmplifiersAlaaeeeNo ratings yet

- Lab (GPDK)Document49 pagesLab (GPDK)Murali MurariNo ratings yet

- Current Mirror Circuit - Wilson and Widlar Current Mirroring TechniquesDocument13 pagesCurrent Mirror Circuit - Wilson and Widlar Current Mirroring TechniquesGanga PandeyNo ratings yet

- Lab 8 - Current MirrorDocument18 pagesLab 8 - Current MirrorKram Nhoj TabatabNo ratings yet