Professional Documents

Culture Documents

Abstract

Abstract

Uploaded by

Jatin NagpalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Abstract

Abstract

Uploaded by

Jatin NagpalCopyright:

Available Formats

Abstract

This project consists of two parts1. In the first part we will design digital circuits on a FPGA based platform (SPARTAN 3E)

using verilog and simulate the same in Orcad Pspice.

2. In the second part we will inject stuck at 0 and stuck at 1 fault in the above mentioned

circuit and generate a test pattern based on fault injection in the FPGA.

This method is able to perform fault diagnosis for stuck-at-0 and stuck-at-1 faults, which can

locate resource faults in the logic elements of FPGA We use SPARTAN 3Eas the object to

generate the test pattern, work out the test circuit and synthesis them Finally, the test circuit is

injected with stuck-at-0 and stuck-at-1 faults and the test patterns are generated by using

PSPICE.

On many occasions, the working environment (such as electrical stress, field effect, temperature

and so on) always leads to the logic resource failure which happens in LE (Logic Element). We

approach a test pattern generation method based on fault injection for logic elements of FPGA.

We design the circuit using verilog and synthesize the same using Xilinx Project Navigator on

the FPGA. Building the corresponding simulation model in SPICE, we inject fault (s-a-0 or s-a1 fault) to every required node and make simulation. In each simulation we can get a

corresponding test pattern. When the s-a-0 or s-a-1 fault occurs in FPGA, using the test pattern

can locate the fault logic resource. Because the FPGA can be reconfigured, we can repair the

system function by changing of the layout.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5822)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Lista Oficial de Proveedor ChinosDocument9 pagesLista Oficial de Proveedor ChinosHerber Malarin Leon100% (2)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Final NMDocument17 pagesFinal NMMausoomNo ratings yet

- English Advanced Vocab and Structure Practice - 208pDocument208 pagesEnglish Advanced Vocab and Structure Practice - 208pspataruancadaniela92% (83)

- Instrumentation QC Inspector Course & Interview QuestionsDocument12 pagesInstrumentation QC Inspector Course & Interview Questionszhangyili100% (2)

- 21 FSM ExamplesDocument4 pages21 FSM ExamplesvikramkolanuNo ratings yet

- CV SidhDocument2 pagesCV SidhJatin NagpalNo ratings yet

- What Is Reeling?: WhichDocument1 pageWhat Is Reeling?: WhichJatin NagpalNo ratings yet

- Importance of Communication Skills: Sidharth Nagpal Neha Gupta Manjari Minti Jain Nikita JainDocument32 pagesImportance of Communication Skills: Sidharth Nagpal Neha Gupta Manjari Minti Jain Nikita JainJatin NagpalNo ratings yet

- SEBI Act 1992Document11 pagesSEBI Act 1992Jatin NagpalNo ratings yet

- Project On: "Neyveli Lignite Corporation Limited"Document12 pagesProject On: "Neyveli Lignite Corporation Limited"Jatin NagpalNo ratings yet

- Electricity Pre-TestDocument15 pagesElectricity Pre-TestAries DolarNo ratings yet

- CH 10 FeebackDocument127 pagesCH 10 Feeback鄭又嘉No ratings yet

- Aircraft PCB Design, Layout, and Assembly ProcessesDocument6 pagesAircraft PCB Design, Layout, and Assembly ProcessesjackNo ratings yet

- Load Transfer SwitchDocument2 pagesLoad Transfer SwitchBruce EgglestonNo ratings yet

- Renesas R2A20113ASP#W5 DatasheetDocument13 pagesRenesas R2A20113ASP#W5 DatasheetbirricaNo ratings yet

- Thermostat Thermo 091 - User'S Manual: Prog ProgDocument2 pagesThermostat Thermo 091 - User'S Manual: Prog ProgSnow White100% (1)

- Shadow Alarm PPT by Sachin Rajak With Saurav ShekharDocument18 pagesShadow Alarm PPT by Sachin Rajak With Saurav ShekharSachin Rajak38% (8)

- In Life.: The PSBDocument4 pagesIn Life.: The PSBctakahac6ectaNo ratings yet

- Panel Outside View: 3508B, 3508C, 3512B, 3512C, 3516C MAR PROP, 3518B, C32 AUX GS 3512C MAR PROP, 3516B, 3516CDocument2 pagesPanel Outside View: 3508B, 3508C, 3512B, 3512C, 3516C MAR PROP, 3518B, C32 AUX GS 3512C MAR PROP, 3516B, 3516CAsep ShaifurrahmanNo ratings yet

- Nmos FabricationDocument45 pagesNmos FabricationDr-GopalNo ratings yet

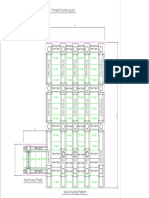

- Precast Concrete LayoutDocument1 pagePrecast Concrete LayoutAmin ZuraiqiNo ratings yet

- IEEE Standard Requirements For Secondary Network ProtectorsDocument56 pagesIEEE Standard Requirements For Secondary Network ProtectorsMahmoud LotfyNo ratings yet

- Pulley Information and Centre Distance Allowances: Table 3. Dimensions of Standard V-Grooved PulleysDocument1 pagePulley Information and Centre Distance Allowances: Table 3. Dimensions of Standard V-Grooved PulleysyokelomeNo ratings yet

- Beckman Coulter X15R CentrifugaDocument60 pagesBeckman Coulter X15R CentrifugaRicardoRiveraNo ratings yet

- ALIMAK SCANDO 450 DOL 32ext. 50Hz 1278 EN Oct 2020Document1 pageALIMAK SCANDO 450 DOL 32ext. 50Hz 1278 EN Oct 2020Boruida MachineryNo ratings yet

- 11-5. Troubleshooting Circuit Diagram For Welding Generator (Deutz F3L912-Powered CC Models)Document2 pages11-5. Troubleshooting Circuit Diagram For Welding Generator (Deutz F3L912-Powered CC Models)helmiNo ratings yet

- M54HC221/221A M74HC221/221A: Dual Monostable MultivibratorDocument14 pagesM54HC221/221A M74HC221/221A: Dual Monostable MultivibratornooorNo ratings yet

- Lenze 9300 Vector Manual 0-37-90kW v3 PDFDocument458 pagesLenze 9300 Vector Manual 0-37-90kW v3 PDFmohammed alkadiNo ratings yet

- Camera Lens Sizes, Mounts & AdaptersDocument11 pagesCamera Lens Sizes, Mounts & AdaptersBenjamin DoverNo ratings yet

- AXERA 5-140 4408: Section 1Document22 pagesAXERA 5-140 4408: Section 1YuriPasenkoNo ratings yet

- AERODYN2 Part 1 Wing TheoryDocument23 pagesAERODYN2 Part 1 Wing TheorySecretNo ratings yet

- Minimum Ignition CurvesDocument6 pagesMinimum Ignition CurvesreeawsNo ratings yet

- (Exact) Comparison Between CB, CC, CE Configuration of BJT - ETechnoGDocument4 pages(Exact) Comparison Between CB, CC, CE Configuration of BJT - ETechnoGSudip MondalNo ratings yet

- Final Drawing-R5D2013Document79 pagesFinal Drawing-R5D2013batizap batizapNo ratings yet

- Canon EF 70 210mm f35 45 USM PartsDocument8 pagesCanon EF 70 210mm f35 45 USM PartsfabiofmudoNo ratings yet

- Calculation Due To High AltitudeDocument1 pageCalculation Due To High AltitudemanishNo ratings yet

- Rectificador Makita gd800c PDFDocument3 pagesRectificador Makita gd800c PDFAlexis GomezzNo ratings yet