Professional Documents

Culture Documents

134 1462424081 - 04-05-2016 PDF

134 1462424081 - 04-05-2016 PDF

Uploaded by

Editor IJRITCCCopyright:

Available Formats

You might also like

- Multiplexer and DemultiplexerDocument5 pagesMultiplexer and DemultiplexerAdebayo AdebariNo ratings yet

- 16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 MuxDocument4 pages16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 Muxsatishbojjawar148458% (19)

- MultiplexerDocument16 pagesMultiplexerPARTEEK RANANo ratings yet

- Mux Ra1911004010178Document10 pagesMux Ra1911004010178Shivanshu TripathiNo ratings yet

- Lab 6Document3 pagesLab 6فیضان حنیفNo ratings yet

- Multiplexer and DemultiplexerDocument12 pagesMultiplexer and Demultiplexermarck_camamaNo ratings yet

- Efficient Multiplexer Synthesis TechniquesDocument8 pagesEfficient Multiplexer Synthesis TechniquesModin HbNo ratings yet

- MUXDocument6 pagesMUXSunil KumarNo ratings yet

- 271 7Document0 pages271 7Usman Sabir100% (1)

- Volume 3 - Number 1 - Tools For Microwave Radio Communications System DesignDocument13 pagesVolume 3 - Number 1 - Tools For Microwave Radio Communications System DesignArter AlayNo ratings yet

- Implementation of 8Ã 1 MultiplexerDocument5 pagesImplementation of 8Ã 1 MultiplexerFrancesco De FlorenceNo ratings yet

- Logika Kombinasi II (Lie)Document10 pagesLogika Kombinasi II (Lie)Desi NoviantiNo ratings yet

- Mimo and OFDM in Wireless CommunicationDocument5 pagesMimo and OFDM in Wireless CommunicationEditor IJRITCCNo ratings yet

- CS 8351 Digital Principles and System Design: MultiplexersDocument25 pagesCS 8351 Digital Principles and System Design: Multiplexerspadmaa1No ratings yet

- Chapter4: Combinational Logic: Originally by Reham S. Al-MajedDocument14 pagesChapter4: Combinational Logic: Originally by Reham S. Al-Majedرغوووودي رغووووديNo ratings yet

- Report On 4x1 MultiplexerDocument17 pagesReport On 4x1 MultiplexerPRAVEEN KUMAWATNo ratings yet

- Analog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidriDocument10 pagesAnalog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidrivenuraoNo ratings yet

- BER Performance of MU-MIMO System Using Dirty Paper CodingDocument4 pagesBER Performance of MU-MIMO System Using Dirty Paper CodingInternational Journal of Electrical and Electronics EngineeringNo ratings yet

- Functions of Multiplexers in A Data Communication Network PDFDocument8 pagesFunctions of Multiplexers in A Data Communication Network PDFAbdu AlhaddiNo ratings yet

- Multiplexer: By: Teknik Elektro 2Document89 pagesMultiplexer: By: Teknik Elektro 2joxNo ratings yet

- A New Approach For Finite-Length Framework of Multi-Input Multi-Output MmseDocument6 pagesA New Approach For Finite-Length Framework of Multi-Input Multi-Output MmseTavvaNo ratings yet

- COA - Experiment No 05-MuxdemuxDocument4 pagesCOA - Experiment No 05-MuxdemuxSakshi Shailendra GoleNo ratings yet

- Performance Enhancement of MIMO MC CDMA System Employing Cylically Rotated Complete Complementary CodesDocument4 pagesPerformance Enhancement of MIMO MC CDMA System Employing Cylically Rotated Complete Complementary CodesEditor IJRITCCNo ratings yet

- ?notes On Multiplexers?Document14 pages?notes On Multiplexers?Sushma ShivaniNo ratings yet

- Ijecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)Document11 pagesIjecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)IAEME PublicationNo ratings yet

- Performance Analysis of Ofdm Transceiver Using GMSK Modulation TechniqueDocument5 pagesPerformance Analysis of Ofdm Transceiver Using GMSK Modulation TechniqueEditor IJRITCCNo ratings yet

- Multiplexer and DemultiplexerDocument18 pagesMultiplexer and DemultiplexerTara SharmaNo ratings yet

- Random Waveform Using Digital Multiplexer: Working PaperDocument5 pagesRandom Waveform Using Digital Multiplexer: Working PaperBunk WahisbullahNo ratings yet

- Multiplex Er 1Document19 pagesMultiplex Er 1pkrk123456789100% (1)

- 16x16 Multiuser MIMO Testbed Employing Simple AdaptiveDocument5 pages16x16 Multiuser MIMO Testbed Employing Simple AdaptiveNhật LongNo ratings yet

- DLD 7 StudentDocument6 pagesDLD 7 StudentAminul IslamNo ratings yet

- EC31 GuideQuestionsMuxDocument2 pagesEC31 GuideQuestionsMuxGrant Lewis BulaongNo ratings yet

- Quick HelpDocument12 pagesQuick HelpLeo TDNo ratings yet

- Efficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogDocument12 pagesEfficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogAnonymous e4UpOQEPNo ratings yet

- MultiplexerDocument7 pagesMultiplexerRavi Tej AdusumilliNo ratings yet

- Avionics Lecture Handouts (L-16)Document4 pagesAvionics Lecture Handouts (L-16)Gowri ShankarNo ratings yet

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Document10 pagesDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- Expt 4. 16x1 Mux Using 4x1 MuxDocument6 pagesExpt 4. 16x1 Mux Using 4x1 Muxanon_64997028367% (3)

- Implementing Boolean Function Over Multiplexer: ObjectivesDocument3 pagesImplementing Boolean Function Over Multiplexer: ObjectivesALviNo ratings yet

- COMBINATIONAL CIRCUITS Part 1Document28 pagesCOMBINATIONAL CIRCUITS Part 1Roob HoodNo ratings yet

- Lab 09 UpdatedDocument4 pagesLab 09 UpdatedALISHBA AZAMNo ratings yet

- Damson University College of Engineering Computer Engineering DepartmentDocument5 pagesDamson University College of Engineering Computer Engineering DepartmentZedrik MojicaNo ratings yet

- Coa Exp4Document4 pagesCoa Exp4anshkasaudhan71463No ratings yet

- Asghari CsiDocument6 pagesAsghari CsiMarwan AhmedNo ratings yet

- DE Viva QuestionDocument5 pagesDE Viva QuestionDevu NarayanaNo ratings yet

- COMSOL 5.0 RF TutorialsDocument402 pagesCOMSOL 5.0 RF TutorialsMuhammad Ahtisham Asif100% (2)

- MIMO Technologies in 3GPP LTE and LTE-AdvancedDocument11 pagesMIMO Technologies in 3GPP LTE and LTE-AdvancedPreyas HathiNo ratings yet

- Energy-Aware Utility Regions: Multiple Access Pareto BoundaryDocument11 pagesEnergy-Aware Utility Regions: Multiple Access Pareto BoundaryjayaNo ratings yet

- DESIGN AND SIMULATION OF 2-TO-4 DECODER USING 32nm, 45nm AND 65nm CMOS TECHNOLOGYDocument4 pagesDESIGN AND SIMULATION OF 2-TO-4 DECODER USING 32nm, 45nm AND 65nm CMOS TECHNOLOGYijsret0% (1)

- VTC PaperDocument6 pagesVTC PaperOPTICALMIMOOFDMNo ratings yet

- Coa Unit-2Document25 pagesCoa Unit-2PARTEEK RANANo ratings yet

- Mobile Coverage Problem Analysis by Using NS2Document4 pagesMobile Coverage Problem Analysis by Using NS2International Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Comparative Study of Approximate MultipliersDocument24 pagesComparative Study of Approximate MultipliersSUDHEER SNo ratings yet

- Logarithmic Multiplier: An Analytical ReviewDocument3 pagesLogarithmic Multiplier: An Analytical ReviewInnovative Research PublicationsNo ratings yet

- Simulation of Convolutional EncoderDocument5 pagesSimulation of Convolutional EncoderInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Experiment 5 MUX DEMUXDocument4 pagesExperiment 5 MUX DEMUXMD Sadique AnsariNo ratings yet

- Weighted Least Squares Kinetic Upwind Method Using Eigen Vector BasisDocument55 pagesWeighted Least Squares Kinetic Upwind Method Using Eigen Vector BasiskonarkaroraNo ratings yet

- Using Artificial Neural Networks for Analog Integrated Circuit Design AutomationFrom EverandUsing Artificial Neural Networks for Analog Integrated Circuit Design AutomationNo ratings yet

- Software Radio: Sampling Rate Selection, Design and SynchronizationFrom EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationNo ratings yet

- Importance of Similarity Measures in Effective Web Information RetrievalDocument5 pagesImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCNo ratings yet

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNo ratings yet

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNo ratings yet

- A Study of Focused Web Crawling TechniquesDocument4 pagesA Study of Focused Web Crawling TechniquesEditor IJRITCCNo ratings yet

- Prediction of Crop Yield Using LS-SVMDocument3 pagesPrediction of Crop Yield Using LS-SVMEditor IJRITCCNo ratings yet

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocument5 pagesDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCNo ratings yet

- 44 1530697679 - 04-07-2018 PDFDocument3 pages44 1530697679 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocument3 pagesPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaNo ratings yet

- 45 1530697786 - 04-07-2018 PDFDocument5 pages45 1530697786 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Itimer: Count On Your TimeDocument4 pagesItimer: Count On Your Timerahul sharmaNo ratings yet

- 41 1530347319 - 30-06-2018 PDFDocument9 pages41 1530347319 - 30-06-2018 PDFrahul sharmaNo ratings yet

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocument5 pagesHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaNo ratings yet

- Paper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineDocument4 pagesPaper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineEditor IJRITCCNo ratings yet

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocument3 pagesSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaNo ratings yet

- 49 1530872658 - 06-07-2018 PDFDocument6 pages49 1530872658 - 06-07-2018 PDFrahul sharmaNo ratings yet

134 1462424081 - 04-05-2016 PDF

134 1462424081 - 04-05-2016 PDF

Uploaded by

Editor IJRITCCOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

134 1462424081 - 04-05-2016 PDF

134 1462424081 - 04-05-2016 PDF

Uploaded by

Editor IJRITCCCopyright:

Available Formats

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

570 - 573

________________________________________________________________________________________________________

Area Efficient, Low Power 4:1 Multiplexer using NMOS 45nm Technology

#1

Pragati Gupta,*1Keshav Mehrotra, *1Khushboo Kashyap, *1Harmeet Kaur, *1Parth Dhall

#1

Associate Professor, *1 UG Scholar

Department of Electronics & Communication Engineering

Moradabad Institute of Technology, Moradabad

Uttar Pradesh, India

Abstract: The field of electronics is trending with miniaturization and reduction in the threshold voltage. In this paper, we dealt with the efficient

use of die area and optimum usage of power. This paper shows the contrast between conventional MUX and MUX using NMOS transistors

and accentuates the advantages of the latter. The conventional 4:1 MUX consisted of a total of four AND gates and few inverters which made it

occupy more die area but in this paper we have presented the design of 4:1 MUX which occupies less area on the die. Multiplexer is a device

which works on the principle of MISO (Multiple Input Single Output).

Keywords: MUX, PISO, SIPO, DeMUX.

__________________________________________________*****_________________________________________________

[I] Introduction

In digital electronics we deal only with high and

low or ON and OFF state of the current. As we know that

actually nothing is digital and all the digital signals are

obtained from their analog counterpart, so we talk of the

digital world but not without the analog signals. The

processes involved in doing the jump from analog to digital

involves some continuous series of processes which includes

first sampling then quantizing and then encoding of the

digital signal. The manipulation of digital signals involves

digital devices which include gates, decoders, registers,

counters and multiplexers, etc. and in this paper we present

the area efficient design of a 4:1 Multiplexer.

Multiplexers (also known as MUX) are the type of

digital devices which have many inputs and only one output.

The output is nothing but is only either of the inputs and the

selection of the inputs is decided by the combination of the

select lines. It works on Parallel Input Serial Output (PISO)

principle. If we have an m-to-1 MUX, where m=2n, then we

would have to use n select lines for selecting the m

inputs accordingly. Thus, different types of MUX can be

made like 2:1, 4:1, 8:1, 16:1, 32:1 etc., by choosing the n

number of select lines.

[II] Multiplexers

have de-multiplexers (De-MUX) which work just the

opposite way as of MUX i.e. they have one input and

multiple outputs. It works on the principle of Serial Input

Parallel Output (SIPO). Multiplexers can also be expanded

with the same naming conventions as de-multiplexers.

[III] Conventional design of 4:1 MUX using AND &

NOT gates

A 4-to-1 MUX will consist of two select lines S1

and S2 whose combinations will decide which input is to be

selected.As shown in table 1, the combination of S1S2 will

decide which input is to be fed to the output.

Table 1: Truth table of 4:1 MUX

S1

S2

Output

0

0

Input 1

0

1

Input2

1

0

Input 3

1

1

Input 4

At the output, we have connected four LEDs which

will glow when the output is high as shown in fig. 2.

As stated previously, a multiplexer, abbreviated as

MUX, is a device that has multiple inputs and one output.

The schematic of MUX is shown in figure 1.

Fig. 1: Schematic symbol of 4:1 MUX

Fig. 2: 4:1 MUX using AND &NOT gates

MUX is a device which is used for the transmission

of multiple streams of digital data along one channel. These

are fitted at the transmitter side. At the receiver side, we

In the circuit, we have taken four 3 input AND

gates which are made of total of 8 NMOS and 8 PMOS

570

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

570 - 573

________________________________________________________________________________________________________

transistors and two inverters are made by a total of 2 PMOS

and NMOS transistors. Thus, this whole circuit is made up

of a total of 36 transistors which are huge! This lot number

of transistors leads to high power dissipation and more die

area.

Fig. 3: Working diagram of 4:1 MUX

The working of the 4:1 MUX can be explained

with the help of fig. 3 which shows how the input is selected

the output when the select lines S1 and S2 are selected and

how LEDs will glow accordingly.When both the select lines

are zero that means S1=S2=0 then input 1 is selected at the

output, as shown in fig.3 (a). Similarly, when S1=0 and S2=1

then input 2 is selected at the output, as shown in fig. 3 (b).

Fig 3 (c) shows when select lines S1=1 and S2=0 then input3

is fed to the output of the multiplexer (4:1). Fig. 3 (d) shows

when select lines S1=1 and S2=1 are selected then input 4 is

selected at the output of the MUX. Thus, fig. 3 works

according to the truth table 1.

Fig. 4: Output waveform of 4:1 MUX

The output waveform of 4-to-1 MUX is shown in

fig.4. In this diagram it can be seen that when S 1& S2 are

low (0) then output1 is high (1), this means that the input1 is

selected at the output. Similarly, when S1& S2 are low and

high respectively, output2 is high. Output3 is high when S 1

is high and S2 is low and output 4 is high when S1 and S2

both are high.The fabrication layout of 4:1 MUX is shown

in fig. 5.

571

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

570 - 573

________________________________________________________________________________________________________

Fig. 5: Fabrication layout of 4:1 MUX

In todays miniaturization scenario, the main

requirement is of lower power dissipation and less die area

for the implementation of any circuit. So the circuit shown

in figure 3 lags on these parameters. Hence, to overcome

these problems, we present an area efficient design of a 4to1 MUX in this paper using NMOS transistors only.

[IV] Proposed design of 4:1 MUX using NMOStransistor

The area efficient design of a 4-to-1 MUX is shown

in fig. 6. In this design, 6 NMOS transistors are used and 1

LED to show the status of the output.

Fig. 6: 4:1 MUX using NMOS

In fig. 6, A, B, C and D are the four inputs to the

MUX and S1 and S2 are the select lines. Table 2 shows how

the input A, B, C and D are selected at the output.

Table 2: Truth table of 4:1 MUX (NMOS)

S1

0

0

1

1

S2

0

1

0

1

Output

Input A

Input B

Input C

Input D

The working diagram of 4:1 MUX using NMOS is

shown in the fig. 7.

Fig. 7: Working diagram of 4:1 MUX using NMOS

transistor

572

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

570 - 573

________________________________________________________________________________________________________

It is clear from fig. 7 that when the combination of

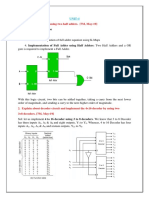

Table 3: Comparison between conventional MUX and

S1S2 is 00 then input A is selected and for 01; input B is

MUX using NMOS

selected, for 10; input C is selected and for 11 input D is

Properties

Conventional

NMOS

carried forward to the output of the MUX. Thus, verifying

MUX

MUX

the truth table 2 of a 4:1 MUX.

Number

of

transistors

36

(NMOS+PMOS)

6 (NMOS)

Power

consumption

75.596W

75.65W

Length

68.5m

45.7m

Breadth

9.4m

8.2m

Area

640.1m2

374.7m2

Fig. 8: Output waveform of 4:1 MUX using NMOS

transistor

The output waveform of NMOS MUX is shown in

the fig. 8 in which when S1S2 both are low (0) then input A

is high (1); when input S1 and S2 are low and high

respectively then input B is high; for input C to be high S 1 is

high and S2 is low. Similarly, when S1S2 both are high, input

D is high. Thus the combination of S1S2 is solely responsible

for the selection of inputs and then giving the corresponding

output. The fabrication layout is shown in the fig. 9.

[VI] Conclusion

From table 3, it can be concluded that the

percentage decrease in the area of the die is approximately

41% as compared to the fabrication of 4:1 MUX using logic

gates, which is a huge achievement! This decrease in area

will in turn result in the reduction of complexity and

efficient usage of power. Thus the area efficient design of a

4:1 MUX using NMOS 45 nm technology is implemented.

References

[1]

[2]

[3]

[4]

Fig.9: Fabrication layout of 4:1 MUX using NMOS

transistor

[5]

From the diagrams, it is clear that the use of NMOS

transistors for making 4-to-1 MUX helps to reduce the die

area and the power dissipation in turn.

[V] Result analysis

From the above discussion, it was seen that the

design of 4:1 MUX using NMOS transistors was much more

area efficient than the conventional MUX made using logic

gates (AND & NOT Gates). In the table 3 given below, it

can also be seen that not only the area but other parameters

like power consumption, speed of operation and number of

transistors are also improved and in such way, the design of

MUX shown in fig. 6 is more advantageous than the

conventional MUX design.

[6]

[7]

[8]

Sarita, Jyoti Hooda, Shewta Chawla, Design and

implementation of low power 4:1 Multiplexer using

adiabatic logic, IJITEE, Vol. 2 Issue-6, May 2013.

M. Morris Mano, Michael D. Giletti, Digital Design

with an introduction to type Verilog HDL, 5th Edition,

pp. 158-163.

John M. Yarbough, Digital logic applications and

design, 3rd Edition, Thomson, 2002.

S. Samnata, Power efficient VLSI design using

adiabatic logic and estimation of power dissipation using

VLSI-EDA tool, Special issue Of International Journal

of Computer Communication Technology, Vol. 2 Issue

2,3,4, pp. 300-303, 2010.

Vandana Shukla, O.P. Singh, G.R. Mishra, R.K. Tiwari,

Novel design of a 4:1 Multiplexer circuit using

Reversible

Logic,

International

Journal

of

Computational Engineering Research, Vol. 3, Issue 10,

Oct 2013.

Weste, CMOS VLSI Design: A Circuits and Systems

Perspective, 3rd Edition, Pearson, 2010.

V.S. Ingole, Prof. V.T. Gaikwad, Design of Multiplexer

using CMOS Ternary Logic, IJERA, Vol. 2 Issue-2,

April 2012.

Maruf M. Ali, S.M. Maniul Islam, Md. Mehedi Farhad,

Analysis of CMOS Multiplexer of different area and

logic styles, IOSR-JVSP, Vol. 3 Issue-6, Dec 2013.

573

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

You might also like

- Multiplexer and DemultiplexerDocument5 pagesMultiplexer and DemultiplexerAdebayo AdebariNo ratings yet

- 16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 MuxDocument4 pages16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 Muxsatishbojjawar148458% (19)

- MultiplexerDocument16 pagesMultiplexerPARTEEK RANANo ratings yet

- Mux Ra1911004010178Document10 pagesMux Ra1911004010178Shivanshu TripathiNo ratings yet

- Lab 6Document3 pagesLab 6فیضان حنیفNo ratings yet

- Multiplexer and DemultiplexerDocument12 pagesMultiplexer and Demultiplexermarck_camamaNo ratings yet

- Efficient Multiplexer Synthesis TechniquesDocument8 pagesEfficient Multiplexer Synthesis TechniquesModin HbNo ratings yet

- MUXDocument6 pagesMUXSunil KumarNo ratings yet

- 271 7Document0 pages271 7Usman Sabir100% (1)

- Volume 3 - Number 1 - Tools For Microwave Radio Communications System DesignDocument13 pagesVolume 3 - Number 1 - Tools For Microwave Radio Communications System DesignArter AlayNo ratings yet

- Implementation of 8Ã 1 MultiplexerDocument5 pagesImplementation of 8Ã 1 MultiplexerFrancesco De FlorenceNo ratings yet

- Logika Kombinasi II (Lie)Document10 pagesLogika Kombinasi II (Lie)Desi NoviantiNo ratings yet

- Mimo and OFDM in Wireless CommunicationDocument5 pagesMimo and OFDM in Wireless CommunicationEditor IJRITCCNo ratings yet

- CS 8351 Digital Principles and System Design: MultiplexersDocument25 pagesCS 8351 Digital Principles and System Design: Multiplexerspadmaa1No ratings yet

- Chapter4: Combinational Logic: Originally by Reham S. Al-MajedDocument14 pagesChapter4: Combinational Logic: Originally by Reham S. Al-Majedرغوووودي رغووووديNo ratings yet

- Report On 4x1 MultiplexerDocument17 pagesReport On 4x1 MultiplexerPRAVEEN KUMAWATNo ratings yet

- Analog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidriDocument10 pagesAnalog and Digital Electronics 21CS33: Venugopala Rao A S Dept. of Computer Science and Design AIET, MoodbidrivenuraoNo ratings yet

- BER Performance of MU-MIMO System Using Dirty Paper CodingDocument4 pagesBER Performance of MU-MIMO System Using Dirty Paper CodingInternational Journal of Electrical and Electronics EngineeringNo ratings yet

- Functions of Multiplexers in A Data Communication Network PDFDocument8 pagesFunctions of Multiplexers in A Data Communication Network PDFAbdu AlhaddiNo ratings yet

- Multiplexer: By: Teknik Elektro 2Document89 pagesMultiplexer: By: Teknik Elektro 2joxNo ratings yet

- A New Approach For Finite-Length Framework of Multi-Input Multi-Output MmseDocument6 pagesA New Approach For Finite-Length Framework of Multi-Input Multi-Output MmseTavvaNo ratings yet

- COA - Experiment No 05-MuxdemuxDocument4 pagesCOA - Experiment No 05-MuxdemuxSakshi Shailendra GoleNo ratings yet

- Performance Enhancement of MIMO MC CDMA System Employing Cylically Rotated Complete Complementary CodesDocument4 pagesPerformance Enhancement of MIMO MC CDMA System Employing Cylically Rotated Complete Complementary CodesEditor IJRITCCNo ratings yet

- ?notes On Multiplexers?Document14 pages?notes On Multiplexers?Sushma ShivaniNo ratings yet

- Ijecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)Document11 pagesIjecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)IAEME PublicationNo ratings yet

- Performance Analysis of Ofdm Transceiver Using GMSK Modulation TechniqueDocument5 pagesPerformance Analysis of Ofdm Transceiver Using GMSK Modulation TechniqueEditor IJRITCCNo ratings yet

- Multiplexer and DemultiplexerDocument18 pagesMultiplexer and DemultiplexerTara SharmaNo ratings yet

- Random Waveform Using Digital Multiplexer: Working PaperDocument5 pagesRandom Waveform Using Digital Multiplexer: Working PaperBunk WahisbullahNo ratings yet

- Multiplex Er 1Document19 pagesMultiplex Er 1pkrk123456789100% (1)

- 16x16 Multiuser MIMO Testbed Employing Simple AdaptiveDocument5 pages16x16 Multiuser MIMO Testbed Employing Simple AdaptiveNhật LongNo ratings yet

- DLD 7 StudentDocument6 pagesDLD 7 StudentAminul IslamNo ratings yet

- EC31 GuideQuestionsMuxDocument2 pagesEC31 GuideQuestionsMuxGrant Lewis BulaongNo ratings yet

- Quick HelpDocument12 pagesQuick HelpLeo TDNo ratings yet

- Efficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogDocument12 pagesEfficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogAnonymous e4UpOQEPNo ratings yet

- MultiplexerDocument7 pagesMultiplexerRavi Tej AdusumilliNo ratings yet

- Avionics Lecture Handouts (L-16)Document4 pagesAvionics Lecture Handouts (L-16)Gowri ShankarNo ratings yet

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Document10 pagesDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- Expt 4. 16x1 Mux Using 4x1 MuxDocument6 pagesExpt 4. 16x1 Mux Using 4x1 Muxanon_64997028367% (3)

- Implementing Boolean Function Over Multiplexer: ObjectivesDocument3 pagesImplementing Boolean Function Over Multiplexer: ObjectivesALviNo ratings yet

- COMBINATIONAL CIRCUITS Part 1Document28 pagesCOMBINATIONAL CIRCUITS Part 1Roob HoodNo ratings yet

- Lab 09 UpdatedDocument4 pagesLab 09 UpdatedALISHBA AZAMNo ratings yet

- Damson University College of Engineering Computer Engineering DepartmentDocument5 pagesDamson University College of Engineering Computer Engineering DepartmentZedrik MojicaNo ratings yet

- Coa Exp4Document4 pagesCoa Exp4anshkasaudhan71463No ratings yet

- Asghari CsiDocument6 pagesAsghari CsiMarwan AhmedNo ratings yet

- DE Viva QuestionDocument5 pagesDE Viva QuestionDevu NarayanaNo ratings yet

- COMSOL 5.0 RF TutorialsDocument402 pagesCOMSOL 5.0 RF TutorialsMuhammad Ahtisham Asif100% (2)

- MIMO Technologies in 3GPP LTE and LTE-AdvancedDocument11 pagesMIMO Technologies in 3GPP LTE and LTE-AdvancedPreyas HathiNo ratings yet

- Energy-Aware Utility Regions: Multiple Access Pareto BoundaryDocument11 pagesEnergy-Aware Utility Regions: Multiple Access Pareto BoundaryjayaNo ratings yet

- DESIGN AND SIMULATION OF 2-TO-4 DECODER USING 32nm, 45nm AND 65nm CMOS TECHNOLOGYDocument4 pagesDESIGN AND SIMULATION OF 2-TO-4 DECODER USING 32nm, 45nm AND 65nm CMOS TECHNOLOGYijsret0% (1)

- VTC PaperDocument6 pagesVTC PaperOPTICALMIMOOFDMNo ratings yet

- Coa Unit-2Document25 pagesCoa Unit-2PARTEEK RANANo ratings yet

- Mobile Coverage Problem Analysis by Using NS2Document4 pagesMobile Coverage Problem Analysis by Using NS2International Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Comparative Study of Approximate MultipliersDocument24 pagesComparative Study of Approximate MultipliersSUDHEER SNo ratings yet

- Logarithmic Multiplier: An Analytical ReviewDocument3 pagesLogarithmic Multiplier: An Analytical ReviewInnovative Research PublicationsNo ratings yet

- Simulation of Convolutional EncoderDocument5 pagesSimulation of Convolutional EncoderInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Experiment 5 MUX DEMUXDocument4 pagesExperiment 5 MUX DEMUXMD Sadique AnsariNo ratings yet

- Weighted Least Squares Kinetic Upwind Method Using Eigen Vector BasisDocument55 pagesWeighted Least Squares Kinetic Upwind Method Using Eigen Vector BasiskonarkaroraNo ratings yet

- Using Artificial Neural Networks for Analog Integrated Circuit Design AutomationFrom EverandUsing Artificial Neural Networks for Analog Integrated Circuit Design AutomationNo ratings yet

- Software Radio: Sampling Rate Selection, Design and SynchronizationFrom EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationNo ratings yet

- Importance of Similarity Measures in Effective Web Information RetrievalDocument5 pagesImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCNo ratings yet

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCNo ratings yet

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCNo ratings yet

- A Study of Focused Web Crawling TechniquesDocument4 pagesA Study of Focused Web Crawling TechniquesEditor IJRITCCNo ratings yet

- Prediction of Crop Yield Using LS-SVMDocument3 pagesPrediction of Crop Yield Using LS-SVMEditor IJRITCCNo ratings yet

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocument5 pagesDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCNo ratings yet

- 44 1530697679 - 04-07-2018 PDFDocument3 pages44 1530697679 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocument3 pagesPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaNo ratings yet

- 45 1530697786 - 04-07-2018 PDFDocument5 pages45 1530697786 - 04-07-2018 PDFrahul sharmaNo ratings yet

- Itimer: Count On Your TimeDocument4 pagesItimer: Count On Your Timerahul sharmaNo ratings yet

- 41 1530347319 - 30-06-2018 PDFDocument9 pages41 1530347319 - 30-06-2018 PDFrahul sharmaNo ratings yet

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocument5 pagesHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaNo ratings yet

- Paper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineDocument4 pagesPaper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineEditor IJRITCCNo ratings yet

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocument3 pagesSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaNo ratings yet

- 49 1530872658 - 06-07-2018 PDFDocument6 pages49 1530872658 - 06-07-2018 PDFrahul sharmaNo ratings yet