Professional Documents

Culture Documents

Using Verilog-A To Simplify A SPICE Netlist: Application Note

Using Verilog-A To Simplify A SPICE Netlist: Application Note

Uploaded by

Prince AbhishekCopyright:

Available Formats

You might also like

- Arduino Project Burglar Zone Input TesterDocument4 pagesArduino Project Burglar Zone Input TesterCezary Jan JaronczykNo ratings yet

- 1 004 - Verilog ADocument2 pages1 004 - Verilog AShameem ShaikNo ratings yet

- Tut - Digital IntegratedDocument32 pagesTut - Digital IntegratedqawaNo ratings yet

- AMS Paper ModelingDocument14 pagesAMS Paper ModelingSubham DattaNo ratings yet

- RI R2 R3: VolitDocument5 pagesRI R2 R3: VolitAldijana ZildžićNo ratings yet

- Ecad Lab Manual PvpsitDocument53 pagesEcad Lab Manual PvpsitpriyankaveeramosuNo ratings yet

- Thotruongvu 1987Document12 pagesThotruongvu 1987Tân GiangNo ratings yet

- VHDL & Optical Fiber Lab: L Ab ManualDocument29 pagesVHDL & Optical Fiber Lab: L Ab ManualR arnaldNo ratings yet

- Subject-Aec Lab: Experiment-4Document12 pagesSubject-Aec Lab: Experiment-4PritamNo ratings yet

- Exp4 RTL Inv Fanout Nor NandDocument9 pagesExp4 RTL Inv Fanout Nor NandJohn wickNo ratings yet

- Computer Simulation of The Monostable MultivibratoDocument4 pagesComputer Simulation of The Monostable Multivibratoakarthi2223No ratings yet

- Exp5 TTL InvDocument7 pagesExp5 TTL InvJohn wickNo ratings yet

- Sl. No. Experiment No 1a 3: Analog and Digital Electronics Laboratory (17CSL37)Document58 pagesSl. No. Experiment No 1a 3: Analog and Digital Electronics Laboratory (17CSL37)baba212No ratings yet

- Islamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesDocument14 pagesIslamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesMUHAMMAD JAWAD CHOWDHURY, 180041228No ratings yet

- Gate Driver For N-Channel Mosfet: Experiment 6Document34 pagesGate Driver For N-Channel Mosfet: Experiment 6Noona MigleiNo ratings yet

- DCS-2 Practical File Part-1Document26 pagesDCS-2 Practical File Part-1ykr007No ratings yet

- Ee 337 Lab8Document10 pagesEe 337 Lab8Kowshik BevaraNo ratings yet

- Exp 07 Analog Discovery or M2kDocument19 pagesExp 07 Analog Discovery or M2kRanit HalderNo ratings yet

- NE555 With Arduino Uno R3Document5 pagesNE555 With Arduino Uno R3Wilson Jesus Rojas BayonaNo ratings yet

- Exp6 TTL Nand PDFDocument4 pagesExp6 TTL Nand PDFJohn wickNo ratings yet

- Switch Level ModelingDocument14 pagesSwitch Level Modelingvenkatesh kumarNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- Midterm Exam Name: ID NumberDocument18 pagesMidterm Exam Name: ID NumberpskumarvlsipdNo ratings yet

- Cadence - Virtuoso: Amity UniversityDocument27 pagesCadence - Virtuoso: Amity UniversityAkhil Aggarwal100% (1)

- ALLAH The Most Merciful, The Most Beneficent"Document89 pagesALLAH The Most Merciful, The Most Beneficent"api-19788618No ratings yet

- Fun Projects 02 ChapterDocument3 pagesFun Projects 02 ChaptertihomihoNo ratings yet

- Introduction To Logic Design Lab: And, Or, Not Nand and Nor GatesDocument5 pagesIntroduction To Logic Design Lab: And, Or, Not Nand and Nor GatesErnest Omorose OsemwegieNo ratings yet

- Laboratory Assignments On Experiment 4: LVDT Phase Sensitive Demodulation Using Analog MultiplexerDocument7 pagesLaboratory Assignments On Experiment 4: LVDT Phase Sensitive Demodulation Using Analog MultiplexerSanjana VermaNo ratings yet

- Analog Electronics Lab ManualDocument9 pagesAnalog Electronics Lab ManualRohan KatkamNo ratings yet

- (QUICK START GUIDE) Make An Arduino Capacitance MeterDocument8 pages(QUICK START GUIDE) Make An Arduino Capacitance MeterOussama LabsailiNo ratings yet

- De Lab PDFDocument36 pagesDe Lab PDFNaveen Yallapu100% (1)

- Lecture 2 - Verilog HDL סונ ןמור) Web siteDocument92 pagesLecture 2 - Verilog HDL סונ ןמור) Web siteMack MastNo ratings yet

- Multiple Choices Huawei HCIADocument16 pagesMultiple Choices Huawei HCIAAugusto LimeraNo ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- Lab2 - Combinational Logic CircuitsDocument2 pagesLab2 - Combinational Logic CircuitsFarishat Nusabbee An NafsNo ratings yet

- ASKDocument16 pagesASKAditya AggarwalNo ratings yet

- NGSPICE-Usage and Examples: Debapratim Ghosh Mohamed JabirDocument20 pagesNGSPICE-Usage and Examples: Debapratim Ghosh Mohamed JabirHARSH GARGNo ratings yet

- ET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)Document19 pagesET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)kaesarsabahNo ratings yet

- Lab Manual FOR Computer Organization LabDocument13 pagesLab Manual FOR Computer Organization Labhifzan786No ratings yet

- Microcontroller Basics: Starting With ArduinoDocument26 pagesMicrocontroller Basics: Starting With ArduinoNuradinNo ratings yet

- NGspice BasicsDocument17 pagesNGspice Basicsvishal kumarNo ratings yet

- Module5 Arduino IoDocument18 pagesModule5 Arduino IoAnonymous Ral0yUmd8aNo ratings yet

- Lab Set Ii - ReportDocument7 pagesLab Set Ii - ReportEZRA MOHAMMEDNo ratings yet

- Verilog Basic ExperimentsDocument62 pagesVerilog Basic ExperimentsGaurav Soni0% (1)

- Arduino UNO Con NRF24L01PDocument6 pagesArduino UNO Con NRF24L01PspidyheroNo ratings yet

- EEE2211 Lab ManualDocument30 pagesEEE2211 Lab ManualMuhammed AslamNo ratings yet

- By Marl Us: Lighting The Right To TheDocument7 pagesBy Marl Us: Lighting The Right To TheGiancarloRichardRivadeneyraMiranda100% (1)

- Lab 9Document8 pagesLab 9Fakhar AbbasNo ratings yet

- Design An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KDocument21 pagesDesign An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KMangaiyarkarasi VengatachalamNo ratings yet

- Logic Gate Circuits (Various Logic Families)Document10 pagesLogic Gate Circuits (Various Logic Families)mmaherNo ratings yet

- Logic GatesDocument21 pagesLogic GatesAditya ParmarNo ratings yet

- EX. NO.:01 Date: Modelling of Solar PV Cell: 1 Pw5261 - Renewable LabDocument47 pagesEX. NO.:01 Date: Modelling of Solar PV Cell: 1 Pw5261 - Renewable Labmohana sundaramNo ratings yet

- Verilog UBCDocument29 pagesVerilog UBCsalNo ratings yet

- Mbed CH 4 v1Document15 pagesMbed CH 4 v1Brian YehNo ratings yet

- D Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALDocument41 pagesD Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALArrnaav Singh RathoreeNo ratings yet

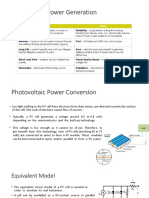

- Photovoltaic Power GenerationDocument61 pagesPhotovoltaic Power GenerationChirag ParasharNo ratings yet

- Digital Electronics 3rd SemDocument39 pagesDigital Electronics 3rd SemPriyanshu ThawaitNo ratings yet

- Laboratory Manual: Microcontroller & Embedded System Lab (EEE-433-F) (Vii Semester)Document26 pagesLaboratory Manual: Microcontroller & Embedded System Lab (EEE-433-F) (Vii Semester)Aanandha SaravananNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

Using Verilog-A To Simplify A SPICE Netlist: Application Note

Using Verilog-A To Simplify A SPICE Netlist: Application Note

Uploaded by

Prince AbhishekOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Using Verilog-A To Simplify A SPICE Netlist: Application Note

Using Verilog-A To Simplify A SPICE Netlist: Application Note

Uploaded by

Prince AbhishekCopyright:

Available Formats

Application Note

Using Verilog-A to

Simplify a SPICE Netlist

The SPICE netlist format is often a complex way of SPICE: Verilog-A

describing a circuit topology.

*RC Circuit // RC Circuit

The Verilog-A language provides designers with R1 in out 10k module RC(in, out);

an alternative method for describing analog circuit C1 out gnd 10u inout in;

blocks. With Verilog-A rich C like syntax and clear inout out;

growth path, Verilog-A is a suitable successor to a electrical in;

method of describing circuit topologies.

electrical out;

The Verilog-A language is supported by both SmartSpice ground gnd;

and Harmony. In SmartSpice, the number of equations

to solve a circuit condition can be simplified by replac- resistor #(.r(10k)) r1 (in, out);

ing certain netlist blocks with Verilog-A equivalent capacitor #(.c(10u)) c1 (out, gnd);

netlists and therefore reducing simulation time. When endmodule

SmartSpice encounters an active device it must solve

a larger number of equations to determine the transis-

tor terminal currents and then use them to solve for the Example 2: A CMOS Inverter

currents in the circuit. By using Verilog-A description a

single calculation step gives the currents for the circuit

thus avoiding the expensive computation. Verilog-A

description allows savings in calculation complexity,

system resources and the simulation time.

The following examples show how to represent a SPICE

netlist as a Verilog-A module.

Example 1: An RC Circuit

Application Note 1-004 Page 1

An Inverter SPICE Verilog-A Equivalent Pulse Generator Description Using

Netlist Netlist Verilog-A Netlist

*CMOS Inverter //CMOS Inverter include discipline.h

MP1 out in vdd vdd module INVERTER(in, out);

+ pch L=1u W=32u input in; module pwlgen (pwlOut);

MN1 out in gnd gnd output out; inout pwlOut;

+ nch L=1u W=16u electrical pwlOut;

electrical in; ground gnd;

V1 in gnd electrical out;

+ pwl( 0, 0, 10e-6, 5 ) ground gnd; vsource #(.pwl ([0,0 10e-6, 5]) vpwlgen() (pwlOut, gnd);

.model nch NMOS PM#(.1(1e-6),.w(32e-6)) endmodule

+ level=49 mp1(out,in,vdd,vdd);

.model pch PMOS NM#(.1(1e-6),.w(16e-6)) Toplevel Testbench

+ level=49 mn1(out,in,gnd,gnd); include discipline.h

.tran 1n 100u timescale 1ns/1ns

endmodule

.save v(in) v(out)

.end

module testbend();

electrical in;

electrical out;

pwlgen pwlgen1 (in);

rc rc1 (in, out);

endmodule

Figure 1. Transient simulation of a pulsed inverter in Harmony of - original SPICE netlist and Verilog-A equivalent netlist show

identical results.

Page 2 Application Note 1-004

You might also like

- Arduino Project Burglar Zone Input TesterDocument4 pagesArduino Project Burglar Zone Input TesterCezary Jan JaronczykNo ratings yet

- 1 004 - Verilog ADocument2 pages1 004 - Verilog AShameem ShaikNo ratings yet

- Tut - Digital IntegratedDocument32 pagesTut - Digital IntegratedqawaNo ratings yet

- AMS Paper ModelingDocument14 pagesAMS Paper ModelingSubham DattaNo ratings yet

- RI R2 R3: VolitDocument5 pagesRI R2 R3: VolitAldijana ZildžićNo ratings yet

- Ecad Lab Manual PvpsitDocument53 pagesEcad Lab Manual PvpsitpriyankaveeramosuNo ratings yet

- Thotruongvu 1987Document12 pagesThotruongvu 1987Tân GiangNo ratings yet

- VHDL & Optical Fiber Lab: L Ab ManualDocument29 pagesVHDL & Optical Fiber Lab: L Ab ManualR arnaldNo ratings yet

- Subject-Aec Lab: Experiment-4Document12 pagesSubject-Aec Lab: Experiment-4PritamNo ratings yet

- Exp4 RTL Inv Fanout Nor NandDocument9 pagesExp4 RTL Inv Fanout Nor NandJohn wickNo ratings yet

- Computer Simulation of The Monostable MultivibratoDocument4 pagesComputer Simulation of The Monostable Multivibratoakarthi2223No ratings yet

- Exp5 TTL InvDocument7 pagesExp5 TTL InvJohn wickNo ratings yet

- Sl. No. Experiment No 1a 3: Analog and Digital Electronics Laboratory (17CSL37)Document58 pagesSl. No. Experiment No 1a 3: Analog and Digital Electronics Laboratory (17CSL37)baba212No ratings yet

- Islamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesDocument14 pagesIslamic University of Technology: EEE 4483 Digital Electronics & Pulse TechniquesMUHAMMAD JAWAD CHOWDHURY, 180041228No ratings yet

- Gate Driver For N-Channel Mosfet: Experiment 6Document34 pagesGate Driver For N-Channel Mosfet: Experiment 6Noona MigleiNo ratings yet

- DCS-2 Practical File Part-1Document26 pagesDCS-2 Practical File Part-1ykr007No ratings yet

- Ee 337 Lab8Document10 pagesEe 337 Lab8Kowshik BevaraNo ratings yet

- Exp 07 Analog Discovery or M2kDocument19 pagesExp 07 Analog Discovery or M2kRanit HalderNo ratings yet

- NE555 With Arduino Uno R3Document5 pagesNE555 With Arduino Uno R3Wilson Jesus Rojas BayonaNo ratings yet

- Exp6 TTL Nand PDFDocument4 pagesExp6 TTL Nand PDFJohn wickNo ratings yet

- Switch Level ModelingDocument14 pagesSwitch Level Modelingvenkatesh kumarNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- Midterm Exam Name: ID NumberDocument18 pagesMidterm Exam Name: ID NumberpskumarvlsipdNo ratings yet

- Cadence - Virtuoso: Amity UniversityDocument27 pagesCadence - Virtuoso: Amity UniversityAkhil Aggarwal100% (1)

- ALLAH The Most Merciful, The Most Beneficent"Document89 pagesALLAH The Most Merciful, The Most Beneficent"api-19788618No ratings yet

- Fun Projects 02 ChapterDocument3 pagesFun Projects 02 ChaptertihomihoNo ratings yet

- Introduction To Logic Design Lab: And, Or, Not Nand and Nor GatesDocument5 pagesIntroduction To Logic Design Lab: And, Or, Not Nand and Nor GatesErnest Omorose OsemwegieNo ratings yet

- Laboratory Assignments On Experiment 4: LVDT Phase Sensitive Demodulation Using Analog MultiplexerDocument7 pagesLaboratory Assignments On Experiment 4: LVDT Phase Sensitive Demodulation Using Analog MultiplexerSanjana VermaNo ratings yet

- Analog Electronics Lab ManualDocument9 pagesAnalog Electronics Lab ManualRohan KatkamNo ratings yet

- (QUICK START GUIDE) Make An Arduino Capacitance MeterDocument8 pages(QUICK START GUIDE) Make An Arduino Capacitance MeterOussama LabsailiNo ratings yet

- De Lab PDFDocument36 pagesDe Lab PDFNaveen Yallapu100% (1)

- Lecture 2 - Verilog HDL סונ ןמור) Web siteDocument92 pagesLecture 2 - Verilog HDL סונ ןמור) Web siteMack MastNo ratings yet

- Multiple Choices Huawei HCIADocument16 pagesMultiple Choices Huawei HCIAAugusto LimeraNo ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- Lab2 - Combinational Logic CircuitsDocument2 pagesLab2 - Combinational Logic CircuitsFarishat Nusabbee An NafsNo ratings yet

- ASKDocument16 pagesASKAditya AggarwalNo ratings yet

- NGSPICE-Usage and Examples: Debapratim Ghosh Mohamed JabirDocument20 pagesNGSPICE-Usage and Examples: Debapratim Ghosh Mohamed JabirHARSH GARGNo ratings yet

- ET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)Document19 pagesET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)kaesarsabahNo ratings yet

- Lab Manual FOR Computer Organization LabDocument13 pagesLab Manual FOR Computer Organization Labhifzan786No ratings yet

- Microcontroller Basics: Starting With ArduinoDocument26 pagesMicrocontroller Basics: Starting With ArduinoNuradinNo ratings yet

- NGspice BasicsDocument17 pagesNGspice Basicsvishal kumarNo ratings yet

- Module5 Arduino IoDocument18 pagesModule5 Arduino IoAnonymous Ral0yUmd8aNo ratings yet

- Lab Set Ii - ReportDocument7 pagesLab Set Ii - ReportEZRA MOHAMMEDNo ratings yet

- Verilog Basic ExperimentsDocument62 pagesVerilog Basic ExperimentsGaurav Soni0% (1)

- Arduino UNO Con NRF24L01PDocument6 pagesArduino UNO Con NRF24L01PspidyheroNo ratings yet

- EEE2211 Lab ManualDocument30 pagesEEE2211 Lab ManualMuhammed AslamNo ratings yet

- By Marl Us: Lighting The Right To TheDocument7 pagesBy Marl Us: Lighting The Right To TheGiancarloRichardRivadeneyraMiranda100% (1)

- Lab 9Document8 pagesLab 9Fakhar AbbasNo ratings yet

- Design An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KDocument21 pagesDesign An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KMangaiyarkarasi VengatachalamNo ratings yet

- Logic Gate Circuits (Various Logic Families)Document10 pagesLogic Gate Circuits (Various Logic Families)mmaherNo ratings yet

- Logic GatesDocument21 pagesLogic GatesAditya ParmarNo ratings yet

- EX. NO.:01 Date: Modelling of Solar PV Cell: 1 Pw5261 - Renewable LabDocument47 pagesEX. NO.:01 Date: Modelling of Solar PV Cell: 1 Pw5261 - Renewable Labmohana sundaramNo ratings yet

- Verilog UBCDocument29 pagesVerilog UBCsalNo ratings yet

- Mbed CH 4 v1Document15 pagesMbed CH 4 v1Brian YehNo ratings yet

- D Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALDocument41 pagesD Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALArrnaav Singh RathoreeNo ratings yet

- Photovoltaic Power GenerationDocument61 pagesPhotovoltaic Power GenerationChirag ParasharNo ratings yet

- Digital Electronics 3rd SemDocument39 pagesDigital Electronics 3rd SemPriyanshu ThawaitNo ratings yet

- Laboratory Manual: Microcontroller & Embedded System Lab (EEE-433-F) (Vii Semester)Document26 pagesLaboratory Manual: Microcontroller & Embedded System Lab (EEE-433-F) (Vii Semester)Aanandha SaravananNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet