Professional Documents

Culture Documents

1.9 Block Diagram: Philips Semiconductors

1.9 Block Diagram: Philips Semiconductors

Uploaded by

utsabCopyright:

Available Formats

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Axioo CNW (w7425 - 6-71-E51q0-D02a.gp) .UnlockedDocument45 pagesAxioo CNW (w7425 - 6-71-E51q0-D02a.gp) .UnlockedChristian Natanael50% (6)

- LG Cm9950 SCHDocument17 pagesLG Cm9950 SCHmitchel taylor100% (1)

- Schematic Diagram t240Document6 pagesSchematic Diagram t240dany weinfeldNo ratings yet

- CM8530 Diagrama-98138Document14 pagesCM8530 Diagrama-98138Marcos D'AquinoNo ratings yet

- 03 - Circuit DescriptionDocument37 pages03 - Circuit Descriptionkhoi vuNo ratings yet

- 6600 nhl-10 Schematics 2 0Document9 pages6600 nhl-10 Schematics 2 0mas parikesitNo ratings yet

- Matrix EnhancedDocument4 pagesMatrix Enhancedmehdi_mehdiNo ratings yet

- Controls: 1. Outline of Application ControlDocument11 pagesControls: 1. Outline of Application ControlIm ChinithNo ratings yet

- Load ScheduleDocument18 pagesLoad SchedulevijayNo ratings yet

- Service Manual: XR3F-19B160Document9 pagesService Manual: XR3F-19B160Andre VPNo ratings yet

- Active Conditioning Unit (ACU) DS 0-0-6Document3 pagesActive Conditioning Unit (ACU) DS 0-0-6Viswanaath SubramanianNo ratings yet

- U010C-Lost Communication With Turbocharger/Supercharger Control ModuleDocument11 pagesU010C-Lost Communication With Turbocharger/Supercharger Control ModuleAshley GymanNo ratings yet

- Z94RP Rev 1 2Document45 pagesZ94RP Rev 1 2NDCENo ratings yet

- LP Series: Service ManualDocument38 pagesLP Series: Service ManualPedro GuilarteNo ratings yet

- Bus Protection: Selector GuideDocument1 pageBus Protection: Selector Guidebaren_royNo ratings yet

- 5 PUCCH - Design and PerformanceDocument52 pages5 PUCCH - Design and PerformanceSulistiyo Tri PutrantoNo ratings yet

- Zungeru Swithcyard Communication SystemDocument30 pagesZungeru Swithcyard Communication Systemrotimi olalekan fataiNo ratings yet

- 02 - NuMicro Architecture - CMSIS PDFDocument42 pages02 - NuMicro Architecture - CMSIS PDFThienNo ratings yet

- Asus Tuf B450m-Pro Gaming Rev1.03Document117 pagesAsus Tuf B450m-Pro Gaming Rev1.03Antonio Carlos Rocha RochaNo ratings yet

- Ipisb Ag r106Document82 pagesIpisb Ag r106Валера ЖмышенкоNo ratings yet

- ALC PDH RADIO Technical Training Siae MiDocument141 pagesALC PDH RADIO Technical Training Siae MiRina AdilahNo ratings yet

- XT172x MAIN SchematicsDocument23 pagesXT172x MAIN SchematicswalterNo ratings yet

- LPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data SheetDocument1 pageLPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data SheetvikkasNo ratings yet

- ASM4106C ApulsIntergratedCircuitsDocument7 pagesASM4106C ApulsIntergratedCircuitsantoni kryzaNo ratings yet

- Title Size D Data Sheet of 99 Sep 14,2016Document23 pagesTitle Size D Data Sheet of 99 Sep 14,2016Miguel AbpNo ratings yet

- Fujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicDocument37 pagesFujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicAsep IndraNo ratings yet

- Block DiagramDocument1 pageBlock DiagramQuang Linh LêNo ratings yet

- Brochure - SEPCOS-PRO - S6 - SG817785BEN - D00-09.10Document8 pagesBrochure - SEPCOS-PRO - S6 - SG817785BEN - D00-09.10Julio MonteiroNo ratings yet

- JVC KD r430 PDFDocument13 pagesJVC KD r430 PDFAleksNo ratings yet

- 8 Block DiagramsDocument2 pages8 Block DiagramsrodrigoapazamoralesNo ratings yet

- Usb11 T11aDocument11 pagesUsb11 T11aMateus CorrêaNo ratings yet

- A/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardDocument1 pageA/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardcahpmasterNo ratings yet

- Calcutta 10-ct10 MP Ti 6050a2357502-A01-Er-Toshiba c600-pdf.6011Document56 pagesCalcutta 10-ct10 MP Ti 6050a2357502-A01-Er-Toshiba c600-pdf.6011oppo cloud007No ratings yet

- Datasheet 1 PDFDocument260 pagesDatasheet 1 PDFMasterDragon96No ratings yet

- CM4450 Diagrama-3395Document13 pagesCM4450 Diagrama-3395Decimeel PapuchoNo ratings yet

- Clevo W940TUDocument36 pagesClevo W940TUaplenoNo ratings yet

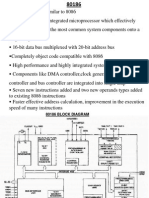

- Hardware Architecture of 8086 and 8088 MicroprocessorsDocument9 pagesHardware Architecture of 8086 and 8088 MicroprocessorsGizmoSX100% (1)

- Ome201102 Huawei Bts3012 Hardware Structure IssueDocument89 pagesOme201102 Huawei Bts3012 Hardware Structure IssueThehidden TruthhNo ratings yet

- DST Tmpm370fydfg-Tde en 21751Document498 pagesDST Tmpm370fydfg-Tde en 21751trân văn tuấnNo ratings yet

- CMOS 8-Bit Single Chip Microcomputer: CXP83408/83412/83416 CXP83409/83413/83417Document24 pagesCMOS 8-Bit Single Chip Microcomputer: CXP83408/83412/83416 CXP83409/83413/83417HerwinTorresNo ratings yet

- 2003 Chrysler Voyager LX 3.3L, V6, Flex, VIN 3, 12V, OHV, USACanada 2Document1 page2003 Chrysler Voyager LX 3.3L, V6, Flex, VIN 3, 12V, OHV, USACanada 2Misa GamezNo ratings yet

- Vibration Motor Sensor Meme TypeDocument42 pagesVibration Motor Sensor Meme TypeBala KrishnanNo ratings yet

- Pape 15Document16 pagesPape 15Aayush PatidarNo ratings yet

- ATA5743Document43 pagesATA5743Jorge Martinez PerezNo ratings yet

- General Description: 16/32-Bit ARM Microcontroller With 10-Bit ADC and External Memory InterfaceDocument40 pagesGeneral Description: 16/32-Bit ARM Microcontroller With 10-Bit ADC and External Memory InterfaceAlexander PrivaloffNo ratings yet

- CXP82316 - I.C.Document20 pagesCXP82316 - I.C.Andre BaezNo ratings yet

- KNX Twisted Pair Tranceiver FZE1066 A6V11933792 - enDocument12 pagesKNX Twisted Pair Tranceiver FZE1066 A6V11933792 - enРоман НовакNo ratings yet

- ALC PDH RADIO Technical Training Siae MiDocument141 pagesALC PDH RADIO Technical Training Siae MiKennedy CostaNo ratings yet

- CXP740096 Sony CorporationDocument31 pagesCXP740096 Sony CorporationGlenn Ian BislumbreNo ratings yet

- Foxconn G43M01 PDFDocument41 pagesFoxconn G43M01 PDFEduinMaracuchoFernandezChaparroNo ratings yet

- Datasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETDocument12 pagesDatasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETdouglasNo ratings yet

- Pos-Pig43bc r100 (Diagramas - Com.br)Document65 pagesPos-Pig43bc r100 (Diagramas - Com.br)Willian CarvalhoNo ratings yet

- TUSB1210 Stand-Alone USB Transceiver Chip Silicon: 1 Device OverviewDocument66 pagesTUSB1210 Stand-Alone USB Transceiver Chip Silicon: 1 Device OverviewCriz MauricioNo ratings yet

- MSP430C11x1, MSP430F11x1A Mixed Signal Microcontroller: DescriptionDocument59 pagesMSP430C11x1, MSP430F11x1A Mixed Signal Microcontroller: Descriptionflo72afNo ratings yet

- MSI MS16811 ScematicDocument51 pagesMSI MS16811 ScematicRosa María AmoneNo ratings yet

- Ad 9254Document40 pagesAd 9254Dileep Kumar AravaNo ratings yet

- P0733 2016 Challenger HellcatDocument3 pagesP0733 2016 Challenger HellcatQuoc LuonglocNo ratings yet

- MPP14-01 2Document63 pagesMPP14-01 2SAMO SAMARANo ratings yet

- Acer Aspire 3300s Service GuideDocument115 pagesAcer Aspire 3300s Service GuideKiran VeesamNo ratings yet

- Manual p5sd2-Vm v3 - UDocument88 pagesManual p5sd2-Vm v3 - UromuloifrjNo ratings yet

- Industrial Automation - Prodotti & Configurazioni: Sistema Base Ht700-1Document2 pagesIndustrial Automation - Prodotti & Configurazioni: Sistema Base Ht700-1marcelloNo ratings yet

- Valleylab Force FX-8C ESU - Schematics PDFDocument45 pagesValleylab Force FX-8C ESU - Schematics PDFZzyxa ZzyxaNo ratings yet

- Chameleon ChipDocument27 pagesChameleon ChipJanu GeethakumariNo ratings yet

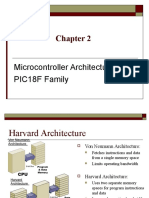

- Chapter 2Document41 pagesChapter 2Eliezer Silverio Acosta100% (1)

- Lecture 1-3 Introduction To Verilog HDLDocument50 pagesLecture 1-3 Introduction To Verilog HDLjjeongdongieeNo ratings yet

- Com 112Document9 pagesCom 112Bedlam HeightsNo ratings yet

- Cost-Effective Flash For Client Computing: Micron 1300 Sata TLC SSDDocument2 pagesCost-Effective Flash For Client Computing: Micron 1300 Sata TLC SSDkumar.arasu8717No ratings yet

- DLD Project Presentation Light DetectorDocument10 pagesDLD Project Presentation Light DetectorMd Mamun HossainNo ratings yet

- Embedded Sample PaperDocument11 pagesEmbedded Sample PaperShashi KanthNo ratings yet

- Chapter 1Document195 pagesChapter 1Naveen NagalingamNo ratings yet

- On Approximate Computing TechniquesDocument58 pagesOn Approximate Computing TechniquesAvishek Sinha RoyNo ratings yet

- I. Matching Type. Write Letters Only. (10pts) : Adamson University Computer Literacy 2 Prelim ExamDocument2 pagesI. Matching Type. Write Letters Only. (10pts) : Adamson University Computer Literacy 2 Prelim ExamFerrolinoLouieNo ratings yet

- 3.1 Product Sales With Missing ValuesDocument54 pages3.1 Product Sales With Missing Valuesbhanu prakashNo ratings yet

- Emergencias-2005 17 5 S79-82Document17 pagesEmergencias-2005 17 5 S79-82fdmbarinasNo ratings yet

- Edc PPTDocument9 pagesEdc PPTParth KelkarNo ratings yet

- Supply and Threshold Voltage Trends: VDD/VTH 2!Document5 pagesSupply and Threshold Voltage Trends: VDD/VTH 2!VCE TANo ratings yet

- Programmer AT89C51Document8 pagesProgrammer AT89C51Pham TrienNo ratings yet

- Instruction Level Parallelism: 1. Scoreboard and Tomasulo AlgorithmsDocument72 pagesInstruction Level Parallelism: 1. Scoreboard and Tomasulo AlgorithmsSAMNo ratings yet

- PIC Microcontrollers For Beginners PIC16F84ADocument186 pagesPIC Microcontrollers For Beginners PIC16F84Aga6ba5No ratings yet

- End-SemEC101 22Document4 pagesEnd-SemEC101 22PLAY LYRICSNo ratings yet

- LiteOn 96fd25 s1tb PLG DatasheetDocument22 pagesLiteOn 96fd25 s1tb PLG Datasheetdigger257No ratings yet

- Microcontroller Based Phase Meter: L. Shrimanth Sudheer, S.S. Patil, R. Laxmikant, Nagabhushana Katte and P. BhaskarDocument3 pagesMicrocontroller Based Phase Meter: L. Shrimanth Sudheer, S.S. Patil, R. Laxmikant, Nagabhushana Katte and P. BhaskarErmin DzankovicNo ratings yet

- DDR3 2666 Qualified Vendors List (QVL) : G.SkillDocument3 pagesDDR3 2666 Qualified Vendors List (QVL) : G.SkillLeyteris NtanosNo ratings yet

- Pal 2021 IOP Conf. Ser. Mater. Sci. Eng. 1187 012008Document11 pagesPal 2021 IOP Conf. Ser. Mater. Sci. Eng. 1187 012008seshu bradyNo ratings yet

- Routerboard 250Gs: - Smart Switch - Small and Compact - Plastic Case - Five Gigabit Ports - Smarter Than SmartDocument1 pageRouterboard 250Gs: - Smart Switch - Small and Compact - Plastic Case - Five Gigabit Ports - Smarter Than SmartNaz LunNo ratings yet

- 8086 Third Term TopicsDocument46 pages8086 Third Term TopicsgandharvsikriNo ratings yet

- Optical Disk Memory Storage DevicesDocument74 pagesOptical Disk Memory Storage DevicesM.WASEEM YOUSAF100% (2)

- A6VMX Series Manual Multi V1.0Document44 pagesA6VMX Series Manual Multi V1.0Charles PhillipsNo ratings yet

1.9 Block Diagram: Philips Semiconductors

1.9 Block Diagram: Philips Semiconductors

Uploaded by

utsabOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1.9 Block Diagram: Philips Semiconductors

1.9 Block Diagram: Philips Semiconductors

Uploaded by

utsabCopyright:

Available Formats

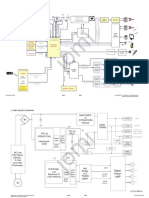

Philips Semiconductors UM10139

Volume 1 Chapter 1: Introductory information

1.9 Block diagram

TMS(1) TDI(1) XTAL2

TRST(1) TCK(1) TDO(1) XTAL1 RST

LPC2141/42/44/46/48

EMULATION TRACE

TEST/DEBUG PLL0

INTERFACE

MODULE

P0[31:28] and system SYSTEM

P0[25:0] FAST GENERAL clock FUNCTIONS

PURPOSE I/O

ARM7TDMI-S

P1[31:16]

PLL1

AHB BRIDGE

VECTORED

USB

INTERRUPT

ARM7 local bus clock

CONTROLLER

AMBA AHB

(Advanced High-performance Bus)

INTERNAL INTERNAL

SRAM FLASH

CONTROLLER CONTROLLER

8 kB RAM AHB

8/16/32 kB 32/64/128/256/512 kB AHB TO VPB VPB SHARED WITH DECODER

SRAM FLASH BRIDGE DIVIDER USB DMA(3)

VPB (VLSI D+

peripheral bus) D

USB 2.0 FULL-SPEED

EXTERNAL

EINT3 to EINT0 DEVICE CONTROLLER UP_LED

INTERRUPTS

WITH DMA(3) CONNECT

VBUS

4 CAP0 SCL0, SCL1

4 CAP1 CAPTURE/COMPARE

(W/EXTERNAL CLOCK) I2C-BUS SERIAL

8 MAT0 INTERFACES 0 AND 1

TIMER 0/TIMER 1 SDA0, SDA1

8 MAT1

AD0[7:6] and SCK0, SCK1

AD0[4:1] A/D CONVERTERS SPI AND SSP MOSI0, MOSI1

AD1[7:0](2) 0 AND 1(2) SERIAL INTERFACES MISO0, MISO1

SSEL0, SSEL1

TXD0, TXD1

RXD0, RXD1

AOUT(4) D/A CONVERTER UART0/UART1

DSR1(2),CTS1(2),

RTS1(2), DTR1(2)

DCD1(2),RI1(2)

P0[31:28] and

GENERAL RTXC1

P0[25:0] REAL-TIME CLOCK

PURPOSE I/O RTXC2

P1[31:16] VBAT

WATCHDOG

PWM6 to PWM0 PWM0

TIMER

SYSTEM

CONTROL

002aab560

(1) Pins shared with GPIO.

(2) LPCC2144/6/8 only.

(3) USB DMA controller with 8 kB of RAM accessible as general purpose RAM and/or DMA is available in LPC2146/8 only.

(4) LPC2142/4/6/8 only.

Fig 1. LPC2141/2/4/6/8 block diagram

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

User manual Rev. 01 15 August 2005 7

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Axioo CNW (w7425 - 6-71-E51q0-D02a.gp) .UnlockedDocument45 pagesAxioo CNW (w7425 - 6-71-E51q0-D02a.gp) .UnlockedChristian Natanael50% (6)

- LG Cm9950 SCHDocument17 pagesLG Cm9950 SCHmitchel taylor100% (1)

- Schematic Diagram t240Document6 pagesSchematic Diagram t240dany weinfeldNo ratings yet

- CM8530 Diagrama-98138Document14 pagesCM8530 Diagrama-98138Marcos D'AquinoNo ratings yet

- 03 - Circuit DescriptionDocument37 pages03 - Circuit Descriptionkhoi vuNo ratings yet

- 6600 nhl-10 Schematics 2 0Document9 pages6600 nhl-10 Schematics 2 0mas parikesitNo ratings yet

- Matrix EnhancedDocument4 pagesMatrix Enhancedmehdi_mehdiNo ratings yet

- Controls: 1. Outline of Application ControlDocument11 pagesControls: 1. Outline of Application ControlIm ChinithNo ratings yet

- Load ScheduleDocument18 pagesLoad SchedulevijayNo ratings yet

- Service Manual: XR3F-19B160Document9 pagesService Manual: XR3F-19B160Andre VPNo ratings yet

- Active Conditioning Unit (ACU) DS 0-0-6Document3 pagesActive Conditioning Unit (ACU) DS 0-0-6Viswanaath SubramanianNo ratings yet

- U010C-Lost Communication With Turbocharger/Supercharger Control ModuleDocument11 pagesU010C-Lost Communication With Turbocharger/Supercharger Control ModuleAshley GymanNo ratings yet

- Z94RP Rev 1 2Document45 pagesZ94RP Rev 1 2NDCENo ratings yet

- LP Series: Service ManualDocument38 pagesLP Series: Service ManualPedro GuilarteNo ratings yet

- Bus Protection: Selector GuideDocument1 pageBus Protection: Selector Guidebaren_royNo ratings yet

- 5 PUCCH - Design and PerformanceDocument52 pages5 PUCCH - Design and PerformanceSulistiyo Tri PutrantoNo ratings yet

- Zungeru Swithcyard Communication SystemDocument30 pagesZungeru Swithcyard Communication Systemrotimi olalekan fataiNo ratings yet

- 02 - NuMicro Architecture - CMSIS PDFDocument42 pages02 - NuMicro Architecture - CMSIS PDFThienNo ratings yet

- Asus Tuf B450m-Pro Gaming Rev1.03Document117 pagesAsus Tuf B450m-Pro Gaming Rev1.03Antonio Carlos Rocha RochaNo ratings yet

- Ipisb Ag r106Document82 pagesIpisb Ag r106Валера ЖмышенкоNo ratings yet

- ALC PDH RADIO Technical Training Siae MiDocument141 pagesALC PDH RADIO Technical Training Siae MiRina AdilahNo ratings yet

- XT172x MAIN SchematicsDocument23 pagesXT172x MAIN SchematicswalterNo ratings yet

- LPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data SheetDocument1 pageLPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data SheetvikkasNo ratings yet

- ASM4106C ApulsIntergratedCircuitsDocument7 pagesASM4106C ApulsIntergratedCircuitsantoni kryzaNo ratings yet

- Title Size D Data Sheet of 99 Sep 14,2016Document23 pagesTitle Size D Data Sheet of 99 Sep 14,2016Miguel AbpNo ratings yet

- Fujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicDocument37 pagesFujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicAsep IndraNo ratings yet

- Block DiagramDocument1 pageBlock DiagramQuang Linh LêNo ratings yet

- Brochure - SEPCOS-PRO - S6 - SG817785BEN - D00-09.10Document8 pagesBrochure - SEPCOS-PRO - S6 - SG817785BEN - D00-09.10Julio MonteiroNo ratings yet

- JVC KD r430 PDFDocument13 pagesJVC KD r430 PDFAleksNo ratings yet

- 8 Block DiagramsDocument2 pages8 Block DiagramsrodrigoapazamoralesNo ratings yet

- Usb11 T11aDocument11 pagesUsb11 T11aMateus CorrêaNo ratings yet

- A/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardDocument1 pageA/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardcahpmasterNo ratings yet

- Calcutta 10-ct10 MP Ti 6050a2357502-A01-Er-Toshiba c600-pdf.6011Document56 pagesCalcutta 10-ct10 MP Ti 6050a2357502-A01-Er-Toshiba c600-pdf.6011oppo cloud007No ratings yet

- Datasheet 1 PDFDocument260 pagesDatasheet 1 PDFMasterDragon96No ratings yet

- CM4450 Diagrama-3395Document13 pagesCM4450 Diagrama-3395Decimeel PapuchoNo ratings yet

- Clevo W940TUDocument36 pagesClevo W940TUaplenoNo ratings yet

- Hardware Architecture of 8086 and 8088 MicroprocessorsDocument9 pagesHardware Architecture of 8086 and 8088 MicroprocessorsGizmoSX100% (1)

- Ome201102 Huawei Bts3012 Hardware Structure IssueDocument89 pagesOme201102 Huawei Bts3012 Hardware Structure IssueThehidden TruthhNo ratings yet

- DST Tmpm370fydfg-Tde en 21751Document498 pagesDST Tmpm370fydfg-Tde en 21751trân văn tuấnNo ratings yet

- CMOS 8-Bit Single Chip Microcomputer: CXP83408/83412/83416 CXP83409/83413/83417Document24 pagesCMOS 8-Bit Single Chip Microcomputer: CXP83408/83412/83416 CXP83409/83413/83417HerwinTorresNo ratings yet

- 2003 Chrysler Voyager LX 3.3L, V6, Flex, VIN 3, 12V, OHV, USACanada 2Document1 page2003 Chrysler Voyager LX 3.3L, V6, Flex, VIN 3, 12V, OHV, USACanada 2Misa GamezNo ratings yet

- Vibration Motor Sensor Meme TypeDocument42 pagesVibration Motor Sensor Meme TypeBala KrishnanNo ratings yet

- Pape 15Document16 pagesPape 15Aayush PatidarNo ratings yet

- ATA5743Document43 pagesATA5743Jorge Martinez PerezNo ratings yet

- General Description: 16/32-Bit ARM Microcontroller With 10-Bit ADC and External Memory InterfaceDocument40 pagesGeneral Description: 16/32-Bit ARM Microcontroller With 10-Bit ADC and External Memory InterfaceAlexander PrivaloffNo ratings yet

- CXP82316 - I.C.Document20 pagesCXP82316 - I.C.Andre BaezNo ratings yet

- KNX Twisted Pair Tranceiver FZE1066 A6V11933792 - enDocument12 pagesKNX Twisted Pair Tranceiver FZE1066 A6V11933792 - enРоман НовакNo ratings yet

- ALC PDH RADIO Technical Training Siae MiDocument141 pagesALC PDH RADIO Technical Training Siae MiKennedy CostaNo ratings yet

- CXP740096 Sony CorporationDocument31 pagesCXP740096 Sony CorporationGlenn Ian BislumbreNo ratings yet

- Foxconn G43M01 PDFDocument41 pagesFoxconn G43M01 PDFEduinMaracuchoFernandezChaparroNo ratings yet

- Datasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETDocument12 pagesDatasheet Mosfet Driver ADP3110A Dual Bootstrapped, 12 V MOSFETdouglasNo ratings yet

- Pos-Pig43bc r100 (Diagramas - Com.br)Document65 pagesPos-Pig43bc r100 (Diagramas - Com.br)Willian CarvalhoNo ratings yet

- TUSB1210 Stand-Alone USB Transceiver Chip Silicon: 1 Device OverviewDocument66 pagesTUSB1210 Stand-Alone USB Transceiver Chip Silicon: 1 Device OverviewCriz MauricioNo ratings yet

- MSP430C11x1, MSP430F11x1A Mixed Signal Microcontroller: DescriptionDocument59 pagesMSP430C11x1, MSP430F11x1A Mixed Signal Microcontroller: Descriptionflo72afNo ratings yet

- MSI MS16811 ScematicDocument51 pagesMSI MS16811 ScematicRosa María AmoneNo ratings yet

- Ad 9254Document40 pagesAd 9254Dileep Kumar AravaNo ratings yet

- P0733 2016 Challenger HellcatDocument3 pagesP0733 2016 Challenger HellcatQuoc LuonglocNo ratings yet

- MPP14-01 2Document63 pagesMPP14-01 2SAMO SAMARANo ratings yet

- Acer Aspire 3300s Service GuideDocument115 pagesAcer Aspire 3300s Service GuideKiran VeesamNo ratings yet

- Manual p5sd2-Vm v3 - UDocument88 pagesManual p5sd2-Vm v3 - UromuloifrjNo ratings yet

- Industrial Automation - Prodotti & Configurazioni: Sistema Base Ht700-1Document2 pagesIndustrial Automation - Prodotti & Configurazioni: Sistema Base Ht700-1marcelloNo ratings yet

- Valleylab Force FX-8C ESU - Schematics PDFDocument45 pagesValleylab Force FX-8C ESU - Schematics PDFZzyxa ZzyxaNo ratings yet

- Chameleon ChipDocument27 pagesChameleon ChipJanu GeethakumariNo ratings yet

- Chapter 2Document41 pagesChapter 2Eliezer Silverio Acosta100% (1)

- Lecture 1-3 Introduction To Verilog HDLDocument50 pagesLecture 1-3 Introduction To Verilog HDLjjeongdongieeNo ratings yet

- Com 112Document9 pagesCom 112Bedlam HeightsNo ratings yet

- Cost-Effective Flash For Client Computing: Micron 1300 Sata TLC SSDDocument2 pagesCost-Effective Flash For Client Computing: Micron 1300 Sata TLC SSDkumar.arasu8717No ratings yet

- DLD Project Presentation Light DetectorDocument10 pagesDLD Project Presentation Light DetectorMd Mamun HossainNo ratings yet

- Embedded Sample PaperDocument11 pagesEmbedded Sample PaperShashi KanthNo ratings yet

- Chapter 1Document195 pagesChapter 1Naveen NagalingamNo ratings yet

- On Approximate Computing TechniquesDocument58 pagesOn Approximate Computing TechniquesAvishek Sinha RoyNo ratings yet

- I. Matching Type. Write Letters Only. (10pts) : Adamson University Computer Literacy 2 Prelim ExamDocument2 pagesI. Matching Type. Write Letters Only. (10pts) : Adamson University Computer Literacy 2 Prelim ExamFerrolinoLouieNo ratings yet

- 3.1 Product Sales With Missing ValuesDocument54 pages3.1 Product Sales With Missing Valuesbhanu prakashNo ratings yet

- Emergencias-2005 17 5 S79-82Document17 pagesEmergencias-2005 17 5 S79-82fdmbarinasNo ratings yet

- Edc PPTDocument9 pagesEdc PPTParth KelkarNo ratings yet

- Supply and Threshold Voltage Trends: VDD/VTH 2!Document5 pagesSupply and Threshold Voltage Trends: VDD/VTH 2!VCE TANo ratings yet

- Programmer AT89C51Document8 pagesProgrammer AT89C51Pham TrienNo ratings yet

- Instruction Level Parallelism: 1. Scoreboard and Tomasulo AlgorithmsDocument72 pagesInstruction Level Parallelism: 1. Scoreboard and Tomasulo AlgorithmsSAMNo ratings yet

- PIC Microcontrollers For Beginners PIC16F84ADocument186 pagesPIC Microcontrollers For Beginners PIC16F84Aga6ba5No ratings yet

- End-SemEC101 22Document4 pagesEnd-SemEC101 22PLAY LYRICSNo ratings yet

- LiteOn 96fd25 s1tb PLG DatasheetDocument22 pagesLiteOn 96fd25 s1tb PLG Datasheetdigger257No ratings yet

- Microcontroller Based Phase Meter: L. Shrimanth Sudheer, S.S. Patil, R. Laxmikant, Nagabhushana Katte and P. BhaskarDocument3 pagesMicrocontroller Based Phase Meter: L. Shrimanth Sudheer, S.S. Patil, R. Laxmikant, Nagabhushana Katte and P. BhaskarErmin DzankovicNo ratings yet

- DDR3 2666 Qualified Vendors List (QVL) : G.SkillDocument3 pagesDDR3 2666 Qualified Vendors List (QVL) : G.SkillLeyteris NtanosNo ratings yet

- Pal 2021 IOP Conf. Ser. Mater. Sci. Eng. 1187 012008Document11 pagesPal 2021 IOP Conf. Ser. Mater. Sci. Eng. 1187 012008seshu bradyNo ratings yet

- Routerboard 250Gs: - Smart Switch - Small and Compact - Plastic Case - Five Gigabit Ports - Smarter Than SmartDocument1 pageRouterboard 250Gs: - Smart Switch - Small and Compact - Plastic Case - Five Gigabit Ports - Smarter Than SmartNaz LunNo ratings yet

- 8086 Third Term TopicsDocument46 pages8086 Third Term TopicsgandharvsikriNo ratings yet

- Optical Disk Memory Storage DevicesDocument74 pagesOptical Disk Memory Storage DevicesM.WASEEM YOUSAF100% (2)

- A6VMX Series Manual Multi V1.0Document44 pagesA6VMX Series Manual Multi V1.0Charles PhillipsNo ratings yet