Professional Documents

Culture Documents

C.a.D. Tools For VLSI Report

C.a.D. Tools For VLSI Report

Uploaded by

darshan knOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

C.a.D. Tools For VLSI Report

C.a.D. Tools For VLSI Report

Uploaded by

darshan knCopyright:

Available Formats

RV College of Engineering, Bangalore

R. V. COLLEGE OF ENGINEERING,

BENGALURU-560059

(Autonomous Institution Affiliated to VTU, Belgaum)

TITLE OF THE ASSIGNMENT

ASAP CODE LEVEL IMPLEMENTATION WITH VERILOG FILE GENERATION

NAME OF THE CANDIDATES: DARSHAN K N (1RV15EC402)

GOWTHAM J (1RV15EC407)

YATHISH KUMAR S (1RV15EC435)

Submitted to

SHILPA D R

Assistant Professor

Department of Electronics and Communication Engineering

R V College of Engineering

Department of Electronics and Communication

RV College of Engineering, Bangalore

R.V. COLLEGE OF ENGINEERING, BENGALURU - 560059

(Autonomous Institution Affiliated to VTU, Belgavi)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

CERTIFICATE

Certified that the case Study work titled ASAP CODE LEVEL IMPLEMENTATION WITH

VERILOG FILE GENERATION is carried out by Darshan K N, Gowtham J, Yathish kumar S

who is bonafide student of R.V College of Engineering, Bangalore, in partial fulfillment for the award of

degree of Bachelor of Engineering in Electronics And Communication of the Visveshwariah

Technological University, Belgaum during the year 2016-2017. It is certified that all

corrections/suggestions indicated for the internal Assessment have been incorporated in the report

deposited in the departmental library. The Self Study report has been approved as it satisfies the academic

requirements in respect of Self Study work prescribed by the institution for the said degree.

Marks awarded = (Evaluation1+ Evaluation2) = 20

Signature of Staff In-charge Signature of Head of the Department

Department of Electronics and Communication

2

RV College of Engineering, Bangalore

Contents

1 Introduction

1.1 Scheduling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...4

1.2 Scheduling without Resource Constraints. . . . . . . . . . .4

1.2.1 ASAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.2.2 ALAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Implementation Details

2.1 ASAP Algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

2.2 ASAP C Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.3 Results and Analysis. . . . . . . . . . . . . . . . . . . . . . . . . .. .. . 14

2.3.1 ASAP Scheduled Graph. . . . . . . . . . . . . . . .14

2.3.2 Verilog File . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Department of Electronics and Communication

3

RV College of Engineering, Bangalore

INTRODUCTION

1.1 SCHEDULING

Scheduling is a very important problem in architectural synthesis. Whereas a sequencing

graph prescribes only dependencies among the operations, the scheduling-of a sequencing

graph determines the precise start time of each task. The start times must satisfy the original

dependencies of the sequencing graph, which limit the amount of parallelism of the

operations, because any pair of operations related by a sequence dependency (or by a chain

of dependencies) may not execute concurrently.

Scheduling determines the concurrency of the resulting implementation, and therefore it

affects its performance. By the same token, the maximum number of concurrent operations

of any given type at any step of the schedule is a lower bound on the number of required

hardware resources of that type. Therefore the choice of a schedule affects also the area of

the implementation.

1.2 SCHEDULING WITHOUT RESOURCE CONSTRAINTS

Before considering the algorithms for unconstrained scheduling, we would like to comment on

the relevance of the problem. Unconstrained scheduling is applied when dedicated resources are

used. Practical cases leading to dedicated resources are those when operations differ in their

types or when their cost is marginal when compared to that of steering logic, registers, wiring

and control.

Unconstrained scheduling is also used when resource binding is done prior to scheduling,

and resource conflicts are solved by serializing the operations that share the same resource. In

this case, the area cost of an implementation is defined before and independently from the

scheduling step.

Eventually unconstrained scheduling can be used to derive bounds on latency for

constrained problems. A lower bound on latency can be computed by unconstrained scheduling,

because the minimum latency of a schedule under some resource constraint is obviously at least

as large as the latency computed with unlimited resources.

Department of Electronics and Communication

4

RV College of Engineering, Bangalore

1.2.1 UNCONSTRAINED SCHEDULING: THE ASAP SCHEDULING ALGORITHM

The unconstrained minimum-latency scheduling problem can be solved in polynomial

time by topologically sorting the vertices of the sequencing graph. This approach is called in

jargon as soon as possible (ASAP) scheduling, because the start time for each operation is the

least one allowed by the dependencies. We denote by ts the start times imputed by the ASAP

Algorithm 5.3.1, i.e., by a vector whose entries are {tis ; i = 0, 1, . . . ., n};

1.2.2 LATENCY-CONSTRAINED SCHEDULING: THE ALAP SCHEDULING

ALGORITHM

We consider now the case in which a schedule must satisfy an upper bound on the latency,

denoted by h. This problem may be solved by executing the ASAP scheduling algorithm and

verifying that (t: - ti) 5 h. If a schedule exists that satisfies the latency bound h, it is possible then

to explore the range of values of the start times of the operations that meet the bound. The ASAP

scheduling algorithm yields the minimum values of the start times. A complementary algorithm,

the as late as possible (ALAP) scheduling Algorithm 5.3.2, provides the corresponding

maximum values.

IMPLEMENTATION DETAILS

2.1 ASAP ALOGORITHM

ASAP ( G,(V, El))

{

Schedule LQ by sening I: = 1;

repeat {

Select a vertex vi whore predecessors are all scheduled:

Schedule vi by setting tis = max rf + d,;

J:(vj,e) E

}

until (vn is scheduled) ;

return (ts);

}

Department of Electronics and Communication

5

RV College of Engineering, Bangalore

2.2 ASAP CODE IN C

/*

Description: Below code is the implementation of ASAP Algorithm in this the operations are allotted to their

respective time slots based on their dependency constraints only.

Compare function is used to know the dependency level of operation so that it can be moved to its respective

timeslots.

Graph function is used to plot the graphical representaiton of the operations.

Constraints of the code all the names of the input,output and operation variables must contain same numbers

of characters preferrably 3 to get proper display of graph.

*/

#include<stdio.h>

#include<stdlib.h>

#include<string.h>

#include"iostream"

#include"fstream"

#include<conio.h>

#include<strings.h>

using namespace std;

struct node{

char *operation,*in1,*in2,*out;

int rep=0,i1=0,i2=0,b1=0,b2=0,b3=0;

}timeslots[10][20];

int length[10],d[20];

void graph(int &k)

{

int x=k;

for(int i=0;i<=k;i++)

{

printf("\n-------------------------------------------------------------------------------------------------------------");

printf("\n-------------------------------------------------TimeSlot-%d -------------------------------------------------",i);

printf("\n-------------------------------------------------------------------------------------------------------------\n");

for(int w=0;w<length[i];w++)

{

printf(" %s %s ",timeslots[i][w].in1,timeslots[i][w].in2);

}

printf("\n");

for(int w=0;w<length[i];w++)

{

printf(" %d %d ",timeslots[i][w].b1,timeslots[i][w].b2);

}

printf("\n ");

for(int w=0;w<length[i];w++)

{

Department of Electronics and Communication

6

RV College of Engineering, Bangalore

printf(" \\ / ");

}

printf("\n ");

for(int w=0;w<length[i];w++)

{

printf(" %s ",timeslots[i][w].operation);

}

printf("\n ");

for(int w=0;w<length[i];w++)

{

printf(" | ");

}

printf("\n ");

for(int w=0;w<length[i];w++)

{

printf(" %s ",timeslots[i][w].out);

}

printf("\n ");

for(int w=0;w<length[i];w++)

{

printf(" %d ",timeslots[i][w].b3);

}

printf("\n ");

for(int w=0;w<length[i];w++)

{

printf(" %d%d%d ",timeslots[i][w].i1,timeslots[i][w].i2,timeslots[i][w].rep);

}

}

}

void equal(int &e)

{

int status=0;

for(int x=0;x<e;x++)

{

for(int q=x+1;q<e;q++)

{

if(d[x]==d[q])

{

for(int i=q;i<e;i++)

d[q]=d[q+1];

status=1;

}

}

Department of Electronics and Communication

7

RV College of Engineering, Bangalore

if(status==1)

{ e--;

}

}

void sort(int &e)

{

int temp;

for(int x=0;x<e;x++)

{

for(int q=0;q<e;q++)

{

if(d[x]<=d[q])

{

temp=d[x];

d[x]=d[q];

d[q]=temp;

}

}

}

equal(e);

equal(e);

equal(e);

equal(e);

}

void Delete(int &k,int *d,int &e,int &p)

{

int j=0,m;

m=e;

while(m)

{ /* to shift the operations from the point of match*/

for(int i=d[j];i<p;i++)

{

timeslots[k][i].operation=timeslots[k][i+1].operation;

timeslots[k][i].in1=timeslots[k][i+1].in1;

timeslots[k][i].in2=timeslots[k][i+1].in2;

timeslots[k][i].out=timeslots[k][i+1].out;

timeslots[k][i].b1=timeslots[k][i+1].b1;

timeslots[k][i].b2=timeslots[k][i+1].b2;

timeslots[k][i].b3=timeslots[k][i+1].b3;

timeslots[k][i].rep=timeslots[k][i+1].rep;

timeslots[k][i].i1=timeslots[k][i+1].i1;

timeslots[k][i].i2=timeslots[k][i+1].i2;

Department of Electronics and Communication

8

RV College of Engineering, Bangalore

for(int q=0;q<e;q++)

d[q]=d[q]-1;

timeslots[k][p-1].operation='\0';

timeslots[k][p-1].in1='\0';

timeslots[k][p-1].in2='\0';

timeslots[k][p-1].out='\0';

timeslots[k][p-1].b1=0;

timeslots[k][p-1].b2=0;

timeslots[k][p-1].b3=0;

timeslots[k][p-1].rep=0;

timeslots[k][p-1].i1=0;

timeslots[k][p-1].i2=0;

p--;

m--;

j++;

}

}

void compare(int &k,int &p,int &j)

{

int e=0,o=0;

int set=0;

for(int l=0;l<p;l++)

{

/* to compare and move dependent operations*/

for (int i=0;i<p;i++)

{

for(int c=0;c<j;c++)

{

if(timeslots[k][l].out[c]==timeslots[k][i].in1[c])

{

o=1;

timeslots[k][i].i1=1;

}

else

{

o=0;

break;

}

}

if(o==0)

{

Department of Electronics and Communication

9

RV College of Engineering, Bangalore

for(int c=0;c<3;c++)

{

if(timeslots[k][l].out[c]==timeslots[k][i].in2[c])

{

o=1;

timeslots[k][i].i2=1;

}

else

{

o=0;

break;

}

}

}

if(o==1)

{ /*to move the dependency operations to next timeslot*/

for(int r=0;r<e;r++)

{

if(d[r]==i)

goto skip;

}

timeslots[k][l].rep=1;

timeslots[k+1][e].operation=timeslots[k][i].operation;

timeslots[k+1][e].in1=timeslots[k][i].in1;

timeslots[k+1][e].in2=timeslots[k][i].in2;

timeslots[k+1][e].out=timeslots[k][i].out;

timeslots[k+1][e].rep=timeslots[k][i].rep;

timeslots[k+1][e].i1=timeslots[k][i].i1;

timeslots[k+1][e].i2=timeslots[k][i].i2;

timeslots[k+1][e].b1=timeslots[k][i].b1;

timeslots[k+1][e].b2=timeslots[k][i].b2;

timeslots[k+1][e].b3=timeslots[k][i].b3;

d[e]=i;

e++;

skip:set=1;

}

}

sort(e);

for(int q=0;q<e;q++)

{ /* to clear the dependency operation that has been moved to next time slot from present time slot*/

timeslots[k][d[q]].operation='\0';

timeslots[k][d[q]].in1='\0';

timeslots[k][d[q]].in2='\0';

timeslots[k][d[q]].out='\0';

timeslots[k][d[q]].b1=0;

timeslots[k][d[q]].b2=0;

Department of Electronics and Communication

10

RV College of Engineering, Bangalore

timeslots[k][d[q]].b3=0;

timeslots[k][d[q]].i1=0;

timeslots[k][d[q]].i2=0;

timeslots[k][d[q]].rep=0;

}

Delete(k,d,e,p);

length[k]=p;

if(set==1)

{

p=e;

k+=1;

compare(k,p,j);

}

}

void output(node *timeslot)

{

printf("\n\toutput\n");

for(int i=0;i<17;i++)

{

printf("%s \t %s[%d] \t %s[%d] \t

%s[%d]\n",timeslot[i].operation,timeslot[i].in1,timeslot[i].b1,timeslot[i].in2,timeslot[i].b2,timeslot[i].out,timeslot[i].b3);

}

}

bool ifnil(char * M)

{

if(M[0]=='N')

{

if(M[1]=='i')

if(M[2]=='l')

return true;

}

return false;

}

void write_verilog(int &k)

{ int d,i;

ofstream outputfile;

printf("\n \twriting to .v file......");

outputfile.open("gowtham.v");

outputfile<<"`timescale 1ns / 1ps"<<endl<<"//////////////////////////////////////////////////////////////////////////////////"<<endl;

outputfile<<"// Module Name:CAD Design\n\n"<<endl;

outputfile<<"module trail( ";

for(d=0;d<=k;d++)

{

for(i=0;i<length[d];i++)

{ if(ifnil(timeslots[d][i].in1))

{

continue;

Department of Electronics and Communication

11

RV College of Engineering, Bangalore

}

if(timeslots[d][i].i1==1)

{

outputfile<<"\tinout ";

if(timeslots[d][i].b1!=0)

outputfile<<"["<<timeslots[d][i].b1<<":"<<"0"<<"]";

outputfile<<timeslots[d][i].in1<<",";

}

else

{

outputfile<<"\tinput ";

if(timeslots[d][i].b1!=0)

outputfile<<"["<<timeslots[d][i].b1<<":"<<"0"<<"]";

outputfile<<timeslots[d][i].in1<<",";

}

if(ifnil(timeslots[d][i].in2))

{

continue;

}

if(timeslots[d][i].i2==1)

{

outputfile<<"inout ";

if(timeslots[d][i].b2!=0)

outputfile<<"["<<timeslots[d][i].b2<<":"<<"0"<<"]";

outputfile<<timeslots[d][i].in2<<",";

}

else

{

outputfile<<"input ";

if(timeslots[d][i].b2!=0)

outputfile<<"["<<timeslots[d][i].b2<<":"<<"0"<<"]";

outputfile<<timeslots[d][i].in2<<",";

}

if(timeslots[d][i].rep==0 && d==k-1)

{

outputfile<<"output ";

if(timeslots[d][i].b3!=0)

outputfile<<"["<<timeslots[d][i].b3<<":"<<"0"<<"]";

outputfile<<timeslots[d][i].out<<",\n";

}

else if(d==k)

{

outputfile<<"output ";

if(timeslots[d][i].b3!=0)

outputfile<<"["<<timeslots[d][i].b3<<":"<<"0"<<"]";

outputfile<<timeslots[d][i].out<<"\n";

}

else

outputfile<<"\n ";

Department of Electronics and Communication

12

RV College of Engineering, Bangalore

outputfile<<"\t);// inputs and outputs\n\n";

outputfile<<"always( ";

for(d=0;d<=k;d++)

{

for(i=0;i<length[d];i++)

{ if(ifnil(timeslots[d][i].in1))

{

continue;

}

if(!(timeslots[d][i].i1==1))

outputfile<<timeslots[d][i].in1<<",";

if(ifnil(timeslots[d][i].in2))

{

continue;

}

if(!(timeslots[d][i].i2==1)&&(d==k-1))

outputfile<<timeslots[d][i].in2<<",";

else if (!(timeslots[d][i].i2==1))

outputfile<<timeslots[d][i].in2;

}

outputfile<<");// sensitivity list \n Begin";

for(int d=0;d<=k;d++)

{

for(int i=0;i<length[d];i++)

{

outputfile<<"\n"<<timeslots[d][i].out<<" = ";

if(!(ifnil(timeslots[d][i].in1)))

{

outputfile<<timeslots[d][i].in1;

}

outputfile<<timeslots[d][i].operation;

if(!(ifnil(timeslots[d][i].in2)))

{

outputfile<<timeslots[d][i].in2;

}

Department of Electronics and Communication

13

RV College of Engineering, Bangalore

outputfile<<";";

}

}

outputfile<<"\nend\n";

outputfile<<"\nendmodule\n";

outputfile.close();

}

int main(void)

{

FILE *fp;

ofstream outputfile;

int n;

printf("Enter number of rows to consider for plotting : ");

scanf("%d",&n);

char ch,temp[20][5][5];

int i=0,j=0,k=0,p=0,z=0;

fp=fopen("temp database.csv","r");

p=n;

// initializer timeslot 0

for(int w=0;w<p;w++)

{

ch=fgetc(fp);

if(ch=='\n')

continue;

j=0;

while(ch!=',')

{ // printf("%c",ch);

temp[w][0][j]=ch;

j++;

ch=fgetc(fp);

}

//printf("\t");

temp[w][0][j]='\0';

timeslots[k][w].operation=temp[w][0];

ch=fgetc(fp);

j=0;

while(ch!=',')

{ //printf("%c",ch);

if(ch=='[')

{

ch=fgetc(fp);

timeslots[k][w].b1=ch-'0';

ch=fgetc(fp);

}

else

{

Department of Electronics and Communication

14

RV College of Engineering, Bangalore

temp[w][1][j]=ch;

j++;

}

ch=fgetc(fp);

}

//printf("\t");

temp[w][1][j]='\0';

timeslots[k][w].in1=temp[w][1];

ch=fgetc(fp);

j=0;

while(ch!=',')

{ //printf("%c",ch);

if(ch=='[')

{

ch=fgetc(fp);

timeslots[k][w].b2=ch-'0';

ch=fgetc(fp);

}

else

{

temp[w][2][j]=ch;

j++;

}

ch=fgetc(fp);

}

//printf("\t");

temp[w][2][j]='\0';

timeslots[k][w].in2=temp[w][2];

ch=fgetc(fp);

j=0;

while(ch!='\n')

{ printf("%c",ch);

if(ch=='[')

{

ch=fgetc(fp);

timeslots[k][w].b3=ch-'0';

ch=fgetc(fp);

}

else

{

temp[w][3][j]=ch;

Department of Electronics and Communication

15

RV College of Engineering, Bangalore

j++;

}

ch=fgetc(fp);

}

//printf("\n");

temp[w][3][j]='\0';

timeslots[k][w].out=temp[w][3];

}

output(timeslots[0]);

compare(k,p,j);

output(timeslots[0]);

graph(k);

write_verilog(k);

return 1;

}

2.3 RESULTS AND ANALYSIS

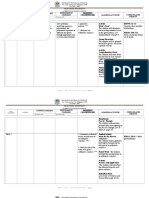

2.3.1 ASAP Scheduled Graph

Department of Electronics and Communication

16

RV College of Engineering, Bangalore

Department of Electronics and Communication

17

RV College of Engineering, Bangalore

Department of Electronics and Communication

18

RV College of Engineering, Bangalore

2.3.2 Verilog File

Department of Electronics and Communication

19

RV College of Engineering, Bangalore

Department of Electronics and Communication

20

You might also like

- Field Study QuestionnaireDocument35 pagesField Study QuestionnaireJohn Zartiga94% (16)

- Influence Lines For Moving Loads On MathcadDocument13 pagesInfluence Lines For Moving Loads On MathcadBarnaby NgNo ratings yet

- Half Wave Rectifier Circuit SimulationDocument33 pagesHalf Wave Rectifier Circuit SimulationHomoudAlsohaibi100% (2)

- VLSI Interview QuestionsDocument7 pagesVLSI Interview QuestionsVlsi GuruNo ratings yet

- Major Issues Affecting Poor and Marginalized Communities (Autosaved)Document37 pagesMajor Issues Affecting Poor and Marginalized Communities (Autosaved)Mycz Doña38% (13)

- University of Tokyo Fact SheetDocument8 pagesUniversity of Tokyo Fact Sheetgoogley71No ratings yet

- Arabic From The Beginning Part One PDFDocument3 pagesArabic From The Beginning Part One PDFRaviNo ratings yet

- FinalDocument19 pagesFinalkluNo ratings yet

- Basic 10 C ProgramsDocument22 pagesBasic 10 C Programsm2005anojrNo ratings yet

- DAA Lab Manual Simplified VersionDocument31 pagesDAA Lab Manual Simplified Versiondeepzd517No ratings yet

- Data Structure - Algorithms - 01Document33 pagesData Structure - Algorithms - 01Oishee GhoshNo ratings yet

- CaculatorDocument20 pagesCaculatorLUCIFER DEVILNo ratings yet

- Ajeesh Moosakutty (4) Sabith P (33) SRUTHI.K.R (45) Shafeek Ma NideeshDocument44 pagesAjeesh Moosakutty (4) Sabith P (33) SRUTHI.K.R (45) Shafeek Ma NideeshJohn112No ratings yet

- Quasistatic Voltage Scaling For Energy Minimization With Time CoDocument6 pagesQuasistatic Voltage Scaling For Energy Minimization With Time CoNguyen Van ToanNo ratings yet

- Optimal Interconnects: Modelling and Synthesis: Vineet Sahula C.P. Ravikumar D. NagchoudhuryDocument8 pagesOptimal Interconnects: Modelling and Synthesis: Vineet Sahula C.P. Ravikumar D. NagchoudhuryVSNo ratings yet

- Analysis of Standard Beam Conditions by C Programming: Jitendra M. Joshi, Aakash S. PawarDocument3 pagesAnalysis of Standard Beam Conditions by C Programming: Jitendra M. Joshi, Aakash S. PawarSyed MustafaNo ratings yet

- Index: Ex No Title No Date SignDocument7 pagesIndex: Ex No Title No Date SignShivangi MajithiyaNo ratings yet

- Karthik Aat PSQDocument13 pagesKarthik Aat PSQAmanGartaanNo ratings yet

- Manual: Computer Aided Analysis and Simulation LAB (CASA) - 15ME65PDocument72 pagesManual: Computer Aided Analysis and Simulation LAB (CASA) - 15ME65PVinayak VinayNo ratings yet

- PPS CBPDocument13 pagesPPS CBPsharanyadinakaran2006No ratings yet

- Lab#12 2019-CPE-27 M.USAMA SAGHARDocument12 pagesLab#12 2019-CPE-27 M.USAMA SAGHARUsama SagharNo ratings yet

- VLSI Design Software ProcedureDocument10 pagesVLSI Design Software ProcedureTilak RajputNo ratings yet

- 17IT8029Document7 pages17IT8029AlexNo ratings yet

- JETC1204-39 - AhsanJETC2015Document25 pagesJETC1204-39 - AhsanJETC2015Muhammad AhsanNo ratings yet

- Satellite Communication Lab ManualDocument52 pagesSatellite Communication Lab ManualSaad Khaliq100% (1)

- Microwave Lab 10Document5 pagesMicrowave Lab 10maxNo ratings yet

- AI Technology For NoC Performance EvaluationDocument5 pagesAI Technology For NoC Performance EvaluationSoumya Shatakshi PandaNo ratings yet

- Electronics Is The Branch of Science and Technology Which Makes Use of The Controlled Motion of Electrons Through Different Media and VacuumDocument47 pagesElectronics Is The Branch of Science and Technology Which Makes Use of The Controlled Motion of Electrons Through Different Media and VacuumNikhil BansalNo ratings yet

- Bengal College of Engineering and Technology, DurgapurDocument13 pagesBengal College of Engineering and Technology, DurgapurAnimesh PrasadNo ratings yet

- DataFlow Modeling in VerilogDocument22 pagesDataFlow Modeling in VerilogWaqas Ahmed0% (1)

- Information Retrieval Practical: A Project ReportDocument16 pagesInformation Retrieval Practical: A Project Reportsahadev jagdish dhargalkarNo ratings yet

- Das PaperDocument13 pagesDas PaperrohanNo ratings yet

- 58 DS ProjectDocument22 pages58 DS Projectrr5221922No ratings yet

- OS Lab ManualDocument33 pagesOS Lab ManualAmruthŇNo ratings yet

- Vlsi Lab ManualDocument81 pagesVlsi Lab ManualKrishnaNo ratings yet

- 17csl47 2018 19 LPD PDFDocument3 pages17csl47 2018 19 LPD PDFvishwa darshiniNo ratings yet

- Muaz Technical Paper FinalDocument16 pagesMuaz Technical Paper FinalAHMAD ASRI ABD SAMATNo ratings yet

- CN Report NewDocument5 pagesCN Report Newnavyanaik826No ratings yet

- Implementing Linear Algebraalgorithms For Dense MatricesDocument22 pagesImplementing Linear Algebraalgorithms For Dense MatricesFilipe AmaroNo ratings yet

- Information Retrieval PracticalDocument16 pagesInformation Retrieval Practicalsahadev jagdish dhargalkar100% (1)

- 1999 (125) - Heterogeneous Task Scheduling AlgorithmsDocument12 pages1999 (125) - Heterogeneous Task Scheduling AlgorithmsfsmondiolatiroNo ratings yet

- CC Lab Manual - 16feb2015Document34 pagesCC Lab Manual - 16feb2015rajanNo ratings yet

- CD_Unit_5Document19 pagesCD_Unit_5baburishabh368No ratings yet

- Tutorial By: A On The LQG/LTR MethodDocument8 pagesTutorial By: A On The LQG/LTR MethodLuis TorresNo ratings yet

- Sattvik 1TJ18CS009 WTA Practical AssessmentDocument33 pagesSattvik 1TJ18CS009 WTA Practical AssessmentSattvik AnnadathaNo ratings yet

- Line Balancing Analysis by Used Rank Positional Weight (RPW) (Case Study: Part Body S11038Z Process)Document7 pagesLine Balancing Analysis by Used Rank Positional Weight (RPW) (Case Study: Part Body S11038Z Process)sitam_nitj4202No ratings yet

- Os Lab ManualDocument51 pagesOs Lab Manualresearch n technologyNo ratings yet

- Practicals - 1-11 - Sudarshan - 91900103137Document23 pagesPracticals - 1-11 - Sudarshan - 91900103137Sudarshan PoudelNo ratings yet

- Control Assign 1 2023Document4 pagesControl Assign 1 2023upeksha erandiNo ratings yet

- 13.A New Task Scheduling Algorithm Based On Value and Time For Cloud Platform PDFDocument8 pages13.A New Task Scheduling Algorithm Based On Value and Time For Cloud Platform PDFBOOMIGA SSNo ratings yet

- Que: Explain With Block Diagram The Steps Involved in Post Layout Synthesis? Ans: SynthesisDocument4 pagesQue: Explain With Block Diagram The Steps Involved in Post Layout Synthesis? Ans: Synthesishumtum_shri5736No ratings yet

- Assignment 3Document29 pagesAssignment 3sayanvk290No ratings yet

- COMPUTER GRAPHICS LABORATORY AY 2022-2023 8 PracticalDocument46 pagesCOMPUTER GRAPHICS LABORATORY AY 2022-2023 8 Practicalubaida saoodNo ratings yet

- Ai File HMDocument19 pagesAi File HMnikunjNo ratings yet

- SDN 2014Document9 pagesSDN 2014AGUNG TRI LAKSONONo ratings yet

- Cs431 CD Lab Manual - Knpy PDFDocument47 pagesCs431 CD Lab Manual - Knpy PDFVishnu SNo ratings yet

- Exploiting Deadline Flexibility in Grid Workflow ReschedulingDocument23 pagesExploiting Deadline Flexibility in Grid Workflow Reschedulingprathyusai1990No ratings yet

- Updated DSP Manual 15ECL57 PDFDocument97 pagesUpdated DSP Manual 15ECL57 PDFanujna100% (1)

- Bachelor of Engineering in Computer Science & Engineering: Visveshvaraya Technological University, BelgaumDocument45 pagesBachelor of Engineering in Computer Science & Engineering: Visveshvaraya Technological University, BelgaumAvin JainNo ratings yet

- Visual Basic Application For Statistical Process Control: A Case of Metal Frame For Actuator Production ProcessDocument6 pagesVisual Basic Application For Statistical Process Control: A Case of Metal Frame For Actuator Production ProcessDanny WatsonNo ratings yet

- Cs 103 Computer System and Programming: Chapter 02: C++ Programming BasicsDocument56 pagesCs 103 Computer System and Programming: Chapter 02: C++ Programming BasicsImtiaz KhanNo ratings yet

- Lab Manual DSP1Document32 pagesLab Manual DSP1OmkarNo ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- Instructional Supervisory Plan School Year 2020-2021Document6 pagesInstructional Supervisory Plan School Year 2020-2021Leonelyn Hermosa Gasco - CosidoNo ratings yet

- Programme Guide - MechanicalDocument54 pagesProgramme Guide - MechanicalBhaskar MajumderNo ratings yet

- The Super Book of Web Tools For EducatorsDocument83 pagesThe Super Book of Web Tools For Educatorsrichardbyrne100% (2)

- HarshavardhanaDocument9 pagesHarshavardhanask aslamNo ratings yet

- C Multiple Choice Questions and Answers PDFDocument3 pagesC Multiple Choice Questions and Answers PDFRAHUL ROYNo ratings yet

- Research ProposalDocument7 pagesResearch ProposalLinh Bảo BảoNo ratings yet

- Yashwant Front ApgeDocument3 pagesYashwant Front Apgeashi ashiNo ratings yet

- Essay Bahasa InggrisDocument2 pagesEssay Bahasa InggrisWilan Bangkong ProNo ratings yet

- Descriptive WritingDocument6 pagesDescriptive Writingvijthor100% (1)

- The K To 12 Grading System of The PhilippinesDocument4 pagesThe K To 12 Grading System of The PhilippinesPeter Philip M. Perez100% (5)

- The Impact of Stress On Academic PerformDocument9 pagesThe Impact of Stress On Academic Performbarbieflores762No ratings yet

- Male PsychologyDocument20 pagesMale PsychologyMaper Anne ManaliliNo ratings yet

- The Johari WindowDocument13 pagesThe Johari WindowManmeet AroraNo ratings yet

- External RelationsDocument6 pagesExternal RelationsNguyễn Tuệ AnNo ratings yet

- Distinguish Between Medical Negligence and Medical Malpractice.Document1 pageDistinguish Between Medical Negligence and Medical Malpractice.Sheilla SayatNo ratings yet

- Ipoa Employment Application Form - 2024Document6 pagesIpoa Employment Application Form - 2024Monicah KasambaNo ratings yet

- 2017 08 en PG Fa SmallDocument284 pages2017 08 en PG Fa SmallNguyen QuocNo ratings yet

- Interview Questions - Ethnographic InterviewingDocument2 pagesInterview Questions - Ethnographic InterviewingigorlsNo ratings yet

- Folleto Tríptico de Servicio de Marketing Agencia Creativa Ilustrado Doodle MulticolorDocument2 pagesFolleto Tríptico de Servicio de Marketing Agencia Creativa Ilustrado Doodle Multicolorangela140302No ratings yet

- Grade 3 Math: Outcomes Strand: Number GLO: Develop Number Sense SLO'sDocument7 pagesGrade 3 Math: Outcomes Strand: Number GLO: Develop Number Sense SLO'sapi-531818346No ratings yet

- Communicated To Students For Different GSB Cohorts)Document6 pagesCommunicated To Students For Different GSB Cohorts)StaygoldNo ratings yet

- CompTIA CTTplusHandbookDocument76 pagesCompTIA CTTplusHandbookfarahnc10% (1)

- Shu Lesson Plan 2Document4 pagesShu Lesson Plan 2api-278838777No ratings yet

- Scenario PlanningDocument4 pagesScenario PlanningWasin SaengnumpongNo ratings yet

- Advertisement: Surguja Kshetriya Gramin Bank Izorzd & Lsuv y Csad VKQ BF.M KDocument15 pagesAdvertisement: Surguja Kshetriya Gramin Bank Izorzd & Lsuv y Csad VKQ BF.M KAchyut SharmaNo ratings yet

- Math Curriculum GuideDocument23 pagesMath Curriculum GuideChristeanne Justerine MendozaNo ratings yet