Professional Documents

Culture Documents

Datasheet PDF

Datasheet PDF

Uploaded by

Boris SantmariaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet PDF

Datasheet PDF

Uploaded by

Boris SantmariaCopyright:

Available Formats

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

D Low rDS(on) . . . 5 Ω Typical DW OR N PACKAGE

D Avalanche Energy . . . 30 mJ (TOP VIEW)

D Eight Power DMOS-Transistor Outputs of

CLR 1 20 VCC

150-mA Continuous Current

D 500-mA Typical Current-Limiting Capability

D1

D2

2

3

19

18

D8

D7

D Output Clamp Voltage . . . 50 V DRAIN1 4 17 DRAIN8

D Low Power Consumption DRAIN2 5 16 DRAIN7

DRAIN3 6 15 DRAIN6

description DRAIN4 7 14 DRAIN5

D3 8 13 D6

The TPIC6B273 is a monolithic, high-voltage, D4 9 12 D5

medium-current, power logic octal D-type latch GND 10 11 CLK

with DMOS-transistor outputs designed for use in

systems that require relatively high load power.

The device contains a built-in voltage clamp on logic symbol†

the outputs for inductive transient protection.

Power driver applications include relays, sole- 1

CLR R

noids, and other medium-current or high-voltage 11

CLK C1

loads.

2 4

The TPIC6B273 contains eight positive-edge- D1 1D DRAIN1

triggered D-type flip-flops with a direct clear input. 3 5

D2 DRAIN2

Each flip-flop features an open-drain power 8 6

D3 DRAIN3

DMOS-transistor output. 9 7

D4 DRAIN4

When clear (CLR) is high, information at the D 12 14

D5 DRAIN5

inputs meeting the setup time requirements is 13 15

D6 DRAIN6

transferred to the DRAIN outputs on the positive- 18 16

going edge of the clock (CLK) pulse. Clock D7 DRAIN7

19 17

triggering occurs at a particular voltage level and D8 DRAIN8

is not directly related to the transition time of the

† This symbol is in accordance with ANSI/IEEE Standard 91-1984

positive-going pulse. When the clock input (CLK)

and IEC Publication 617-12.

is at either the high or low level, the D input signal

has no effect at the output. An asynchronous CLR FUNCTION TABLE

is provided to turn all eight DMOS-transistor (each channel)

outputs off. When data is low for a given output, INPUTS OUTPUT

the DMOS-transistor output is off. When data is CLR CLK D DRAIN

high, the DMOS-transistor output has sink-current L X X H

capability. H ↑ H L

H ↑ L H

Outputs are low-side, open-drain DMOS

H L X Latched

transistors with output ratings of 50 V and 150-mA

H = high level, L = low level, X = irrelevant

continuous sink-current capability. Each output

provides a 500-mA typical current limit at

TC = 25°C. The current limit decreases as the

junction temperature increases for additional

device protection.

The TPIC6B273 is characterized for operation over the operating case temperature range of – 40°C to 125°C.

PRODUCTION DATA information is current as of publication date. Copyright 1997, Texas Instruments Incorporated

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

logic diagram (positive logic)

4

DRAIN1

1

CLR CLR

D1 2

1D

11

CLK C1

5

DRAIN2

CLR

3

D2 1D

C1

6

DRAIN3

CLR

8

D3 1D

C1

7

DRAIN4

CLR

9

D4 1D

C1

14

DRAIN5

CLR

12

D5 1D

C1

15

DRAIN6

CLR

13

D6 1D

C1

16

DRAIN7

CLR

18

D7 1D

C1

17

DRAIN8

CLR

19

D8 1D

10

GND

C1

2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

schematic of inputs and outputs

EQUIVALENT OF EACH INPUT TYPICAL OF ALL DRAIN OUTPUTS

VCC

DRAIN

50 V

Input

25 V

12 V 20 V

GND

GND

absolute maximum ratings over recommended operating case temperature range (unless

otherwise noted)†

Logic supply voltage, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

Logic input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 0.3 V to 7 V

Power DMOS drain-to-source voltage, VDS (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 V

Continuous source-to-drain diode anode current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 mA

Pulsed source-to-drain diode anode current (see Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 A

Pulsed drain current, each output, all outputs on, ID, TC = 25°C (see Note 3) . . . . . . . . . . . . . . . . . . . 500 mA

Continuous drain current, each output, all outputs on, ID, TC = 25°C . . . . . . . . . . . . . . . . . . . . . . . . . . . 150 mA

Peak drain current single output, IDM,TC = 25°C (see Note 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 mA

Single-pulse avalanche energy, EAS (see Figure 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 mJ

Avalanche current, IAS (see Note 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 mA

Continuous total dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Dissipation Rating Table

Operating virtual junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 40°C to 150°C

Operating case temperature range, TC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 40°C to 125°C

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 65°C to 150°C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to GND.

2. Each power DMOS source is internally connected to GND.

3. Pulse duration ≤ 100 µs and duty cycle ≤ 2%.

4. DRAIN supply voltage = 15 V, starting junction temperature (TJS) = 25°C, L = 200 mH, IAS = 0.5 A (see Figure 4).

DISSIPATION RATING TABLE

TC ≤ 25°C DERATING FACTOR TC = 125°C

PACKAGE

POWER RATING ABOVE TC = 25°C POWER RATING

DW 1389 mW 11.1 mW/°C 278 mW

N 1050 mW 10.5 mW/°C 263 mW

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

recommended operating conditions

MIN MAX UNIT

Logic supply voltage, VCC 4.5 5.5 V

High-level input voltage, VIH 0.85 VCC V

Low-level input voltage, VIL 0.15 VCC V

Pulsed drain output current, TC = 25°C, VCC = 5 V (see Notes 3 and 5) – 500 500 mA

Setup time, D high before CLK↑, tsu (see Figure 2) 20 ns

Hold time, D high after CLK↑, th (see Figure 2) 20 ns

Pulse duration, tw (see Figure 2) 40 ns

Operating case temperature, TC – 40 125 °C

electrical characteristics, VCC = 5 V, TC = 25°C (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Drain-to-source breakdown

V(BR)DSX voltage ID = 1 mA 50 V

Source-to-drain diode forward

VSD voltage IF = 100 mA 0.85 1 V

IIH High-level input current VCC = 5.5 V, VI = VCC 1 µA

IIL Low-level input current VCC = 5.5 V, VI = 0 –1 µA

All outputs off 20 100

ICC Logic supply current VCC = 5 5V

5.5 µA

All outputs on 150 300

VDS(on) = 0.5 V, IN = ID, TC = 85°C,

IN Nominal current 90 mA

See Notes 5, 6, and 7

VDS = 40 V, VCC = 5.5 V 0.1 5

IDSX Off state drain current

Off-state µA

VDS = 40 V, VCC = 5.5 V, TC = 125°C 0.15 8

ID = 100 mA, VCC = 4.5 V 4.2 5.7

Static drain-to-source on-state ID = 100 mA, VCC = 4.5 V, See Notes 5 and 6

rDS(on) 6.8 9.5 Ω

resistance TC = 125°C and Figures 6 and 7

ID = 350 mA, VCC = 4.5 V 5.5 8

switching characteristics, VCC = 5 V, TC = 25°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

tPLH Propagation delay time, low-to-high-level output from CLK 150 ns

tPHL Propagation delay time, high-to-low-level output from CLK CL = 30 pF,, ID = 100 mA,, 90 ns

tr Rise time, drain output See Figures 1, 2, and 8 200 ns

tf Fall time, drain output 200 ns

ta Reverse-recovery-current rise time IF = 100 mA, µ

di/dt = 20 A/µs, 100

ns

trr Reverse-recovery time See Notes 5 and 6 and Figure 3 300

NOTES: 3. Pulse duration ≤ 100 µs and duty cycle ≤ 2%.

5. Technique should limit TJ – TC to 10°C maximum.

6. These parameters are measured with voltage-sensing contacts separate from the current-carrying contacts.

7. Nominal current is defined for a consistent comparison between devices from different sources. It is the current that produces a

voltage drop of 0.5 V at TC = 85°C.

4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

thermal resistance

PARAMETER TEST CONDITIONS MIN MAX UNIT

DW package 90

RθJA resistance junction-to-ambient

Thermal resistance, junction to ambient All 8 outputs with equal power °C/W

N package 95

PARAMETER MEASUREMENT INFORMATION

5V 24 V

20 5V

ID CLK

VCC 0V

235 Ω

11 DUT 5V

CLK 4 –7, Output D

14 –17 0V

Word DRAIN

Generator D 5V

(see Note A) 1 CL = 30 pF CLR

CLR (see Note B) 0V

GND

24 V

10 Output

0.5 V

TEST CIRCUIT VOLTAGE WAVEFORMS

Figure 1. Resistive-Load Test Circuit and Voltage Waveforms

5V

D

5V 0V

5V

CLK

1 24 V 50% 50%

20

0V

VCC CLR tPLH tPHL

Word ID

Generator D

DUT 235 Ω 24 V

(see Note A) 90% 90%

Output

10% 10%

4 –7, Output 0.5 V

Word 14 –17

11 DRAIN tr tf

Generator CLK

(see Note A) SWITCHING TIMES

CL = 30 pF

GND

(see Note B)

10 5V

CLK 50%

0V

TEST CIRCUIT tsu

th

5V

D 50% 50%

0V

tw

INPUT SETUP AND HOLD WAVEFORMS

Figure 2. Test Circuit, Switching Times, and Voltage Waveforms

NOTES: A. The word generator has the following characteristics: tr ≤ 10 ns, tf ≤ 10 ns, tw = 300 ns, pulsed repetition rate (PRR) = 5 KHz,

ZO = 50 Ω.

B. CL includes probe and jig capacitance.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 5

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

PARAMETER MEASUREMENT INFORMATION

TP K

DRAIN

0.1 A

Circuit 2500 µF

Under 250 V di/dt = 20 A/µs

Test + IF

L = 1 mH 25 V

IF –

(see Note A) 0

TP A

25% of IRM

t2

t1 t3 Driver

IRM

RG

VGG ta

50 Ω

(see Note B) trr

CURRENT WAVEFORM

TEST CIRCUIT

NOTES: A. The DRAIN terminal under test is connected to the TP K test point. All other terminals are connected together and connected to the

TP A test point.

B. The VGG amplitude and RG are adjusted for di/dt = 20 A/µs. A VGG double-pulse train is used to set IF = 0.1 A, where t1 = 10 µs,

t2 = 7 µs, and t3 = 3 µs.

Figure 3. Reverse-Recovery-Current Test Circuit and Waveforms of Source-to-Drain Diode

5V 15 V

tw

tav

20 5V

Input

VCC 10.5 Ω

1 See Note B

CLR ID 0V

IAS = 0.5 A

11 DUT 200 mH

Word CLK ID

4 –7,

Generator

14 –17

(see Note A) D DRAIN VDS

V(BR)DSX = 50 V

GND

VDS MIN

10

TEST CIRCUIT VOLTAGE AND CURRENT WAVEFORMS

NOTES: A. The word generator has the following characteristics: tr ≤ 10 ns, tf ≤ 10 ns, ZO = 50 Ω.

B. Input pulse duration, tw, is increased until peak current IAS = 0.5 A.

Energy test is defined as EAS = IAS x V(BR)DSX x tav/2 = 30 mJ.

Figure 4. Single-Pulse Avalanche Energy Test Circuit and Waveforms

6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

TYPICAL CHARACTERISTICS

PEAK AVALANCHE CURRENT DRAIN-TO-SOURCE ON-STATE RESISTANCE

vs vs

TIME DURATION OF AVALANCHE DRAIN CURRENT

10 18

r DS(on) –Drain-to-Source On-State Resistance – Ω

VCC = 5 V

TC = 25°C See Note A

16

IAS – Peak Avalanche Current – A

4

14

TC = 125°C

2 12

10

1

8

0.4 6

TC = 25°C

4

0.2 TC = – 40°C

2

0.1 0

0.1 0.2 0.4 1 2 4 10 0 100 200 300 400 500 600 700

tav – Time Duration of Avalanche – ms ID – Drain Current – mA

Figure 5 Figure 6

STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE SWITCHING TIME

vs vs

LOGIC SUPPLY VOLTAGE CASE TEMPERATURE

r DS(on) – Static Drain-to-Source On-State Resistance – Ω

8 300

ID = 100 mA ID = 100 mA

See Note A See Note A

7 tf

TC = 125°C

250

6

Switching Time – ns

tr

5 200

TC = 25°C

4

tPLH

150

3

TC = – 40°C

2

100 tPHL

0 50

4 4.5 5 5.5 6 6.5 7 – 50 – 25 0 25 50 75 100 125

TC – Case Temperature – °C

VCC – Logic Supply Voltage – V

Figure 7 Figure 8

NOTE C: Technique should limit TJ – TC to 10°C maximum.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7

TPIC6B273

POWER LOGIC OCTAL D-TYPE LATCH

SLIS031 – APRIL 1994 – REVISED JULY 1995

THERMAL INFORMATION

MAXIMUM CONTINUOUS MAXIMUM PEAK DRAIN CURRENT

DRAIN CURRENT OF EACH OUTPUT OF EACH OUTPUT

vs vs

NUMBER OF OUTPUTS CONDUCTING NUMBER OF OUTPUTS CONDUCTING

SIMULTANEOUSLY SIMULTANEOUSLY

I D – Maximum Peak Drain Current of Each Output – A

0.45 0.5

VCC = 5 V d = 10%

I D – Maximum Continuous Drain Current

0.4 0.45

d = 20%

0.35 0.4

0.35

0.3 d = 50%

of Each Output – A

0.3

0.25

TC = 25°C 0.25

0.2 d = 80%

0.2

0.15

TC = 100°C 0.15

0.1 VCC = 5 V

0.1

TC = 125°C TC = 25°C

0.05 d = tw/tperiod

0.05

= 1 ms/tperiod

0 0

1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8

N – Number of Outputs Conducting Simultaneously N – Number of Outputs Conducting Simultaneously

Figure 9 Figure 10

8 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Astm D-4189Document3 pagesAstm D-4189Rafael De la cruz MaquerhuaNo ratings yet

- D D D D D D D D D: DescriptionDocument17 pagesD D D D D D D D D: DescriptionCatalin Constantin PopaNo ratings yet

- Tpic6595 PDFDocument9 pagesTpic6595 PDFljNo ratings yet

- Tpic 6 B 259Document20 pagesTpic 6 B 259Drew AlbaneseNo ratings yet

- D D D D D D D D: TLC556, TLC556Y Dual Lincmos TimersDocument24 pagesD D D D D D D D: TLC556, TLC556Y Dual Lincmos Timerselfak.2000No ratings yet

- TLC 556 MDocument23 pagesTLC 556 MNitin SharmaNo ratings yet

- D D D D D D D D: SN75437A Quadruple Peripheral DriverDocument7 pagesD D D D D D D D: SN75437A Quadruple Peripheral DriverCarlos Luis ColmenaresNo ratings yet

- D D D D D D: SN54HC74, SN74HC74 Dual D-Type Positive-Edge-Triggered Flip-Flops With Clear and PresetDocument24 pagesD D D D D D: SN54HC74, SN74HC74 Dual D-Type Positive-Edge-Triggered Flip-Flops With Clear and PresetViola Safa Nur AnnisaNo ratings yet

- L293D Motor Driver DatasheetDocument14 pagesL293D Motor Driver DatasheetAnkit Daftery100% (3)

- D D D D D D D D D D D D D D D D: SN75ALS170, SN75ALS170A Triple Differential Bus TransceiverDocument22 pagesD D D D D D D D D D D D D D D D: SN75ALS170, SN75ALS170A Triple Differential Bus TransceiverDedii KurniawanNo ratings yet

- D D D D D D D: MC3487 Quadruple Differential Line DriverDocument7 pagesD D D D D D D: MC3487 Quadruple Differential Line DriverRichard Andrianjaka LuckyNo ratings yet

- 74 Als 151Document19 pages74 Als 151Lu HoaNo ratings yet

- Quad 2-Input NAND Buffer: Integrated CircuitsDocument8 pagesQuad 2-Input NAND Buffer: Integrated CircuitsMarco AndresNo ratings yet

- En: Thisdatasheet Ispresentedby Themanufacturer.: Please V Isit Our Websit E F or PR Icing and Av Ailabilit Y atDocument19 pagesEn: Thisdatasheet Ispresentedby Themanufacturer.: Please V Isit Our Websit E F or PR Icing and Av Ailabilit Y atTara BurgessNo ratings yet

- TPIC46L01, TPIC46L02, TPIC46L03 6-Channel Serial and Parallel Low-Side Pre-Fet DriverDocument37 pagesTPIC46L01, TPIC46L02, TPIC46L03 6-Channel Serial and Parallel Low-Side Pre-Fet DriverChristian Tubay MaciasNo ratings yet

- D D D D D D D D D D: Description/ordering InformationDocument21 pagesD D D D D D D D D D: Description/ordering InformationJoil AlvesNo ratings yet

- bd8389fv M eDocument21 pagesbd8389fv M eNicrostNo ratings yet

- TPIC6B595 Power Logic 8-Bit Shift Register: 1 FeaturesDocument27 pagesTPIC6B595 Power Logic 8-Bit Shift Register: 1 FeaturesmuaadhNo ratings yet

- D D D D D D D D D D: SN75174 Quadruple Differential Line DriverDocument17 pagesD D D D D D D D D D: SN75174 Quadruple Differential Line DriverViệt Hà ThanhNo ratings yet

- SN75174Document9 pagesSN75174Fernando Montes de OcaNo ratings yet

- 5 Volt Only Driver/Receiver: RS232 EIA-232-E and CCITT V.28Document9 pages5 Volt Only Driver/Receiver: RS232 EIA-232-E and CCITT V.28Mauro Miranda CoutoNo ratings yet

- D D D D D D D D D D: Description/ordering InformationDocument19 pagesD D D D D D D D D D: Description/ordering InformationJulio C. SalinasNo ratings yet

- TLC5620Document14 pagesTLC5620Dirson Volmir WilligNo ratings yet

- ths5661 PDFDocument29 pagesths5661 PDFIqbal AchmadiNo ratings yet

- SN75ALS172ADocument14 pagesSN75ALS172AJuan HernándezNo ratings yet

- TL3842 5Document12 pagesTL3842 5ajit_kmsNo ratings yet

- SN75172 LCB 2 Ci TransceiverDocument16 pagesSN75172 LCB 2 Ci TransceiverHUGO SOARESNo ratings yet

- D D D D D D D: SN54AHCT132, SN74AHCT132 Quadruple Positive-Nand Gates With Schmitt-Trigger InputsDocument10 pagesD D D D D D D: SN54AHCT132, SN74AHCT132 Quadruple Positive-Nand Gates With Schmitt-Trigger InputsStuxnetNo ratings yet

- ACTOM CE BROCHURE-March 2013 LRDocument23 pagesACTOM CE BROCHURE-March 2013 LRWHann Peter ChuiNo ratings yet

- Alarm 087 IC QuemadoDocument9 pagesAlarm 087 IC QuemadoLio SnNo ratings yet

- MC145406 PDocument10 pagesMC145406 PpoindextNo ratings yet

- SN 74 Abt 16500 BDocument11 pagesSN 74 Abt 16500 Bmaxa95xf4No ratings yet

- D D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownDocument23 pagesD D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownJulio Rafael GamboaNo ratings yet

- Description/ordering Information: 1out 1IN 1IN+ GND V 2out 2IN 2IN+Document18 pagesDescription/ordering Information: 1out 1IN 1IN+ GND V 2out 2IN 2IN+ARSYIAN RIZKI PRATAMANo ratings yet

- 75als194 Ic2Document11 pages75als194 Ic2TomNo ratings yet

- Circuit CollectionsDocument30 pagesCircuit CollectionsHtet Myat Soe100% (1)

- DatasheetDocument8 pagesDatasheetStuxnetNo ratings yet

- D D D D D D D D D D D: Description/ordering InformationDocument14 pagesD D D D D D D D D D D: Description/ordering InformationКонстантин МережкоNo ratings yet

- TPS5125Document21 pagesTPS5125Shaun Dwyer Van HeerdenNo ratings yet

- Features Applications: D D D D D D D D D D D D D D DDocument15 pagesFeatures Applications: D D D D D D D D D D D D D D DĐịnh Xuân HàNo ratings yet

- Wiring Diagram: Noise Filter PowerDocument4 pagesWiring Diagram: Noise Filter Powervoicedont dieNo ratings yet

- 7402Document11 pages7402Roberto BelanNo ratings yet

- D D D D D: SN54AHC138, SN74AHC138 3-Line To 8-Line Decoders/DemultiplexersDocument10 pagesD D D D D: SN54AHC138, SN74AHC138 3-Line To 8-Line Decoders/DemultiplexersEva AvilésNo ratings yet

- L2917Document7 pagesL2917Sofyan AndikaNo ratings yet

- SN54HCT74-SN74HCT74 - Flip FlopDocument15 pagesSN54HCT74-SN74HCT74 - Flip FlopTiago LeonhardtNo ratings yet

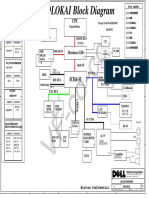

- MOLOKAI Block Diagram: VF-co-ccDocument39 pagesMOLOKAI Block Diagram: VF-co-ccWILLPC369No ratings yet

- Automotive ISO 9141 Serial Link Driver: MC33199 SemiconductorDocument12 pagesAutomotive ISO 9141 Serial Link Driver: MC33199 SemiconductorromoNo ratings yet

- D D D D D D: Description/ordering InformationDocument15 pagesD D D D D D: Description/ordering InformationDave LakesNo ratings yet

- SN 75114Document11 pagesSN 75114Hector LopezNo ratings yet

- D D D D D D D D D D D D D: SN75ALS1177, SN75ALS1178 Dual Differential Drivers and ReceiversDocument16 pagesD D D D D D D D D D D D D: SN75ALS1177, SN75ALS1178 Dual Differential Drivers and ReceiversMichael_Stefan_5630No ratings yet

- Lvds 388Document14 pagesLvds 388jack danialsNo ratings yet

- 3 V Headphone Amplifier: Ton GiesbertsDocument1 page3 V Headphone Amplifier: Ton GiesbertsTariq ZuhlufNo ratings yet

- SN 74 HCT 573Document20 pagesSN 74 HCT 573bvNo ratings yet

- Quad Intelligent Power Low Side Switch: Dson JDocument14 pagesQuad Intelligent Power Low Side Switch: Dson JTahar BenacherineNo ratings yet

- Data Sheets ImportantesDocument13 pagesData Sheets ImportantesFabiano Ferreira SaldanhaNo ratings yet

- MC3486 Quadruple Differential Line Receiver With 3-State OutputsDocument15 pagesMC3486 Quadruple Differential Line Receiver With 3-State OutputsRayMachado1No ratings yet

- ICL7135Document16 pagesICL7135JIGNESHNo ratings yet

- lm339 PDFDocument19 pageslm339 PDFAlexis LozanoNo ratings yet

- Analytical Methods For Slope Stability AnalysisDocument23 pagesAnalytical Methods For Slope Stability AnalysisPetrucio José Dos Santos Junior0% (1)

- Chapter 6Document55 pagesChapter 6Amanu WorkuNo ratings yet

- Owolabi - Akinyemi - Friday - Publication-UpdatedDocument10 pagesOwolabi - Akinyemi - Friday - Publication-UpdatedAkinNo ratings yet

- LTRT-83309 Mediant 600 and Mediant 1000 SIP User's Manual v6.4Document824 pagesLTRT-83309 Mediant 600 and Mediant 1000 SIP User's Manual v6.4kaz7878No ratings yet

- Huawei S6720-HI Series Switches DatasheetDocument25 pagesHuawei S6720-HI Series Switches DatasheetAbdelhafid LarouiNo ratings yet

- AB1014 - Performance Tuning - v2.0Document46 pagesAB1014 - Performance Tuning - v2.0sameer1562000No ratings yet

- 1 PUC Manual-17Document22 pages1 PUC Manual-17shyla100% (1)

- Nadia Karima Izzaty 1306369466 Dept. Teknik Sipil: Time (H) Rate (In/h) Direct Runoff (CFS) RM (In.)Document7 pagesNadia Karima Izzaty 1306369466 Dept. Teknik Sipil: Time (H) Rate (In/h) Direct Runoff (CFS) RM (In.)Nadia KarimaNo ratings yet

- Check List For Interior Elevation Drawings. Please Use These As A Guide Where ApplicableDocument3 pagesCheck List For Interior Elevation Drawings. Please Use These As A Guide Where ApplicableSafwan AhammedNo ratings yet

- Suntech 175w 24v Black Label Solar Panel PalletDocument2 pagesSuntech 175w 24v Black Label Solar Panel PalletfarhanNo ratings yet

- MTCR Handbook Item9Document20 pagesMTCR Handbook Item9makenodimaNo ratings yet

- 0 Rebut 1 JDHLWXDocument3 pages0 Rebut 1 JDHLWXRidho AinurNo ratings yet

- Problems On Batch Reactor-2Document11 pagesProblems On Batch Reactor-2Subhajit BagNo ratings yet

- Mivan Deck Panel Modification DocumentDocument60 pagesMivan Deck Panel Modification Documentkmandar99No ratings yet

- Analisa Teknis Pengujian Kekedapan Pengelasan Pada Tangki Tongkang Dengan Membandingkan Metode Chalk Test, Air Pressure Test Dan VacuumDocument18 pagesAnalisa Teknis Pengujian Kekedapan Pengelasan Pada Tangki Tongkang Dengan Membandingkan Metode Chalk Test, Air Pressure Test Dan VacuumIbnu HajarNo ratings yet

- 1.08 Example: 1 Exploring DataDocument2 pages1.08 Example: 1 Exploring DataAisha ChohanNo ratings yet

- Peel Synchro GuidelinesDocument20 pagesPeel Synchro GuidelinesSyed Imam100% (1)

- Agronomy 10 00702 v2 PDFDocument18 pagesAgronomy 10 00702 v2 PDFLuella LukenNo ratings yet

- BusDocument82 pagesBuspadmaNo ratings yet

- Specifications Indiana Limestone InstituteDocument19 pagesSpecifications Indiana Limestone InstituteAyman_Elmasry_9107No ratings yet

- Group 17 - Inorganic ChemistryDocument7 pagesGroup 17 - Inorganic ChemistryDefaults rulezNo ratings yet

- PNN Most Frequent Questions and AnswersDocument38 pagesPNN Most Frequent Questions and AnswersRoCo GeologoNo ratings yet

- CS3391 OOPS UNIT 5 NOTES EduEnggDocument34 pagesCS3391 OOPS UNIT 5 NOTES EduEnggAravind SamyNo ratings yet

- Vinay Sharma - inDocument3 pagesVinay Sharma - inVinay SharmaNo ratings yet

- 4x4 MIMO Boosts 4G and Gives Consumers A Taste of The Gigabit ExperienceDocument26 pages4x4 MIMO Boosts 4G and Gives Consumers A Taste of The Gigabit ExperiencemathNo ratings yet

- Ewing Dian Setyadi - Artikel Ilmiah - PpjpiDocument17 pagesEwing Dian Setyadi - Artikel Ilmiah - PpjpiewingsetyadiNo ratings yet

- Ppe Unit 1Document118 pagesPpe Unit 1Vbalaji VaithiyanathanNo ratings yet

- Synopsis PrintDocument4 pagesSynopsis PrintRuchika khekareNo ratings yet

- IB Biology IA ChecklistDocument2 pagesIB Biology IA Checklistpooja g pNo ratings yet