Professional Documents

Culture Documents

BLRF cd920 A3 C L3 V11

BLRF cd920 A3 C L3 V11

Uploaded by

Germano SthefanCopyright:

Available Formats

You might also like

- Wiring Diagram Honda Fit - PGM-FI System PDFDocument1 pageWiring Diagram Honda Fit - PGM-FI System PDFJoshua Varona100% (1)

- VPDM Pin LayoutDocument1 pageVPDM Pin LayoutBernardo OlivaNo ratings yet

- The Hillman Group Key Catalog PDFDocument124 pagesThe Hillman Group Key Catalog PDFgyrfalcon50% (2)

- Sparrow - Creative Agency Powerpoint PresentationDocument124 pagesSparrow - Creative Agency Powerpoint PresentationjackaleenNo ratings yet

- Electrical System 793D Off-Highway Truck: Harness and Wire Electrical Schematic SymbolsDocument4 pagesElectrical System 793D Off-Highway Truck: Harness and Wire Electrical Schematic SymbolsJose luis ConsuegraNo ratings yet

- Motorola Ming A1200Document3 pagesMotorola Ming A1200bassrivastava100% (2)

- Motorola V3 1Document3 pagesMotorola V3 1Techno Max IT SolutionsNo ratings yet

- Level 3 Repair: 8-1. Block DiagramDocument24 pagesLevel 3 Repair: 8-1. Block Diagramdialla abdarahimNo ratings yet

- OLIMEXINO-STM32 SCH LatestDocument1 pageOLIMEXINO-STM32 SCH Latestnathantshama1No ratings yet

- Dokumen - Tips Samsung GT E1200 SchematicsDocument7 pagesDokumen - Tips Samsung GT E1200 SchematicsHogir DoskyNo ratings yet

- TC1221 BaseDocument2 pagesTC1221 Baseand roidNo ratings yet

- Dumariya Station 25 KV Ac Traction Station Working Rule DiagramDocument1 pageDumariya Station 25 KV Ac Traction Station Working Rule DiagramAbhishek SinghNo ratings yet

- Taae Rce 11 09 2022Document22 pagesTaae Rce 11 09 2022Orbenson TanNo ratings yet

- TroubleshootingDocument34 pagesTroubleshootingsabbarapinajaji2No ratings yet

- Algae Neptune: RX Mid Channels GSM: CH 62 - 947,4 MHZDocument2 pagesAlgae Neptune: RX Mid Channels GSM: CH 62 - 947,4 MHZaposticaa100% (1)

- 08 - GT S5222 Tshoo 7Document37 pages08 - GT S5222 Tshoo 7Nelson BoneNo ratings yet

- Renr8131-01 C12Document2 pagesRenr8131-01 C12ait mimouneNo ratings yet

- Air Bag SrsDocument1 pageAir Bag SrspeterrozenveldNo ratings yet

- Va2-Yu02-P1bay-145001 - Overall Protection and Metering Single Line Diagram - R1Document1 pageVa2-Yu02-P1bay-145001 - Overall Protection and Metering Single Line Diagram - R1Công TràNo ratings yet

- NGR Alarm Panel Drawing 623265Document2 pagesNGR Alarm Panel Drawing 623265Claudio GuevaraNo ratings yet

- Carvin C-1644 4 Bussmaster Audio 2002 SCHDocument1 pageCarvin C-1644 4 Bussmaster Audio 2002 SCHAndres GuerreroNo ratings yet

- ANT Block Diagram CurrentDocument1 pageANT Block Diagram CurrentGurinderjeet SinghNo ratings yet

- DLC3Document2 pagesDLC3Raul Garcia GuevaraNo ratings yet

- Schematic Diagram: 7-1 Circuit DescriptionDocument8 pagesSchematic Diagram: 7-1 Circuit Descriptionoppa BaruNo ratings yet

- Level 3 Repair: 8-1. Block DiagramDocument79 pagesLevel 3 Repair: 8-1. Block DiagramAli UnlockNo ratings yet

- Onkyo tx-sr876 SMDocument23 pagesOnkyo tx-sr876 SMMoto MottoNo ratings yet

- ProductChart A2-Web PDFDocument1 pageProductChart A2-Web PDFAllan NallaNo ratings yet

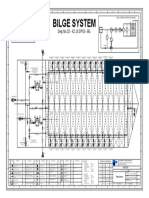

- Bilge System of Oil CarrierDocument1 pageBilge System of Oil CarrierArrijal PratamaNo ratings yet

- ME-1831 Service ManualDocument13 pagesME-1831 Service ManualmeahdiNo ratings yet

- Data Sheet MTI EN - 0Document2 pagesData Sheet MTI EN - 0lara2005No ratings yet

- Observation April 01, 2021 - 01Document2 pagesObservation April 01, 2021 - 01Abdul RahmanNo ratings yet

- Sti 510 PDFDocument1 pageSti 510 PDFPresli Joel Clemente SullcaNo ratings yet

- Planos de Grua CaterpillarDocument4 pagesPlanos de Grua CaterpillarMarco RodriguezNo ratings yet

- HCD-GTZ4 - GTZ5 Diagrama-20135Document11 pagesHCD-GTZ4 - GTZ5 Diagrama-20135vivian elizabeth hurtadoNo ratings yet

- 12AX7 Phono Tube Preamplifier User ManualDocument7 pages12AX7 Phono Tube Preamplifier User ManualmikelikespieNo ratings yet

- Darlington: Silicon NPN Triple Diffused Planar TransistorDocument2 pagesDarlington: Silicon NPN Triple Diffused Planar TransistorGilberto DiazNo ratings yet

- En.x Nucleo Iks02a1 SchematicDocument4 pagesEn.x Nucleo Iks02a1 SchematicIbrahim AkNo ratings yet

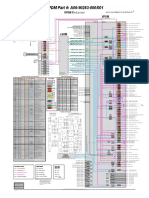

- Cat Dcs Sis ControllerDocument6 pagesCat Dcs Sis ControllerMechanical departmentNo ratings yet

- Transformer /175W Line Safety Line: MotorDocument1 pageTransformer /175W Line Safety Line: Motororo plataNo ratings yet

- 08 DRG - Protection SLD 220kV SarigamDocument1 page08 DRG - Protection SLD 220kV SarigamAmarjit Kulkarni100% (1)

- Sti 503Document1 pageSti 503Rene Mendoza100% (1)

- 1242 B2 ISMB200: No (S) - BEAM - B2 1Document1 page1242 B2 ISMB200: No (S) - BEAM - B2 1M. Azharuddin TamboliNo ratings yet

- Sti 503 Sitema Electeico Cascadia Dd16Document2 pagesSti 503 Sitema Electeico Cascadia Dd16jlrossi.tlcNo ratings yet

- SLD For CPP Metering SystemDocument1 pageSLD For CPP Metering SystemJagadeesh rNo ratings yet

- Senr1361 01Document2 pagesSenr1361 01Reinaldo Alonso Martinez CuellarNo ratings yet

- (Kas001043 - Inq - 2021 - 10 - 0016256) - Ewd Kick Sensor 716BDocument1 page(Kas001043 - Inq - 2021 - 10 - 0016256) - Ewd Kick Sensor 716BBYU OTOVLOGNo ratings yet

- ANT GSM850 RX Dcs/Pcs RX GSM900/W900 RX W2100 RX W1900 TX/RX GSM850/900 TX Dcs/Pcs TX W900 TX W2100 TXDocument7 pagesANT GSM850 RX Dcs/Pcs RX GSM900/W900 RX W2100 RX W1900 TX/RX GSM850/900 TX Dcs/Pcs TX W900 TX W2100 TXELECTRONICA TRUJILLONo ratings yet

- Twitter SLDDocument1 pageTwitter SLDMohamed ShafeyNo ratings yet

- 001 ASSEMBLY ModelDocument1 page001 ASSEMBLY ModelsanusiibrahimNo ratings yet

- In Out SEL 787Document1 pageIn Out SEL 787Tosikur RahmanNo ratings yet

- July 2020 UENR8299-05: Harness and Wire Electrical Schematic SymbolsDocument6 pagesJuly 2020 UENR8299-05: Harness and Wire Electrical Schematic SymbolsImtiaz AhmedNo ratings yet

- Gigabyte Gv-R67xtgaming Oc-12gd Rev 1.0Document42 pagesGigabyte Gv-R67xtgaming Oc-12gd Rev 1.0techgamebr85No ratings yet

- Vestax Vss PMC 280Document33 pagesVestax Vss PMC 280Diogo SilvaNo ratings yet

- Darlington: Silicon PNP Epitaxial Planar TransistorDocument1 pageDarlington: Silicon PNP Epitaxial Planar Transistormarcelo giussaniNo ratings yet

- Esq Manager Net 3+ USB (T0300101)Document1 pageEsq Manager Net 3+ USB (T0300101)RobertoBarbosaNo ratings yet

- STI 510VPDMPinLayoutDocument1 pageSTI 510VPDMPinLayoutManuel Solar100% (2)

- 8997 0846 00 DrawingsDocument41 pages8997 0846 00 Drawingsedduami montoya neyraNo ratings yet

- 3 Phase Electrical Circuit - 480 Volt & 230 Volt / 12V: Wire Color Code and GaugeDocument1 page3 Phase Electrical Circuit - 480 Volt & 230 Volt / 12V: Wire Color Code and GaugeYhonni IrwanNo ratings yet

- Motor StartingDocument1 pageMotor StartingMoazam AliNo ratings yet

- Parts Catalogue DCD 250Document23 pagesParts Catalogue DCD 250Quốc Viêtj HuỳnhNo ratings yet

- Instant Assessments for Data Tracking, Grade 2: MathFrom EverandInstant Assessments for Data Tracking, Grade 2: MathNo ratings yet

- PRDFlipflatKeyboard cd920930 A4 C L4 V1.0 PDFDocument2 pagesPRDFlipflatKeyboard cd920930 A4 C L4 V1.0 PDFGermano SthefanNo ratings yet

- Zap Analysis Overview: Motorola Confidential Proprietry InformationDocument53 pagesZap Analysis Overview: Motorola Confidential Proprietry InformationGermano SthefanNo ratings yet

- RP Zap A4 BW l3 VXXDocument30 pagesRP Zap A4 BW l3 VXXGermano SthefanNo ratings yet

- Product Description: GSM Zap and Zap C (Refresh)Document17 pagesProduct Description: GSM Zap and Zap C (Refresh)Germano SthefanNo ratings yet

- PRDFlipflatKeyboard Cd920930 A4 C L4 V1.0Document2 pagesPRDFlipflatKeyboard Cd920930 A4 C L4 V1.0Germano SthefanNo ratings yet

- TX VCO Tuning Voltage A C D E: Logic - GSM - Dcs GSM - Dcs GSM - Dcs Logic - GSM - DcsDocument1 pageTX VCO Tuning Voltage A C D E: Logic - GSM - Dcs GSM - Dcs GSM - Dcs Logic - GSM - DcsGermano SthefanNo ratings yet

- LG KT610 Service Manual PDFDocument234 pagesLG KT610 Service Manual PDFGermano SthefanNo ratings yet

- National Semiconductor-LM317T P+-DatasheetDocument13 pagesNational Semiconductor-LM317T P+-DatasheetGermano SthefanNo ratings yet

- De Grote Vakantie Muziek BingoDocument17 pagesDe Grote Vakantie Muziek BingoKoen BothNo ratings yet

- Uts English Grade 4Document5 pagesUts English Grade 4prasetyoeko19889No ratings yet

- (Assignment) Apple Inc, (Profile)Document15 pages(Assignment) Apple Inc, (Profile)SvS79% (24)

- RC Module - Tone Based QuestionsDocument19 pagesRC Module - Tone Based QuestionsRohit NayakNo ratings yet

- SteinbeckDocument4 pagesSteinbeckRosu Daniel Si MirelaNo ratings yet

- Don't Ask, Don't TellDocument9 pagesDon't Ask, Don't TellMarionNo ratings yet

- Science PR Ques 3 and 6Document2 pagesScience PR Ques 3 and 6Vyan Anand (Admn. No : 7366)No ratings yet

- App InventorDocument6 pagesApp InventorErik Martin Juarez AparicioNo ratings yet

- Veggie and Fruit Charts For Guinea PigsDocument4 pagesVeggie and Fruit Charts For Guinea Pigsg264906No ratings yet

- 2 The Business of Opera: Nicholas PayneDocument17 pages2 The Business of Opera: Nicholas PayneJilly CookeNo ratings yet

- Datos JeanDocument8 pagesDatos JeanJean Carlo GuarenasNo ratings yet

- Service Manual Tektronix TDS 500D TDS 600C TDS 700D TDS 714LDocument330 pagesService Manual Tektronix TDS 500D TDS 600C TDS 700D TDS 714Lrotex100% (1)

- The 4a'sDocument5 pagesThe 4a'sRisha BaconesNo ratings yet

- Tourism Task Force Final2Document62 pagesTourism Task Force Final2Hayat Ali Shaw100% (1)

- Akhree RashtaDocument15 pagesAkhree Rashtakumarkhiladi67No ratings yet

- Fallout: Project Brazil Development DocumentDocument12 pagesFallout: Project Brazil Development DocumentDanielson CageNo ratings yet

- Disassembly HPpro8000Document6 pagesDisassembly HPpro8000Denis Camacho50% (2)

- Pronunciation Worksheet Final - Ed: (T) (D) (/D) : //D/ Adds An Extra SyllableDocument2 pagesPronunciation Worksheet Final - Ed: (T) (D) (/D) : //D/ Adds An Extra SyllableSebastian castañedaNo ratings yet

- GFD 14 - Procedure in Drafting The Basic Patterns For Bodice, Sleeve, and SkirtDocument3 pagesGFD 14 - Procedure in Drafting The Basic Patterns For Bodice, Sleeve, and SkirtTrisha SaysonNo ratings yet

- Raag Darbari SongsDocument3 pagesRaag Darbari Songssubbaiah54No ratings yet

- Hidilyn DiazDocument3 pagesHidilyn DiazKen PedereNo ratings yet

- Motivate! 1 Test U4 StandardDocument6 pagesMotivate! 1 Test U4 StandardDragana VučkovićNo ratings yet

- Pinch 2002 PDFDocument23 pagesPinch 2002 PDFAbel CastroNo ratings yet

- Forms Dayof CoordinationDocument2 pagesForms Dayof CoordinationJacque Dee DuranNo ratings yet

- A Birthday Poem If Those I Loved Were LostDocument6 pagesA Birthday Poem If Those I Loved Were LostAira Dagus Maraña IINo ratings yet

- DAX Measures and Calculated Columns POWER BIDocument5 pagesDAX Measures and Calculated Columns POWER BIaiexplorer009No ratings yet

- Pakistani Diet PlanDocument4 pagesPakistani Diet Planmustafvi-927860% (1)

- Best Jason Statham Movies - Google SearchDocument1 pageBest Jason Statham Movies - Google SearchMuhammed RafelNo ratings yet

BLRF cd920 A3 C L3 V11

BLRF cd920 A3 C L3 V11

Uploaded by

Germano SthefanOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BLRF cd920 A3 C L3 V11

BLRF cd920 A3 C L3 V11

Uploaded by

Germano SthefanCopyright:

Available Formats

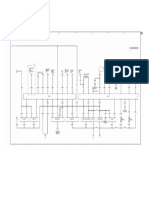

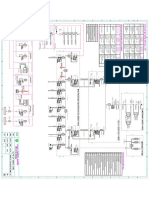

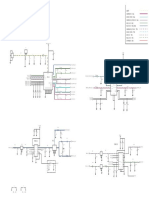

DUAL BAND ZAP RF BLOCK DIAGRAM RF BOARD SIGNALS

ANT GSM / DCS 1,2V Tx SIGNALS - 110062#, 1215#, 310#

Logig_*GSM_DCS g

CR 220 Frequency 217Hz - 1ms/cm

3 1

Logig_GSM_*DCS f

RX

43

U220 SAT_DET 3Vpp

Signal from PAC to SMOC.

When PA is at or near saturation signal is low, telling SMOC to reduce AOC drive

When the PA is not near saturation this is high, telling SMOC to increase AOC drive.

GSM ( CH 62 )

4

Q412

6

2

RX_EN RX275

Osc.

discrete

LOCAL

OSCILLATOR

41

GIFSYN Power Step:

04-11 - 50mVpp

Signal from the SMOC to the PAC

When this signal is low, the internal gain in the PAC is unity.

Loss from 430 MHz PLL DET_SW 12-15 - 900mVpp

circuty When this signal is high, the internal gain in the PAC is 1.

Antenna and EXT ANT 947,4 MHz

42

GSM -1.7dB B GSM 9,8dB

C

DCS -2.1dB GSM -0,6dB Q411 Q460 DCS 9,8dB GSM 10dB From uP to PAC.

FL400 FL461 TX_KEY

DCS -1,0dB 215 MHz DCS 10dB 46 2,75Vpp

This is a timing signal to the PAC to provide the current path for the initial loop precharge

7 GSM -2,2dB

C B C k 31 ATT.

RXI

5 GSM 12,8dB GSM -2,2dB 47

U401

DCS 9,3dB DCS -2,2dB

B C FL480 Q480 25dB DEMODULATION IQ REF to SMOC

Power Step:

DCS -2,2dB 48 Signal from SMOC to PAC.

4 B B C RXQ 04 - 520mVpp

C GSM -4,5dB AOC 15 - 280mVpp This is a linear control voltage for ramp up and ramp down of the PA output level.

2 Q430 SW_VCC 33

V1 V2 FL401 FL462 DCS -4,5dB This controls the voltage on the exciter control output (EXC) from the PAC.

SWITCH

EXT ANT j 12

6 3 c 16 VRef

Signal from uP but inverted via Q500 and used to time:-

SW_RF 1842,8 MHz b

from and to C B 1. GIF SYN 2. TIC 3. Tx VCO 4. PAC 5. RF Switch

3 2 RX_EN MDM_ANA_VCC Q221 13 TX_EN 3Vpp

J600 Pin2 DCS ( CH 700 ) GSM ( CH 62) DCS ( CH 700 ) to SMOCand 13 MHZ Clock Enables Tx Path when high

V1 V2

U401

U403 732,4 MHz h i 1627,8 MHz B+

E

17

E RF_START Signal from uP inverted via Q504.

SWITCH f 51

Logig_GSM_*DCS a RX275 Q222 DM_CS 2,8Vpp Enables TIC, PA and TX VCO.

18

8 CONTROL C B

g 19 When high, this enables Tx path.

Logig_*GSM_DCS

1 4 5 6

FILTER

SUPER

1 3 From SMOC IC to GIF SYN

TXI 2.1Vpp

RX_EN

TX_EN

MAIN VCO This signal is the in-phase input to the I-Q Modulator of the GIF SYN.

RX275

4 Q205 2 SF_VCC 21 59 CLK_OUT

-10V

6 26 From SMOC IC to GIF SYN

Q200 works as 2nd

GSM ( CH 62 ) DCS ( CH 700 ) TXQ 2.1Vpp This signal is the quadrature input to the I-Q Modulator of the GIF SYN.

HarmonicAmpl.

a d c e C C

C212 732,4 MHz 813,9 MHz

DCS 23 57 AFC

C Q201

Q200 PLL Y702

GSM ( CH 62 ) C B Q202 B

902,4 MHz C

C213

LOOP FILTER

CR221

Modem Callprocessor Interface

GSM

Q206 C214

C B GSM 1,5V - 2,5V From uP to SMOC.

CR203 CR 202 2,8Vpp

DCS ( CH 700 ) DCS 1,5V - 3,0V MDM_RD 500us/cm This signal indicates when the uP is reading data from the SMOC. High when enabled.

1747,8 MHz

*GSM_DCS

2,8Vpp From uP to SMOC.

GSM / DCS 52 RF_SPI MDM_WR 500us/cm This signal indicates when the uP is writing data to the SMOC. High when enabled.

R275 SPI SERIAL

GSM -0.4dB DCS 1,8 - 2,1V DATA BUS 53 RF_SCK

DCS -0.5dB INTERFACE

Output

FL301

GSM -17dB GSM 21dB GSM 8,7dB C TX VCO 14 1

Rx SIGNALS - In Standby Mode

DCS 17dB DCS 12dB GSM -5dB DCS

DCS -13dB B 7

CR303 DCS -5dB

C

Q350 U370 / TIC DM_CS

R475V From uP to SMOC

11, 22, 44 This is an interrupt from the uP to the SMOC. When high this indicates to the SMOC the

R337 VR353 PHASE 9,10 2,8Vpp

FL301 U301 Q330 Q331 Attenuator

GSM

C

8 CHARGE

PUMP4 DET. R475 RX_ACQ 500us/cm beginning of the receive burst.

B 2 ,12 61

Q351

PA GSM 2,5dB

DCS 6,0dB

C 4 R275 62

TXQ_P

TXQ_M 2,8Vpp

From uP to GIF SYN

Signal to drive the GIFSYN IC. This is a pulsed signal which controls the sending of SPI data

Q305

Q362 VR354 MODULATION 63 from SMOC RF_START

Q306 4 TXI_P 20us/cm

to the GIFSYN for all RF functions.

64

GSM 170 MHz TXI_M

FLTR_-10V 4

EXC 6 2

DM_CS

DCS 120 MHz

Osc.

6 Rx SIGNALS - 110062#, 262000#, 25013#, 241#

U340 / PAC 7 Q309 discrete 7 PLL Frequency 217Hz - 1ms/cm

3 1

f circuty RX SIGNAL PATH

RF_IN Logig_GSM_*DCS TX From GIF Syn to SMOC IC.

DET g LOCAL

TX SIGNAL PATH RXI

1.8Vpp

500us/cm This is a baseband analogue signal to A/D convertors of SMOC

2 Logig_*GSM_DCS

CR223 CR 261 OSCILLATOR

PAC_EN

1, 3 GSM 340 MHz MAIN VCO SIGNAL PATH

SAT. GSM_*DCS

DCS 240 MHz RXQ 1.8Vpp

From GIF Syn to SMOC IC.

4, 14 C271 500us/cm This is a baseband analogue signal to A/D convertors of SMOC

10

10 12 8 11 TUNING VOLTAGES

SAT_DET

From SMOC to GIF Syn.

REFERENCE CLOCK

DET_SW

TX_KEY

GSM ----- 1V 1.38Vrms

IQ_REF 500us/cm This is a DC level from SMOC for the RXI and Q signals to ride on.

DCS 1,7 - 2V

Orderable Part

AOC_DRIVE Non - Orderable Part

RF LAYER - ORDERABLE SPARES TEST COMMANDS RECEIVE DEBUG - GSM MODE TRANSMIT DEBUG

Part Part Part Part Part Part a MDM_ANA_VCC______, c -10V ______and

# press 2 sec. Enter Manual Test Mode with Test Card Before actually removing any cans it may be worth checking the RX275_____, b RX_EN______, e Put the phone into test mode and key in the commands: 110062#, 1200#, 310#

Designator Description Number Designator Description Number Firstly if no Transmiter output we should check the modulation output at U220 Pin 4 and the Main VCO

01 # Exit Manual Test Mode f is high to switch the output of Q412 Pin6 and Q205 Pin4 to high.

if the Logig_GSM_*DCS______

A1 Antenna Connector 3909155T01 Q350-351 TX VCO Transistor 4809940E01 j h i establish which of the signals are missing or if both the signals are missing.

at point _________to

07 # Mute Rx Audio Path TEST MODE: Type in Key commands: 110062#, 262000#, 25013#, 241#. Test for a set level eg. (-30dB’s) at point ______to compensate cable losses.

CR202 Main VCO Varactor 4809641F02 Q411 Receive Power Transistor 4809527E24 08 # Unmute Rx Audio Path k (pin 31of GIF).

- If the modulation output is missing and Main VCO is fine then remove SH03 and check in the TX Local Oscillator

The only real short-cut we can take is by probing the 215MHz test point_______ the CR212 and the tuning voltage from U220 Pin10. Check if Q222 and Q221 have both 2.7V.

CR203 Main VCO Diode 4809948D10 Q412 GSM / DCS Switch 4809939C07 09 # Mute Tx Audio Path

- If the 215 is OK then we can assume problem lies around GIF, either 430MHz Local Oscillator or in generation of RXI and RXQ. The can If still no problems found, measure from CPU DM_CS at SMOC Pin2. If ok replace U220.

10 # Unmute Tx Audio Path SH03 should then be removed. Check that IQ Ref from the SMOC is around 1.38Vdc and then the RXI and Q outputs from the GIF to check which is

CR220 RX Local Osc.Varactor 4809641F02 Q430 Receive Power Transistor 4809527E32 - -If Main VCO is missing but modulation is fine remove SH07 and check discretes, SF_VCC U220 Pin23 and

11 xxxx # Program Main Local Osc. to Channel faulty.

Main VCO tuning voltage U220 Pin21.

CR221 Master Xtal Varactor 4809641F04 Q460 Receive Mixer Transistor 4809527E20 - If the 215Mhz is low probe the R.F inputs to the Mixer to see which RF path (RF INPUT or MAIN VCO) the fault lies on.

12 xx # Set Tx Power level to fixed valure

- If Main VCO is low, the main suspicions are with the main VCO, or the VCO filter (FL461/462) and the SH07can should be removed. - If bothMain VCO and modulation are missing then check the collectors of Q221 and Q222 for 2.7V. If ok, then

CR223 Tx Local Osc. Diode 4809948D05 Q480 IF Isolation Aplifier 4809940E01 19 # Display SW Version Number of Call Processor check from CPU DM_CS at SMOC Pin2. Possible GIF SYN or SMOC problem.

. If the input to the filter is low, then there is some discretes under the VCO can. Check SF_VCC U220 Pin23 and Main VCO tuning voltage U220 Pin21.

CR261 Tx Local Osc. Varactor 4809641F02 U220 GIFSYN IC 5109632D92 20 # Display SW Version Number of Modem - If RF INPUT, and the MAIN VCO OK, the main suspicions are with the 2 input filters FL400 and FL401 and the can SH01 should be removed. - If TX is generated but is low then we look for problems under SH02 and SH09 and follow path through to antenna.

22 # Display SW Version Number of Speech Coder If the signal is low at the input to these, it could be losses caused by the Antenna Switch U401.

CR303 TX Exciter Diode 4809948D10 U401 Antenna Switch IC 5109572E04 k then we must also remove can SH08. The SAW filter (FL480) - If TX looks OK but fails in wingate check at the T/R switching circuitry (U401/U403) switching RF to J600 Pin2

- If 947.4 and 794.4 RF values are fine but 215MHz into GIF is low_____

25 # Set Continuous AGC and the J600 connector itself.

FL301 1st Rx Filter 9109193T05 U403 Switch Control 5109923D14 and IF Isolation AMP (Q480) is located under here.

26xxxx # Set Continuous AFC

FL400 2nd Rx Filter 9109144M01 U301 PA Dual FET IC 4809527E31 31x # Initiate Pseudo-Random Sequence with Midamble

FL401

FL480

VCO Filter

IF Saw Filter

9109111C08

9109035M01

U370

U340

TIC IC

PAC IC

5109879E12

5109632D91

33xxxx #

36 #

Synchronize to BCH Carrier

Initiate Acoustic Loopback

FREQUENCIES GSM / DCS

FL461 RX GSM Injection Filter 9109157M01 VR353 TX VCO Varactor 4809877C06 37 #

45xxxx #

Stop Test

Serving Cell Power Level

GSM / CHANNEL Tx Rx MAIN VCO Rx I.F Rx IF LO Tx I.F Tx IF LO REVISIONS

FL462 RX DCS Injection Filter 9109429J04 VR354 TX VCO Variator 4809877C04 1-Low 890.2 935.2 782.2 215 430 170 340 Europe Middle East & Africa Customer Services 13.04.99

46 # Display Current Valure od AFC DAC

LEVEL 3 COLOUR DIAGRAMS Rev. 1.1

Q200 Main VCO Transistor 4809527E30 SH1 Shield Low Noise Ampl. 2609474M01 47x # Set Audio Volume 62-Middle 902.4 947.4 794.4 215 430 170 340

Dual band ZAP

Q201-202 Main VCO Transistor 4809527E24 SH2 Shield PA 2609475M01 58 / xxxxxx # Display / Modify Security Code

124-High 914.8 959.8 806.8 215 430 170 340 Colin Jack, Michael Hansen, Billy Jenkins Page 2 of 2

Q205 GSM / DCS Switch 4809939C07 SH3 Shield GIFSYN 2609476M01 59 / xxx # Display / Modify Lock Code

60 # Display IMEI DCS / CHANNEL Tx Rx MAIN VCO Rx I.F Rx IF LO Tx I.F Tx IF LO

Q221-222 Supply Transistor 4809579E18 SH4 Shiel Exiter 2609477M01

7100 # Display Error Code

Q305-306 PAC Transistor 4809939C06 SH5-SH7 Shield VCO TIC 2609480M01 512-Low 1710 1805 1590 215 430 120 240

Q309 GSM / DCS Switch 4809939C07 SH8 Shield Mixer Iso Ampl. 2609478M01

700-Middle 1747,8 1842,8 1627,8 215 430 120 240

Q330 TX Buffer 4809527E26 SH9 Shield Rf Switch 2609479M01

885-High 1785 1880 1665 215 430 120 240

Q331 TX Predriver 4809527E24

Motorola Confidential Proprietary

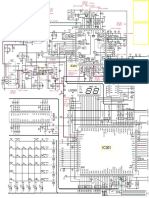

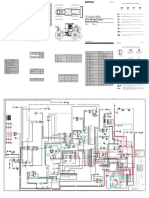

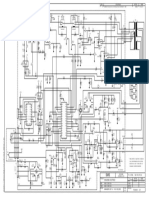

DUAL BAND ZAP AUDIO LOGIC BLOCK DIAGRAM LOGIC BOARD SIGNALS

13 MHz Clock

J600 Measured in standby mode

CLK_13IN

37 17 from GIFSYN

MF_INT

38 DSC_EN_B

217 Hz 63 13 From the CPU (U701). When high, Rx path enabled and low muted.

20

R275

BIC_INT

40 BIC 39

DOWNLINK

12

RX_EN

2.8mVpp

10ms / cm 1. Enables the Rf switch (U400) for receive mode.

2. Biases the mixer Q420, and low noise amp (Q418).

RESET

L275 DISPLAY 35 U703 UPLINK

CONNECTOR 46 11 From CPU (U701), but inverted by Q501. High when

L275 48, 57, 60 TX_EN 7Vpp 1. Enable the Rf switch for transmit mode & also the GIFSYN for transmit mode.

E J500 MAN_TEST

d TX_EN C B

3 10ms / cm 2. Supply Voltage for the PAC IC.

34 CLK_OUT 3. Isolates RF, by switching the PA Bias Circuitry ( Not shown).

Q500

Q501

DP_EN 1 31 32 1 64 4 54 58 33 FS_AUD

RX_EN Controlled at power up by GCAP (U900) & CPU (U701).

DISPLAY SW_RF RESET 2,8Vrms 1. Connected to CPU (U701), BIC (U703), Modem (U501) & Speech coder (U801).

to U403 Pin8 power on

c 2 200ms / cm After power up sequence, any chip can hold RESET low to power phone off if there is a problem.

BIC_INT BL_CNTL 30 SRAM

DWNLINK_AUD

to BIC

ON_OFF_SENSE

SP_INT

Processing

U702

UPLINK_AUD

BATT_SENSE

to SMOC From CPU (U701) to Eprom.

AD_THERM

RF_START Chip uBGA 2.8Vpp

Time

ROM1_CS DUAL_CS

Unit

1. Chip Enable controlling read/write access to and from Eprom (U702).

B+_SENSE

to GIFSYN to U704 100ns / cm

DACOUT

RX_ACQ

to SMOC Select RAM1_CS

DM_CS to U702

to TIC ....

Call Processor

to PAC / SMOC

TX_KEY RAM2_CS

to U702

EEPROM RAM1_CS 2.8Vpp

From CPU (U701) to SRAM.

100ns / cm 1. Chip Enable controlling read/write access to and from 1st half of SRAM (U704).

BATT_CNTL U705

U701

BGA

VA_SPI_SCK

VA_CS RESET

GND From CPU (U701) to SRAM.

1, 3,10,15 RAM2_CS 2.8Vpp

to SMOC VA_SPI_MI 100ns / cm 1. Chip Enable controlling read/write access to and from 2nd half of SRAM (U704).

FLASH MAN_TEST

VA_SPI_MO 5

ADDRESSS / DATA BUS U704

SPI_RFCS External uBGA From CPU (U701) to Eprom.

Queued SCI_TX ROM1_CS 2.8Vpp

SPI_MOSI Bus 100ns / cm 1. Chip Enable controlling read/write access to and from Eprom (U702).

SPI_MISO Serial

Interface

SPI_CLK Module

start up or 2.8Vpp From CPU (U701) to display, via connector J101.

MDM_RD AUDIO_IN DP_EN 100ns / cm 1. Processor selects to enable display. When high, the display is enabled and low disabled.

press key

MDM_WR 8

BATTERY L_BATT+ start up or Speech Coder Interface. This is a signal from uP (U701) to Speech Coder (U801).

U709 SC_INT press key 2.8Vpp

ADDRESSS / DATA BUS

1) This is a 20ms timing signal from U701 which times the decoding and encoding function of the Speech Coder

ADDRESSS / DATA BUS

2ns / cm U801.

THERM J610, 1

13MHz CLOCK

from CPU

DATA J613, 1 BATT_CNTL From BIC to uP.

BATT_FDBAK 2.8Vpp

Parts of Q602 4 MF_INT

1ms / cm This signal periodically interrupts the uP at 217Hz. During Power Saving mode this signal is set

to DC.

Backhousing L_BATT+ J611, 1

CR605

EXT_B+

DWNLINK_AUD

Assembly 14 Regulator Output from CLA 4.4V From BIC to uP. This signal interrupts the uP for a number of reasons.

Q601 R602

UPLINK_AUD

without charging 2.8Vpp 1. Keypad detection

GND J612, 1 BIC_INT press a key 2. Power Sense

AUDIO_IN

AUDIO_OUT 50us / cm

9 3. SIM Functions

4. DSC Bus Status Indicators

SP_INT

L_BATT+ CHRGC ISENSE

CLK_AUD

FS_AUD

RESET

2.8Vpp From butt plug (J600) to BIC chip (J600).. This is a comms link from an external peripherale and the phone,

14 47 46 29 17 15 16 UPLINK 10us / cm and could be either data information or speech information. It is also used to sense the presence of a DHFA and

the ignition status of the DHFA with DC levels

CHARGER

RESET 18 MOBPORTB

30

RX_ACQ 65 62 47 98 56 64 63

J802 MIC From BIC chip (U703) to butt plug (J600).. This is a comms link from an external peripherale and the phone,

20 12 13 DOWNLINK

5Vpp and could be either data information or speech information. It is also used to sense the presence of a DHFA and

CPU 2 10us / cm the ignition status of the DHFA with DC levels

10 9 1

TX_KEY Tone - From GIF Syn to BIC IC - 13MHz clock..

16

Generator CLK_13_IN 1.6Vpp This is the master clock reference required for the radio

- - 20

SPEAKER

21 50ns / cm

+

MDM_RD Audio 45

MDM_WR

4 Filter -1 + 19

DM_CS

100

A/D Buffer

49 RX_AUD 6 - - 5 Measured in test mode

Processing

ALERT

2 +

Signal

SPI_RFCS CPU Ampl. 54 AUX_AUD

99 CODEC test mode

SPI_MOSI Interface B+ 08#, 10#, 36# 2.7Vpp External audio from butt plug, directly to SMOC IC

1 37 AUDIO IN

2 434#, 477# 5us / cm

SPI_MISO 28

3 1 B+ DC/DC RF R275V

SPI_SCK D/A Audio MIC_BIAS 3 U982

RX SIGNAL PATH

11 Multiplexer test mode

Filter 40, 25 Vswitch DC/DC 22

RF_SPI AL L275V AUDIO OUT 08#, 10#, 36# 2.8Vpp External audio from SMOC via FCAP to butt plug

9 TX SIGNAL PATH 434#, 477# 5us / cm

to RF_SCK SPI 41

GIFSYN

10 26

27

TXQ_P U980 2, 7, 35, 36 RF R475

MAIN VCO SIGNAL PATH

TXQ_M 3

AFC

38 AFC 29 TXI_P L275 7, 26 25

U900 AL L500 2.8Vpp

D/A 5us / cm This signal is from the BIC to the SMOC

GMSK 28 TUNING VOLTAGES CLK_AUD

Voice Annotation

TXI_M

GCAP SW 11 VRef It is a timing signal and runs at 512KHz, and times the transfer of speech information on the DSC

40 PLL U500 23 RXI 39 37

REFERENCE CLOCK Bus between BIC and SMOC.

IQ REF

AOC

39 Transmit SMOC IC 21

22 RXQ VA_SPI_SCK

VSWITCH 5.6V

DET_SW Power Orderable Part

SAT_DET

14 Control BGA AUX_MIC 7

5 VA_CS

VA_SPI_MI

to Call Processor L901 VSWITCH

2.8Vpp

This signal is from the BIC to the SMOC

15 D/A FS_AUD It is a timing signal at 8KHz and provides for frame synchronisation during speech transfer on

46 U982 6 VA_SPI_MO 5us / cm

20 Boost Mode Circuitry CR910 Non - Orderable Part the DSC bus.

AL LAYER - ORDERABLE SPARES TEST COMMANDS POWER UP DEBUG COMMON PROBLEMS

Part Part Part Part Part Part # press 2 sec. Enter Manual Test Mode Tie watchdog as shown in Signal Flow diagram, and supply power to radio: Customer complaints Special Note Part Part / Prefix Reason

Designator Description Number Designator Description Number 01 # Exit Manual Test Mode

- Check that there is B+ present at input to GCAP on pin 40. If not, could be problem with Battery Select Circuitry (Q906)

1. NO PWR UP SRAM U702 bad soldering / defective

07 # Mute Rx Audio Path 2. NO PWR UP EPROM U704 bad soldering / defective

Alert Alert 5009005J03 Q601 Power Transistor Charging 4809579E04

08 # Unmute Rx Audio Path - GCAP should then drive R275, L275 and VRef. If these are not present, could be a problem with GCAP itself. 3. TX PROBLEM ( PWR DWN) PA U301 defective

BT700 Connector Real Time Clock 0909888M01 Q602 Transistor Battery Feedback 4809939C05

09 # Mute Tx Audio Path - Verify collectors of regulators Q221 and Q222 are both around 2.75V. 4. PWR DWN CAPACITY C330 defective

CR607 Diode Charge Line 4809606E07 R602 Resistor I Sense 0680195M64 10 # Unmute Tx Audio Path 5. NO CHARGING RESISTOR R602 broken

- If ok, then check that the SMOC drives the Xtal Varactor Diode CR201 on the AFC line with a DC Voltage.

CR910 Diode Switched Supply 4809653F02 U500 SMOC IC 5199332C04 11xxxx # Program Main Local Osc. to Channelbb 6. TX / RX FEHLER GIF_SYN U220 defective

- If ok, then follow 13MHz path through GIF SYN & BIC and then to Call Processor and SMOC.

J500 Keyboard Connector 2809424M01 U703 BIC IC 5109962C11 12xx # Set Tx Power level to fixed valure 7. NO PWR UP GCAP U900 defective

19 # Display SW Version Number of Call Processor - If ok, then check chip enables from Eprom, and SRams at Test Points.

8. NO DISPLAY / NO PWR UP DISPLAY BOARD DISPLAY BOARD defective

J600 Connector-Extern 0909449B03 U900 GCAP 5109632D75

20 # Display SW Version Number of Modem - If ok, then verify Reset Line. 9. PX PROBLEM FILTER FL480 defective

J603 Connector Vibra 0909888M01 U980 Voice Annotation IC 5109152M07 22 # Display SW Version Number of Speech Coder 10. NO BATT CONTACT BACKHOUSING BACKHOUSING broken

J802 Connector Microphone 0909195E01 U982 Amlifier IC 5109731C03 25 # Set Continuous AGC

J803 Connector Speaker 0909888M04 SH11 Shield Call Processor 2609482M01 26xxxx # Set Continuous AFC

31x # Initiate Pseudo-Random Sequence with Midamble

J900

LS802

SIM Connector

Speaker

3909426M01

5009076E12

SH12

SH13

Shield GCAP

Shield SMOC

2609481M01

2609483M01

33xxxx #

36 #

Synchronize to BCH Carrier

Initiate Acoustic Loopback

REVISIONS

Europe Middle East & Africa Customer Services 13.04.99

Mic Microphone 5009536H15 SH14 Shield BIC / EEPROM 2609484M01 37 # Stop Test

LEVEL 3 COLOUR DIAGRAMS Rev. 1.1

Q501 Transistor TX_EN 4809607E05 45xxxx # Serving Cell Power Level

Dual Band ZAP

46 # Display Current Valure od AFC DAC

Colin Jack, Michael Hansen, Billy Jenkins Page 1 of 2

47x # Set Audio Volume

58 / xxxxxx # Display / Modify Security Code

59 / xxx # Display / Modify Lock Code

60 # Display IMEI

7100 # Display Error Code

Motorola Confidential Proprietary

You might also like

- Wiring Diagram Honda Fit - PGM-FI System PDFDocument1 pageWiring Diagram Honda Fit - PGM-FI System PDFJoshua Varona100% (1)

- VPDM Pin LayoutDocument1 pageVPDM Pin LayoutBernardo OlivaNo ratings yet

- The Hillman Group Key Catalog PDFDocument124 pagesThe Hillman Group Key Catalog PDFgyrfalcon50% (2)

- Sparrow - Creative Agency Powerpoint PresentationDocument124 pagesSparrow - Creative Agency Powerpoint PresentationjackaleenNo ratings yet

- Electrical System 793D Off-Highway Truck: Harness and Wire Electrical Schematic SymbolsDocument4 pagesElectrical System 793D Off-Highway Truck: Harness and Wire Electrical Schematic SymbolsJose luis ConsuegraNo ratings yet

- Motorola Ming A1200Document3 pagesMotorola Ming A1200bassrivastava100% (2)

- Motorola V3 1Document3 pagesMotorola V3 1Techno Max IT SolutionsNo ratings yet

- Level 3 Repair: 8-1. Block DiagramDocument24 pagesLevel 3 Repair: 8-1. Block Diagramdialla abdarahimNo ratings yet

- OLIMEXINO-STM32 SCH LatestDocument1 pageOLIMEXINO-STM32 SCH Latestnathantshama1No ratings yet

- Dokumen - Tips Samsung GT E1200 SchematicsDocument7 pagesDokumen - Tips Samsung GT E1200 SchematicsHogir DoskyNo ratings yet

- TC1221 BaseDocument2 pagesTC1221 Baseand roidNo ratings yet

- Dumariya Station 25 KV Ac Traction Station Working Rule DiagramDocument1 pageDumariya Station 25 KV Ac Traction Station Working Rule DiagramAbhishek SinghNo ratings yet

- Taae Rce 11 09 2022Document22 pagesTaae Rce 11 09 2022Orbenson TanNo ratings yet

- TroubleshootingDocument34 pagesTroubleshootingsabbarapinajaji2No ratings yet

- Algae Neptune: RX Mid Channels GSM: CH 62 - 947,4 MHZDocument2 pagesAlgae Neptune: RX Mid Channels GSM: CH 62 - 947,4 MHZaposticaa100% (1)

- 08 - GT S5222 Tshoo 7Document37 pages08 - GT S5222 Tshoo 7Nelson BoneNo ratings yet

- Renr8131-01 C12Document2 pagesRenr8131-01 C12ait mimouneNo ratings yet

- Air Bag SrsDocument1 pageAir Bag SrspeterrozenveldNo ratings yet

- Va2-Yu02-P1bay-145001 - Overall Protection and Metering Single Line Diagram - R1Document1 pageVa2-Yu02-P1bay-145001 - Overall Protection and Metering Single Line Diagram - R1Công TràNo ratings yet

- NGR Alarm Panel Drawing 623265Document2 pagesNGR Alarm Panel Drawing 623265Claudio GuevaraNo ratings yet

- Carvin C-1644 4 Bussmaster Audio 2002 SCHDocument1 pageCarvin C-1644 4 Bussmaster Audio 2002 SCHAndres GuerreroNo ratings yet

- ANT Block Diagram CurrentDocument1 pageANT Block Diagram CurrentGurinderjeet SinghNo ratings yet

- DLC3Document2 pagesDLC3Raul Garcia GuevaraNo ratings yet

- Schematic Diagram: 7-1 Circuit DescriptionDocument8 pagesSchematic Diagram: 7-1 Circuit Descriptionoppa BaruNo ratings yet

- Level 3 Repair: 8-1. Block DiagramDocument79 pagesLevel 3 Repair: 8-1. Block DiagramAli UnlockNo ratings yet

- Onkyo tx-sr876 SMDocument23 pagesOnkyo tx-sr876 SMMoto MottoNo ratings yet

- ProductChart A2-Web PDFDocument1 pageProductChart A2-Web PDFAllan NallaNo ratings yet

- Bilge System of Oil CarrierDocument1 pageBilge System of Oil CarrierArrijal PratamaNo ratings yet

- ME-1831 Service ManualDocument13 pagesME-1831 Service ManualmeahdiNo ratings yet

- Data Sheet MTI EN - 0Document2 pagesData Sheet MTI EN - 0lara2005No ratings yet

- Observation April 01, 2021 - 01Document2 pagesObservation April 01, 2021 - 01Abdul RahmanNo ratings yet

- Sti 510 PDFDocument1 pageSti 510 PDFPresli Joel Clemente SullcaNo ratings yet

- Planos de Grua CaterpillarDocument4 pagesPlanos de Grua CaterpillarMarco RodriguezNo ratings yet

- HCD-GTZ4 - GTZ5 Diagrama-20135Document11 pagesHCD-GTZ4 - GTZ5 Diagrama-20135vivian elizabeth hurtadoNo ratings yet

- 12AX7 Phono Tube Preamplifier User ManualDocument7 pages12AX7 Phono Tube Preamplifier User ManualmikelikespieNo ratings yet

- Darlington: Silicon NPN Triple Diffused Planar TransistorDocument2 pagesDarlington: Silicon NPN Triple Diffused Planar TransistorGilberto DiazNo ratings yet

- En.x Nucleo Iks02a1 SchematicDocument4 pagesEn.x Nucleo Iks02a1 SchematicIbrahim AkNo ratings yet

- Cat Dcs Sis ControllerDocument6 pagesCat Dcs Sis ControllerMechanical departmentNo ratings yet

- Transformer /175W Line Safety Line: MotorDocument1 pageTransformer /175W Line Safety Line: Motororo plataNo ratings yet

- 08 DRG - Protection SLD 220kV SarigamDocument1 page08 DRG - Protection SLD 220kV SarigamAmarjit Kulkarni100% (1)

- Sti 503Document1 pageSti 503Rene Mendoza100% (1)

- 1242 B2 ISMB200: No (S) - BEAM - B2 1Document1 page1242 B2 ISMB200: No (S) - BEAM - B2 1M. Azharuddin TamboliNo ratings yet

- Sti 503 Sitema Electeico Cascadia Dd16Document2 pagesSti 503 Sitema Electeico Cascadia Dd16jlrossi.tlcNo ratings yet

- SLD For CPP Metering SystemDocument1 pageSLD For CPP Metering SystemJagadeesh rNo ratings yet

- Senr1361 01Document2 pagesSenr1361 01Reinaldo Alonso Martinez CuellarNo ratings yet

- (Kas001043 - Inq - 2021 - 10 - 0016256) - Ewd Kick Sensor 716BDocument1 page(Kas001043 - Inq - 2021 - 10 - 0016256) - Ewd Kick Sensor 716BBYU OTOVLOGNo ratings yet

- ANT GSM850 RX Dcs/Pcs RX GSM900/W900 RX W2100 RX W1900 TX/RX GSM850/900 TX Dcs/Pcs TX W900 TX W2100 TXDocument7 pagesANT GSM850 RX Dcs/Pcs RX GSM900/W900 RX W2100 RX W1900 TX/RX GSM850/900 TX Dcs/Pcs TX W900 TX W2100 TXELECTRONICA TRUJILLONo ratings yet

- Twitter SLDDocument1 pageTwitter SLDMohamed ShafeyNo ratings yet

- 001 ASSEMBLY ModelDocument1 page001 ASSEMBLY ModelsanusiibrahimNo ratings yet

- In Out SEL 787Document1 pageIn Out SEL 787Tosikur RahmanNo ratings yet

- July 2020 UENR8299-05: Harness and Wire Electrical Schematic SymbolsDocument6 pagesJuly 2020 UENR8299-05: Harness and Wire Electrical Schematic SymbolsImtiaz AhmedNo ratings yet

- Gigabyte Gv-R67xtgaming Oc-12gd Rev 1.0Document42 pagesGigabyte Gv-R67xtgaming Oc-12gd Rev 1.0techgamebr85No ratings yet

- Vestax Vss PMC 280Document33 pagesVestax Vss PMC 280Diogo SilvaNo ratings yet

- Darlington: Silicon PNP Epitaxial Planar TransistorDocument1 pageDarlington: Silicon PNP Epitaxial Planar Transistormarcelo giussaniNo ratings yet

- Esq Manager Net 3+ USB (T0300101)Document1 pageEsq Manager Net 3+ USB (T0300101)RobertoBarbosaNo ratings yet

- STI 510VPDMPinLayoutDocument1 pageSTI 510VPDMPinLayoutManuel Solar100% (2)

- 8997 0846 00 DrawingsDocument41 pages8997 0846 00 Drawingsedduami montoya neyraNo ratings yet

- 3 Phase Electrical Circuit - 480 Volt & 230 Volt / 12V: Wire Color Code and GaugeDocument1 page3 Phase Electrical Circuit - 480 Volt & 230 Volt / 12V: Wire Color Code and GaugeYhonni IrwanNo ratings yet

- Motor StartingDocument1 pageMotor StartingMoazam AliNo ratings yet

- Parts Catalogue DCD 250Document23 pagesParts Catalogue DCD 250Quốc Viêtj HuỳnhNo ratings yet

- Instant Assessments for Data Tracking, Grade 2: MathFrom EverandInstant Assessments for Data Tracking, Grade 2: MathNo ratings yet

- PRDFlipflatKeyboard cd920930 A4 C L4 V1.0 PDFDocument2 pagesPRDFlipflatKeyboard cd920930 A4 C L4 V1.0 PDFGermano SthefanNo ratings yet

- Zap Analysis Overview: Motorola Confidential Proprietry InformationDocument53 pagesZap Analysis Overview: Motorola Confidential Proprietry InformationGermano SthefanNo ratings yet

- RP Zap A4 BW l3 VXXDocument30 pagesRP Zap A4 BW l3 VXXGermano SthefanNo ratings yet

- Product Description: GSM Zap and Zap C (Refresh)Document17 pagesProduct Description: GSM Zap and Zap C (Refresh)Germano SthefanNo ratings yet

- PRDFlipflatKeyboard Cd920930 A4 C L4 V1.0Document2 pagesPRDFlipflatKeyboard Cd920930 A4 C L4 V1.0Germano SthefanNo ratings yet

- TX VCO Tuning Voltage A C D E: Logic - GSM - Dcs GSM - Dcs GSM - Dcs Logic - GSM - DcsDocument1 pageTX VCO Tuning Voltage A C D E: Logic - GSM - Dcs GSM - Dcs GSM - Dcs Logic - GSM - DcsGermano SthefanNo ratings yet

- LG KT610 Service Manual PDFDocument234 pagesLG KT610 Service Manual PDFGermano SthefanNo ratings yet

- National Semiconductor-LM317T P+-DatasheetDocument13 pagesNational Semiconductor-LM317T P+-DatasheetGermano SthefanNo ratings yet

- De Grote Vakantie Muziek BingoDocument17 pagesDe Grote Vakantie Muziek BingoKoen BothNo ratings yet

- Uts English Grade 4Document5 pagesUts English Grade 4prasetyoeko19889No ratings yet

- (Assignment) Apple Inc, (Profile)Document15 pages(Assignment) Apple Inc, (Profile)SvS79% (24)

- RC Module - Tone Based QuestionsDocument19 pagesRC Module - Tone Based QuestionsRohit NayakNo ratings yet

- SteinbeckDocument4 pagesSteinbeckRosu Daniel Si MirelaNo ratings yet

- Don't Ask, Don't TellDocument9 pagesDon't Ask, Don't TellMarionNo ratings yet

- Science PR Ques 3 and 6Document2 pagesScience PR Ques 3 and 6Vyan Anand (Admn. No : 7366)No ratings yet

- App InventorDocument6 pagesApp InventorErik Martin Juarez AparicioNo ratings yet

- Veggie and Fruit Charts For Guinea PigsDocument4 pagesVeggie and Fruit Charts For Guinea Pigsg264906No ratings yet

- 2 The Business of Opera: Nicholas PayneDocument17 pages2 The Business of Opera: Nicholas PayneJilly CookeNo ratings yet

- Datos JeanDocument8 pagesDatos JeanJean Carlo GuarenasNo ratings yet

- Service Manual Tektronix TDS 500D TDS 600C TDS 700D TDS 714LDocument330 pagesService Manual Tektronix TDS 500D TDS 600C TDS 700D TDS 714Lrotex100% (1)

- The 4a'sDocument5 pagesThe 4a'sRisha BaconesNo ratings yet

- Tourism Task Force Final2Document62 pagesTourism Task Force Final2Hayat Ali Shaw100% (1)

- Akhree RashtaDocument15 pagesAkhree Rashtakumarkhiladi67No ratings yet

- Fallout: Project Brazil Development DocumentDocument12 pagesFallout: Project Brazil Development DocumentDanielson CageNo ratings yet

- Disassembly HPpro8000Document6 pagesDisassembly HPpro8000Denis Camacho50% (2)

- Pronunciation Worksheet Final - Ed: (T) (D) (/D) : //D/ Adds An Extra SyllableDocument2 pagesPronunciation Worksheet Final - Ed: (T) (D) (/D) : //D/ Adds An Extra SyllableSebastian castañedaNo ratings yet

- GFD 14 - Procedure in Drafting The Basic Patterns For Bodice, Sleeve, and SkirtDocument3 pagesGFD 14 - Procedure in Drafting The Basic Patterns For Bodice, Sleeve, and SkirtTrisha SaysonNo ratings yet

- Raag Darbari SongsDocument3 pagesRaag Darbari Songssubbaiah54No ratings yet

- Hidilyn DiazDocument3 pagesHidilyn DiazKen PedereNo ratings yet

- Motivate! 1 Test U4 StandardDocument6 pagesMotivate! 1 Test U4 StandardDragana VučkovićNo ratings yet

- Pinch 2002 PDFDocument23 pagesPinch 2002 PDFAbel CastroNo ratings yet

- Forms Dayof CoordinationDocument2 pagesForms Dayof CoordinationJacque Dee DuranNo ratings yet

- A Birthday Poem If Those I Loved Were LostDocument6 pagesA Birthday Poem If Those I Loved Were LostAira Dagus Maraña IINo ratings yet

- DAX Measures and Calculated Columns POWER BIDocument5 pagesDAX Measures and Calculated Columns POWER BIaiexplorer009No ratings yet

- Pakistani Diet PlanDocument4 pagesPakistani Diet Planmustafvi-927860% (1)

- Best Jason Statham Movies - Google SearchDocument1 pageBest Jason Statham Movies - Google SearchMuhammed RafelNo ratings yet