Professional Documents

Culture Documents

1 A, Low Quiescent Current, Low-Noise Voltage Regulator: Applications

1 A, Low Quiescent Current, Low-Noise Voltage Regulator: Applications

Uploaded by

Oscar HuertaCopyright:

Available Formats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 3G RBS 6000 Alarms and TroubleshootingDocument1,478 pages3G RBS 6000 Alarms and TroubleshootingDaveNo ratings yet

- Acer Aspire One AO756 Service Manual PDFDocument219 pagesAcer Aspire One AO756 Service Manual PDFCarlo100% (1)

- Marelli MF4 Toyota 101 EngDocument6 pagesMarelli MF4 Toyota 101 EngpepeladazoNo ratings yet

- Motorola W388: Getting Started GuideDocument58 pagesMotorola W388: Getting Started GuideyokonakagimaNo ratings yet

- New Generation Single-Board Telecoms Trainer For Advanced ExperimentsDocument8 pagesNew Generation Single-Board Telecoms Trainer For Advanced ExperimentsHuy DoNo ratings yet

- Radio Electronics November 1991 PDFDocument188 pagesRadio Electronics November 1991 PDFlivslx100% (1)

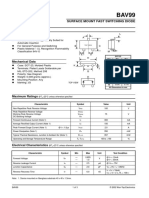

- Features: Surface Mount Fast Switching DiodeDocument4 pagesFeatures: Surface Mount Fast Switching DiodeDe faNo ratings yet

- POE Switches User ManualDocument1 pagePOE Switches User ManualFer DesignerNo ratings yet

- Update Instructions For The MMI HighDocument28 pagesUpdate Instructions For The MMI Highmadalinc1No ratings yet

- Relay Basics: By: Andrew KrauseDocument4 pagesRelay Basics: By: Andrew Krauselavar_wrightNo ratings yet

- SVP309 SIP IP Phone User Manual: Stephen Technologies Co.,Limited All Rights ReservedDocument49 pagesSVP309 SIP IP Phone User Manual: Stephen Technologies Co.,Limited All Rights ReservedanycikaNo ratings yet

- Black Star Meteor 600 Frequency Counter Service ManualDocument18 pagesBlack Star Meteor 600 Frequency Counter Service Manualbill1068No ratings yet

- I Sem PDFDocument324 pagesI Sem PDFRahul AvhadNo ratings yet

- 3102319-En R004 EST Life Safety Systems UL 2572 Application GuideDocument36 pages3102319-En R004 EST Life Safety Systems UL 2572 Application GuideMoises ReyesNo ratings yet

- Iot Based Smart Charger: An Esp8266 Based Automatic ChargerDocument6 pagesIot Based Smart Charger: An Esp8266 Based Automatic Chargerrock starNo ratings yet

- PHILIPS Service ManualDocument161 pagesPHILIPS Service Manualpandorabox2012No ratings yet

- Transmission ModesDocument5 pagesTransmission ModesMuneeza AlizaNo ratings yet

- UF6450 Spec SheetDocument1 pageUF6450 Spec SheetAEyermanNo ratings yet

- Panasonic TH42PX75U Chassis GP10DHU TV Plasma Service ManualDocument540 pagesPanasonic TH42PX75U Chassis GP10DHU TV Plasma Service ManualromarloNo ratings yet

- BARC InterviewDocument9 pagesBARC InterviewShounakDutta100% (1)

- Cylinder Pressure SensorDocument2 pagesCylinder Pressure SensorDiamante HernandezNo ratings yet

- Lec 2.4 Network Hardware & MediaDocument16 pagesLec 2.4 Network Hardware & MediaSuman JyotiNo ratings yet

- ManualDocument11 pagesManualKos Intel DooNo ratings yet

- Product Catalogue: June 2014Document105 pagesProduct Catalogue: June 2014Adrian TodeaNo ratings yet

- Lab ManualDocument8 pagesLab ManualDavinder KakkarNo ratings yet

- DF4GDataFill AC5935 San Jose 20230614 B2 B7 S1 S2Document36 pagesDF4GDataFill AC5935 San Jose 20230614 B2 B7 S1 S2Frank aliaga berrocalNo ratings yet

- Design of A Controlled Solid State Device For Fault Current Limitation and Arc Flash SuppressionDocument6 pagesDesign of A Controlled Solid State Device For Fault Current Limitation and Arc Flash SuppressionAnwar HossanNo ratings yet

- DCC MicroprojectDocument10 pagesDCC Microprojectomahale751No ratings yet

- NI Serial Hardware Specifications PDFDocument62 pagesNI Serial Hardware Specifications PDFKmilo RamirezNo ratings yet

1 A, Low Quiescent Current, Low-Noise Voltage Regulator: Applications

1 A, Low Quiescent Current, Low-Noise Voltage Regulator: Applications

Uploaded by

Oscar HuertaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1 A, Low Quiescent Current, Low-Noise Voltage Regulator: Applications

1 A, Low Quiescent Current, Low-Noise Voltage Regulator: Applications

Uploaded by

Oscar HuertaCopyright:

Available Formats

LD39100

1 A, low quiescent current, low-noise voltage regulator

Datasheet - production data

Applications

Printers

Personal digital assistants (PDAs)

Cordless phones

Consumer applications

DFN6 (3x3 mm)

Description

The LD39100 provides 1 A maximum current with

an input voltage range from 1.5 V to 5.5 V and a

Features typical dropout voltage of 200 mV. The device is

Input voltage from 1.5 to 5.5 V stable with ceramic capacitors on the input and

Ultra low-dropout voltage (200 mV typ. at 1 output. The ultra low drop voltage, low quiescent

A load) current and low-noise features make it suitable

Very low quiescent current (20 µA typ. at no for low power battery-powered applications.

load, 200 µA typ. at 1 A load, 1 µA max. in Power supply rejection is 70 dB at low frequency

off mode) and starts to roll off at 10 kHz. Enable logic

Very low-noise with no bypass capacitor (30 control function puts the LD39100 in shutdown

µ VRMS at VOUT = 0.8 V) mode, allowing a total current consumption lower

Output voltage tolerance: ± 2.0% @ 25 °C than 1 µA. The device also includes short-circuit

1 A guaranteed output current constant current limiting and thermal protection.

Wide range of output voltages available on Table 1: Device summary

request: 0.8 V to 4.5 V with 100 mV step and Order code Output voltage

adjustable from 0.8 V

Logic-controlled electronic shutdown LD39100PUR Adj. from 0.8 V

Stable with ceramic capacitors COUT = 1 µF LD39100PU12R 1.2 V

Internal current and thermal limit

LD39100PU25R 2.5 v

DFN6 (3x3 mm) package

Temperature range: - 40 °C to 125 °C LD39100PU30R 3.0 V

September 2015 DocID15676 Rev 5 1/25

This is information on a product in full production. www.st.com

Contents LD39100

Contents

1 Circuit schematics........................................................................... 5

2 Pin configuration ............................................................................. 6

3 Maximum ratings ............................................................................. 7

4 Electrical characteristics ................................................................ 8

5 Typical performance characteristics ........................................... 11

6 Application information ................................................................ 16

6.1 Power dissipation ............................................................................ 17

6.2 Enable function ............................................................................... 18

6.3 Power Good function ....................................................................... 18

7 Package information ..................................................................... 19

7.1 DFN6 (3x3 mm) package information ............................................. 20

7.2 DFN6 (3x3 mm) packing information ............................................... 22

8 Revision history ............................................................................ 24

2/25 DocID15676 Rev 5

LD39100 List of tables

List of tables

Table 1: Device summary ........................................................................................................................... 1

Table 2: Pin description .............................................................................................................................. 6

Table 3: Absolute maximum ratings ........................................................................................................... 7

Table 4: Thermal data ................................................................................................................................. 7

Table 5: ESD performance ......................................................................................................................... 7

Table 6: LD39100 electrical characteristics (adjustable version) ............................................................... 8

Table 7: LD39100 electrical characteristics (fixed version) ........................................................................ 9

Table 8: DFN6 (3x3 mm) mechanical data ............................................................................................... 21

Table 9: DFN6 (3x3 mm) tape and reel mechanical data ......................................................................... 23

Table 10: Document revision history ........................................................................................................ 24

DocID15676 Rev 5 3/25

List of figures LD39100

List of figures

Figure 1: LD39100 schematic diagram (adjustable version) ...................................................................... 5

Figure 2: LD39100 schematic diagram (fixed version) ............................................................................... 5

Figure 3: Pin connection (top view) ............................................................................................................ 6

Figure 4: VADJ accuracy ............................................................................................................................ 11

Figure 5: VOUT accuracy ............................................................................................................................ 11

Figure 6: Dropout voltage vs. temperature (VOUT = 2.5 V) ........................................................................ 11

Figure 7: Dropout voltage vs. temperature (VOUT = 1.5 V) ........................................................................ 11

Figure 8: Dropout voltage vs. output current ............................................................................................ 11

Figure 9: Short-circuit current vs. drop voltage ......................................................................................... 11

Figure 10: Output voltage vs. input voltage (VOUT = 0.8 V) ....................................................................... 12

Figure 11: Output voltage vs. input voltage (VOUT = 2.5 V) ....................................................................... 12

Figure 12: Quiescent current vs. temperature .......................................................................................... 12

Figure 13: VIN input current in off mode vs. temperature......................................................................... 12

Figure 14: Load regulation ........................................................................................................................ 12

Figure 15: Line regulation VOUT = 0.8 V .................................................................................................... 12

Figure 16: Line regulation VOUT = 2.5 V .................................................................................................... 13

Figure 17: Supply voltage rejection vs. temperature (V OUT = 0.8 V) ......................................................... 13

Figure 18: Supply voltage rejection vs. temperature (V OUT = 2.5 V) ......................................................... 13

Figure 19: Supply voltage rejection vs. frequency (VOUT = 0.8 V) ............................................................ 13

Figure 20: Supply voltage rejection vs. frequency (VOUT = 2.5 V) ............................................................ 13

Figure 21: Output noise voltage vs. frequency ......................................................................................... 13

Figure 22: Enable voltage vs. temperature ............................................................................................... 14

Figure 23: Load transient (IOUT = from 10 mA to 1 A) ............................................................................... 14

Figure 24: Load transient (VOUT = 0.8 V)................................................................................................... 14

Figure 25: Load transient (VOUT = 2.5 V)................................................................................................... 14

Figure 26: Load transient (IOUT = from 100 mA to 1 A) ............................................................................. 14

Figure 27: Line regulation transient .......................................................................................................... 14

Figure 28: Start-up transient ..................................................................................................................... 15

Figure 29: Enable transient ....................................................................................................................... 15

Figure 30: ESR required for stability with (VOUT = 0.8 V) .......................................................................... 15

Figure 31: ESR required for stability with (VOUT = 2.5 V) .......................................................................... 15

Figure 32: Typical application circuit for fixed output version ................................................................... 16

Figure 33: Typical application circuit for adjustable version ..................................................................... 17

Figure 34: Power dissipation vs. ambient temperature ............................................................................ 18

Figure 35: DFN6 (3x3 mm) package outline ............................................................................................. 20

Figure 36: DFN6 (3x3 mm) recommended footprint ................................................................................. 21

Figure 37: DFN6 (3x3 mm) tape outline ................................................................................................... 22

Figure 38: DFN6 (3x3 mm) reel outline .................................................................................................... 23

4/25 DocID15676 Rev 5

LD39100 Circuit schematics

1 Circuit schematics

Figure 1: LD39100 schematic diagram (adjustable version)

IN Power-good PG

signal

IN

BandGap

reference

Current

OpAmp

limit

OUT

Thermal

protection

ADJ

EN Internal

enable

GND

GIPD010920151332MT

Figure 2: LD39100 schematic diagram (fixed version)

IN Power-good PG

signal

IN

BandGap

reference

Current

OpAmp

limit

OUT

Thermal

protection

R1

NC

R2

EN Internal

enable

GND

GIPD010920151333MT

DocID15676 Rev 5 5/25

Pin configuration LD39100

2 Pin configuration

Figure 3: Pin connection (top view)

EN 1 6 VIN EN 1 6 VIN

GND 2 5 NC GND 2 5 ADJ

PG 3 4 VOUT PG 3 4 VOUT

LD39100 (fixed version) LD39100 (adjustable version)

GIPD010920151334MT

Table 2: Pin description

Pin

Symbol LD39100 LD39100 Function

(adjustable version) (fixed version)

Enable pin logic input: low = shutdown,

EN 1 1

high = active

GND 2 2 Common ground

PG 3 3 Power Good

VOUT 4 4 Output voltage

ADJ 5 - Adjust pin

VIN 6 6 LDO input voltage

NC - 5 Not connected

GND Exposed pad Exposed pad has to be connected to GND

6/25 DocID15676 Rev 5

LD39100 Maximum ratings

3 Maximum ratings

Table 3: Absolute maximum ratings

Symbol Parameter Value Unit

VIN DC input voltage -0.3 to 7 V

-0.3 to VIN + 0.3

VOUT DC output voltage V

(7 V max.)

-0.3 to VIN + 0.3

EN Enable pin V

(7 V max.)

PG Power Good pin -0.3 to 7 V

ADJ Adjust pin 4 V

IOUT Output current Internally limited

PD Power dissipation Internally limited

TSTG Storage temperature range - 65 to 150 °C

TOP Operating junction temperature range - 40 to 125 °C

Absolute maximum ratings are those values beyond which damage to the device

may occur. Functional operation under these conditions is not implied. All values

are referred to GND.

Table 4: Thermal data

Symbol Parameter Value Unit

RthJA Thermal resistance junction-ambient 55 °C/W

RthJC Thermal resistance junction-case 10 °C/W

Table 5: ESD performance

Symbol Parameter Test conditions Value Unit

HBM 4 kV

ESD ESD protection voltage

MM 0.4 kV

DocID15676 Rev 5 7/25

Electrical characteristics LD39100

4 Electrical characteristics

TJ = 25 °C, VIN = 1.8 V, CIN = COUT = 1 µF, IOUT = 100 mA, VEN = VIN, unless otherwise

specified.

Table 6: LD39100 electrical characteristics (adjustable version)

Symbol Parameter Test conditions Min. Typ. Max. Unit

Operating input

VIN 1.5 5.5 V

voltage

IOUT = 10 mA, TJ = 25 °C 784 800 816

VADJ VADJ accuracy mV

IOUT = 10 mA, -40 °C < TJ < 125 °C 776 800 824

IADJ Adjust pin current 1 µA

VOUT + 1 V £ VIN £ 5.5 V, IOUT = 100

DVOUT Static line regulation 0.01 %/V

mA

DVIN = 500mV, IOUT = 100 mA,

10

Transient line tR = 5 µs

DVOUT mVpp

regulation (1) DVIN = 500 mV, IOUT = 100 mA,

10

tF = 5 µs

Static load

DVOUT IOUT = 10 mA to 1 A 0.002 %/mA

regulation

Transient load IOUT = 10 mA to 1 A, tR = 5 µs 40

DVOUT mVpp

regulation (1) IOUT = 1 A to 10 mA, tF = 5µs 40

IOUT = 1 A, VO fixed to 1.5 V

VDROP Dropout voltage (2) 200 400 mV

-40 °C < TJ < 125 °C

Output noise 10 Hz to 100 kHz, IOUT = 100 mA,

eN 30 µVRMS

voltage VOUT = 0.8 V

VIN = 1.8 V+/-VRIPPLE

VRIPPLE = 0.25 V, frequency = 1 70

Supply voltage kHz IOUT = 10 mA

SVR dB

rejection VO = 0.8 V VIN = 1.8 V+/-VRIPPLE

VRIPPLE = 0.25, frequency = 10 kHz 65

IOUT = 100 mA

IOUT = 0 mA 20

IOUT = 0 mA, -40 °C < TJ < 125 °C 50

IOUT = 0 to 1 A 200

IQ Quiescent current IOUT = 0 to 1 A, µA

300

-40 °C < TJ < 125 °C

VIN input current in off mode:

0.001 1

VEN = GND (3)

0.92*

Rising edge

Power good output VOUT

V

threshold 0.8*

PG Falling edge

VOUT

Power good output

Isink = 6 mA open drain output 0.4 V

voltage low

8/25 DocID15676 Rev 5

LD39100 Electrical characteristics

Symbol Parameter Test conditions Min. Typ. Max. Unit

ISC Short-circuit current RL= 0 1.5 A

Enable input logic

0.4 V

low VIN = 1.5 V to 5.5 V,

VEN

Enable input logic -40 °C < TJ< 125 °C

0.9 V

high

Enable pin input

IEN VEN = VIN 0.1 100 nA

current

tON Turn-on time (4) 30 µs

Thermal shutdown 160

TSHDN °C

Hysteresis 20

Capacitance (see typical

COUT Output capacitor performance characteristics for 1 22 µF

stability)

Notes:

(1)All transient values are guaranteed by design, not tested in production.

(2)Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal

value. This specification does not apply to output voltages below 1.5 V.

(3)PG pin floating.

(4)Turn-on time is time measured between the enable input just exceeding VEN high value and the output voltage

just reaching 95% of its nominal value.

TJ = 25 °C, VIN = VOUT(NOM) + 1 V, CIN = COUT = 1 µF, IOUT = 100 mA, VEN = VIN, unless

otherwise specified.

Table 7: LD39100 electrical characteristics (fixed version)

Symbol Parameter Test conditions Min. Typ. Max. Unit

Operating input

VI 1.5 5.5 V

voltage

VOUT >1.5 V, IOUT = 10 mA,

-2.0 2.0

TJ = 25 °C

%

VOUT > 1.5 V, IOUT = 10 mA,

-3.0 3.0

VOUT VOUT accuracy -40 °C < TJ < 125 °C

VOUT ≤ 1.5 V, IOUT = 10 mA ±20

VOUT ≤ 1.5 V, IOUT = 10 mA, mV

±30

-40 °C < TJ < 125 °C

Static line VOUT + 1 V ≤ VIN ≤ 5.5 V,

DVOUT 0.01 %/V

regulation IOUT = 100 mA

DVIN = 500 mV, IOUT = 100 mA,

10

Transient line tR = 5 µs

DVOUT mVpp

regulation (1) DVIN = 500 mV, IOUT = 100 mA,

10

tF = 5 µs

Static load

DVOUT IOUT = 10 mA to 1 A 0.002 %/mA

regulation

Transient load IOUT = 10 mA to 1 A, tR = 5 µs 40

DVOUT mVpp

regulation (1) IOUT = 1 A to 10 mA, tF = 5 µs 40

DocID15676 Rev 5 9/25

Electrical characteristics LD39100

Symbol Parameter Test conditions Min. Typ. Max. Unit

IOUT = 1 A, VOUT > 1.5 V,

VDROP Dropout voltage (2) 200 400 mV

-40 °C < TJ < 125 °C

Output noise 10 Hz to 100 kHz, IOUT = 100 mA,

eN 85 µVRMS

voltage VOUT = 2.5 V

VIN = VOUT(NOM)+0.5 V+/-VRIPPLE

VRIPPLE = 0.1 V, frequency = 1 kHz 65

Supply voltage IOUT = 10 mA

SVR rejection dB

VOUT=1.5V VIN = VOUT(NOM)+0.5 V+/-VRIPPLE

VRIPPLE = 0.1 V, frequency = 10 kHz 62

IOUT = 100 mA

IOUT = 0 mA 20

IOUT = 0 mA, -40 °C < TJ < 125 °C 50

IOUT = 0 to 1 A 200

IQ Quiescent current µA

IOUT = 0 to 1 A -40 °C < TJ < 125 °C 300

VIN input current in OFF mode:

0.001 1

VEN = GND (3)

0.92*

Rising edge

Power good VOUT

V

output threshold 0.8*

PG Falling edge

VOUT

Power good

Isink = 6 mA open drain output 0.4 V

output voltage low

Short-circuit

ISC RL = 0 1.5 A

current

Enable input logic

0.4 V

low VIN = 1.5 V to 5.5 V,

VEN

Enable input logic -40 °C < TJ< 125 °C

0.9 V

high

Enable pin input

IEN VEN = VIN 0.1 100 nA

current

TON Turn-on time (4) 30 µs

Thermal shutdown 160

TSHDN °C

Hysteresis 20

Capacitance (see typical

COUT Output capacitor performance characteristics for 1 22 µF

stability)

Notes:

(1)All transient values are guaranteed by design, not tested in production.

(2)Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal

value. This specification does not apply to output voltages below 1.5 V.

(3)

PG pin floating.

(4)Turn-on time is time measured between the enable input just exceeding VEN high value and the output voltage

just reaching 95% of its nominal value.

10/25 DocID15676 Rev 5

LD39100 Typical performance characteristics

5 Typical performance characteristics

CIN = COUT = 1 µF

Figure 4: VADJ accuracy Figure 5: VOUT accuracy

0.86 2.56

VIN

VIN= =1.8

1.8V,V,VEN

VEN== VVIN,, IIOUT== 10

10mA

mA VINV=IN =3.5

3.5V ,VV, EN

VEN==VVININ, ,I OUT

IOUT = 10 mA

0.84 2.54

0.82 2.52

VOUT [V]

V ADJ [V ]

0.8 2.5

0.78 2.48

0.76 2.46

0.74 2.44

-50 -25 0 25 50 75 100 125 150 --50 --25 0 25 50 75 100 125 150

T [°C ] T [°C]

GIPD020920151100MT GIPD020920151101MT

Figure 6: Dropout voltage vs. temperature Figure 7: Dropout voltage vs. temperature

(VOUT = 2.5 V) (VOUT = 1.5 V)

400

VEVNE NtotoVINV,INV, OVUOTU@

T

@1.5

1.5V,V,IO IU T = 1 A

350

300

D r o p o u t [m V ]

250

200

150

100

50

0

-50 -25 0 25 50 75 100 125 150

T [°C]

GIPD020920151102MT GIPD020920151103MT

Figure 9: Short-circuit current vs. drop

Figure 8: Dropout voltage vs. output current

voltage

0 .2 5

3.5

V O U T @ 1 .5 V V E N to V I N VIN from0 to 5.5 V, VEN to VIN, VOUT =0.8 V

0 .2 3

V O U T = 2 .5 V

2.5

Dropout [V]

0 .1 5

2 125 °C

I SC [A]

85 °C

0 .1 1.5 55 °C

25 °C

0 .0 5 1

0 °C

0.5 -25 °C

0 -40 °C

0 200 400 600 800 1 0 00 1200 0

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 6

I O U T [m A ]

Vdrop [V]

GIPD020920151104MT

GIPD020920151105MT

DocID15676 Rev 5 11/25

Typical performance characteristics LD39100

Figure 11: Output voltage vs. input voltage

Figure 10: Output voltage vs. input voltage

(VOUT = 2.5 V)

(VOUT = 0.8 V)

3

1.2

VIN from 0 to 5V, VEN to VIN, VOUT = 2.5 V, IOUT = 1A

VIN from 0 to 5.5 V, VEN to VIN, VOUT = 0.8 V, IOUT = 1 A

1 2.5

125°C

0.8 2

85°C

V O UT [V]

VOUT [V]

125°C

0.6 85°C 1.5 55°C

55°C 25°C

0.4 25°C 1 0°C

0°C

0.2 -25°C

-25°C 0.5

-40°C -40°C

0 0

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 6 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 6

VIN [V]

VIN [V]

GIPD020920151106MT GIPD020920151107MT

Figure 13: VIN input current in off mode vs.

Figure 12: Quiescent current vs. temperature temperature

140

0 .6

120 V IN = 3.5 V , V E N to G N D , V O U T = 2.5 V

0 .5

100

0 .4

Iq [µA]

80 No Load Iq [µA]

IOUT = 1 A 0 .3

60

VIN = 1.8 V, VEN to VIN, VOUT = 2.5 V

40 0 .2

20

0 .1

0

-50 -25 0 25 50 75 100 125 150 0

-5 0 -2 5 0 25 50 75 10 0 125 15 0

T [°C]

T [°C ]

GIPD020920151108MT

GIPD020920151109MT

Figure 14: Load regulation Figure 15: Line regulation VOUT = 0.8 V

0.015 0.04

V IN = from 1.8 V to 5.5 V, IOUT = 100 m A, V EN = V IN , V OUT = 0.8 V

V IN = 3.5 V, IOUT = from 10 mA to 1 A, V EN=V IN, V OUT = 2.5 V

0.03

0.01

0.02

Load [%/mA]

0.005

Line [%/V]

0.01

0 0

-0.005

-0.01

-0.02

-0.01

-0.03

-0.015 -0.04

-50 -25 0 25 50 75 100 125 150 -50 -25 0 25 50 75 100 125 150

T [°C] T [°C]

GIPD020920151110MT

GIPD020920151111MT

12/25 DocID15676 Rev 5

LD39100 Typical performance characteristics

Figure 17: Supply voltage rejection vs.

Figure 16: Line regulation VOUT = 2.5 V

temperature (VOUT = 0.8 V)

0.04

V IN = f ro m 3 .5 V to 5 .5 V , I O U T = 1 0 0 m A , V E N = V IN , V O U T = 2 .5 V 100

0.03 V IN from 1.7 V to 1.9 V, V EN to V IN, V OUT = 0.8 V

0.02

Line [%/V] 80

0.01

SV R [dB]

60

0

-0.01 40

-0.02 Freq.10 kHz, IOUT = 100 mA

-0.03 20

Freq.1 kHz, IOUT = 10 mA

-0.04

-50 -25 0 25 50 75 100 125 150 0

-50 -25 0 25 50 75 100 125 150

T [°C]

T [°C]

GIPD020920151112MT

GIPD020920151113MT

Figure 18: Supply voltage rejection vs. Figure 19: Supply voltage rejection vs.

temperature (VOUT = 2.5 V) frequency (VOUT = 0.8 V)

100 100

V IN from 2.9 V to 3.1 V, V EN to V IN, V OUT = 2.5 V VIN from 1.55 V to 2.05 V, VEN to VIN, VOUT = 0.8 V IOUT = 10 mA

80 80 IOUT = 100 mA

SVR [dB]

60

SVR [dB]

60

40 40

Freq. = 10 kHz, IOUT = 100 mA

20 20

Freq. = 1 kHz, IOUT = 10 mA

0 0

-50 -25 0 25 50 75 100 125 150 0 10 20 30 40 50 60 70 80 90 100 110

T [°C] Freq [kHz]

GIPD020920151114MT GIPD020920151115MT

Figure 20: Supply voltage rejection vs. Figure 21: Output noise voltage vs.

frequency (VOUT = 2.5 V) frequency

100 2 .5

V IN from 2.9 V to 3.1 V, V EN to V IN, V OUT = 2.5 V

90 IOUT = 10 mA A P - IO U T = 10 0 m A

80 IOUT = 100 mA 2 .0 A P - IO U T = 10 mA

eN [µV/SQRT(Hz)]

70 A P - IO U T = 1m A

SVR [dB]

60 1 .5 A P - IO U T = 0 A

50

40 1 .0

30

20 0 .5

10

0 0 .0

0 10 20 30 40 50 60 70 80 90 100 110 1.E+01 1.E+02 1.E+03 1.E+04 1.E+05

f [Hz]

Freq [kHz]

V IN = 1.8 V, V O U T = 0.8 V, V E N = V IN

GIPD020920151116MT GIPD020920151117MT

DocID15676 Rev 5 13/25

Typical performance characteristics LD39100

Figure 23: Load transient (IOUT = from 10 mA

Figure 22: Enable voltage vs. temperature to 1 A)

1 VIN = 5.5 V IOUT = 100 mA, VOUT = 0.8 V

0.9 High

0.8 Low VO UT

0.7

0.6

V E N [V]

0.5

0.4

0.3

0.2 IO U T

0.1

0

-50 -25 0 25 50 75 100 125 150

T [°C]

VEN= VIN=3.5V, VOUT=0.8V, IOUT= from10mA to 1A,

GIPD020920151118MT tR= tF =5 µs

GIPD02092015 1119MT

Figure 25: Load transient (VOUT = 2.5 V)

Figure 24: Load transient (VOUT = 0.8 V)

VOUT VOUT

IOUT

IOUT

VEN= VIN=3.5V, VOUT=0.8V, IOUT= from100 mA to 1A,

tR= tF =5 µs VEN= VIN=3.5V, VOUT=2.5V, IOUT= from10 mA to 1A,

GIPD02092015 1120MT tR= tF =5 µs

GIPD02092015 1121MT

Figure 26: Load transient (IOUT = from 100 Figure 27: Line regulation transient

mA to 1 A)

VIN

VO U T

VOUT

IO U T

VEN= VIN=3.5V, VOUT=2.5V, IOUT= from100 mA to 1A, VEN= VIN =1.8 V to 2.3 V, VOUT = 0.8V, IOUT=100 mA,

tR= tF =5 µs tR = tF = 5 µs

GIPD02092015 1122MT GIPD040920151016M T

14/25 DocID15676 Rev 5

LD39100 Typical performance characteristics

Figure 29: Enable transient

Figure 28: Start-up transient

VIN VEN

VOUT

VOUT

VEN= VIN= from0.8 V, VOUT=0.8 V, IOUT = 100 mA

VEN= 0 to 2 V, VOUT=0.8V, VIN = 3.5 V, IOUT = 100mA,

GIPD040920151220M T tR = 5 µs

GIPD040920151221M T

Figure 30: ESR required for stability with Figure 31: ESR required for stability with

ceramic capacitors (VOUT = 0.8 V) ceramic capacitors (VOUT = 2.5 V)

0.25

0.25

0.2 UNSTABLEZONE

]

0.2 UNSTABLEZONE

E S R @ 100 k H z [o h m ]

E S R @ 100 k H z [

0.15

0.15

0.1

0.1

STABLEZONE STABLEZONE

0.05

0.05

0 0

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22

COUT [µF] (nominal value) COUT [µF](nominal value)

VIN =VEN =from1.5V to5.5V, VOUT =0.8V, IOUT =from1 VIN =VEN =from3.5Vto5.5V, VOUT =2.5V, IOUT =from1

mAto1A mAto1A

GIPD040920151222M T GIPD040920151223M T

DocID15676 Rev 5 15/25

Application information LD39100

6 Application information

The LD39100 is an ultra low-dropout linear regulator. It provides up to 1 A with a low 200

mV dropout. The input voltage range is from 1.5 V to 5.5 V. The device is available in fixed

and adjustable output versions.

The regulator is equipped with internal protection circuitry, such as short-circuit current

limiting and thermal protection.

The regulator is stable with ceramic capacitors on the input and the output. The expected

values of the input and output ceramic capacitors are from 1 µF to 22 µF with 1 µF typical.

The input capacitor has to be connected within 1 cm from VIN terminal. The output

capacitor has also to be connected within 1 cm from output pin. There isn’t any upper limit

to the value of the input capacitor.

not found and not found illustrate the typical application schematics:

Figure 32: Typical application circuit for fixed output version

VIN

IN

6 3

V IN PG

PG

IN

VOU

OU T

1 4

EN

EN LD39100

LD V OU

OUT

OFF ON

CCIN

IN 5

NC

NC CCOUT

G ND

GN

2

GIPD040920151351MT

16/25 DocID15676 Rev 5

LD39100 Application information

Figure 33: Typical application circuit for adjustable version

VIN

IN

6 3

VIN

IN

PG

PG

VOUT

O

1 LD3

LD391

9100

00 4

EN

EN VOU

O T T U

O

OFF ON

O N R1

C IN

IN 5 C

ADJ

AD J O

OUT

GND GN

2

R2

GIPD040920151352MT

Regarding to the adjustable version, the output voltage can be adjusted from 0.8 V up to

the input voltage, minus PMOS voltage drop across (dropout voltage), by connecting a

resistor divider between ADJ pin and the output, thus allowing remote voltage sensing.

The resistor divider should be selected as follows:

Equation 1

VOUT = VADJ (1 + R1 / R2) with VADJ = 0.8 V (typ.)

Resistors should be used with values in the range from 10 kΩ to 50 kΩ. Lower values can

also be suitable, but they increase current consumption.

6.1 Power dissipation

An internal thermal feedback loop disables the output voltage if the die temperature rises to

approximately 160 °C. This feature protects the device from excessive temperature and

allows the user to push the limits of the power handling capability of a given circuit board

without the risk of damaging the device.

A good PC board layout should be used to maximize power dissipation. The thermal path

for the heat generated by the device is from the die to the copper lead frame through the

package leads and exposed pad to the PC board copper. The PC board copper acts as a

heatsink. The footprint copper pads should be as wide as possible to spread and dissipate

the heat to the surrounding ambient. Feed-through vias to the inner or backside copper

layers are also useful to improve the overall thermal performance of the device.

The device power dissipation depends on the input voltage, output voltage and output

current, and is given by:

Equation 2

PD = (VIN -VOUT) IOUT

Junction temperature of the device is:

DocID15676 Rev 5 17/25

Application information LD39100

Equation 3

TJ_MAX = TA + RthJA x PD

where:

TJ_MAX is the maximum junction of the die,125 °C

TA is the ambient temperature

RthJA is the thermal resistance junction-to-ambient

Figure 34: Power dissipation vs. ambient temperature

3.5

3

2.5

PD [W]

2

1.5

1

0.5

0

-50 -30 -10 10 30 50 70 90 110 130

TA [°C]

GIPD040920151415MT

6.2 Enable function

The LD39100 features the enable function. When EN voltage is higher than 2 V, the device

is ON, and if it is lower than 0.8 V, the device is OFF. In shutdown mode, consumption is

lower than 1 µA.

EN pin has not an internal pull-up, so it cannot be left floating if it is not used.

6.3 Power Good function

Most applications require a flag showing that the output voltage is in the correct range.

Power Good threshold depends on the adjust voltage. When it is higher than 0.92*V ADJ,

Power Good (PG) pin goes to high impedance. If it is below 0.80*VADJ PG pin goes to low

impedance. If the device works well, Power Good pin is at high impedance. If the output

voltage is fixed using an external or internal resistor divider, Power Good threshold is

0.92*VOUT.

Power Good function requires an external pull-up resistor, which has to be connected

between PG pin and VIN or VOUT. PG pin typical current capability is up to 6 mA. A pull-up

resistor for PG should be in the range from 100 kΩ to 1 MΩ. If Power Good function is not

used, PG pin has to remain floating.

18/25 DocID15676 Rev 5

LD39100 Package information

7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK ®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

DocID15676 Rev 5 19/25

Package information LD39100

7.1 DFN6 (3x3 mm) package information

Figure 35: DFN6 (3x3 mm) package outline

20/25 DocID15676 Rev 5

LD39100 Package information

Table 8: DFN6 (3x3 mm) mechanical data

mm

Dim.

Min. Typ. Max.

A 0.80 1

A1 0 0.02 0.05

A3 0.20

b 0.23 0.45

D 2.90 3 3.10

D2 2.23 2.50

E 2.90 3 3.10

E2 1.50 1.75

e 0.95

L 0.30 0.40 0.50

Figure 36: DFN6 (3x3 mm) recommended footprint

DocID15676 Rev 5 21/25

Package information LD39100

7.2 DFN6 (3x3 mm) packing information

Figure 37: DFN6 (3x3 mm) tape outline

22/25 DocID15676 Rev 5

LD39100 Package information

Figure 38: DFN6 (3x3 mm) reel outline

Table 9: DFN6 (3x3 mm) tape and reel mechanical data

mm

Dim.

Min. Typ. Max.

A0 3.20 3.30 3.40

B0 3.20 3.30 3.40

K0 1 1.10 1.20

DocID15676 Rev 5 23/25

Revision history LD39100

8 Revision history

Table 10: Document revision history

Date Revision Changes

29-Jul-2009 1 Initial release.

16-Apr-2010 2 Modified Figure 8 on page 9.

11-Oct-2011 3 Document status promoted from preliminary data to datasheet.

Part numbers LD39100xx, LD39100xx12 and LD39100xx25 changed

to LD39100.

Updated Table 1: Device summary .

Updated the description in cover page Section 1: "Circuit schematics",

Section 2: "Pin configuration", Section 4: "Electrical characteristics",

24-Apr-2014 4 Section 5: "Typical performance characteristics", not found, not found.

Deleted previous Section 8: Different output voltage versions of the

LD39100xx available on request.

Added Section 8: Packaging mechanical data.

Minor text changes.

Updated Figure 32: Typical application circuit for fixed output version.

24-Sep-2015 5

Minor text changes.

24/25 DocID15676 Rev 5

LD39100

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and

improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST

products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order

acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the

design of Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID15676 Rev 5 25/25

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 3G RBS 6000 Alarms and TroubleshootingDocument1,478 pages3G RBS 6000 Alarms and TroubleshootingDaveNo ratings yet

- Acer Aspire One AO756 Service Manual PDFDocument219 pagesAcer Aspire One AO756 Service Manual PDFCarlo100% (1)

- Marelli MF4 Toyota 101 EngDocument6 pagesMarelli MF4 Toyota 101 EngpepeladazoNo ratings yet

- Motorola W388: Getting Started GuideDocument58 pagesMotorola W388: Getting Started GuideyokonakagimaNo ratings yet

- New Generation Single-Board Telecoms Trainer For Advanced ExperimentsDocument8 pagesNew Generation Single-Board Telecoms Trainer For Advanced ExperimentsHuy DoNo ratings yet

- Radio Electronics November 1991 PDFDocument188 pagesRadio Electronics November 1991 PDFlivslx100% (1)

- Features: Surface Mount Fast Switching DiodeDocument4 pagesFeatures: Surface Mount Fast Switching DiodeDe faNo ratings yet

- POE Switches User ManualDocument1 pagePOE Switches User ManualFer DesignerNo ratings yet

- Update Instructions For The MMI HighDocument28 pagesUpdate Instructions For The MMI Highmadalinc1No ratings yet

- Relay Basics: By: Andrew KrauseDocument4 pagesRelay Basics: By: Andrew Krauselavar_wrightNo ratings yet

- SVP309 SIP IP Phone User Manual: Stephen Technologies Co.,Limited All Rights ReservedDocument49 pagesSVP309 SIP IP Phone User Manual: Stephen Technologies Co.,Limited All Rights ReservedanycikaNo ratings yet

- Black Star Meteor 600 Frequency Counter Service ManualDocument18 pagesBlack Star Meteor 600 Frequency Counter Service Manualbill1068No ratings yet

- I Sem PDFDocument324 pagesI Sem PDFRahul AvhadNo ratings yet

- 3102319-En R004 EST Life Safety Systems UL 2572 Application GuideDocument36 pages3102319-En R004 EST Life Safety Systems UL 2572 Application GuideMoises ReyesNo ratings yet

- Iot Based Smart Charger: An Esp8266 Based Automatic ChargerDocument6 pagesIot Based Smart Charger: An Esp8266 Based Automatic Chargerrock starNo ratings yet

- PHILIPS Service ManualDocument161 pagesPHILIPS Service Manualpandorabox2012No ratings yet

- Transmission ModesDocument5 pagesTransmission ModesMuneeza AlizaNo ratings yet

- UF6450 Spec SheetDocument1 pageUF6450 Spec SheetAEyermanNo ratings yet

- Panasonic TH42PX75U Chassis GP10DHU TV Plasma Service ManualDocument540 pagesPanasonic TH42PX75U Chassis GP10DHU TV Plasma Service ManualromarloNo ratings yet

- BARC InterviewDocument9 pagesBARC InterviewShounakDutta100% (1)

- Cylinder Pressure SensorDocument2 pagesCylinder Pressure SensorDiamante HernandezNo ratings yet

- Lec 2.4 Network Hardware & MediaDocument16 pagesLec 2.4 Network Hardware & MediaSuman JyotiNo ratings yet

- ManualDocument11 pagesManualKos Intel DooNo ratings yet

- Product Catalogue: June 2014Document105 pagesProduct Catalogue: June 2014Adrian TodeaNo ratings yet

- Lab ManualDocument8 pagesLab ManualDavinder KakkarNo ratings yet

- DF4GDataFill AC5935 San Jose 20230614 B2 B7 S1 S2Document36 pagesDF4GDataFill AC5935 San Jose 20230614 B2 B7 S1 S2Frank aliaga berrocalNo ratings yet

- Design of A Controlled Solid State Device For Fault Current Limitation and Arc Flash SuppressionDocument6 pagesDesign of A Controlled Solid State Device For Fault Current Limitation and Arc Flash SuppressionAnwar HossanNo ratings yet

- DCC MicroprojectDocument10 pagesDCC Microprojectomahale751No ratings yet

- NI Serial Hardware Specifications PDFDocument62 pagesNI Serial Hardware Specifications PDFKmilo RamirezNo ratings yet