Professional Documents

Culture Documents

DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design

DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design

Uploaded by

Mani KandanOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design

DFT Compiler Lab 1: Insert Scan Chain: Computer-Aided VLSI System Design

Uploaded by

Mani KandanCopyright:

Available Formats

NTUEE GIEE

Computer-Aided VLSI System Design

Dft Compiler Lab 1: Insert Scan Chain

Objectives:

In this lab, you will learn:

1. How to insert scan chain into a synthesized gate level design

Copy Files from CSDTA Directory

1. copy all the files into your work directory,

cp –R ~cvsd/06F/DftCompiler/Lab1 .

2. check if you have these files

filename Description

Lab1_alu_synth.v synthesized gate level Verilog code for the simple ALU

(no scan chain yet)

DftCompilerLab1.scrip scripts to run DftCompiler

t

.synopsys_dc.setup Synopsys Dft Compiler setup file (same format as Design

Compiler). define search paths, library name etc.

3. Check the contents of these files.

Environment Setup

Please add this line into your .cshrc file.

source /usr/cad/synopsys/CIC/tmax.csh

Invoke DftCompiler

Dft Compiler is actually embedded in the Design Compiler. To invoke Dft

Compiler, you can do either one

dc_shell -db_mode -dcsh_mode (command mode)

dv –dcsh_mode & (GUI mode)

I encourage everybody to use command mode because:

a. command mode helps you to keep a record of what you have done.

b. command mode runs more efficiently than GUI mode.

c. command mode helps you to lookup the manual/reference quickly.

In spite of the above advantages, command mode sometimes is not as good as

GUI mode in terms of debugging the schematic problem. We will use command

mode throughout this Lab. You are welcome to try the GUI mode by yourself.

NOTE: maybe you see some error message like “Error: current design not

NTU GIEE Computer Aided System Design 1/4

NTUEE GIEE

defined.” just ignore it for now.

Read Input Files

1. type these lines to read in CIC .18 library and your gate level netlist.

The “target_library” is written in your .synopsys_dc.setup.

read target_library

read Lab1_alu_synth.v -format Verilog

2. To obtain a timing/area report of your scan_inserted design, type

current_design ALU

report_area > Lab1_alu_synth.area_rpt

report_timing > Lab1_alu_synth.timing_rpt

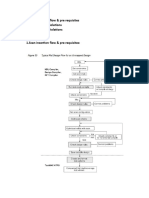

STEP 1 Scan Ready Synthesis

Although you have done the synthesis before, you did not use the –scan option.

This compilation (with –scan option) considers the impact of scan insertion on

mission mode constraints during optimization. This –scan option causes the

command to replace all sequential elements during optimization. Type in these lines.

set_scan_configuration –style multiplexed_flip_flop

set_scan_configuration -methodology full_scan

compile -scan

Question: Do you see any warning messages? _____ Can you explain what are

the sources of the warnings? ________________________________________

Do these warning impact our scan chain insertion? ________

NOTE: The things we have done so far actually should have been done in our

last synthesis Lab1. We do them separately here for educational purpose.

STEP 2 Set ATE configuration

To create a test clock waveform, type

create_test_clock -period 100 -waveform {40, 60} find(port,

"clk")

STEP 3 Pre-scan Check

This command check if your follow the gate-level scan design rule. Type

check_test

Question 1: How many scan cells do you have? _____

Question 2: How many rule violation do you have? _____

NTU GIEE Computer Aided System Design 2/4

NTUEE GIEE

STEP 4 Scan specification

This step tells the Dft Compiler how many scan chains you want. You can also

specify the names of scan related pins (scan_enable, scan_in, scan_out). We will let

Dft Compiler to choose the pin names for us.

set_scan_configuration -chain_count 1

STEP 5 scan preview

This step checks your scan specification for consistency. Please type

preview_scan

Questions: How many scan chains will you have? _____ What are their pin

names? __________________

STEP 6 scan chain synthesis

stitch your scan cells into a chain. And do some more optimizations.

insert_scan

STEP 7 post scan check

To obtain a final summary of your scan chain, type

check_test

STEP 8 Reports

1. To obtain a timing/area report of your scan_inserted design, type

report_area > Lab1_alu_dft.area_rpt

report_timing > Lab1_alu_dft.timing_rpt

Examine the report files of our scan_inserted design. Compare these reports

with those of the non-scan design. Answer these questions if you kept a timing and

area report of synthesis lab 1.

Questions: How much is the area overhead of scan? ______%

How much is the timing overhead of scan? ____%

2. If you want to know the order of your scan chain, type:

report_test -scan_path > Lab1_alu_dft.scan_path

STEP 9 Write out files

1. To output our scan-inserted netlist, type

write -format verilog -hierarchy -output

NTU GIEE Computer Aided System Design 3/4

NTUEE GIEE

Lab1_alu_dft.v

2. the spf (Stil Protocol File) file is needed in our next Lab, ATPG.

write_test_protocol -format stil -out Lab1_alu_dft.spf

3. the sdf (standard delay format) file is for timing analysis. Our next tool, Prime

time, will need this file.

write_sdf Lab1_alu_dft.sdf

Questions/Comments: Check your Verilog netlist.

1. What type of DFF before dft_compiler? ___________ What type of

DFF after dft_compiler? _________

2. What two pins did dft_compiler add? _ &

3. Where is scan ouput pin? ___dft_compiler share the scan_output pin with

the functional output pin so there is NO dedicated scan output pin. This is

done for saving the number of pins. If you want dft_compiler to create a

dedicate scan out pin, use this command before you insert the scan chain..

set_scan_configuration -dedicated_scan_port true

We do not do this in this lab.

Congratulations! You have done.

What we have done is in the file DftCompilerLab1.script.

You can use “include DftCompilerLab1.script” to run it.

END of LAB

Creator:

1st Edition: Chien-Mo Li, 2002

2nd Edition: Yu-Lin Chang, 2004

NTU GIEE Computer Aided System Design 4/4

You might also like

- Mbist FlowDocument2 pagesMbist FlowJaita Bakshi KulshreshthaNo ratings yet

- Split Capture Cycle: During Scan Insertion - During SimulationDocument1 pageSplit Capture Cycle: During Scan Insertion - During Simulationsrikanth0% (1)

- DFT Strategy For IPsDocument11 pagesDFT Strategy For IPsumeshNo ratings yet

- Edt Insertion Lab Observations Test Case 1: - Problem Definition: - InputsDocument42 pagesEdt Insertion Lab Observations Test Case 1: - Problem Definition: - Inputspoojithas acharyaNo ratings yet

- 3 IT - Unit-1 - OSDocument26 pages3 IT - Unit-1 - OSAnbessNo ratings yet

- On DFTDocument16 pagesOn DFTAman TyagiNo ratings yet

- MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCDocument44 pagesMG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCchaitanyaNo ratings yet

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseDocument22 pagesA Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseSiva Sreeramdas100% (1)

- DFT ProtocolDocument33 pagesDFT Protocolnoor_dcetNo ratings yet

- VLSI Test Principles and Architectures: Design for TestabilityFrom EverandVLSI Test Principles and Architectures: Design for TestabilityRating: 4.5 out of 5 stars4.5/5 (4)

- System-on-Chip Test Architectures: Nanometer Design for TestabilityFrom EverandSystem-on-Chip Test Architectures: Nanometer Design for TestabilityNo ratings yet

- Scan Insertion Labs GuidelinesDocument12 pagesScan Insertion Labs GuidelinessenthilkumarNo ratings yet

- ATPG LAB3dDocument2 pagesATPG LAB3dMani KandanNo ratings yet

- Lab4 Testing DFTDocument6 pagesLab4 Testing DFTDeepuNo ratings yet

- Edt Lab DocumentDocument12 pagesEdt Lab DocumentsenthilkumarNo ratings yet

- DFTDocument21 pagesDFTMuhsin Nk100% (1)

- DFT Lab DescriptionDocument22 pagesDFT Lab DescriptionElla ColonNo ratings yet

- At Speed OccDocument5 pagesAt Speed OccAdhi SuruliNo ratings yet

- Asic Design Flow:: Specification FloorplanDocument9 pagesAsic Design Flow:: Specification Floorplanp gangadhar KumarNo ratings yet

- MbistDocument38 pagesMbistNaga NitheshNo ratings yet

- DFT Interview Question2Document1 pageDFT Interview Question2pravallika vysyarajuNo ratings yet

- (Notes) DESIGN FOR TESTABILITYDocument34 pages(Notes) DESIGN FOR TESTABILITYsarathkumarNo ratings yet

- Scan Insertion FlowDocument9 pagesScan Insertion Flowsharath ANo ratings yet

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingDocument3 pagesScan Insertion Lab Observations: Vlsiguru DFT Trainingsenthilkumar100% (1)

- DFT Workout Rev42Document23 pagesDFT Workout Rev42qc3g09No ratings yet

- Mentorpaper 27753Document8 pagesMentorpaper 27753Sunil VermaNo ratings yet

- Design Clock Controllers For Hierarchical TestDocument2 pagesDesign Clock Controllers For Hierarchical Testneelalohith100% (1)

- DFT Interview QuestionsDocument3 pagesDFT Interview QuestionsJayesh PopatNo ratings yet

- DFT With Tetramax PDFDocument33 pagesDFT With Tetramax PDFdeepakk_alpineNo ratings yet

- Lab1 Scan Chain Insertion and Atpg Using Design Compiler and TetramaxDocument47 pagesLab1 Scan Chain Insertion and Atpg Using Design Compiler and TetramaxLakshmi PrasadNo ratings yet

- Scan Insertion CommandsDocument8 pagesScan Insertion CommandsVENKATRAMANNo ratings yet

- Synthesis Netlist - Library Model - Dofile CommandsDocument30 pagesSynthesis Netlist - Library Model - Dofile CommandsPrafulani GajbhiyeNo ratings yet

- On Chip Clock Controller For At-Speed TestingDocument4 pagesOn Chip Clock Controller For At-Speed TestingSachin*123No ratings yet

- Tessent Samsung Han U2U18Document22 pagesTessent Samsung Han U2U18vasav1No ratings yet

- Boundary Scan TutorialDocument58 pagesBoundary Scan TutorialSandeep PandeyNo ratings yet

- Scan Insertion Lab ObservationsDocument2 pagesScan Insertion Lab ObservationssenthilkumarNo ratings yet

- Some DFT Related QuestionsDocument5 pagesSome DFT Related QuestionsAdhi SuruliNo ratings yet

- MBIST Verification Best Practices ChallengesDocument5 pagesMBIST Verification Best Practices ChallengessureshNo ratings yet

- An Introduction To DFT - Bridging & Switch Level FaultsDocument24 pagesAn Introduction To DFT - Bridging & Switch Level FaultsNaga NitheshNo ratings yet

- Testing of Repairable Embedded Memories in SoC Approach and ChallengesDocument6 pagesTesting of Repairable Embedded Memories in SoC Approach and Challengesassantiago1No ratings yet

- DFT - CLK - Mux and DFT - CLK - Chain Data SheetDocument12 pagesDFT - CLK - Mux and DFT - CLK - Chain Data SheetRohit PatelNo ratings yet

- Scan Training Class 4 - EDT Scan Compression, STF, and Border SealingDocument29 pagesScan Training Class 4 - EDT Scan Compression, STF, and Border SealingChandraNo ratings yet

- Fault ClassificationDocument7 pagesFault ClassificationsuburaajNo ratings yet

- Stil PDFDocument9 pagesStil PDFSaurin ShahNo ratings yet

- Basic Interview Questions On DFTDocument5 pagesBasic Interview Questions On DFTHardik TrivediNo ratings yet

- Memory Built in Self TestingDocument30 pagesMemory Built in Self TestingShereenHusseinNo ratings yet

- Edt DofileDocument2 pagesEdt DofilesenthilkumarNo ratings yet

- Basic Interview Questions On DFTDocument1 pageBasic Interview Questions On DFTdeepaNo ratings yet

- Scan InsertionDocument40 pagesScan InsertionAmena FarhatNo ratings yet

- Boundary ScanDocument8 pagesBoundary Scanmechbull11No ratings yet

- Tracing CoverageDocument2 pagesTracing CoverageSrinath M SNo ratings yet

- Segregated QuestionsDocument1 pageSegregated QuestionsdeepaNo ratings yet

- Tshell UserDocument440 pagesTshell UserSujit TikekarNo ratings yet

- Case1 ObservationDocument5 pagesCase1 ObservationsenthilkumarNo ratings yet

- Mahitha Scan Insertion Observation PDFDocument30 pagesMahitha Scan Insertion Observation PDFPrafulani Gajbhiye100% (1)

- Assignment 1 Poovika.tDocument12 pagesAssignment 1 Poovika.tsenthilkumarNo ratings yet

- Lock Up Latch in VLSIDocument8 pagesLock Up Latch in VLSIsandy_711100% (1)

- Tetramax® Lab: Automatic Test Pattern Generation (Atpg) : Computer-Aided Vlsi System DesignDocument4 pagesTetramax® Lab: Automatic Test Pattern Generation (Atpg) : Computer-Aided Vlsi System Designkondalarao79No ratings yet

- Design For Testability - Theory and Practice: Organized by VLSI Society of IndiaDocument2 pagesDesign For Testability - Theory and Practice: Organized by VLSI Society of IndiaMani KandanNo ratings yet

- Government Initiatives in Health and Nutrition: Vinod PaulDocument29 pagesGovernment Initiatives in Health and Nutrition: Vinod PaulMani KandanNo ratings yet

- Design For Test Scan TestDocument31 pagesDesign For Test Scan TestMani KandanNo ratings yet

- Basics of Multicycle Path and Fals PathDocument11 pagesBasics of Multicycle Path and Fals PathMani KandanNo ratings yet

- Low-Power Design and Test, Lecture 8Document35 pagesLow-Power Design and Test, Lecture 8Mani KandanNo ratings yet

- Lecture 6: Combinational Atpg: Design For Testability Theory and PracticeDocument28 pagesLecture 6: Combinational Atpg: Design For Testability Theory and PracticeMani KandanNo ratings yet

- Tmax Quick ReferenceDocument80 pagesTmax Quick ReferenceMani KandanNo ratings yet

- TA Web Page: WWW - Ee.nthu - Edu.tw/ee625001Document1 pageTA Web Page: WWW - Ee.nthu - Edu.tw/ee625001Mani KandanNo ratings yet

- UFS - Universal Flash StorageDocument11 pagesUFS - Universal Flash StorageMani Kandan100% (1)

- Cpapameletis ThesisDocument96 pagesCpapameletis ThesisMani KandanNo ratings yet

- Msem 2011Document2 pagesMsem 2011Mani KandanNo ratings yet

- Design For Testability - Theory and Practice: Organized by VLSI Society of IndiaDocument2 pagesDesign For Testability - Theory and Practice: Organized by VLSI Society of IndiaMani KandanNo ratings yet

- English@Work in AsiaDocument11 pagesEnglish@Work in AsiaMani KandanNo ratings yet

- JTAG - Save Money With ItDocument42 pagesJTAG - Save Money With ItMani KandanNo ratings yet

- SCAN & ATPG WorkbookDocument12 pagesSCAN & ATPG WorkbookMani KandanNo ratings yet

- Pattern: Each Paper Contains 65 Questions Carrying 100 Marksquestion Paper Pattern in Papers Bearing The CodesDocument3 pagesPattern: Each Paper Contains 65 Questions Carrying 100 Marksquestion Paper Pattern in Papers Bearing The CodesMani KandanNo ratings yet

- Recruitement For The Post of Project Assistant: Office of The Dean (R & C), Nit, TiruchiDocument3 pagesRecruitement For The Post of Project Assistant: Office of The Dean (R & C), Nit, TiruchiMani KandanNo ratings yet

- Aquarium Shop Management SystemDocument41 pagesAquarium Shop Management Systemkrishnithyan67% (3)

- UNIT 5 Java Beans Components PDFDocument15 pagesUNIT 5 Java Beans Components PDFaashika shresthaNo ratings yet

- EBall TechnologyDocument24 pagesEBall TechnologytasmiyaNo ratings yet

- Mobile Application Development: by Wahid QayyumDocument271 pagesMobile Application Development: by Wahid QayyumAbu HurairaNo ratings yet

- Google Cloud Fund M2 Getting Started With Google CloudDocument52 pagesGoogle Cloud Fund M2 Getting Started With Google CloudGiuseppe TrittoNo ratings yet

- UI & UX For Responsive Web DesignDocument9 pagesUI & UX For Responsive Web Designrekharawat56515No ratings yet

- Python Programming Unit 1 NotesDocument21 pagesPython Programming Unit 1 NotesAtebar HaiderNo ratings yet

- Unit 6: Operating SystemDocument66 pagesUnit 6: Operating SystemNasarMahmoodNo ratings yet

- Blindness TechnologyDocument28 pagesBlindness TechnologyDennis GarrettNo ratings yet

- Manual XMR401HDSDocument73 pagesManual XMR401HDSEduardo FernandezNo ratings yet

- Ark Embarked On Their VoyageDocument25 pagesArk Embarked On Their VoyageChris Cider ThompsonNo ratings yet

- VSM OverviewDocument12 pagesVSM OverviewPopescu Tiberius NectarNo ratings yet

- Bachelor ArbeitDocument152 pagesBachelor Arbeitcristi_pet4742No ratings yet

- Eng - Using MATLAB Component Object Model With Visual Basic Graphical User Interface (GUI) Application To One Dimensional Diffusion Heat Transfer Equations of Extended Surface (FINS) PDFDocument5 pagesEng - Using MATLAB Component Object Model With Visual Basic Graphical User Interface (GUI) Application To One Dimensional Diffusion Heat Transfer Equations of Extended Surface (FINS) PDFYuriadiNo ratings yet

- Full SyllabusDocument1,070 pagesFull SyllabusXyzNo ratings yet

- Hype Cycle For Web and User 214448Document88 pagesHype Cycle For Web and User 214448Rushab AgarwalNo ratings yet

- XCSoar Manual 500Document169 pagesXCSoar Manual 500RafaelGrockNo ratings yet

- SAP HANA Server Installation Guide en PDFDocument272 pagesSAP HANA Server Installation Guide en PDFRwin TupangNo ratings yet

- Stmicroelectronics Pfe Book 2024Document34 pagesStmicroelectronics Pfe Book 2024Haythem JameiNo ratings yet

- D60 Line Distance Relay: Instruction ManualDocument442 pagesD60 Line Distance Relay: Instruction ManualyaneiroNo ratings yet

- CGI Studio: 2D/3D HMI/GUI Software Development PlatformDocument2 pagesCGI Studio: 2D/3D HMI/GUI Software Development PlatformWojciech BłądekNo ratings yet

- Autocad 1Document15 pagesAutocad 1ahmustNo ratings yet

- Hci Lab 01 (21-Se-101)Document5 pagesHci Lab 01 (21-Se-101)Agha Muhammad Yar KhanNo ratings yet

- Manual Harris1Document146 pagesManual Harris1luiscastillo7No ratings yet

- Application Software Glossary PDFDocument3 pagesApplication Software Glossary PDFMuhammad Haider AliNo ratings yet

- Red Hat Enterprise Virtualization 3.1 Administration Guide en USDocument374 pagesRed Hat Enterprise Virtualization 3.1 Administration Guide en USbangbus77No ratings yet

- Chapter 2 Class 9Document7 pagesChapter 2 Class 9a38478873No ratings yet

- QueryDocument11 pagesQueryswathiNo ratings yet

- Ibm Flashsystem 7200 Product Guide: PaperDocument60 pagesIbm Flashsystem 7200 Product Guide: PaperWiston CorderoNo ratings yet