Professional Documents

Culture Documents

64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632K

64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632K

Uploaded by

Cường MchwCopyright:

Available Formats

You might also like

- XMTG 7000 Programmer User Manual PDFDocument17 pagesXMTG 7000 Programmer User Manual PDFCường Mchw100% (1)

- A729000 Control Unit Operation ManualDocument27 pagesA729000 Control Unit Operation Manualjohn castillo100% (4)

- Yr1030 en (Draft)Document10 pagesYr1030 en (Draft)Cường Mchw100% (1)

- E09A92GADocument1 pageE09A92GACường Mchw100% (1)

- How To Install and Run Android x86 On VirtualBoxDocument13 pagesHow To Install and Run Android x86 On VirtualBoxalfarysiNo ratings yet

- 056-095 Remote Start Input FunctionsDocument2 pages056-095 Remote Start Input FunctionsOsvaldo ChimbasNo ratings yet

- 256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Document14 pages256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Cường MchwNo ratings yet

- Sb5101 Samsung UpgradeDocument14 pagesSb5101 Samsung Upgradejohnny-lawless3277No ratings yet

- K4S561632EDocument15 pagesK4S561632ELelik GhhNo ratings yet

- 64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Document12 pages64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Luis AntunesNo ratings yet

- 013 - k4s64xx32n - Rev111 RAM DinámicaDocument15 pages013 - k4s64xx32n - Rev111 RAM DinámicanachcratchNo ratings yet

- Data SheetDocument11 pagesData SheetManuel VillarNo ratings yet

- Iiic - CC: 128Mb K-Die SDRAM SpecificationDocument15 pagesIiic - CC: 128Mb K-Die SDRAM SpecificationTan Hung LuuNo ratings yet

- Advanced Tech Mapping Supp4Document8 pagesAdvanced Tech Mapping Supp48711110029No ratings yet

- KTLP 3616Document10 pagesKTLP 3616Ismael silvaNo ratings yet

- Dimensions in MM (Inches) .: TO39 (TO205AD) PinoutsDocument2 pagesDimensions in MM (Inches) .: TO39 (TO205AD) PinoutsJinsmon AlexNo ratings yet

- Detail 02 L Vinkel Var 1Document14 pagesDetail 02 L Vinkel Var 1BrcakNo ratings yet

- Mechanical Data: D (R-PDSO-G ) Plastic Small-Outline PackageDocument2 pagesMechanical Data: D (R-PDSO-G ) Plastic Small-Outline PackageEva AvilésNo ratings yet

- Voltage Mode Multiplying DAC Reference DesignDocument16 pagesVoltage Mode Multiplying DAC Reference DesignMouloud IbelaidenNo ratings yet

- ECS RS880PM-AM Rev 1.0 СхемаDocument37 pagesECS RS880PM-AM Rev 1.0 СхемаA2139No ratings yet

- 2 N 2243 ADocument1 page2 N 2243 AAhmed EL-arabyNo ratings yet

- High-Friquency General-Purpose Amplifier Applications: Package Dimensions FeaturesDocument5 pagesHigh-Friquency General-Purpose Amplifier Applications: Package Dimensions FeaturesArturo ArmuellesNo ratings yet

- High Performance CMOS 5 X 7 Alphanumeric Displays: Technical DataDocument16 pagesHigh Performance CMOS 5 X 7 Alphanumeric Displays: Technical DataEmanuel OanceaNo ratings yet

- User's Manual of Haiwell Classic PLC Analog ModuleDocument18 pagesUser's Manual of Haiwell Classic PLC Analog ModuleMayte GomezNo ratings yet

- Molding Power Inductors: FeaturesDocument5 pagesMolding Power Inductors: FeaturesPușcă MartinNo ratings yet

- SML-D14x (C) Series: Data SheetDocument10 pagesSML-D14x (C) Series: Data SheetKhadija EL ATRASSINo ratings yet

- Surface Roughness Conversion Chart Tables - Engineers EdgeDocument10 pagesSurface Roughness Conversion Chart Tables - Engineers Edgejames.anitNo ratings yet

- pdf-userManuals-03-Product Manual - Loop Powered 4-20 Ma Output Vibration SensorDocument8 pagespdf-userManuals-03-Product Manual - Loop Powered 4-20 Ma Output Vibration SensorTAHRI BELGACEMNo ratings yet

- 413 05857 0 LC35256FT 70uDocument7 pages413 05857 0 LC35256FT 70uA.hNo ratings yet

- SunonDocument4 pagesSunonEmerson Müller Juarez AvilaNo ratings yet

- KTLP3616 COSMOElectronicsCorporationDocument10 pagesKTLP3616 COSMOElectronicsCorporationaltakadum78No ratings yet

- Memory Module Specification: KHX6400D2LLK2/2GDocument2 pagesMemory Module Specification: KHX6400D2LLK2/2GΒΙΒΗ ΓΚΑΣΙΩΝΗNo ratings yet

- Heds-9140#i00 Heds-9140#i00Document14 pagesHeds-9140#i00 Heds-9140#i00LuisEdgarMartinezAvilaNo ratings yet

- 步进电机详细参数资料Document13 pages步进电机详细参数资料Andy YouQuanTexNo ratings yet

- 40 X 40 X 10 MM SERIES: Dimensions DrawingDocument9 pages40 X 40 X 10 MM SERIES: Dimensions DrawingVíctor RomeuNo ratings yet

- TS12864c-5 YGDocument13 pagesTS12864c-5 YGHéctor Eduardo Urbina UrbinaNo ratings yet

- SANMOTION K Series DC Servo MotorDocument5 pagesSANMOTION K Series DC Servo MotorNisar AhmedNo ratings yet

- Power Scaling of Kw-Diode Lasers Optimized For Material Processing ApplicationsDocument9 pagesPower Scaling of Kw-Diode Lasers Optimized For Material Processing ApplicationsDu RoyNo ratings yet

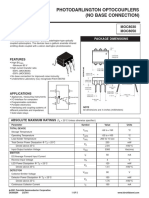

- Photodarlington Optocouplers (No Base Connection) : DescriptionDocument8 pagesPhotodarlington Optocouplers (No Base Connection) : DescriptionThomas ThomasNo ratings yet

- Led2 1.2Document12 pagesLed2 1.2EduardoNo ratings yet

- 10/100 PC Card LAN Magnetic Modules: MechanicalsDocument2 pages10/100 PC Card LAN Magnetic Modules: MechanicalsAbdelrhman ElsayedNo ratings yet

- Optically Coupled 20 Ma Current Loop Receiver: HCPL-4200Document13 pagesOptically Coupled 20 Ma Current Loop Receiver: HCPL-4200bigm94iNo ratings yet

- Characteristics DF Pipingmateriais SteelpipeDocument4 pagesCharacteristics DF Pipingmateriais SteelpipeMauricio RodriguesNo ratings yet

- Snap-In Mounting: Specifications IntroductionsDocument2 pagesSnap-In Mounting: Specifications IntroductionsMangueras Hidraulicas H-RojasNo ratings yet

- TACT Switch TDSDocument3 pagesTACT Switch TDSHareram ShuklaNo ratings yet

- Vishay 1445Document2 pagesVishay 1445rogerNo ratings yet

- Surface Roughness-Conersion Chart TableDocument2 pagesSurface Roughness-Conersion Chart TableAnonymous w1yuNZTqONNo ratings yet

- Di100s SeriesDocument5 pagesDi100s Seriesivanshitov2015No ratings yet

- Varactor Diode For FM Receiver Electronic Tuning ApplicationsDocument3 pagesVaractor Diode For FM Receiver Electronic Tuning ApplicationsАндрей ПоляковNo ratings yet

- Trubka Ocel ST 37 4 Bezesva Cerna Uk Katalogovy ListDocument2 pagesTrubka Ocel ST 37 4 Bezesva Cerna Uk Katalogovy ListVratislav Němec ml.No ratings yet

- 135616ds k4s56xx32n Rev10Document18 pages135616ds k4s56xx32n Rev10dmitry esaulkovNo ratings yet

- Crystek Corporation: Voltage Controlled Oscillator-VCO CVCO55CL-0805-0900Document2 pagesCrystek Corporation: Voltage Controlled Oscillator-VCO CVCO55CL-0805-0900Gerard PabloNo ratings yet

- Bu 9348 KDocument3 pagesBu 9348 KbinkyfishNo ratings yet

- Pg240128a DisplayDocument1 pagePg240128a Displaybancadasol03No ratings yet

- Optically Coupled 20 Ma Current Loop Transmitter: HCPL-4100Document13 pagesOptically Coupled 20 Ma Current Loop Transmitter: HCPL-4100bigm94iNo ratings yet

- Samsung SPMWHT541ML5XATMS6 DatasheetDocument36 pagesSamsung SPMWHT541ML5XATMS6 Datasheetstephane.krycNo ratings yet

- 14PM M201V NMBDocument1 page14PM M201V NMBCristianEnacheNo ratings yet

- Av02 0565en - Ds - Acpl m43t - 2015 10 19Document10 pagesAv02 0565en - Ds - Acpl m43t - 2015 10 19Denis CarlosNo ratings yet

- sj5 43502pmDocument1 pagesj5 43502pmthatatkdferreiraNo ratings yet

- CHF190104xBF Series 800 W Power RF Flanged Chip Termination/ResistorDocument1 pageCHF190104xBF Series 800 W Power RF Flanged Chip Termination/ResistorMPIMLACNo ratings yet

- T.D.A 04H0SK1RDocument1 pageT.D.A 04H0SK1Rmichael luqueNo ratings yet

- PNP Silicon Epitaxial Base Power Tansistors: ApplicationsDocument2 pagesPNP Silicon Epitaxial Base Power Tansistors: ApplicationsGabriel GaniNo ratings yet

- 32data Sheet lm561c Rev.7.0Document37 pages32data Sheet lm561c Rev.7.0stephane.krycNo ratings yet

- High-Performance. Advanced Scan ControlDocument2 pagesHigh-Performance. Advanced Scan ControlCường MchwNo ratings yet

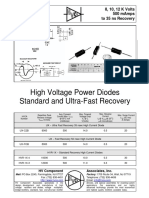

- UX-G5B Data Sheet: V 7.5 KV, I 350 Ma High-Frequency and High-Voltage Rectifier DiodeDocument5 pagesUX-G5B Data Sheet: V 7.5 KV, I 350 Ma High-Frequency and High-Voltage Rectifier DiodeCường MchwNo ratings yet

- Sequencing With Next-Generation Non-Signaling Test EquipmentDocument7 pagesSequencing With Next-Generation Non-Signaling Test EquipmentCường MchwNo ratings yet

- UX FOB HVComponentAssociatesDocument1 pageUX FOB HVComponentAssociatesCường MchwNo ratings yet

- Power - Integrations:TO-220: Title: Class D AmplifierDocument1 pagePower - Integrations:TO-220: Title: Class D AmplifierCường Mchw100% (1)

- Acoustic Wave Music System IIDocument30 pagesAcoustic Wave Music System IICường MchwNo ratings yet

- BOM For Class-D Amplifier: Nr. Designator Package Quantity DesignationDocument1 pageBOM For Class-D Amplifier: Nr. Designator Package Quantity DesignationCường MchwNo ratings yet

- 256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Document14 pages256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Cường MchwNo ratings yet

- 8202RDocument5 pages8202RCường MchwNo ratings yet

- Downloaded From Manuals Search EngineDocument28 pagesDownloaded From Manuals Search EngineCường MchwNo ratings yet

- Onvex: Catalogue 2005Document52 pagesOnvex: Catalogue 2005Cường MchwNo ratings yet

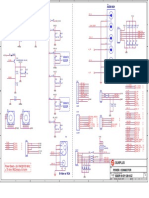

- GM 9.2 SchematicDocument1 pageGM 9.2 SchematicCường MchwNo ratings yet

- VIA+EPIA+M Datasheet v090217Document2 pagesVIA+EPIA+M Datasheet v090217rekluzoNo ratings yet

- Sheet #3Document7 pagesSheet #3Youssef EbrahimNo ratings yet

- METSEPM5560: Product Data SheetDocument3 pagesMETSEPM5560: Product Data SheetDedeKurniawanNo ratings yet

- Current Mirrors II - Source Degeneration: in This LectureDocument2 pagesCurrent Mirrors II - Source Degeneration: in This LectureHassan FarssiNo ratings yet

- BMW R 1200 RT - Nov. 2004 Onward - Model Code 0368Document174 pagesBMW R 1200 RT - Nov. 2004 Onward - Model Code 0368Vlad SusmanNo ratings yet

- Oscillation Waves 09-11 MC 2Document23 pagesOscillation Waves 09-11 MC 2AllyLauNo ratings yet

- A Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationDocument30 pagesA Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode Simulationiarcad9403No ratings yet

- Smith Chart in Color - 2Document1 pageSmith Chart in Color - 2Andro Elnatan HarianjaNo ratings yet

- RB411UAHL Repair InstructionsDocument9 pagesRB411UAHL Repair InstructionscontatoseconnectNo ratings yet

- Switches and IndicatorsDocument88 pagesSwitches and IndicatorsMukhtar KhadyrbergenovNo ratings yet

- Instruction Manual Alfa Laval Level Switch (Recuperado) (Recuperado) (Recuperado)Document8 pagesInstruction Manual Alfa Laval Level Switch (Recuperado) (Recuperado) (Recuperado)Natsu HgkNo ratings yet

- Datasheet en 20170526Document10 pagesDatasheet en 20170526LODELBARRIO RDNo ratings yet

- DebugDocument13 pagesDebugwsosaNo ratings yet

- iTM Plus Adaptor: Installation ManualDocument36 pagesiTM Plus Adaptor: Installation Manuallucio ruiz jrNo ratings yet

- CD Floppy, Hard Disk DriveDocument76 pagesCD Floppy, Hard Disk DriveIam BeccaNo ratings yet

- MicrostripantennaDocument47 pagesMicrostripantennaNuzhath FathimaNo ratings yet

- Mve Kimera 1 - A14-132 - Dokumentace enDocument62 pagesMve Kimera 1 - A14-132 - Dokumentace enshahramkh59No ratings yet

- WEEK 11 F TOPIC11 RADAR ARPA Different Signals 3Document7 pagesWEEK 11 F TOPIC11 RADAR ARPA Different Signals 3Daniel OrenaNo ratings yet

- Elevator System Modellingand Simulation Paperrev 6140704Document11 pagesElevator System Modellingand Simulation Paperrev 6140704Prajwal TeppalwarNo ratings yet

- DH48SDocument2 pagesDH48SGold JoshuaNo ratings yet

- PM240P 2 FSD FSG 0521Document2 pagesPM240P 2 FSD FSG 0521SANTIAGO JOSUE FARFAN TRUJILLONo ratings yet

- En 305 Magflux Datasheet 1711Document23 pagesEn 305 Magflux Datasheet 1711Gerrard ArchuletaNo ratings yet

- A Buck Converter Based On PID Controller For Voltage Step - Down Application.... Trae Un Circuito Buck Aplicado en MatlabDocument4 pagesA Buck Converter Based On PID Controller For Voltage Step - Down Application.... Trae Un Circuito Buck Aplicado en MatlabDavid RomeroNo ratings yet

- 362 Ps 6 SolnsDocument13 pages362 Ps 6 Solnsrameshaarya99No ratings yet

- Change Log PDFDocument16 pagesChange Log PDFCesar MartinezNo ratings yet

- Dragomir Et Ski y 2014Document14 pagesDragomir Et Ski y 2014kalokosNo ratings yet

64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632K

64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632K

Uploaded by

Cường MchwOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632K

64Mb K-Die SDRAM Specification: K4S640832K Synchronous DRAM K4S641632K

Uploaded by

Cường MchwCopyright:

Available Formats

K4S640832K

K4S641632K Synchronous DRAM

64Mb K-die SDRAM Specification

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure couldresult in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

1 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

Revision History

Revision Month Year History

0.0 January 2005 - Target spec release

0.1 March 2005 - Change DC current

0.2 April 2005 - Delete bit organization for x4

0.3 July 2005 - Delete 7ns speed bin

1.0 September 2005 - Final spec release

1.1 February 2006 - Added 5ns speed bin for x16

2 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

2M x 8Bit x 4Banks / 1M x 16Bit x 4Banks SDRAM

FEATURES

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system clock

• Burst read single-bit write operation

• DQM (x8) & L(U)DQM (x16) for masking

• Auto & self refresh

• 64ms refresh period (4K cycle)

• Pb/Pb-free Package

• RoHS compliant for Pb-free Package

GENERAL DESCRIPTION

The K4S640832K / K4S641632K is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 8

bits, / 4 x 1,048,576 words by 16 bits, fabricated with SAMSUNG′s high performance CMOS technology. Synchronous design allows

precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies,

programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high perfor-

mance memory system applications.

Ordering Information

Part No. Orgainization Max Freq. Interface Package

K4S640832K-T(U)C/L75 8Mb x 8 133MHz(CL=3)

K4S641632K-T(U)C/L50 200MHz(CL=3) 54pin TSOP(II)

LVTTL

K4S641632K-T(U)C/L60 4Mb x 16 166MHz(CL=3) Pb (Pb-free)

K4S641632K-T(U)C/L75 133MHz(CL=3)

Organization Row Address Column Address

8Mx8 A0~A11 A0-A8

4Mx16 A0~A11 A0-A7

Row & Column address configuration

3 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

Package Physical Dimension

0~8°C

0.25

TYP

0.010

#54 #28

0.018~0.030

0.45~0.75

0.463±0.008

11.76±0.20

0.400

10.16

#1 #27

( 0.50 )

0.125+0.075

0.020

-0.035

22.62 0.005+0.003

-0.001

MAX

0.891

22.22 ± 0.10 0.21 ± 0.05 1.00 ± 0.10 1.20

0.875 MAX

± 0.004 0.008 ± 0.002 0.039 ± 0.004 0.047

0.10

MAX

0.004 0.05

+0.10

0.71 0.30 -0.05 0.80 MIN

( ) 0.002

0.028 0.012 +0.004

-0.002

0.0315

54Pin TSOP(II) Package Dimension

4 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

FUNCTIONAL BLOCK DIAGRAM

I/O Control

LWE

Data Input Register

LDQM

Bank Select

2M x 8 / 1M x 16

Refresh Counter

Output Buffer

Row Decoder

Sense AMP

Row Buffer

2M x 8 / 1M x 16

DQi

Address Register

2M x 8 / 1M x 16

CLK

2M x 8 / 1M x 16

ADD

Column Decoder

LRAS

LCBR

Col. Buffer

Latency & Burst Length

LCKE

Programming Register

LRAS LCBR LWE LCAS LWCBR LDQM

Timing Register

CLK CKE CS RAS CAS WE L(U)DQM

* Samsung Electronics reserves the right to change products or specification without notice.

5 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

PIN CONFIGURATION (Top view)

x16 x8 x8 x16

VDD VDD 1 54 VSS VSS

DQ0 DQ0 2 53 DQ7 DQ15

VDDQ VDDQ 3 52 VSSQ VSSQ

DQ1 N.C 4 51 N.C DQ14

DQ2 DQ1 5 50 DQ6 DQ13

VSSQ VSSQ 6 49 VDDQ VDDQ

DQ3 N.C 7 48 N.C DQ12

DQ4 DQ2 8 47 DQ5 DQ11

VDDQ VDDQ 9 46 VSSQ VSSQ

DQ5 N.C 10 45 N.C DQ10

DQ6 DQ3 11 44 DQ4 DQ9

VSSQ VSSQ 12 43 VDDQ VDDQ

DQ7 N.C 13 42 N.C DQ8

VDD VDD 14 41 VSS VSS

LDQM N.C 15 40 N.C/RFU N.C/RFU

WE WE 16 39 DQM UDQM

CAS CAS 17 38 CLK CLK

RAS RAS 18 37 CKE CKE

CS CS 19 36 N.C N.C

BA0 BA0 20 35 A11 A11

BA1 BA1 21 34 A9 A9

A10/AP A10/AP 22 33 A8 A8

A0 A0 23 32 A7 A7

A1 A1 24 31 A6 A6

A2 A2 25 30 A5 A5 54Pin TSOP (II)

A3 A3 26 29 A4 A4 (400mil x 875mil)

VDD VDD 27 28 VSS VSS (0.8 mm Pin pitch)

PIN FUNCTION DESCRIPTION

Pin Name Input Function

CLK System clock Active on the positive going edge to sample all inputs.

Disables or enables device operation by masking or enabling all inputs except

CS Chip select

CLK, CKE and DQM

Masks system clock to freeze operation from the next clock cycle.

CKE Clock enable CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

Row/column addresses are multiplexed on the same pins.

A0 ~ A11 Address Row address : RA0 ~ RA11,

Column address : (x8 : CA0 ~ CA8 , x16 : CA0 ~ CA7)

Selects bank to be activated during row address latch time.

BA0 ~ BA1 Bank select address

Selects bank for read/write during column address latch time.

Latches row addresses on the positive going edge of the CLK with RAS low.

RAS Row address strobe

Enables row access & precharge.

Latches column addresses on the positive going edge of the CLK with CAS low.

CAS Column address strobe

Enables column access.

Enables write operation and row precharge.

WE Write enable

Latches data in starting from CAS, WE active.

Makes data output Hi-Z, tSHZ after the clock and masks the output.

DQM Data input/output mask

Blocks data input when DQM active.

Data inputs/outputs are multiplexed on the same pins.

DQ0 ~ N Data input/output

(x8 : DQ0 ~ 7), (x16 : DQ0 ~ 15)

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

Isolated power supply and ground for the output buffers to provide improved noise

VDDQ/VSSQ Data output power/ground

immunity.

No connection

N.C/RFU This pin is recommended to be left No Connection on the device.

/reserved for future use

6 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Value Unit

Voltage on any pin relative to VSS VIN, VOUT -1.0 ~ 4.6 V

Voltage on VDD supply relative to VSS VDD, VDDQ -1.0 ~ 4.6 V

Storage temperature TSTG -55 ~ +150 °C

Power dissipation PD 1 W

Short circuit current IOS 50 mA

Note : Permanent device damage may occur if "ASOLUTE MAXIMUM RATINGS" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to VSS = 0V, TA = 0 to 70°C)

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD, VDDQ 3.0 3.3 3.6 V

Input logic high voltage VIH 2.0 3.0 VDD+0.3 V 1

Input logic low voltage VIL -0.3 0 0.8 V 2

Output logic high voltage VOH 2.4 - - V IOH = -2mA

Output logic low voltage VOL - - 0.4 V IOL = 2mA

Input leakage current ILI -10 - 10 uA 3

Notes : 1. VIH (max) = 5.6V AC.The overshoot voltage duration is ≤ 3ns.

2. VIL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.

3. Any input 0V ≤ VIN ≤ VDDQ.

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State outputs.

CAPACITANCE (VDD = 3.3V, TA = 23°C, f = 1MHz, VREF =1.4V ± 200 mV)

Pin Symbol Min Max Unit Note

Clock CCLK 2.5 4.0 pF

RAS, CAS, WE, CS, CKE, DQM CIN 2.5 5.0 pF

Address CADD 2.5 5.0 pF

(x8 : DQ0 ~ DQ7), (x16 : DQ0 ~DQ15) COUT 4.0 6.5 pF

7 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

DC CHARACTERISTICS (x8)

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C for x8)

Version

Parameter Symbol Test Condition Unit Note

75

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 55 mA 1

(One bank active)

IO = 0 mA

Precharge standby current in ICC2P CKE ≤ VIL(max), tCC = 10ns 1 mA

power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 1

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 15

Precharge standby current in Input signals are changed one time during 20ns

mA

non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC2NS 6

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 3

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 3

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 30

Input signals are changed one time during 20ns

non power-down mode mA

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC3NS 25

Input signals are stable

IO = 0 mA

Operating current Page burst

ICC4 80 mA 1

(Burst mode) 4Banks Activated

tCCD = 2CLKs

Refresh current ICC5 tRC ≥ tRC(min) 85 mA 2

C 1 mA 3

Self refresh current ICC6 CKE ≤ 0.2V

L 400 uA 4

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S640832K-T(U)C

4. K4S640832K-T(U)L

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

8 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

DC CHARACTERISTICS (x16)

(Recommended operating condition unless otherwise noted, TA = 0 to 70°C for x16 only)

Version

Parameter Symbol Test Condition Unit Note

50 60 75

Burst length = 1

Operating current

ICC1 tRC ≥ tRC(min) 80 70 55 mA 1

(One bank active)

IO = 0 mA

Precharge standby current in ICC2P CKE ≤ VIL(max), tCC = 10ns 1 mA

power-down mode ICC2PS CKE & CLK ≤ VIL(max), tCC = ∞ 1

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

ICC2N 15

Precharge standby current in Input signals are changed one time during 20ns

mA

non power-down mode CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC2NS 6

Input signals are stable

Active standby current in ICC3P CKE ≤ VIL(max), tCC = 10ns 3

mA

power-down mode ICC3PS CKE & CLK ≤ VIL(max), tCC = ∞ 3

CKE ≥ VIH(min), CS ≥ VIH(min), tCC = 10ns

Active standby current in ICC3N 30

Input signals are changed one time during 20ns

non power-down mode mA

(One bank active) CKE ≥ VIH(min), CLK ≤ VIL(max), tCC = ∞

ICC3NS 25

Input signals are stable

IO = 0 mA

Operating current Page burst

ICC4 110 100 85 mA 1

(Burst mode) 4Banks Activated

tCCD = 2CLKs

Refresh current ICC5 tRC ≥ tRC(min) 110 100 85 mA 2

C 1 mA 3

Self refresh current ICC6 CKE ≤ 0.2V

L 400 uA 4

Notes : 1. Measured with outputs open.

2. Refresh period is 64ms.

3. K4S641632K-T(U)C

4. K4S641632K-T(U)L

5. Unless otherwise noted, input swing IeveI is CMOS(VIH /VIL=VDDQ/VSSQ)

9 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

AC OPERATING TEST CONDITIONS (VDD = 3.3V ± 0.3V, TA = 0 to 70°C)

Parameter Value Unit

AC input levels (Vih/Vil) 2.4/0.4 V

Input timing measurement reference level 1.4 V

Input rise and fall time tr/tf = 1/1 ns

Output timing measurement reference level 1.4 V

Output load condition See Fig. 2

3.3V Vtt = 1.4V

1200Ω 50Ω

VOH (DC) = 2.4V, IOH = -2mA

Output Output Z0 = 50Ω

VOL (DC) = 0.4V, IOL = 2mA

30pF 30pF

870Ω

(Fig. 1) DC output load circuit (Fig. 2) AC output load circuit

OPERATING AC PARAMETER

(AC operating conditions unless otherwise noted)

Version

Parameter Symbol Unit Note

50 60 75

Row active to row active delay tRRD(min) 10 12 15 ns 1

RAS to CAS delay tRCD(min) 15 18 20 ns 1

Row precharge time tRP(min) 15 18 20 ns 1

tRAS(min) 40 42 45 ns 1

Row active time

tRAS(max) 100 us

Row cycle time tRC(min) 55 60 65 ns 1, 6

Last data in to row precharge tRDL(min) 2 CLK 2,5,6

Last data in to Active delay tDAL(min) 2 CLK + tRP - 5

Last data in to new col. address delay tCDL(min) 1 CLK 2

Last data in to burst stop tBDL(min) 1 CLK 2

Col. address to col. address delay tCCD(min) 1 CLK 3

CAS latency = 3 2

Number of valid output data ea 4

CAS latency = 2 1

Notes : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time

and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

5. In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported.

SAMSUNG recommends tRDL=2CLK and tDAL=2CLK + tRP.

6. tRC =tRFC, tRDL = tWR.

10 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

50 60 75

Parameter Symbol Unit Note

Min Max Min Max Min Max

CAS latency=3 5 6 7.5

CLK cycle time tCC 1000 1000 1000 ns 1

CAS latency=2 - 10 10

CLK to valid CAS latency=3 - 4.5 - 5 - 5.4

tSAC ns 1,2

output delay CAS latency=2 - - - 6 - 6

Output data CAS latency=3 2 - 2.5 - 3 -

tOH ns 2

hold time CAS latency=2 - - 3 - 3 -

CLK high pulse width tCH 2 - 2.5 - 2.5 - ns 3

CLK low pulse width tCL 2 - 2.5 - 2.5 - ns 3

Input setup time tSS 1.5 - 1.5 - 1.5 - ns 3, 4

Input hold time tSH 1 - 1 - 0.8 - ns 3, 4

CLK to output in Low-Z tSLZ 1 - 1 - 1 - ns 2

CLK to output CAS latency=3 - 4.5 - 5 - 5.4

tSHZ ns

in Hi-Z CAS latency=2 - - - 6 - 6

Notes : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

3. Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

4. tSS applies for address setup time, clock enable setup time, commend setup time and data setup time

tSH applies for address holde time, clock enable hold time, commend hold time and data hold time

DQ BUFFER OUTPUT DRIVE CHARACTERISTICS

Parameter Symbol Condition Min Typ Max Unit Notes

Measure in linear

Output rise time trh 1.37 4.37 Volts/ns 3

region : 1.2V ~ 1.8V

Measure in linear

Output fall time tfh 1.30 3.8 Volts/ns 3

region : 1.2V ~ 1.8V

Measure in linear

Output rise time trh 2.8 3.9 5.6 Volts/ns 1,2

region : 1.2V ~ 1.8V

Measure in linear

Output fall time tfh 2.0 2.9 5.0 Volts/ns 1,2

region : 1.2V ~ 1.8V

Notes : 1. Rise time specification based on 0pF + 50 Ω to VSS, use these values to design to.

2. Fall time specification based on 0pF + 50 Ω to VDD, use these values to design to.

3. Measured into 50pF only, use these values to characterize to.

4. All measurements done with respect to VSS.

11 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

IBIS SPECIFICATION 200MHz/133MHz Pull-up

0 0.5 1 1.5 2 2.5 3 3.5

IOH Characteristics (Pull-up)

0

200MHz/133MHz 200MHz/133MHz

Voltage

Min Max

(V) I (mA) I (mA) -100

3.45 - -1.68

3.30 - -19.11

-200

3.00 -0.35 -51.87

2.70 -3.75 -90.44

mA

2.50 -6.65 -107.31 -300

1.95 -13.75 -137.9

1.80 -17.75 -158.34

-400

1.65 -20.55 -173.6

1.50 -23.55 -188.79

1.40 -26.2 -199.01 -500

1.00 -36.25 -241.15

0.20 -46.5 -351.68

-600

Voltage

IOH Min (200MHz / 133MHz)

IOH Max (200MHz / 133MHz)

200MHz/133MHz Pull-down

IOL Characteristics (Pull-down)

250

200MHz/133MHz 200MHz/133MHz

Voltage

Min Max

(V) I (mA) I (mA)

200

3.45 43.92 155.82

3.30 - -

3.00 43.36 153.72

150

1.95 41.20 148.40

mA

1.80 40.56 146.02

1.65 39.60 141.75

100

1.50 38.40 136.08

1.40 37.28 131.39

1.00 30.08 105.84

50

0.85 26.64 93.66

0.65 21.52 75.25

0.40 14.16 49.14

0

0 0.5 1 1.5 2 2.5 3 3.5

Voltage

IOL Min (200MHz / 133MHz)

IOL Max (200MHz / 133MHz)

12 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

Minimum VDD clamp current

VDD Clamp @ CLK, CKE, CS, DQM & DQ (Referenced to VDD)

VDD (V) I (mA)

20

0.0 0.0

0.2 0.0

0.4 0.0

0.6 0.0 15

0.7 0.0

0.8 0.0

0.9 0.0

1.0 0.23 10

mA

1.2 1.34

1.4 3.02

1.6 5.06

1.8 7.35 5

2.0 9.83

2.2 12.48

2.4 15.30

0

2.6 18.31

0 1 2 3

Voltage

I (mA)

Minimum VSS clamp current

VSS Clamp @ CLK, CKE, CS, DQM & DQ

-3 -2 -1 0

VSS (V) I (mA)

-2.6 -57.23 0

-2.4 -45.77

-2.2 -38.26 -10

-2.0 -31.22

-1.8 -24.58

-1.6 -18.37 -20

-1.4 -12.56

-1.2 -7.57 -30

mA

-1.0 -3.37

-0.9 -1.75

-40

-0.8 -0.58

-0.7 -0.05

-0.6 0.0 -50

-0.4 0.0

-0.2 0.0

-60

0.0 0.0

Voltage

I (mA)

13 of 14 Rev. 1.1 February 2006

K4S640832K

K4S641632K Synchronous DRAM

SIMPLIFIED TRUTH TABLE (V=Valid, X=Don′t care, H=Logic high, L=Logic low)

A11,

Command CKEn-1 CKEn CS RAS CAS WE DQM BA0,1 A10/AP Note

A9 ~ A0

Register Mode register set H X L L L L X OP code 1,2

Auto refresh H 3

H L L L H X X

Entry L 3

Refresh Self

L H H H 3

refresh Exit L H X X

H X X X 3

Bank active & row addr. H X L L H H X V Row address

Read & Auto precharge disable L Column 4

column address H X L H L H X V address

Auto precharge enable H 4,5

Write & Auto precharge disable L Column 4

column address H X L H L L X V address

Auto precharge enable H 4,5

Burst stop H X L H H L X X 6

Bank selection V L

Precharge H X L L H L X X

All banks X H

H X X X

Clock suspend or Entry H L X

L V V V X

active power down

Exit L H X X X X X

H X X X

Entry H L X

L H H H

Precharge power down mode X

H X X X

Exit L H X

L V V V

DQM H X V X 7

H X X X

No operation command H X X X

L H H H

Notes : 1. OP Code : Operand code

A0 ~ A11 & BA0 ~ BA1 : Program keys. (@ MRS)

2. MRS can be issued only at all banks precharge state.

A new command can be issued after 2 CLK cycles of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto".

Auto/self refresh can be issued only at all banks precharge state.

4. BA0 ~ BA1 : Bank select addresses.

If both BA0 and BA1 are "Low" at read, write, row active and precharge, bank A is selected.

If both BA0 is "Low" and BA1 is "High" at read, write, row active and precharge, bank B is selected.

If both BA0 is "High" and BA1 is "Low" at read, write, row active and precharge, bank C is selected.

If both BA0 and BA1 are "High" at read, write, row active and precharge, bank D is selected.

If A10/AP is "High" at row precharge, BA0 and BA1 is ignored and all banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read/write command can be issued after the end of burst.

New row active of the associated bank can be issued at tRP after the end of burst.

6. Burst stop command is valid at every burst length.

7. DQM sampled at positive going edge of a CLK and masks the data-in at the very CLK (Write DQM latency is 0),

but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

14 of 14 Rev. 1.1 February 2006

You might also like

- XMTG 7000 Programmer User Manual PDFDocument17 pagesXMTG 7000 Programmer User Manual PDFCường Mchw100% (1)

- A729000 Control Unit Operation ManualDocument27 pagesA729000 Control Unit Operation Manualjohn castillo100% (4)

- Yr1030 en (Draft)Document10 pagesYr1030 en (Draft)Cường Mchw100% (1)

- E09A92GADocument1 pageE09A92GACường Mchw100% (1)

- How To Install and Run Android x86 On VirtualBoxDocument13 pagesHow To Install and Run Android x86 On VirtualBoxalfarysiNo ratings yet

- 056-095 Remote Start Input FunctionsDocument2 pages056-095 Remote Start Input FunctionsOsvaldo ChimbasNo ratings yet

- 256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Document14 pages256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Cường MchwNo ratings yet

- Sb5101 Samsung UpgradeDocument14 pagesSb5101 Samsung Upgradejohnny-lawless3277No ratings yet

- K4S561632EDocument15 pagesK4S561632ELelik GhhNo ratings yet

- 64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Document12 pages64Mb H-Die (x32) SDRAM Specification: Revision 1.3 February 2004Luis AntunesNo ratings yet

- 013 - k4s64xx32n - Rev111 RAM DinámicaDocument15 pages013 - k4s64xx32n - Rev111 RAM DinámicanachcratchNo ratings yet

- Data SheetDocument11 pagesData SheetManuel VillarNo ratings yet

- Iiic - CC: 128Mb K-Die SDRAM SpecificationDocument15 pagesIiic - CC: 128Mb K-Die SDRAM SpecificationTan Hung LuuNo ratings yet

- Advanced Tech Mapping Supp4Document8 pagesAdvanced Tech Mapping Supp48711110029No ratings yet

- KTLP 3616Document10 pagesKTLP 3616Ismael silvaNo ratings yet

- Dimensions in MM (Inches) .: TO39 (TO205AD) PinoutsDocument2 pagesDimensions in MM (Inches) .: TO39 (TO205AD) PinoutsJinsmon AlexNo ratings yet

- Detail 02 L Vinkel Var 1Document14 pagesDetail 02 L Vinkel Var 1BrcakNo ratings yet

- Mechanical Data: D (R-PDSO-G ) Plastic Small-Outline PackageDocument2 pagesMechanical Data: D (R-PDSO-G ) Plastic Small-Outline PackageEva AvilésNo ratings yet

- Voltage Mode Multiplying DAC Reference DesignDocument16 pagesVoltage Mode Multiplying DAC Reference DesignMouloud IbelaidenNo ratings yet

- ECS RS880PM-AM Rev 1.0 СхемаDocument37 pagesECS RS880PM-AM Rev 1.0 СхемаA2139No ratings yet

- 2 N 2243 ADocument1 page2 N 2243 AAhmed EL-arabyNo ratings yet

- High-Friquency General-Purpose Amplifier Applications: Package Dimensions FeaturesDocument5 pagesHigh-Friquency General-Purpose Amplifier Applications: Package Dimensions FeaturesArturo ArmuellesNo ratings yet

- High Performance CMOS 5 X 7 Alphanumeric Displays: Technical DataDocument16 pagesHigh Performance CMOS 5 X 7 Alphanumeric Displays: Technical DataEmanuel OanceaNo ratings yet

- User's Manual of Haiwell Classic PLC Analog ModuleDocument18 pagesUser's Manual of Haiwell Classic PLC Analog ModuleMayte GomezNo ratings yet

- Molding Power Inductors: FeaturesDocument5 pagesMolding Power Inductors: FeaturesPușcă MartinNo ratings yet

- SML-D14x (C) Series: Data SheetDocument10 pagesSML-D14x (C) Series: Data SheetKhadija EL ATRASSINo ratings yet

- Surface Roughness Conversion Chart Tables - Engineers EdgeDocument10 pagesSurface Roughness Conversion Chart Tables - Engineers Edgejames.anitNo ratings yet

- pdf-userManuals-03-Product Manual - Loop Powered 4-20 Ma Output Vibration SensorDocument8 pagespdf-userManuals-03-Product Manual - Loop Powered 4-20 Ma Output Vibration SensorTAHRI BELGACEMNo ratings yet

- 413 05857 0 LC35256FT 70uDocument7 pages413 05857 0 LC35256FT 70uA.hNo ratings yet

- SunonDocument4 pagesSunonEmerson Müller Juarez AvilaNo ratings yet

- KTLP3616 COSMOElectronicsCorporationDocument10 pagesKTLP3616 COSMOElectronicsCorporationaltakadum78No ratings yet

- Memory Module Specification: KHX6400D2LLK2/2GDocument2 pagesMemory Module Specification: KHX6400D2LLK2/2GΒΙΒΗ ΓΚΑΣΙΩΝΗNo ratings yet

- Heds-9140#i00 Heds-9140#i00Document14 pagesHeds-9140#i00 Heds-9140#i00LuisEdgarMartinezAvilaNo ratings yet

- 步进电机详细参数资料Document13 pages步进电机详细参数资料Andy YouQuanTexNo ratings yet

- 40 X 40 X 10 MM SERIES: Dimensions DrawingDocument9 pages40 X 40 X 10 MM SERIES: Dimensions DrawingVíctor RomeuNo ratings yet

- TS12864c-5 YGDocument13 pagesTS12864c-5 YGHéctor Eduardo Urbina UrbinaNo ratings yet

- SANMOTION K Series DC Servo MotorDocument5 pagesSANMOTION K Series DC Servo MotorNisar AhmedNo ratings yet

- Power Scaling of Kw-Diode Lasers Optimized For Material Processing ApplicationsDocument9 pagesPower Scaling of Kw-Diode Lasers Optimized For Material Processing ApplicationsDu RoyNo ratings yet

- Photodarlington Optocouplers (No Base Connection) : DescriptionDocument8 pagesPhotodarlington Optocouplers (No Base Connection) : DescriptionThomas ThomasNo ratings yet

- Led2 1.2Document12 pagesLed2 1.2EduardoNo ratings yet

- 10/100 PC Card LAN Magnetic Modules: MechanicalsDocument2 pages10/100 PC Card LAN Magnetic Modules: MechanicalsAbdelrhman ElsayedNo ratings yet

- Optically Coupled 20 Ma Current Loop Receiver: HCPL-4200Document13 pagesOptically Coupled 20 Ma Current Loop Receiver: HCPL-4200bigm94iNo ratings yet

- Characteristics DF Pipingmateriais SteelpipeDocument4 pagesCharacteristics DF Pipingmateriais SteelpipeMauricio RodriguesNo ratings yet

- Snap-In Mounting: Specifications IntroductionsDocument2 pagesSnap-In Mounting: Specifications IntroductionsMangueras Hidraulicas H-RojasNo ratings yet

- TACT Switch TDSDocument3 pagesTACT Switch TDSHareram ShuklaNo ratings yet

- Vishay 1445Document2 pagesVishay 1445rogerNo ratings yet

- Surface Roughness-Conersion Chart TableDocument2 pagesSurface Roughness-Conersion Chart TableAnonymous w1yuNZTqONNo ratings yet

- Di100s SeriesDocument5 pagesDi100s Seriesivanshitov2015No ratings yet

- Varactor Diode For FM Receiver Electronic Tuning ApplicationsDocument3 pagesVaractor Diode For FM Receiver Electronic Tuning ApplicationsАндрей ПоляковNo ratings yet

- Trubka Ocel ST 37 4 Bezesva Cerna Uk Katalogovy ListDocument2 pagesTrubka Ocel ST 37 4 Bezesva Cerna Uk Katalogovy ListVratislav Němec ml.No ratings yet

- 135616ds k4s56xx32n Rev10Document18 pages135616ds k4s56xx32n Rev10dmitry esaulkovNo ratings yet

- Crystek Corporation: Voltage Controlled Oscillator-VCO CVCO55CL-0805-0900Document2 pagesCrystek Corporation: Voltage Controlled Oscillator-VCO CVCO55CL-0805-0900Gerard PabloNo ratings yet

- Bu 9348 KDocument3 pagesBu 9348 KbinkyfishNo ratings yet

- Pg240128a DisplayDocument1 pagePg240128a Displaybancadasol03No ratings yet

- Optically Coupled 20 Ma Current Loop Transmitter: HCPL-4100Document13 pagesOptically Coupled 20 Ma Current Loop Transmitter: HCPL-4100bigm94iNo ratings yet

- Samsung SPMWHT541ML5XATMS6 DatasheetDocument36 pagesSamsung SPMWHT541ML5XATMS6 Datasheetstephane.krycNo ratings yet

- 14PM M201V NMBDocument1 page14PM M201V NMBCristianEnacheNo ratings yet

- Av02 0565en - Ds - Acpl m43t - 2015 10 19Document10 pagesAv02 0565en - Ds - Acpl m43t - 2015 10 19Denis CarlosNo ratings yet

- sj5 43502pmDocument1 pagesj5 43502pmthatatkdferreiraNo ratings yet

- CHF190104xBF Series 800 W Power RF Flanged Chip Termination/ResistorDocument1 pageCHF190104xBF Series 800 W Power RF Flanged Chip Termination/ResistorMPIMLACNo ratings yet

- T.D.A 04H0SK1RDocument1 pageT.D.A 04H0SK1Rmichael luqueNo ratings yet

- PNP Silicon Epitaxial Base Power Tansistors: ApplicationsDocument2 pagesPNP Silicon Epitaxial Base Power Tansistors: ApplicationsGabriel GaniNo ratings yet

- 32data Sheet lm561c Rev.7.0Document37 pages32data Sheet lm561c Rev.7.0stephane.krycNo ratings yet

- High-Performance. Advanced Scan ControlDocument2 pagesHigh-Performance. Advanced Scan ControlCường MchwNo ratings yet

- UX-G5B Data Sheet: V 7.5 KV, I 350 Ma High-Frequency and High-Voltage Rectifier DiodeDocument5 pagesUX-G5B Data Sheet: V 7.5 KV, I 350 Ma High-Frequency and High-Voltage Rectifier DiodeCường MchwNo ratings yet

- Sequencing With Next-Generation Non-Signaling Test EquipmentDocument7 pagesSequencing With Next-Generation Non-Signaling Test EquipmentCường MchwNo ratings yet

- UX FOB HVComponentAssociatesDocument1 pageUX FOB HVComponentAssociatesCường MchwNo ratings yet

- Power - Integrations:TO-220: Title: Class D AmplifierDocument1 pagePower - Integrations:TO-220: Title: Class D AmplifierCường Mchw100% (1)

- Acoustic Wave Music System IIDocument30 pagesAcoustic Wave Music System IICường MchwNo ratings yet

- BOM For Class-D Amplifier: Nr. Designator Package Quantity DesignationDocument1 pageBOM For Class-D Amplifier: Nr. Designator Package Quantity DesignationCường MchwNo ratings yet

- 256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Document14 pages256Mb E-Die SDRAM Specification: Revision 1.5 May 2004Cường MchwNo ratings yet

- 8202RDocument5 pages8202RCường MchwNo ratings yet

- Downloaded From Manuals Search EngineDocument28 pagesDownloaded From Manuals Search EngineCường MchwNo ratings yet

- Onvex: Catalogue 2005Document52 pagesOnvex: Catalogue 2005Cường MchwNo ratings yet

- GM 9.2 SchematicDocument1 pageGM 9.2 SchematicCường MchwNo ratings yet

- VIA+EPIA+M Datasheet v090217Document2 pagesVIA+EPIA+M Datasheet v090217rekluzoNo ratings yet

- Sheet #3Document7 pagesSheet #3Youssef EbrahimNo ratings yet

- METSEPM5560: Product Data SheetDocument3 pagesMETSEPM5560: Product Data SheetDedeKurniawanNo ratings yet

- Current Mirrors II - Source Degeneration: in This LectureDocument2 pagesCurrent Mirrors II - Source Degeneration: in This LectureHassan FarssiNo ratings yet

- BMW R 1200 RT - Nov. 2004 Onward - Model Code 0368Document174 pagesBMW R 1200 RT - Nov. 2004 Onward - Model Code 0368Vlad SusmanNo ratings yet

- Oscillation Waves 09-11 MC 2Document23 pagesOscillation Waves 09-11 MC 2AllyLauNo ratings yet

- A Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode SimulationDocument30 pagesA Tutorial: Transient Domain Flip-Flop Models For Mixed-Mode Simulationiarcad9403No ratings yet

- Smith Chart in Color - 2Document1 pageSmith Chart in Color - 2Andro Elnatan HarianjaNo ratings yet

- RB411UAHL Repair InstructionsDocument9 pagesRB411UAHL Repair InstructionscontatoseconnectNo ratings yet

- Switches and IndicatorsDocument88 pagesSwitches and IndicatorsMukhtar KhadyrbergenovNo ratings yet

- Instruction Manual Alfa Laval Level Switch (Recuperado) (Recuperado) (Recuperado)Document8 pagesInstruction Manual Alfa Laval Level Switch (Recuperado) (Recuperado) (Recuperado)Natsu HgkNo ratings yet

- Datasheet en 20170526Document10 pagesDatasheet en 20170526LODELBARRIO RDNo ratings yet

- DebugDocument13 pagesDebugwsosaNo ratings yet

- iTM Plus Adaptor: Installation ManualDocument36 pagesiTM Plus Adaptor: Installation Manuallucio ruiz jrNo ratings yet

- CD Floppy, Hard Disk DriveDocument76 pagesCD Floppy, Hard Disk DriveIam BeccaNo ratings yet

- MicrostripantennaDocument47 pagesMicrostripantennaNuzhath FathimaNo ratings yet

- Mve Kimera 1 - A14-132 - Dokumentace enDocument62 pagesMve Kimera 1 - A14-132 - Dokumentace enshahramkh59No ratings yet

- WEEK 11 F TOPIC11 RADAR ARPA Different Signals 3Document7 pagesWEEK 11 F TOPIC11 RADAR ARPA Different Signals 3Daniel OrenaNo ratings yet

- Elevator System Modellingand Simulation Paperrev 6140704Document11 pagesElevator System Modellingand Simulation Paperrev 6140704Prajwal TeppalwarNo ratings yet

- DH48SDocument2 pagesDH48SGold JoshuaNo ratings yet

- PM240P 2 FSD FSG 0521Document2 pagesPM240P 2 FSD FSG 0521SANTIAGO JOSUE FARFAN TRUJILLONo ratings yet

- En 305 Magflux Datasheet 1711Document23 pagesEn 305 Magflux Datasheet 1711Gerrard ArchuletaNo ratings yet

- A Buck Converter Based On PID Controller For Voltage Step - Down Application.... Trae Un Circuito Buck Aplicado en MatlabDocument4 pagesA Buck Converter Based On PID Controller For Voltage Step - Down Application.... Trae Un Circuito Buck Aplicado en MatlabDavid RomeroNo ratings yet

- 362 Ps 6 SolnsDocument13 pages362 Ps 6 Solnsrameshaarya99No ratings yet

- Change Log PDFDocument16 pagesChange Log PDFCesar MartinezNo ratings yet

- Dragomir Et Ski y 2014Document14 pagesDragomir Et Ski y 2014kalokosNo ratings yet