Professional Documents

Culture Documents

FSMD RTL 1-25 PDF

FSMD RTL 1-25 PDF

Uploaded by

KhalidTaherAl-HussainiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FSMD RTL 1-25 PDF

FSMD RTL 1-25 PDF

Uploaded by

KhalidTaherAl-HussainiCopyright:

Available Formats

Hardware Design with VHDL Register Transfer Methodology I ECE 443

Register Transfer Methodology: Principle

We typically use algorithms to accomplish complex tasks

Although it is common to execute algorithms on a GPU, a hardware implementation

is sometimes needed because of performance constraints

RT methodology is a design process that describes system operation by a sequence of

data transfers and manipulations among registers

This methodology supports the sequential execution, e.g., data and control dependen-

cies, required to carry out an algorithm

Consider an algorithm that computes the sum of 4 numbers, divides by 8 and rounds

the result to the nearest integer

size = 4;

sum = 0;

for i in (0 to size-1) do

{ sum = sum + a(i); }

ECE UNM 1 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

Register Transfer Methodology: Principle

q = sum/8;

r = sum rem 8;

if (r > 3)

{ q = q + 1; }

outp = q;

Algorithm characteristics:

• Algorithms use variables, memory locations with a symbolic addresses

Variables can be used to store intermediate results

• Algorithms are executed sequentially and the order of the steps is important

As we know, variables and sequential execution are supported as a special case and

are encapsulated inside a process

However, variables are NOT treated as symbolic names for memory locations!

We also note that the sequential semantics of an algorithm are very different from the

concurrent model of hardware

ECE UNM 2 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

Register Transfer Methodology: Principle

What we have learned so far is how to transfer sequential execution into a struc-

tural data flow, where the sequence is embedded in the ’flow of data’

This is accomplished by mapping an algorithm into a system of cascading hard-

ware blocks, where each block represents a statement in the algorithm

The previous algorithm can be unrolled into a data flow diagram

sum <= 0;

sum0 <= a(0);

sum1 <= sum0 + a(1);

sum2 <= sum1 + a(2);

sum3 <= sum2 + a(3);

q <= "000" & sum3(8 downto 3);

r <= "00000" & sum3(2 downto 0);

outp <= q + 1 when (r > 3) else

q;

Note that this is very different from the algorithm -- the circuit is a pure combina-

tional (and parallel) logic circuit with NO memory elements

ECE UNM 3 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

Register Transfer Methodology: Principle

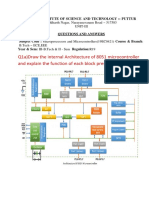

Block diagram

The problem is the structural data flow implementation is that it can only be applied

to trivial problems and is not flexible (is specific to an array of 4 values)

A better implementation is to share one adder in a time-multiplexed manner (as is

done on a GPU)

Register Transfer Methodology introduces hardware that matches the variable and

sequential execution model

• Registers are used to store intermediate data (model symbolic variables)

• A datapath is used to implement the operations

• A control path (FSM) is used to specify the order of register operations

ECE UNM 4 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD

The control, data path and registers are implemented as an FSMD (FSM with a data-

path)

FSMDs are key to realizing RT methodology

The basic action in RT methodology is the register transfer operation:

r dest ← f ( r src1, r src2, …, r src3 )

The destination register is shown on the left while the source registers are listed on

the right

The function f uses the contents of the source registers, plus external outputs in some

cases

Difference between an algorithm and an RT register is the implicit embedding of clk

• At the rising edge of the clock, the output of registers rsrc1, rsrc2 become available

• The output are passed to a combinational circuit that represents f( )

• At the next rising edge of the clock, the result is stored into rdest

ECE UNM 5 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD

The function f() can be any expression that is representable by a combinational circuit

r←1

r←r

r0 ← r1

n←n–1

y←a⊕b⊕c⊕d

2 2

s←a +b

Note that we will continue to use the notation _reg and _next for the current output

and next input of a register

The notation

r1 ← r1 + r2

is translated as

r1_next <= r1_reg + r2_reg;

r1_reg <= r1_next; -- on the next rising edge of clk

Block diagram and timing diagram are shown below

ECE UNM 6 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD

Be sure to study this carefully because it is heavily used in digital systems

r ← r1 + r2

Multiple RT operations

An algorithm consists of many steps and a destination register my be loaded

with different values over time, e.g., initialized to 0, stores result of addition,

etc.

ECE UNM 7 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD

Consider the following sequence of operations

r1 ← 1

r1 ← r1 + r2

r1 ← r1 + 1

r1 ← r1

Since r1 is the destination of multiple operations, we need a MUX to route the proper

value to its input

An FSM is used to drive the control signals so that the sequence of operations are

carried out in the order given

The FSM can also implement conditional execution based, e.g., on external signals

ECE UNM 8 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD

Note that the state transitions take place on the rising edge of clk -- the same instant

that the RT registers are updated

So we can embed the RT operations within the state boxes/arcs of the FSM

An extended ASM chart known as ASMD (ASM with datapath) chart can be used to

represent the FSMD

**

delayed

store

operation

** IMPORTANT: the new value of r1 is only available when the FSM exits the s1 state

ECE UNM 9 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD

NOTE: When a register is NOT being updated with a new value, it is assumed that it

maintains its current value, i.e.,

r1 ← r1 These actions are NOT shown in the ASMD/state chart

Conceptual block diagram of an FSMD

Data Path

Regular sequential circuit

Study and become familiar

with the input/output

signals of both modules

Control Path

Random sequential circuit

ECE UNM 10 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

Repetitive addition multiplier

We built a combinational multiplier earlier which used multiple adders in a data-

flow configuration

It’s also possible to build it using one adder and a sequential algorithm

Basic algorithm: 7*5 = 7+7+7+7+7

if (a_in=0 or b_in=0) then

{ r = 0; }

else

{

a = a_in;

n = b_in;

r = 0;

while (n != 0)

{

r = r + a;

ECE UNM 11 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

n = n - 1;

}

}

return(r);

This code is a better match to an ASMD because ASMD does not have a loop con-

struct

if (a_in = 0 or b_in = 0) then

{ r = 0; }

else

{

a = a_in;

n = b_in;

r = 0;

op: r = r + a;

n = n - 1;

if (n = 0) then

{ goto stop; }

ECE UNM 12 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

else

{ goto op; }

}

stop: return(r);

To implement this in hardware, we must first define the I/O signals

• a_in, b_in: 8-bit unsigned input

• clk, reset: 1-bit input

• start: 1-bit command input

• r: 16-bit unsigned output

• ready: 1-bit status output -- asserted when unit has completed and is ready again

The start and ready signals are added to support sequential operation

When this unit is embedded in a larger design, and the main system wants to perform

multiplication

• It checks ready

• If ’1’, it places inputs on a_in and b_in and asserts the start signal

ECE UNM 13 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

The ASMD uses n, a and r data registers to emulate the three variables

Decision boxes are used to

implement the if stmts

One difference between the

pseudo code and the ASMD

is the parallelism available

in the latter

When RT operations are

scheduled in the same state

they execute in parallel

in that clock cycle, e.g., op

state

Multiple operations can be

scheduled in the same state

if enough hardware resources

are available and there are

no data dependencies

ECE UNM 14 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

With the ASMD chart available, we can refine the original block diagram

We first divide the system into a data path and a control path

For the control path, the input signals are start, a_is_0, b_is_0 and count_0 -- the first

is an external signal, the latter three are status signals from the data path

These signals constitute the inputs to the FSM and are used in the decision boxes

The output of the control path are ready and control signals that specify the RT oper-

ations of the data path

In this example, we use the state register as the output control signals

Construction of the data path is easier if it is handled as follows:

• List all RT operations

• Group RT operation according to the destination register

• Add combinational circuit/mux

• Add status circuits

ECE UNM 15 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

For example

• RT operation with the r register

r ← r (in the idle state)

r ← 0 (in the load and op states)

r ← r + a (in the op state)

• RT operations with the n register

n ← n (in the idle state)

n ← b_in (in the load and ab0 state)

n ← n – 1 (in the op state)

• RT operations with the a register

a ← a (in the idle and op states)

a ← a_in (in the load and ab0 states)

Note that the default operations MUST be included to build the proper data path

ECE UNM 16 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

Let’s consider the circuit associated with the r register

The three possible sources, 0, r and r+a are selected using a MUX

The select signals are labeled symbolically with the state names

The routing specified matches that given on the previous slide

We can repeat this process for the other two registers and combine them

The status signals are implemented using three comparators

ECE UNM 17 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

The entire control and data path

Note that some elements

are more complicated than

necessary

For example, the a_next

signal can be replaced

with a register with an

enable signal

Don’t worry, the synthesis

tool will optimize this

design

ECE UNM 18 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

The VHDL code follows the block diagram and is divided into seven blocks

• Control path state registers

• Control path next-state logic

• Control path output logic

• Data path data registers

• Data path functional units

• Data path routing network

• Data path status circuit

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity seq_mult is

port(

clk, reset: in std_logic;

start: in std_logic;

a_in, b_in: in std_logic_vector(7 downto 0);

ECE UNM 19 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

ready: out std_logic;

r: out std_logic_vector(15 downto 0)

);

end seq_mult;

architecture mult_seg_arch of seq_mult is

constant WIDTH: integer:=8;

type state_type is (idle, ab0, load, op);

signal state_reg, state_next: state_type;

signal a_is_0, b_is_0, count_0: std_logic;

signal a_reg, a_next: unsigned(WIDTH-1 downto 0);

signal n_reg, n_next: unsigned(WIDTH-1 downto 0);

signal r_reg, r_next: unsigned(2*WIDTH-1 downto 0);

signal adder_out: unsigned(2*WIDTH-1 downto 0);

signal sub_out: unsigned(WIDTH-1 downto 0);

begin

ECE UNM 20 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

-- control path: state register

process(clk, reset)

begin

if (reset = ’1’) then

state_reg <= idle;

elsif (clk’event and clk = ’1’) then

state_reg <= state_next;

end if;

end process;

-- control path: next-state/output logic

process(state_reg, start, a_is_0, b_is_0, count_0)

begin

case state_reg is

when idle =>

if (start = ’1’) then

if (a_is_0 = ’1’ or b_is_0 = ’1’) then

state_next <= ab0;

ECE UNM 21 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

else

state_next <= load;

end if;

else

state_next <= idle;

end if;

when ab0 =>

state_next <= idle;

when load =>

state_next <= op;

when op =>

if (count_0 = ’1’) then

state_next <= idle;

else

state_next <= op;

end if;

end case;

end process;

ECE UNM 22 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

-- control path: output logic

ready <= ’1’ when state_reg=idle else ’0’;

-- data path: data register

process(clk, reset)

begin

if (reset = ’1’) then

a_reg <= (others=>’0’);

n_reg <= (others=>’0’);

r_reg <= (others=>’0’);

elsif (clk’event and clk=’1’) then

a_reg <= a_next;

n_reg <= n_next;

r_reg <= r_next;

end if;

end process;

ECE UNM 23 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

-- data path: routing multiplexer

process(state_reg, a_reg, n_reg, r_reg,

a_in, b_in, adder_out, sub_out)

begin

case state_reg is

when idle =>

a_next <= a_reg;

n_next <= n_reg;

r_next <= r_reg;

when ab0 =>

a_next <= unsigned(a_in);

n_next <= unsigned(b_in);

r_next <= (others => ’0’);

when load =>

a_next <= unsigned(a_in);

n_next <= unsigned(b_in);

r_next <= (others => ’0’);

when op =>

ECE UNM 24 (11/23/09)

Hardware Design with VHDL Register Transfer Methodology I ECE 443

FSMD Design Examples

a_next <= a_reg;

n_next <= sub_out;

r_next <= adder_out;

end case;

end process;

-- data path: functional units

adder_out <= ("00000000" & a_reg) + r_reg;

sub_out <= n_reg - 1;

-- data path: status

a_is_0 <= ’1’ when a_in = "00000000" else ’0’;

b_is_0 <= ’1’ when b_in = "00000000" else ’0’;

count_0 <= ’1’ when n_next = "00000000" else ’0’;

-- data path: output

r <= std_logic_vector(r_reg);

end mult_seg_arch;

ECE UNM 25 (11/23/09)

You might also like

- Full Download Test Bank For Operating Systems Internals and Design Principles 7th Edition William Stallings PDF Full ChapterDocument36 pagesFull Download Test Bank For Operating Systems Internals and Design Principles 7th Edition William Stallings PDF Full Chapterbailey.chaus0dqj100% (25)

- Lecture 1 - Introduction: Arto Perttula TIE-50206 Logic Synthesis Tampere University of Technology 2017-2018Document57 pagesLecture 1 - Introduction: Arto Perttula TIE-50206 Logic Synthesis Tampere University of Technology 2017-2018antoniocljNo ratings yet

- Chapter 7: Register Transfer: ObjectivesDocument7 pagesChapter 7: Register Transfer: ObjectivesSteffany RoqueNo ratings yet

- FSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Document25 pagesFSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNo ratings yet

- Project FileDocument131 pagesProject FileshaanjalalNo ratings yet

- Lec20 RTL DesignDocument40 pagesLec20 RTL DesignVrushali patilNo ratings yet

- Atrenta Tutorial PDFDocument15 pagesAtrenta Tutorial PDFTechy GuysNo ratings yet

- Lecture 5 - Combinatorial and Sequential LogicDocument76 pagesLecture 5 - Combinatorial and Sequential LogicantoniocljNo ratings yet

- Chapter 8 - CPU PerformanceDocument40 pagesChapter 8 - CPU PerformanceNurhidayatul FadhilahNo ratings yet

- DSD 12 Synchronous DesignDocument9 pagesDSD 12 Synchronous DesignDavis AbrahamNo ratings yet

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaNo ratings yet

- Commands Used in Soc Workshop PDFDocument16 pagesCommands Used in Soc Workshop PDFabhishek bhandareNo ratings yet

- 03b - FIE - Parcial #3 PLD - Resumen 04c 09Document36 pages03b - FIE - Parcial #3 PLD - Resumen 04c 09amilcar93No ratings yet

- Chapter 6 - IO (Part 2)Document42 pagesChapter 6 - IO (Part 2)Nurhidayatul FadhilahNo ratings yet

- SOC TestingDocument27 pagesSOC TestingMaria AllenNo ratings yet

- 2.sys Bus ArchDocument14 pages2.sys Bus ArchChar MondeNo ratings yet

- Testability in EOCHL (And Beyond ) : Vladimir ZivkovicDocument24 pagesTestability in EOCHL (And Beyond ) : Vladimir ZivkovicsenthilkumarNo ratings yet

- Bus System & Data TransferDocument5 pagesBus System & Data Transferlmehta16No ratings yet

- ARM Based Development Course Summary-MouliSankaranDocument39 pagesARM Based Development Course Summary-MouliSankaranChandramouleeswaran SankaranNo ratings yet

- Haps-54 March2009 ManualDocument74 pagesHaps-54 March2009 Manualjohn92691No ratings yet

- NBB - Module II - System PartitioingDocument60 pagesNBB - Module II - System Partitioing20D076 SHRIN BNo ratings yet

- Partitioning An ASICDocument6 pagesPartitioning An ASICSwtz ZraonicsNo ratings yet

- Low Power VLSI Design: J.Ramesh ECE Department PSG College of TechnologyDocument146 pagesLow Power VLSI Design: J.Ramesh ECE Department PSG College of TechnologyVijay Kumar TNo ratings yet

- Unit - IV: Input - OutputDocument50 pagesUnit - IV: Input - Outputkarvind08No ratings yet

- CPFDocument47 pagesCPFcknishuNo ratings yet

- 5 - Internal MemoryDocument22 pages5 - Internal Memoryerdvk100% (1)

- tc1 6 Architecture Vol1Document225 pagestc1 6 Architecture Vol1Neelakandan Natarajan100% (1)

- Buffer InsertionDocument47 pagesBuffer InsertionAkshay DesaiNo ratings yet

- Zynq 7000 TRMDocument1,770 pagesZynq 7000 TRMSambhav VermanNo ratings yet

- ASIC TimingDocument54 pagesASIC TimingKrishna MohanNo ratings yet

- Arduino-Based Embedded System ModuleDocument8 pagesArduino-Based Embedded System ModuleIJRASETPublicationsNo ratings yet

- Image Cryptography Design Based On Nano AES Security AlgorithmDocument6 pagesImage Cryptography Design Based On Nano AES Security AlgorithmIJRASETPublicationsNo ratings yet

- SDC PDFDocument2 pagesSDC PDFCharan UkkuNo ratings yet

- 05 Systemc TutorialDocument32 pages05 Systemc TutorialjasonturfNo ratings yet

- Unit 1 Computer ArchitectureDocument36 pagesUnit 1 Computer ArchitectureAnshulNo ratings yet

- Power Dissipation in CMOS Circuits: Advanced VLSI EEE 6405 Slide1 Abm Harun-Ur RashidDocument28 pagesPower Dissipation in CMOS Circuits: Advanced VLSI EEE 6405 Slide1 Abm Harun-Ur RashidAbu RaihanNo ratings yet

- Asic Prototyping AldecDocument10 pagesAsic Prototyping AldecKhaled Abou ElseoudNo ratings yet

- Vi Editor Basic CommandsDocument2 pagesVi Editor Basic CommandsJust FriendNo ratings yet

- Coreapb3: Nivin PaulDocument19 pagesCoreapb3: Nivin PaulNivin PaulNo ratings yet

- Simple RTL PipelineDocument7 pagesSimple RTL PipelinepawanzNo ratings yet

- All Ac379 AnDocument43 pagesAll Ac379 AnsajusasiNo ratings yet

- PF Smarttime Sta Ug PDFDocument90 pagesPF Smarttime Sta Ug PDFmsterdangNo ratings yet

- Unit 1and II - ASIC - Design NewDocument120 pagesUnit 1and II - ASIC - Design New20D076 SHRIN BNo ratings yet

- Introduction To The I/O Buses Technical and Historical Background For The I/O BusesDocument9 pagesIntroduction To The I/O Buses Technical and Historical Background For The I/O BusesshankyguptaNo ratings yet

- IO Pad InsertionDocument7 pagesIO Pad InsertionAparna TiwariNo ratings yet

- Topic 6 - Clocking & Met A StabilityDocument9 pagesTopic 6 - Clocking & Met A Stabilityanish1988100% (1)

- VLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaDocument4 pagesVLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaGunapalli venkata saikiranNo ratings yet

- USB To RS-232 ConverterDocument11 pagesUSB To RS-232 Converteryeateshwarrior100% (1)

- System On Chip SoC ReportDocument14 pagesSystem On Chip SoC Reportshahd dawood100% (1)

- DVD2 JNTU Set1 SolutionsDocument12 pagesDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలNo ratings yet

- Introduction To Asics: Ni Logic Pvt. LTD., PuneDocument84 pagesIntroduction To Asics: Ni Logic Pvt. LTD., PuneankurNo ratings yet

- Synth ConstraintsDocument28 pagesSynth ConstraintsCherry AnushaNo ratings yet

- Labview Serial CommunicationDocument0 pagesLabview Serial Communicationmajidkhan04No ratings yet

- Study and Analysis of RTL Verification Tool IEEE ConferenceDocument7 pagesStudy and Analysis of RTL Verification Tool IEEE ConferenceZC LNo ratings yet

- Complex Clocking Situations 010904Document54 pagesComplex Clocking Situations 010904maniNo ratings yet

- Rs-232 To I2c Protocol ConverterDocument4 pagesRs-232 To I2c Protocol ConverterHarsha100% (2)

- A Structured VHDL Design Method-Jiri GaislerDocument28 pagesA Structured VHDL Design Method-Jiri GaislerTho RaNo ratings yet

- Register Transfer Methodology: PracticeDocument54 pagesRegister Transfer Methodology: PracticeSrinivas CherukuNo ratings yet

- 2.2 StructdesDocument28 pages2.2 Structdesjinto007No ratings yet

- 1.0 The Design of Datapath Decoder: Ece 522/computer OrganizationDocument36 pages1.0 The Design of Datapath Decoder: Ece 522/computer OrganizationacapNo ratings yet

- Waside SseDocument20 pagesWaside SsesunbeamNo ratings yet

- Object-Oriented Reverse EngineeringDocument144 pagesObject-Oriented Reverse EngineeringKhalidTaherAl-HussainiNo ratings yet

- 6.cost of Software Quality 0Document19 pages6.cost of Software Quality 0KhalidTaherAl-Hussaini100% (1)

- PS Student Program - Plan GuideDocument5 pagesPS Student Program - Plan GuideKhalidTaherAl-HussainiNo ratings yet

- Ulfc125439 Tiago AlvesDocument100 pagesUlfc125439 Tiago AlvesKhalidTaherAl-HussainiNo ratings yet

- Assessment of Knowledge About Hepatitis Bvirusinfectionand Vaccination StatusDocument61 pagesAssessment of Knowledge About Hepatitis Bvirusinfectionand Vaccination StatusKhalidTaherAl-HussainiNo ratings yet

- Uptake of Hepatitis B Vaccination...Document101 pagesUptake of Hepatitis B Vaccination...KhalidTaherAl-HussainiNo ratings yet

- Lab 1 TutorialDocument14 pagesLab 1 TutorialKhalidTaherAl-HussainiNo ratings yet

- An-Najah National University - Undergraduate Programs - Midwifery - Study PlansDocument4 pagesAn-Najah National University - Undergraduate Programs - Midwifery - Study PlansKhalidTaherAl-HussainiNo ratings yet

- Protocol ArchDocument90 pagesProtocol ArchKhalidTaherAl-HussainiNo ratings yet

- DOCSDB - Academic Program CodesDocument4 pagesDOCSDB - Academic Program CodesKhalidTaherAl-HussainiNo ratings yet

- Turnitin-Training JMUDocument41 pagesTurnitin-Training JMUKhalidTaherAl-HussainiNo ratings yet

- BSC in Doctor of Pharmacy PharmDDocument39 pagesBSC in Doctor of Pharmacy PharmDKhalidTaherAl-HussainiNo ratings yet

- ParallelDocument4 pagesParallelShanntha JoshittaNo ratings yet

- DBSDocument18 pagesDBSHema DarshanaNo ratings yet

- BIOFACE ENGLISH BrochureDocument2 pagesBIOFACE ENGLISH BrochureYOVANY MONTESNEGRONo ratings yet

- XI - CH-3, Conditional and Looping Construct (Assign)Document8 pagesXI - CH-3, Conditional and Looping Construct (Assign)Arun SharmaNo ratings yet

- Task 4: This Task Covers Basic Commands and System Administration in LinuxDocument18 pagesTask 4: This Task Covers Basic Commands and System Administration in LinuxSreelekha GaddagollaNo ratings yet

- g9 Mid Term..computer SDocument4 pagesg9 Mid Term..computer SMarkNo ratings yet

- Linux Scenario QuestionsDocument7 pagesLinux Scenario QuestionsVineet Vidyavilas PathakNo ratings yet

- Assignment DDWD2663Document4 pagesAssignment DDWD2663danishfirhan9No ratings yet

- USER GUIDE - Web - ZERO-Pi - Easy PDFDocument17 pagesUSER GUIDE - Web - ZERO-Pi - Easy PDFfbaldnerNo ratings yet

- Aruba Fabric ComposerDocument6 pagesAruba Fabric Composerfirewall822No ratings yet

- Data Science Workshop BrainovisionDocument25 pagesData Science Workshop BrainovisionDr Sumithabhashini PokuriNo ratings yet

- CloudSwyft Labs Management Platform Student GuideDocument8 pagesCloudSwyft Labs Management Platform Student GuideFundraising MOVeNo ratings yet

- Unit-5 (Cyber Security)Document4 pagesUnit-5 (Cyber Security)tinime3820No ratings yet

- C++ Move Semantics: Michael GopshteinDocument34 pagesC++ Move Semantics: Michael GopshteinSemih YavuzNo ratings yet

- ALV - Word WrapDocument4 pagesALV - Word WrapLaxmikant RathiNo ratings yet

- Practice 18 - Handling Enqueue WaitsDocument7 pagesPractice 18 - Handling Enqueue WaitsAbdo MohamedNo ratings yet

- Secure Workloads VM Series OracleDocument9 pagesSecure Workloads VM Series Oracleneaman_ahmedNo ratings yet

- CNLP 2014 4Document58 pagesCNLP 2014 4Guttula EdukondaluNo ratings yet

- Mme DesignDocument77 pagesMme DesignhariNo ratings yet

- Advanced Java Lab ManualDocument23 pagesAdvanced Java Lab ManualPrakash BhagatNo ratings yet

- What Every Engineer Should Know About Software Engineering Phillip A Laplante Mohamad Kassab Online Ebook Texxtbook Full Chapter PDFDocument68 pagesWhat Every Engineer Should Know About Software Engineering Phillip A Laplante Mohamad Kassab Online Ebook Texxtbook Full Chapter PDFjdssamindbdavdr774100% (7)

- HCIA-Big Data V2.0 Mock ExamDocument6 pagesHCIA-Big Data V2.0 Mock ExamAdeyemiNo ratings yet

- Wt2021 Handout w04 JavaScript BootstrapDocument44 pagesWt2021 Handout w04 JavaScript BootstrapMobewtime StylesNo ratings yet

- COMP 204bundleDocument45 pagesCOMP 204bundleRagnar LothbrokNo ratings yet

- Operating Systems Basics 1.0 Overview Aug 2023Document1 pageOperating Systems Basics 1.0 Overview Aug 2023Ziadi NafaaNo ratings yet

- Blockchain Based Cloud Computing Architecture and Research ChallengesDocument16 pagesBlockchain Based Cloud Computing Architecture and Research Challengesunnati srivastavaNo ratings yet

- 1300Pl CNC Plasma Table: TravelsDocument2 pages1300Pl CNC Plasma Table: TravelsBen LernerNo ratings yet

- SBL Exp5Document6 pagesSBL Exp5Abhishek BapatNo ratings yet

- x530L Series: Stackable Intelligent Layer 3 SwitchesDocument8 pagesx530L Series: Stackable Intelligent Layer 3 SwitchesO-Javier M-ParraNo ratings yet