Professional Documents

Culture Documents

Testway Express Lean Npi Optimizes Test Coverage

Testway Express Lean Npi Optimizes Test Coverage

Uploaded by

aniket pawarCopyright:

Available Formats

You might also like

- Coverage WS OverviewDocument101 pagesCoverage WS OverviewHien HaNo ratings yet

- Netapp Snapmirror ConfigurationDocument62 pagesNetapp Snapmirror ConfigurationNagarajan DNo ratings yet

- Dev 004544Document2 pagesDev 004544William PaivaNo ratings yet

- Fusion QBD Product Development BrochureDocument8 pagesFusion QBD Product Development Brochurexq63x8ggmNo ratings yet

- Logismiko Win Test Analysis V4Document11 pagesLogismiko Win Test Analysis V4Tâm NguyễnNo ratings yet

- Evaluate Test Management SoftwareDocument15 pagesEvaluate Test Management SoftwareKecseg Fonce AndreiNo ratings yet

- Dreams-Testing ApproachesDocument6 pagesDreams-Testing ApproachesleoNo ratings yet

- 5.1 Software Test AutomationDocument20 pages5.1 Software Test Automationudhayan udhaiNo ratings yet

- iTEST PRO (B)Document2 pagesiTEST PRO (B)goofflineNo ratings yet

- Chakshu Sharma: Senior Test EngineerDocument5 pagesChakshu Sharma: Senior Test EngineerRakesh JhalaniNo ratings yet

- Why Sweat The Small Stuff in Functional Test?: 7 Best Practices For Mid-Volume / High-Mix Production TestDocument12 pagesWhy Sweat The Small Stuff in Functional Test?: 7 Best Practices For Mid-Volume / High-Mix Production Testapi-90729201No ratings yet

- Framework For Intelligent and Rapid Execution (FIRE) : Flexi Hybrid Test Automation SolutionsDocument12 pagesFramework For Intelligent and Rapid Execution (FIRE) : Flexi Hybrid Test Automation SolutionsDinesh YepuruNo ratings yet

- 03 Sisman 2023 Product Design and Development Assembly DisassemblyDocument70 pages03 Sisman 2023 Product Design and Development Assembly Disassemblyfarhan srgNo ratings yet

- Analizador System 1Document5 pagesAnalizador System 1Eva Karia colorado MartinezNo ratings yet

- STLC Stage Entry Criteria Activity Exit Criteria DeliverablesDocument10 pagesSTLC Stage Entry Criteria Activity Exit Criteria DeliverablesAnkit TrivediNo ratings yet

- Experienced Resume sampleDocument2 pagesExperienced Resume sampleAmresh PattnaikNo ratings yet

- ISTQB ConceptsDocument41 pagesISTQB ConceptsJackson HernandezNo ratings yet

- Cornerstones Summary by PhaseDocument3 pagesCornerstones Summary by PhaseAbhijat MittalNo ratings yet

- Subra Man I 2014Document6 pagesSubra Man I 2014manojkumarNo ratings yet

- STLC Means "Software Testing Life Cycle". It Involves Following StagesDocument9 pagesSTLC Means "Software Testing Life Cycle". It Involves Following StageskrisnareshNo ratings yet

- Chapter 4 - STLC (Software Testing Life Cycle) Phases, Entry, Exit CriteriaDocument8 pagesChapter 4 - STLC (Software Testing Life Cycle) Phases, Entry, Exit CriteriaAamir AfzalNo ratings yet

- System Verilog Verification BasicsDocument38 pagesSystem Verilog Verification BasicsHardik TrivediNo ratings yet

- Examples Eight VisualCV ResumeDocument2 pagesExamples Eight VisualCV ResumeAlam ZebNo ratings yet

- Implementation MethodologyDocument10 pagesImplementation MethodologyismailalshanulNo ratings yet

- BateriasDocument6 pagesBateriasAnonymous q9c7KY1vNo ratings yet

- Measure. Understand. CommunicateDocument4 pagesMeasure. Understand. CommunicateZoltan FegeteNo ratings yet

- CRDB Konnect - Test StrategyDocument31 pagesCRDB Konnect - Test StrategymsvinuNo ratings yet

- Test Case Design by Means of CTM and CteDocument14 pagesTest Case Design by Means of CTM and Cteapi-3738458No ratings yet

- MindTree Testing BU BrochureDocument4 pagesMindTree Testing BU BrochureTanin ChakrabortyNo ratings yet

- Cost EstimationDocument69 pagesCost EstimationMr. KNo ratings yet

- Software Testing Short NoteDocument17 pagesSoftware Testing Short NoteSudhan SudhanNo ratings yet

- Life Cycle ModelsDocument46 pagesLife Cycle ModelsARINDAM BISWASNo ratings yet

- Delcam - PowerINSPECT 2016 QuickStart OMV EN - 2015Document58 pagesDelcam - PowerINSPECT 2016 QuickStart OMV EN - 2015phạm minh hùngNo ratings yet

- Data Warehouse Testing - Practical ApproachDocument8 pagesData Warehouse Testing - Practical ApproachRahul SharmaNo ratings yet

- Test Case Design Based On Z and The Classification-Tree MethodDocument10 pagesTest Case Design Based On Z and The Classification-Tree MethodCahaya SNo ratings yet

- STLC - Software Testing Life Cycle Phases & Entry, Exit CriteriaDocument9 pagesSTLC - Software Testing Life Cycle Phases & Entry, Exit CriteriasimonaNo ratings yet

- Software Quality Assurance and Software Testing Strategies Session 15 (Tutorial)Document38 pagesSoftware Quality Assurance and Software Testing Strategies Session 15 (Tutorial)michael bennyNo ratings yet

- Manual TestingDocument37 pagesManual Testingapi-3815323100% (4)

- Performance Engineering BasicsDocument16 pagesPerformance Engineering BasicsImpetusNo ratings yet

- 3 YearsExp SeleniumDocument5 pages3 YearsExp Seleniumbkumar.ece91No ratings yet

- Olivier I 2012Document6 pagesOlivier I 2012HakimHabibiNo ratings yet

- GUI Testing On A Product Suite Using On-The-Shelf Testing SoftwareDocument15 pagesGUI Testing On A Product Suite Using On-The-Shelf Testing SoftwareAnubhav JainNo ratings yet

- Framework ChecklistDocument1 pageFramework Checklistichary.chellojiNo ratings yet

- Quality AssuranceDocument23 pagesQuality Assurancesaimanaaz40No ratings yet

- Testing in Software Life CycleDocument24 pagesTesting in Software Life CycleZain ShahidNo ratings yet

- Roles: Unit 4: Workstream OverviewDocument1 pageRoles: Unit 4: Workstream Overviewshree.patil20028558No ratings yet

- SMMT AQMS FMEA Alignment AIAG and VDA - en PDFDocument32 pagesSMMT AQMS FMEA Alignment AIAG and VDA - en PDFNilton de OliveraNo ratings yet

- (Insert Project, Program or Organization Name Here) : State of Michigan Test StrategyDocument22 pages(Insert Project, Program or Organization Name Here) : State of Michigan Test StrategyArminto Natanagari IINo ratings yet

- Unit TestingDocument23 pagesUnit TestingGiridharNo ratings yet

- 04 - ADAS & Autonomous Driving - 2Document28 pages04 - ADAS & Autonomous Driving - 2Oliver TahirNo ratings yet

- Software TestingDocument56 pagesSoftware TestingAnonymous i9tSg4JNo ratings yet

- Fundamentals of Building A Test System CompleteGuideDocument190 pagesFundamentals of Building A Test System CompleteGuideHưng Nguyễn NgọcNo ratings yet

- Soujanya: Professional SummaryDocument3 pagesSoujanya: Professional Summarymunna thoNo ratings yet

- Performance Testing TestRailDocument26 pagesPerformance Testing TestRailfxgbizdcsNo ratings yet

- QC-Gage 40Document2 pagesQC-Gage 40dadiNo ratings yet

- Software Testing Interview Questions You'll Most Likely Be AskedFrom EverandSoftware Testing Interview Questions You'll Most Likely Be AskedNo ratings yet

- 1.1 AlgorithmsDocument68 pages1.1 AlgorithmsJCNo ratings yet

- Lecture 10 Closer Look at Classes, MethodsDocument21 pagesLecture 10 Closer Look at Classes, MethodsKashif MujeebNo ratings yet

- Nte Electronics Actives and Passives 9357002Document3 pagesNte Electronics Actives and Passives 9357002sienkoplaneNo ratings yet

- Single-Phase To Three-Phase Power Converters: State of The ArtDocument16 pagesSingle-Phase To Three-Phase Power Converters: State of The Artnl vinay kumarNo ratings yet

- Moxa Mgate mb3180 mb3280 mb3480 Series Datasheet v1.0Document5 pagesMoxa Mgate mb3180 mb3280 mb3480 Series Datasheet v1.0Nicole FelicianoNo ratings yet

- Basic PPT On Cloud ComputingDocument32 pagesBasic PPT On Cloud ComputingSavyasachi Vats54% (13)

- Poweredge r730 - Owners Manual2 - en UsDocument201 pagesPoweredge r730 - Owners Manual2 - en UsANthonyNo ratings yet

- A53tp50d crdmh1Document234 pagesA53tp50d crdmh1LOUKILkarimNo ratings yet

- Cyber Security Lecture Notes 04Document24 pagesCyber Security Lecture Notes 04Sampath DarshanaNo ratings yet

- Books PHPDocument53 pagesBooks PHPV.M.B.SNo ratings yet

- Toshiba+Placa de Sinal 32AV550T+Ver.+2.00Document11 pagesToshiba+Placa de Sinal 32AV550T+Ver.+2.00Nelson PintoNo ratings yet

- sg246528 - MQ Integrator For zOS PDFDocument392 pagessg246528 - MQ Integrator For zOS PDFecorradiNo ratings yet

- Operational AmplifierDocument85 pagesOperational AmplifierRajatSardanaNo ratings yet

- Ese 570 Mos Inverters: Static CharacteristicsDocument42 pagesEse 570 Mos Inverters: Static CharacteristicsVipul MistryNo ratings yet

- PDRM AssignmentDocument30 pagesPDRM Assignmentdynamic143No ratings yet

- Power System Automation ReportDocument11 pagesPower System Automation ReportSahana P MNo ratings yet

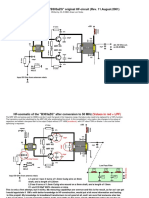

- Zetagi b303 With Board B303azg Original HF Circuit - 59cdb0a71723ddfb65ec727bDocument2 pagesZetagi b303 With Board B303azg Original HF Circuit - 59cdb0a71723ddfb65ec727bHerintsalamaNo ratings yet

- TechRef DCDC ConverterDocument11 pagesTechRef DCDC ConverterАлишер ГалиевNo ratings yet

- Siemens Simatic C7 Control SystemDocument12 pagesSiemens Simatic C7 Control SystemJuan Carlos Barberán MuñozNo ratings yet

- JDBC ExcellentDocument20 pagesJDBC ExcellentNego RemoNo ratings yet

- Sony TVC LCD Ke 32ts2uDocument99 pagesSony TVC LCD Ke 32ts2uGiada SpaccarotellaNo ratings yet

- Gujarat Technological University: Computer Engineering (Software Engineering) (02) Semester IDocument23 pagesGujarat Technological University: Computer Engineering (Software Engineering) (02) Semester IdivyaNo ratings yet

- Office Productivity Week 4Document4 pagesOffice Productivity Week 4Erizza PastorNo ratings yet

- DEFENSEDocument45 pagesDEFENSEClarence PradoNo ratings yet

- Hands On Module PDFDocument71 pagesHands On Module PDFzamani ismailNo ratings yet

- Port AddressDocument25 pagesPort AddressLaiba TahirNo ratings yet

- 555 Timer As Mono Stable Multi VibratorDocument8 pages555 Timer As Mono Stable Multi VibratorchrisgeclayNo ratings yet

- Ethernet DLSW+ Redundancy White PaperDocument12 pagesEthernet DLSW+ Redundancy White Papergborja8881331No ratings yet

Testway Express Lean Npi Optimizes Test Coverage

Testway Express Lean Npi Optimizes Test Coverage

Uploaded by

aniket pawarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Testway Express Lean Npi Optimizes Test Coverage

Testway Express Lean Npi Optimizes Test Coverage

Uploaded by

aniket pawarCopyright:

Available Formats

® Lean NPI optimizes

TestWay Express Test Coverage

TestWay Express is a fully integrated TestWay Express analyzes the num- Key product benefits:

solution that enables electronic manu- ber of defects detected at each stage in

facturers to optimize the design to test the test process and identifies any Ease of Use

flow: shortfall in test coverage and unde- Application wizards guide you through the

Define the manufacturing line; in- tected defects. It allows the computa- project. Add multiple test strategies for

cluding a combination of assem- tion of the IPC metrics such as first project analysis, by simply drag and drop

bly, inspection and test machines. pass yield (FPY), fall-of-rate or es- from the machine list.

Estimate the test coverage of each cape rate by importing the real time

individual stage and optimize the DPMO (Defect Per Million Opportu- Probe allocation & accessibility

combined results. nities) from the manufacturing proc- Place probes aligned to priority rules for

Generate the input files for each ess. The manufacturing test strategy is top or bottom side access using test points,

test stage that reflect the selected tuned to provide the optimal test cov- connectors, vias, THT, SMD, bead probes,

strategy. erage for identifying potential defects. and generate detailed accessibility report.

Measure the real test coverage by

importing the post-debug test pro- Test coverage estimation

gram or coverage data. TestWay Express is built around Maximize test and inspection coverage by

TestWay, the industry leading DfT estimating coverage aligned to selected

Compare the early estimation with

and test coverage analysis tool from test strategies. Perform “what-if” analysis

the actual measured test program

the ASTER product portfolio. to select the optimal test strategy, to

coverage, identifying gaps in the

achieve maximum coverage.

overall strategy.

Eliminate redundant test steps.

Test is essential for improving product

quality by striving to detect and pre- Automated test program creation

EASE OF USE Generate the input files for AOI, AXI,

vent all faults on a product. This

maximizes the number of good prod- A combination of application wizards, BST, ICT, FPT in a matter of minutes or

ucts shipped to the customer. It is im- and drag and drop operations guide hours rather than days.

portant to: you through the project creation to

Define the optimum test strategy enable coverage reports to be gener- Test coverage measurement

to maximize the test coverage. ated in 6 easy steps: Determine the real test coverage and com-

pare against the early estimation to iden-

Produce a test specification docu-

Input the board data. tify areas for improvement.

ment that defines what to test.

Compare the developed tests Modelize the components.

Place the probes. Yield estimation

against the test requirements.

Select the manufacturing strategy Calculate the first pass yield (FPY) by im-

Understand the production process

Generate input files for test & in- porting real time DPMO data for the

capability and determine an ac-

spection machines. manufacturing process to tune the test

ceptable level of defects that can

strategy for optimum test coverage.

be shipped to the customer. Create the test coverage reports.

Wide variety of testers supported

Import & Export test programs from a

wide range of vendors, more than 45 test

& inspection machines supported.

Layout from native CAD formats

Create layout view from standard CAD

formats such as GENCAD, CAMCAD,

FATF, ODB++, or direct from native CAD

layout data.

Component classification

Visualize and edit component attributes

such as part number, shape, class, value,

tolerance, mounted status, etc.

Prompts for missing information.

ASTER Technologies www.aster-technologies.com

INPUT BOARD DATA PLACE THE PROBES

53 CAD importers are available to support layout, schematic Probes are placed by considering the mechanical and design

netlist and schematic graphics. This is a key differentiator as for test (DFT) constraints practiced by respective companies.

other commercial DfT tools work only from the layout stage.

TestWay Express operates from native CAD formats and

ensures the full interoperability between all stages across the

design/manufacturing flow.

CAD data is required to understand the board design. Geo-

metrical and electrical information such as component class,

value, tolerance, package shape, height, centroid and test

probes are automatically extracted.

The probe locations are referenced when assessing the nodal

access for flying probe and in-circuit during test program

generation or coverage analysis.

The Bill Of Material (BOM) can be used to supplement the

CAD data with additional attributes that may not be provided

in the CAD data, such as part number, component descrip- Probe locations may already be defined within the CAD data,

tion, value, mounted status, etc. but there may be insufficient access for total test coverage. In

The board schematic can be imported to allow full interac- which case the probe analyzer can be used to consider alter-

tion between the reports and the viewer, and to visualize any native top and bottom side accessibility options such as

attributes such as test coverage. through hole pins (THT), connectors, SMD pads, vias or bead

probes etc.

MODELIZE THE COMPONENTS

The better the components are modelized, the more accurate

is the test strategy analysis.

The component classificator is a user friendly editor that al-

lows users to: Once the possible probe positions have been analyzed, the

Edit component type, value, tolerances, part number, etc, nail allocation algorithm selects the best of these opportuni-

which is required to determine the type of test that can be ties for the nail positioning according to the preferences set

conducted on the component. by the user.

Define pin function of polarized components and internal

component structures for multi-element components such This allows the estimated coverage to be calculated according

as resistor packs or double diodes. to the real test access.

Import BSDL file to describe the boundary-scan cell

structure of boundary-scan compliant devices. TestWay Express generates a complete set of documenta-

Re-use IBIS, TestWay or test models in order to specify tion:

component and pin attributes. Accessibility report is created to provide a list of the

nodes that do not have access, with reference to the rule

A component wizard is provided to sim- placement violation that prevents access.

plify the component modeling by auto- Check plots and drill files.

matically identifying device classes, im- List of probes and nails in MS-EXCEL format.

porting any available models and extract- Nail retro-annotation back to the schematic. This is help-

ing valuable component information such ful for repair because it allows visualization of nails on

as value, tolerance, shape etc, directly the layout, schematic and virtual schematic viewers with

from the BOM description. full cross-probing.

SELECT MANUFACTURING STRATEGY DESIGN TO TEST

The test strategies simulation results are used to automate the

When deciding on the optimal test flow, it is important to

assembly, test & inspection program generation for assembly

consider all available test and inspection machines such as

machine, in-circuit test (ICT), flying-probe, X-ray, Auto-

AOI, AXI, BST, ICT, FPT and Functional test.

mated Optical Inspection (AOI) and Boundary-Scan test.

The “test line” is easily defined using a simple drag and drop Output processors are available for test & inspection ma-

operation. The theoretical test models for coverage estimation chines from leading suppliers such as Acculogic, Aeroflex,

and the actual test models for coverage measurement, can be Agilent, Asset, Goepel Electronics, JTAG Technologies, Ta-

combined to reflect your manufacturing strategy. kaya, Teradyne/Genrad, Mydata, XJTAG and ...

In addition to creating the test machine input files, TestWay

The gauges provide a quick view of the level of component Express also generates test models for analog multi-element

modeling and board accessibility. To review the respective components and digital models including disable configura-

report, you simply click-on the gauges ! tion.

REAL COVERAGE

The real test coverage is determined after the test has been

developed and debugged, by analyzing the test program or

coverage reports from a wide range of test and inspection sys-

tems used within the industry.

Industry standard coverage metrics such as PPVS (Presence,

Polarity, Value, Solder), or PCOLA/SOQ (Placement, Cor-

rect, Orientation, Live, Alignment / Short, Open, Quality) are

used in calculating both the estimated and real coverage, so

that the same analysis criteria is used in the overall analysis.

COVERAGE ESTIMATION

Each of the theoretical test strategies allows selection of tester

settings from a feature list for a particular test strategy.

In order to provide a more accurate estimation, any specific

test features that are available on the target tester should also

be included in the analysis. This aligns the estimated cover-

age to the real tester coverage.

More than 45 coverage importers are available from the lead-

ing test and inspection suppliers within the industry.

When combining theoretical tester models with the real tester

TestWay Express handles cross optimization along the test program, or report. It allows direct comparison to verify that

line such as Boundary-Scan or AOI that can be used to mini- the completed test program is in alignment with your early

mize the In-Circuit Test or Flying Probe Test. expectations.

The overall coverage is defined by the “board score”

EXPLORE TEST COVERAGE within the top level report. The individual coverage

Once the test strategy is defined and the respective tester set- scores for the respective test strategies are highlighted in

tings are selected, simply press the “Analyze” button to the test line.

launch the analysis and visualize the resultant coverage Individual test reports can be viewed by selecting the re-

across all views and reports. spective tester from the test line.

Navigation is aided by full interactive cross-probing be-

TestWay Express creates a variety of comprehensive HTML tween all the HTML reports, the schematic, layout and

and MS-Excel reports. virtual schematic views.

Board level overview of the combined coverage, or inde- Coverage visualizations are categorized using easy to in-

pendent reports that define the coverage provided by each terpret traffic light color coding.

of the test and inspection machines in the test line.

All components are categorized within the “Device

Type” field. To access the pin level coverage simply se-

lect the device category to drill down to the component

list and select the respective device.

Visit our web site at www.aster-technologies.com for the latest product news.

Copyright © 2011 ASTER Technologies. TestWay, TestWay Express, QuadView and QUAD are trademarks of ASTER Technologies.

All other trademarks mentioned in this document are trademarks of their respective owners.

Corporate Headquarters United Kingdom

ASTER Technologies ASTER Technologies Ltd.

55 bis, rue de Rennes

F35510 Cesson-Sevigne

PO Box 327

Tarporley ASTER Technologies

France Cheshire, CW6 9WD

Phone: +33 (0)2 99 83 01 01 Phone: +44 (0) 1829 261557

Fax: +33 (0)2 99 83 01 00 Mob. +44 (0) 7711 927840

sales@aster-technologies.com sales-UK@aster-technologies.com

You might also like

- Coverage WS OverviewDocument101 pagesCoverage WS OverviewHien HaNo ratings yet

- Netapp Snapmirror ConfigurationDocument62 pagesNetapp Snapmirror ConfigurationNagarajan DNo ratings yet

- Dev 004544Document2 pagesDev 004544William PaivaNo ratings yet

- Fusion QBD Product Development BrochureDocument8 pagesFusion QBD Product Development Brochurexq63x8ggmNo ratings yet

- Logismiko Win Test Analysis V4Document11 pagesLogismiko Win Test Analysis V4Tâm NguyễnNo ratings yet

- Evaluate Test Management SoftwareDocument15 pagesEvaluate Test Management SoftwareKecseg Fonce AndreiNo ratings yet

- Dreams-Testing ApproachesDocument6 pagesDreams-Testing ApproachesleoNo ratings yet

- 5.1 Software Test AutomationDocument20 pages5.1 Software Test Automationudhayan udhaiNo ratings yet

- iTEST PRO (B)Document2 pagesiTEST PRO (B)goofflineNo ratings yet

- Chakshu Sharma: Senior Test EngineerDocument5 pagesChakshu Sharma: Senior Test EngineerRakesh JhalaniNo ratings yet

- Why Sweat The Small Stuff in Functional Test?: 7 Best Practices For Mid-Volume / High-Mix Production TestDocument12 pagesWhy Sweat The Small Stuff in Functional Test?: 7 Best Practices For Mid-Volume / High-Mix Production Testapi-90729201No ratings yet

- Framework For Intelligent and Rapid Execution (FIRE) : Flexi Hybrid Test Automation SolutionsDocument12 pagesFramework For Intelligent and Rapid Execution (FIRE) : Flexi Hybrid Test Automation SolutionsDinesh YepuruNo ratings yet

- 03 Sisman 2023 Product Design and Development Assembly DisassemblyDocument70 pages03 Sisman 2023 Product Design and Development Assembly Disassemblyfarhan srgNo ratings yet

- Analizador System 1Document5 pagesAnalizador System 1Eva Karia colorado MartinezNo ratings yet

- STLC Stage Entry Criteria Activity Exit Criteria DeliverablesDocument10 pagesSTLC Stage Entry Criteria Activity Exit Criteria DeliverablesAnkit TrivediNo ratings yet

- Experienced Resume sampleDocument2 pagesExperienced Resume sampleAmresh PattnaikNo ratings yet

- ISTQB ConceptsDocument41 pagesISTQB ConceptsJackson HernandezNo ratings yet

- Cornerstones Summary by PhaseDocument3 pagesCornerstones Summary by PhaseAbhijat MittalNo ratings yet

- Subra Man I 2014Document6 pagesSubra Man I 2014manojkumarNo ratings yet

- STLC Means "Software Testing Life Cycle". It Involves Following StagesDocument9 pagesSTLC Means "Software Testing Life Cycle". It Involves Following StageskrisnareshNo ratings yet

- Chapter 4 - STLC (Software Testing Life Cycle) Phases, Entry, Exit CriteriaDocument8 pagesChapter 4 - STLC (Software Testing Life Cycle) Phases, Entry, Exit CriteriaAamir AfzalNo ratings yet

- System Verilog Verification BasicsDocument38 pagesSystem Verilog Verification BasicsHardik TrivediNo ratings yet

- Examples Eight VisualCV ResumeDocument2 pagesExamples Eight VisualCV ResumeAlam ZebNo ratings yet

- Implementation MethodologyDocument10 pagesImplementation MethodologyismailalshanulNo ratings yet

- BateriasDocument6 pagesBateriasAnonymous q9c7KY1vNo ratings yet

- Measure. Understand. CommunicateDocument4 pagesMeasure. Understand. CommunicateZoltan FegeteNo ratings yet

- CRDB Konnect - Test StrategyDocument31 pagesCRDB Konnect - Test StrategymsvinuNo ratings yet

- Test Case Design by Means of CTM and CteDocument14 pagesTest Case Design by Means of CTM and Cteapi-3738458No ratings yet

- MindTree Testing BU BrochureDocument4 pagesMindTree Testing BU BrochureTanin ChakrabortyNo ratings yet

- Cost EstimationDocument69 pagesCost EstimationMr. KNo ratings yet

- Software Testing Short NoteDocument17 pagesSoftware Testing Short NoteSudhan SudhanNo ratings yet

- Life Cycle ModelsDocument46 pagesLife Cycle ModelsARINDAM BISWASNo ratings yet

- Delcam - PowerINSPECT 2016 QuickStart OMV EN - 2015Document58 pagesDelcam - PowerINSPECT 2016 QuickStart OMV EN - 2015phạm minh hùngNo ratings yet

- Data Warehouse Testing - Practical ApproachDocument8 pagesData Warehouse Testing - Practical ApproachRahul SharmaNo ratings yet

- Test Case Design Based On Z and The Classification-Tree MethodDocument10 pagesTest Case Design Based On Z and The Classification-Tree MethodCahaya SNo ratings yet

- STLC - Software Testing Life Cycle Phases & Entry, Exit CriteriaDocument9 pagesSTLC - Software Testing Life Cycle Phases & Entry, Exit CriteriasimonaNo ratings yet

- Software Quality Assurance and Software Testing Strategies Session 15 (Tutorial)Document38 pagesSoftware Quality Assurance and Software Testing Strategies Session 15 (Tutorial)michael bennyNo ratings yet

- Manual TestingDocument37 pagesManual Testingapi-3815323100% (4)

- Performance Engineering BasicsDocument16 pagesPerformance Engineering BasicsImpetusNo ratings yet

- 3 YearsExp SeleniumDocument5 pages3 YearsExp Seleniumbkumar.ece91No ratings yet

- Olivier I 2012Document6 pagesOlivier I 2012HakimHabibiNo ratings yet

- GUI Testing On A Product Suite Using On-The-Shelf Testing SoftwareDocument15 pagesGUI Testing On A Product Suite Using On-The-Shelf Testing SoftwareAnubhav JainNo ratings yet

- Framework ChecklistDocument1 pageFramework Checklistichary.chellojiNo ratings yet

- Quality AssuranceDocument23 pagesQuality Assurancesaimanaaz40No ratings yet

- Testing in Software Life CycleDocument24 pagesTesting in Software Life CycleZain ShahidNo ratings yet

- Roles: Unit 4: Workstream OverviewDocument1 pageRoles: Unit 4: Workstream Overviewshree.patil20028558No ratings yet

- SMMT AQMS FMEA Alignment AIAG and VDA - en PDFDocument32 pagesSMMT AQMS FMEA Alignment AIAG and VDA - en PDFNilton de OliveraNo ratings yet

- (Insert Project, Program or Organization Name Here) : State of Michigan Test StrategyDocument22 pages(Insert Project, Program or Organization Name Here) : State of Michigan Test StrategyArminto Natanagari IINo ratings yet

- Unit TestingDocument23 pagesUnit TestingGiridharNo ratings yet

- 04 - ADAS & Autonomous Driving - 2Document28 pages04 - ADAS & Autonomous Driving - 2Oliver TahirNo ratings yet

- Software TestingDocument56 pagesSoftware TestingAnonymous i9tSg4JNo ratings yet

- Fundamentals of Building A Test System CompleteGuideDocument190 pagesFundamentals of Building A Test System CompleteGuideHưng Nguyễn NgọcNo ratings yet

- Soujanya: Professional SummaryDocument3 pagesSoujanya: Professional Summarymunna thoNo ratings yet

- Performance Testing TestRailDocument26 pagesPerformance Testing TestRailfxgbizdcsNo ratings yet

- QC-Gage 40Document2 pagesQC-Gage 40dadiNo ratings yet

- Software Testing Interview Questions You'll Most Likely Be AskedFrom EverandSoftware Testing Interview Questions You'll Most Likely Be AskedNo ratings yet

- 1.1 AlgorithmsDocument68 pages1.1 AlgorithmsJCNo ratings yet

- Lecture 10 Closer Look at Classes, MethodsDocument21 pagesLecture 10 Closer Look at Classes, MethodsKashif MujeebNo ratings yet

- Nte Electronics Actives and Passives 9357002Document3 pagesNte Electronics Actives and Passives 9357002sienkoplaneNo ratings yet

- Single-Phase To Three-Phase Power Converters: State of The ArtDocument16 pagesSingle-Phase To Three-Phase Power Converters: State of The Artnl vinay kumarNo ratings yet

- Moxa Mgate mb3180 mb3280 mb3480 Series Datasheet v1.0Document5 pagesMoxa Mgate mb3180 mb3280 mb3480 Series Datasheet v1.0Nicole FelicianoNo ratings yet

- Basic PPT On Cloud ComputingDocument32 pagesBasic PPT On Cloud ComputingSavyasachi Vats54% (13)

- Poweredge r730 - Owners Manual2 - en UsDocument201 pagesPoweredge r730 - Owners Manual2 - en UsANthonyNo ratings yet

- A53tp50d crdmh1Document234 pagesA53tp50d crdmh1LOUKILkarimNo ratings yet

- Cyber Security Lecture Notes 04Document24 pagesCyber Security Lecture Notes 04Sampath DarshanaNo ratings yet

- Books PHPDocument53 pagesBooks PHPV.M.B.SNo ratings yet

- Toshiba+Placa de Sinal 32AV550T+Ver.+2.00Document11 pagesToshiba+Placa de Sinal 32AV550T+Ver.+2.00Nelson PintoNo ratings yet

- sg246528 - MQ Integrator For zOS PDFDocument392 pagessg246528 - MQ Integrator For zOS PDFecorradiNo ratings yet

- Operational AmplifierDocument85 pagesOperational AmplifierRajatSardanaNo ratings yet

- Ese 570 Mos Inverters: Static CharacteristicsDocument42 pagesEse 570 Mos Inverters: Static CharacteristicsVipul MistryNo ratings yet

- PDRM AssignmentDocument30 pagesPDRM Assignmentdynamic143No ratings yet

- Power System Automation ReportDocument11 pagesPower System Automation ReportSahana P MNo ratings yet

- Zetagi b303 With Board B303azg Original HF Circuit - 59cdb0a71723ddfb65ec727bDocument2 pagesZetagi b303 With Board B303azg Original HF Circuit - 59cdb0a71723ddfb65ec727bHerintsalamaNo ratings yet

- TechRef DCDC ConverterDocument11 pagesTechRef DCDC ConverterАлишер ГалиевNo ratings yet

- Siemens Simatic C7 Control SystemDocument12 pagesSiemens Simatic C7 Control SystemJuan Carlos Barberán MuñozNo ratings yet

- JDBC ExcellentDocument20 pagesJDBC ExcellentNego RemoNo ratings yet

- Sony TVC LCD Ke 32ts2uDocument99 pagesSony TVC LCD Ke 32ts2uGiada SpaccarotellaNo ratings yet

- Gujarat Technological University: Computer Engineering (Software Engineering) (02) Semester IDocument23 pagesGujarat Technological University: Computer Engineering (Software Engineering) (02) Semester IdivyaNo ratings yet

- Office Productivity Week 4Document4 pagesOffice Productivity Week 4Erizza PastorNo ratings yet

- DEFENSEDocument45 pagesDEFENSEClarence PradoNo ratings yet

- Hands On Module PDFDocument71 pagesHands On Module PDFzamani ismailNo ratings yet

- Port AddressDocument25 pagesPort AddressLaiba TahirNo ratings yet

- 555 Timer As Mono Stable Multi VibratorDocument8 pages555 Timer As Mono Stable Multi VibratorchrisgeclayNo ratings yet

- Ethernet DLSW+ Redundancy White PaperDocument12 pagesEthernet DLSW+ Redundancy White Papergborja8881331No ratings yet