Professional Documents

Culture Documents

An RTL Power Optimization Technique Base PDF

An RTL Power Optimization Technique Base PDF

Uploaded by

maniOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An RTL Power Optimization Technique Base PDF

An RTL Power Optimization Technique Base PDF

Uploaded by

maniCopyright:

Available Formats

An RTL Power Optimization Technique Based on

SystemVerilog Assertions

Khaled Khalifa Khaled Salah

Alexandria University Mentor Graphics

Alexandria, Egypt Cairo, Egypt

khaled.khalifa.eg@ieee.org Khaled_Mohamed@mentor.com

Abstract ـــــThis paper presents a novel technique based on consumed power. Performing accurate and efficient power

System Verilog assertions to optimize the consumed power of enhancement as early as possible in the flow of creating any

RTL designs. The proposed technique helps the designer to design is important in creating a power optimized designs

enhance his RTL code towards achieving low power design. and essential for the successful low power designs. Our

The designer codes the proposed technique according to the

technique is concerned of performing accurate and efficient

design specifications and integrates the coded technique into

his test bench. The coded technique generates directive design power enhancement through being part of the design

massages which will be followed to modify and enhance the verification environment in the flow of creating RTL

design code to reduce the consumed power of the design. The designs.

idea behind this technique is to monitor the whole design

signals. Thus, this technique is a design-dependent technique as Our key contributions of this paper are as follows:

it depends on the design specifications. The coded technique

determines the targeted signals of the specific input then it I. Proposing a power optimization technique utilizing

displays the mistakenly setting signals which may consume System Verilog assertions.

additional wasted power. This technique can be applied and

II. A detailed discussion of our power optimization

included in any verification framework like the Universal

Verification Methodology (UVM) to integrate the power technique through a simple case study to compare

optimization feature of this technique with the features of the the power results of the original code with the

used framework. Through applying this technique, the optimized code after applying the proposed

consumed power of the design is significantly reduced as it technique.

catches each unused design signal that consumes additional III. An overview on how assertions are written to

wasted power. This paper explains how to apply the proposed generate directed test cases.

technique with respect to any design specifications and also IV. Providing a method of how to extract the consumed

provides the technique code itself of a simple RTL case study. power of any synthesizable code with respect to the

Moreover, it also attaches the resultant directive massages and

dissipated power in signals activities.

presents a comparison between the consumed power before

and after the modification of the RTL code according to the

directive massages of the coded technique. The rest of paper is organized as follows. In section II,

The proposed power optimization technique is presented. In

Index Terms— Design Power Optimization, System Verilog Section III. A simple case study is explained. Conclusions

Assertions, Verification Environment, HDL, RTL, Test Cases, are given in section IV.

Power Extraction.

II. THE PROPOSED POWER OPTIMIZATION

I. INTRODUCTION

TECHNIQUE

With the explosive growth in laptops, portable personal

communication systems, and the evolution of the shrinking Design verification is considered to be the most important

technology, the research efforts in low power design process in the SoC design flow as more than 70 percent of

techniques have been intensified. Today, there are the time is spent on design verification. Since the

increasing numbers of portable applications requiring low verification process verifies the correctness of the design, it

power architectures than ever before. Therefore, may doesn’t concern of any other additional design code

architectures with low power consumption become the that doesn’t affect the design correctness. This additional

major candidates for design of microprocessors and system design code may cause consuming more additional wasted

components [1]. power as this code isn’t in the design specifications but it

The VLSI low power design problems can be broadly doesn’t affect the design correctness.

classified into two categories: analysis and optimization. For example, if the specifications of a certain design tell

Optimization is the process of generating the best design that when the input is high, the output signal (A) only must

with the lowest power consumption. The task of the design be high. But in the real implementation code, the designer

engineer is to carefully weigh each design code line with the wrote that when the input is high, both output signals (A)

specification constraints to generate the lowest design and (B) are high. In the implementation code, setting signal

978-1-5090-1496-5/16/$31.00 © 2016 IEEE

(A) is considered to be a specification code but setting

signal (B) is considered to be an additional code which A. Create Sequence Expressions

doesn’t affect the design correctness, but consumes In any design model, the functionality is represented by

additional wasted power. So, the verification environment the combination of multiple logical events. These events

must integrate a power specific verification code which is could be simple Boolean expressions that get evaluated on

responsible for catching the resources of the design code the same clock edge or could be events that evaluate over a

which consume additional wasted power and then displays period of time involving multiple clock cycles.

directive massages to help the designer to improve his SystemVerilog assertion provides a key word to represent

these events called "sequence" [2].

design code and optimize the design consumed power. This

In sequence step, the designer specifies the state of the

can help any design and verification engineer to catch the

design signals at every single input combination according

power wasting resources in the design code and accurately to the design specifications where every input combination

determine the correction of the code with respect to the sets some specific design signals to high state and the others

design specifications. to low state. Every single input combination has to be

One of the main power consumption resources in any described by two different types of sequences which are

design is pulling up the design signals to keep them in high state sequences and operating sequence.

state. Thus, this paper concerned of optimizing the State Sequences

consumed power of setting the design signals by The state sequences specify the signals state of a single

determining the unused signals which consume additional input combination in different expressions using different

wasted power. In this paper, we propose a novel technique SVA keywords and relationships to cover every single test

for any RTL design code to catch the coding mistakes in scenario to specify these signals setting state. To create the

setting the design signals and generate directive massages to state sequences, the designer will use SVA logical

help the designer to enhance the design code and optimize relationships to accurately specify the setting states of the

the design consumed power. Such a technique can be design signals. These SVA logical relationships are used to

applied on any RTL design code makes it a generic describe the relationships between different design signals

methodology. of a certain input combination which can be used to AND

The technique concerned of the design signals only which signals (&&), OR signals (||) or NOT signals (!).

are the design output signals and the design internal signals The state sequences are divided into two categories which

as the design input signals can’t be controlled by the design are continuous state sequence and change state sequences.

1) Continuous State Sequence

code itself. This makes us know for a fact that as the number

The continuous state sequence specifies the continuity of

of these design signals increase, the consumed power of the setting the state of certain design signals as a specific input

design subsequently increases. This proposed technique combination continues to be applied on the design input

employs System Verilog assertions based verification to signals for a period of time. Thus, the continuous state

continuously monitor the whole design signals and verify sequence is always only one sequence as it describes the

the functionality of each design signal with respect to the state of each design signal with respect to a specific input

design specifications. So, this technique is a design combination according to the design specifications.

dependent technique. Thus in this paper, we are going to 2) Change State Sequences

explain the creation criteria of the technique and how to The change state sequences specify the change of the

apply it on any design specifications. design signals state while a new input combination is

This section explains the proposed power optimization applied on the design input signals. So the number of

technique which utilizes System Verilog assertions. This change state sequences is more than one as any design

technique proposes two different types of assertions to signal can be in any state before getting set to the targeted

perform two different types of checks which are warning state of the new input combination. Even it can be more than

assertions and fault assertions by following certain creation the number of the design signals themselves as there are

steps which are shown in Fig.1. multi combinations of these states with respect to the design

specifications. Change state sequences will be created with

edge definitions as SVA has built in edge expressions that

Create Sequence Expressions let the designer monitor the transition of signal value from

(Specifying design specifications of setting the design signals

state)

one clock cycle to the next. This allows the designer to

check for the edge sensitivity of signals. These built-in

functions are:

Create Property $rose (signal name): This returns true if LSB of the signal

(Specifying input combinations with respect to the design

specifications) changed to 1.

$fell (signal name): This returns true if LSB of the signal

changed to 0.

$stable (signal name): This returns true if the value of the

Assert Property

(Specifying the content of the displayed directive massages signal did not change.

whatever warning massages or fault massages)

Fig.1 The assertions creation flow.

Operating Sequence

After specifying every setting state of the whole design Listing.2 The creation code of the property step

signals of every single input combination in the state 1 //Property of input combination1: x’bxxx //

sequences, the designer has to integrate these state 2 property p_x’bxxx;

3 @(posedge …) ( specific input combination) (|->,|=>)

sequences into only one operating sequence which will be 4 (so_x’bxxx “operating sequence of the specific input

verified during simulation. The binary operator (or) is used 5 combination”);

to logically combine all of the different state sequences of a 6 endproperty

certain single input combination to cover all test scenarios C. Assert Property

described in every state sequence. The operating sequence The property is the one that is verified during a simulation.

will succeed when any of the state sequences succeed and It has to be asserted to take effect during a simulation. SVA

will fail when all of the state sequences fail. provides a key word called "assert" to check the property

After explaining the creation of sequences, the sequence [2]. In this step, the designer asserts the property of each

expressions must be coded as shown in Listing.1. input combination and specifies the displayed information

B. Create Property of the directive massages. A designer can print a custom

A number of sequences can be combined logically or error or success message using the "action block" in the

sequentially to create more complex sequences. SVA assert statement. In this action block, several system tasks

provides a keyword to represent these complex sequential can be used to control over severity of a failing assertions.

behaviors called "property" [2]. In property step, the As ($fatal) will be used with fault massages and ($display)

designer integrates the input combination with its operating is used for warning massages. Thus, the assert property step

Listing.1 The creation code of the state sequences must be coded as shown in Listing.3.

1 // input combination1: x’bxxx // Listing.3 The creation code of the assert property step

2 // State Sequences 1 //Assert property of input combination1: x’bxxx //

3 // Continuous State Sequence 2 assert_pro_x’bxxx: assert property ( p_x’bxxx)

4 sequence s1_x’bxxx; sig1 && !sig2 && … ; endsequence 3 else ($display,$fatal) ("%m: warning/fault massage:

4 information of the directive massage");

5 // Change State Sequences

6 sequence s2_x’bxxx; $rose (sig1) && !sig2 && … ; After explaining the assertions creation flow of the

endsequence proposed technique which is presented in Fig.1, this

7 sequence s3_x’bxxx; $rose (sig1) && $fell (sig2) && …. ; technique follows the assertions creation flow to propose

endsequence two different categories of assertions which are warning

8 //………. The other change state sequences …………` assertions and fault assertions.

9 // Operating Sequence of input combination (x’bxxx) 1) Warning Assertions

10 sequence so_x’bxxx; s1_x’bxxx or s2_x’bxxx or s3_x’bxxx or Warning assertions are responsible for catching the

…. ; additional code which doesn’t affect the design correctness,

11 endsequence but consumes additional wasted power. These warning

sequence according to the design specifications. In this assertions will be created by following the assertions

integration, the designer will use concurrent definition creation flow presented in Fig.1. Warning assertions display

which is based on clock cycles. In concurrent assertions, test directive warning massages which contain directive

expression is evaluated at clock edges based on the sampled information to be followed by the designer to modify and

values of the signals involved. In SVA, clock cycle delays enhance the design code and reduce the design consumed

are represented by a "##" sign and implication operator power. This directive information must be displayed as

with its different types. There are three types of implication shown in Listing.4.

operator which are overlapped implication, non-overlapped Listing.4. The displayed information of different directive massages.

implication and implication with a fixed delay on the 1 //Displayed Information of the directive massages //

consequent. 2 Warning/Fault massage: input combination,

3 additional/wrong setting signals, correct setting signals.

Overlapped implication: Overlapped implication is

denoted by the symbol (|->). If there is a match on the 2) Fault Assertions

antecedent, then the consequent expression is evaluated in Fault assertions are responsible for catching the wrong

the same clock cycle. code which violates the design specifications and affect the

Non-overlapped implication: Non-overlapped implication design correctness. Thus, fault assertions are used as

is denoted by the symbol (|=>). If there is a match on the directed test cases to verify the correctness of setting the

design signals and correct them. These fault assertions will

antecedent, then the consequent expression is evaluated in

be created by following the assertions creation flow shown

the next clock cycle. A delay of one clock cycle is assumed in Fig.1 except in property step. In property step, (not)

for the evaluation of the consequent expression. operator is used to create a forbidden sequence from

Implication with a fixed delay on the consequent: This happening. In other words, it is expected that the property to

type uses both of overlapped and non-overlapped be false always. If the property is true, the assertion fails.

implications, however the designer specify the number of Thus, fault assertions also display directive fault massages

clock cycles delay. It is recommended to use overlapped as shown in Listing.4 which contain directive information to

implication to easily specify the targeted delay directly after be followed by the designer to correct the design code with

the symbol of overlapped implication (|->) using "##" sign. respect to the design specifications.

Thus, the property creation just must be coded as shown in

Listing.2.

TABLE 1.

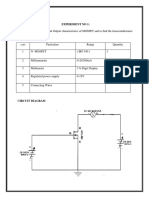

III. A CASE STUDY : DE-MULTIPLEXER COMPARISON BETWEEN THE POWER RESULTS OF THE DE-

MULTIPLEXER CODE

Consumed power of

As setting the design signals to high state increases the the DE-MUX code

consumed power of the design, this paper is interested in Before applying the modification of the

the case where the signals of the clocked de-multiplexer is 17 mW

technique directive massages

high ‘1’. This de-multiplexer is one hot output design After applying the modification of the

14 mW

which has two input control signals; regardless of the technique directive massages

clock and reset signals; and two output signals as shown in

Fig. 2. This paper studies only when input (A) is high. The

other input signal is a one bit select signal which chooses RTL Design Simple RTL

only one output of the two de-multiplexer outputs will be Tesetbench

set to the high state (‘1’). We have implemented the de-

multiplexer using Verilog hardware description language. Xilinx ISE QuestaSim

In Listing.5, the case statement of the de-multiplexer (RTL Synthesis) (RTL Simulation)

Verilog RTL code is provided. Place and Route Simulation Dump

To generate the power report of the RTL code, some Netlist

NCD VCD

files are needed to be generated from the RTL code. These

files are the native circuit description file (.ncd) and the

value change dump file (.vcd). The NCD file is a fully XPower Analyzer

placed and routed netlist file generated from the place and (Consumed Power Calculation)

route process in Xilinx tool [3]. The VCD file contains a

Power Report

series of time-ordered value changes for the signals in the

given simulation model which generated from Questasim PWR

tool [4]. To generate the VCD file from Questasim tool, a

simple test bench must drive the RTL code to insert all of Fig.3 The flow of extracting power report of the RTL code.

the valid input combinations to the design input signals.

Finally, the resultant power report file (.pwr) is generated

from XPower Analyzer tool [5] as shown in Fig. 3. IV. CONCLUSIONS

After applying the proposed technique in Listing.6 on the This paper proposed a novel technique which employs

de-multiplexer code in listing.5, the resultant directive the power of System Verilog assertions to optimize the

massage will be as follow: DE_MUX design consumed power. We have discussed our technique

_tb.dut.output_monitoring.assert_set_out1: Warning strategy which is utilizing System Verilog assertions to

Massage: select: 1’b0, Out2:1'b1, Out2:1'b0. continuously watch the whole signals of the design since

Enhancing the de-multiplexer code according to the any design signal is set at any time can be monitored. Thus,

displayed directive massage makes out2 in line 4 of this technique catches the code mistakes in setting the

Listing.5 must be equal to 0. By comparing the power design signals which consume additional wasted power and

reports of the de-multiplexer code before and after the displays directive massages to correct the design code.

modification of the directive massages, the power results in Regardless of the abstraction level of the design code, the

TABLE.1 shows that the consumed power of the modified proposed technique is a generic methodology which can be

de-multiplexer code is reduced by more than 17.5%. applied on any design code to enhance it. The proposed

Clk Reset technique can be included in any verification framework to

Out1 integrate the power optimization feature of this technique

A with the features of the used framework. For our future

DE-MUX work,, we are going to create a computer aid design tool to

Out2 systematically generate the proposed types of assertions

Select (1bit)

Fig.2 The architecture and the truth table of the DE-MUX case study. according to the user design specifications to be attached in

Listing.5 The case statement of the DE-MUX case study the user verification environment. So the designer doesn’t

1 case (select) need to think about all possible cases and the CAD tool will

2 1'b0 : begin automatically generate them.

3 out1 = A ;

4 out2 = A ; // Insert directive warning message

REFERENCES

5 end

[1] Yeap, Gary K. Practical low power digital VLSI design. Springer

6 1'b1 : begin

Science & Business Media, 2012.

7 out1 = 0 ;

[2] S. Vijayaraghavan and M. Ramanathan. A Practical Guide for

8 out2 = A ;

SystemVerilog Assertions. Springer, 2005.

9 end

10 default : begin [3] http://www.xilinx.com/support/documentation/sw_manuals/xili

11 out1 = 0 ; nx 13_1/ise_c_overview.html.

12 out2 = 0 ; [4] http://www.mentor.com/products/fv/questa/

13 end [5] http://www.xilinx.com/support/documentation/sw_manuals/xili

14 endcase nx11/pp_p_process_xpower_analyzer.html.

You might also like

- Low-Current Systems Engineer’S Technical Handbook: A Guide to Design and SupervisionFrom EverandLow-Current Systems Engineer’S Technical Handbook: A Guide to Design and SupervisionRating: 5 out of 5 stars5/5 (1)

- Wiring Harness Innovations: Editorial GuideDocument23 pagesWiring Harness Innovations: Editorial GuideJE Vikky Kumar MandalNo ratings yet

- Paper Wcas RevisedDocument4 pagesPaper Wcas RevisedJoão Luiz CarvalhoNo ratings yet

- Mil Sil PilDocument87 pagesMil Sil Pilmdur67No ratings yet

- Unveil The Mystery of Code Coverage in Low-Power Designs: Achieving Power AwareDocument13 pagesUnveil The Mystery of Code Coverage in Low-Power Designs: Achieving Power AwareNishit GuptaNo ratings yet

- A PDFDocument6 pagesA PDFpoojaNo ratings yet

- MICPRO PublishedDocument13 pagesMICPRO PublishedKeran KomalNo ratings yet

- EDNI Ebook TM Automotive - 35Document26 pagesEDNI Ebook TM Automotive - 35Roberto AraizaNo ratings yet

- Introduction, Design Flow, Algorithmic Level Analysis & Optimization, Architectural Level Estimation & SynthesisDocument35 pagesIntroduction, Design Flow, Algorithmic Level Analysis & Optimization, Architectural Level Estimation & SynthesisPrabhavathi PNo ratings yet

- Verification of Axi Bus Protocol Using SystemverilogDocument8 pagesVerification of Axi Bus Protocol Using SystemverilogQasim ZamanNo ratings yet

- Formal Verificaiton of A FIFODocument8 pagesFormal Verificaiton of A FIFOSandesh BorgaonkarNo ratings yet

- Using Python Tools To Assist Mixed-Signal ASIC Design and Verification MethodologiesDocument6 pagesUsing Python Tools To Assist Mixed-Signal ASIC Design and Verification Methodologiesshagu952No ratings yet

- A Matlab To VHDL Conversion Toolbox For Digital ControlDocument5 pagesA Matlab To VHDL Conversion Toolbox For Digital ControlrahulpsomanNo ratings yet

- How To Automate Millions Lines of Top-Level UVM Testbench and Handle Huge Register ClassesDocument3 pagesHow To Automate Millions Lines of Top-Level UVM Testbench and Handle Huge Register ClassesUsha KrishnaNo ratings yet

- Kreiranje PLC ProgramaDocument7 pagesKreiranje PLC Programasaid sakićNo ratings yet

- Embedded Steer-by-Wire System DevelopmentDocument7 pagesEmbedded Steer-by-Wire System DevelopmentkeshNo ratings yet

- Vlsi Systems For Simultaneous in Logic Simulation: Karthik. S Priyadarsini. K Jeanshilpa. VDocument5 pagesVlsi Systems For Simultaneous in Logic Simulation: Karthik. S Priyadarsini. K Jeanshilpa. Vﻳﻮﺳﻒ أردي ﺑﺧﺘﻴارNo ratings yet

- Hardware Performance Simulations of Round 2 Advanced Encryption Standard AlgorithmsDocument55 pagesHardware Performance Simulations of Round 2 Advanced Encryption Standard AlgorithmsMihai Alexandru OlaruNo ratings yet

- Systemverilog Based Verification Environment For Wishbone Interface of Ahb-Wishbone BridgeDocument4 pagesSystemverilog Based Verification Environment For Wishbone Interface of Ahb-Wishbone Bridgemeghna veggalamNo ratings yet

- CND111 Project-AllDocument10 pagesCND111 Project-AllHamadaNo ratings yet

- Specc System-Level Design Methodology Applied To The Design of A GSM VocoderDocument8 pagesSpecc System-Level Design Methodology Applied To The Design of A GSM Vocoderdrchris32No ratings yet

- Digital Design Through Verilog PDFDocument68 pagesDigital Design Through Verilog PDFSammed UpadhyeNo ratings yet

- Model Based System Engineering (Mbse) : For Accelerating Software Development CycleDocument12 pagesModel Based System Engineering (Mbse) : For Accelerating Software Development CycleBalajee AsokanNo ratings yet

- Can Protocol Uvm PDFDocument5 pagesCan Protocol Uvm PDFMayank JaiswalNo ratings yet

- End-to-End Formal Using Abstractions To Maximize CoverageDocument8 pagesEnd-to-End Formal Using Abstractions To Maximize Coverageamitpatel1991No ratings yet

- C To VHDL Converter in A Codesign Environment: June 1994Document11 pagesC To VHDL Converter in A Codesign Environment: June 1994Vivek SinghNo ratings yet

- Design of An Error Detection and Correction Architecture For Video Coding Testing ApplicationsDocument5 pagesDesign of An Error Detection and Correction Architecture For Video Coding Testing ApplicationshawltuNo ratings yet

- Encounter Conformal Low PowerDocument4 pagesEncounter Conformal Low PowerVakeel Mohammad AnsariNo ratings yet

- Cdnlive Jungeblut PaperDocument5 pagesCdnlive Jungeblut PaperSamNo ratings yet

- AvmDocument4 pagesAvmPinakin UpadhyayaNo ratings yet

- Levels of Microcontroller Integration in Power-Supply DesignDocument11 pagesLevels of Microcontroller Integration in Power-Supply DesignDenny Firmansyah ZNo ratings yet

- Synopsis Master of Technology IN Vlsi Design: Ims Engineering College, GhaziabadDocument9 pagesSynopsis Master of Technology IN Vlsi Design: Ims Engineering College, GhaziabadAnubhav SinghalNo ratings yet

- An MPEG 2 Decoder Case Study As A DriverDocument5 pagesAn MPEG 2 Decoder Case Study As A DriverHariniNo ratings yet

- FV WikiDocument19 pagesFV Wikikundan1991No ratings yet

- DSDV Mod5@AzDOCUMENTS - inDocument26 pagesDSDV Mod5@AzDOCUMENTS - inAnu YSNo ratings yet

- Verification of AMBA Bus Model Using SystemVerilogDocument5 pagesVerification of AMBA Bus Model Using SystemVerilogdoomachaleyNo ratings yet

- Sarma 2015 Ijca 907609Document7 pagesSarma 2015 Ijca 907609animesharnavNo ratings yet

- To Perform SIL and PIL Testing On Fast D PDFDocument4 pagesTo Perform SIL and PIL Testing On Fast D PDFgil lerNo ratings yet

- Whitepaper Substation Automation Schneider ElectricDocument5 pagesWhitepaper Substation Automation Schneider Electricsahil4INDNo ratings yet

- Engineer: Why Software?Document50 pagesEngineer: Why Software?Jay PenNo ratings yet

- Practices Resulting From Migration To IEC 61850Document9 pagesPractices Resulting From Migration To IEC 61850DanielAlejandroRamosQueroNo ratings yet

- A HW/SW Co-Design Methodology: An Accurate Power Efficiency Model and Design Metrics For Embedded SystemDocument5 pagesA HW/SW Co-Design Methodology: An Accurate Power Efficiency Model and Design Metrics For Embedded SystemShivarth SharmaNo ratings yet

- Alarm Clock Using VerilogDocument5 pagesAlarm Clock Using VerilogRadhikaNo ratings yet

- Testing Challenges of A Complete PAC Digital SubstationDocument9 pagesTesting Challenges of A Complete PAC Digital Substationchandraippa2No ratings yet

- Digital Design Through Verilog-18 PDFDocument31 pagesDigital Design Through Verilog-18 PDFAnanth G NNo ratings yet

- PubDat 188476Document15 pagesPubDat 188476Mohamed AlmortadaNo ratings yet

- An On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SDocument7 pagesAn On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SBhaskar YalamoluNo ratings yet

- BateriasDocument6 pagesBateriasAnonymous q9c7KY1vNo ratings yet

- Eda ExamplesDocument27 pagesEda ExamplesTamilinbaaNo ratings yet

- Platform-Based Design Methodology and Modeling For Aircraft Electric Power SystemsDocument7 pagesPlatform-Based Design Methodology and Modeling For Aircraft Electric Power SystemsThale1905No ratings yet

- Managing Logic Transformations FinalDocument6 pagesManaging Logic Transformations FinalevilgreenieNo ratings yet

- Accurate Spectral Testing With Impure Source and Noncoherent SamplingDocument10 pagesAccurate Spectral Testing With Impure Source and Noncoherent SamplingMa SeenivasanNo ratings yet

- VHDL Modeling and Synthesis in The Laboratory: Session 2647Document12 pagesVHDL Modeling and Synthesis in The Laboratory: Session 2647Красимир КостадиновNo ratings yet

- Tutorials: A1 System Level Specification Beyond RTLDocument4 pagesTutorials: A1 System Level Specification Beyond RTLRahul MehtaNo ratings yet

- Design of A Shopping Cart 2Document7 pagesDesign of A Shopping Cart 2d71guhaNo ratings yet

- Synopsys Test CompilerDocument6 pagesSynopsys Test Compilerece gate2021No ratings yet

- ASIC Design Flow and Methodology - An OverviewDocument6 pagesASIC Design Flow and Methodology - An OverviewAhtasham KhokherNo ratings yet

- Digital Electronics Lab Manual For Cse & ItDocument72 pagesDigital Electronics Lab Manual For Cse & ItSairam DasariNo ratings yet

- Benchmarking IC Development For Automotive ApplicationsDocument8 pagesBenchmarking IC Development For Automotive ApplicationsymNo ratings yet

- Analog Mixed Signal Verification MethodologyDocument5 pagesAnalog Mixed Signal Verification MethodologySrikanthNo ratings yet

- Super Conductors Question and AnswersDocument7 pagesSuper Conductors Question and AnswersManish SinghNo ratings yet

- Siemens Euroset 802 ManualDocument2 pagesSiemens Euroset 802 ManualAr MaNo ratings yet

- Remote Data Acquisition For Condition Monitoring of Wind TurbinesDocument10 pagesRemote Data Acquisition For Condition Monitoring of Wind TurbinesCrossNo ratings yet

- Pennbuying, Dual Motor Driver L298 PDFDocument11 pagesPennbuying, Dual Motor Driver L298 PDFbaymax love spideyNo ratings yet

- Symmetrical Components PDFDocument24 pagesSymmetrical Components PDFtanayspatel100% (1)

- Battery Report - Korean - LeBlancDocument5 pagesBattery Report - Korean - LeBlancAnonymous zbtydHNo ratings yet

- 7SD52 enDocument372 pages7SD52 enMadhan KumarNo ratings yet

- Mpdi K3000Document2 pagesMpdi K3000Juan JuanNo ratings yet

- Volumetric Helical Screw Feeder For Dry Chemicals: AdvantagesDocument4 pagesVolumetric Helical Screw Feeder For Dry Chemicals: AdvantagesdenversagariolimNo ratings yet

- Quick PRD Surge ArresterDocument2 pagesQuick PRD Surge ArrestersebadolzNo ratings yet

- B01-TB16I-PHO-003 - TB16IN-PHO Basic Installation Instructions V1.0 - ENGDocument2 pagesB01-TB16I-PHO-003 - TB16IN-PHO Basic Installation Instructions V1.0 - ENGDavinYudikaNo ratings yet

- Ieee STD 404 2012Document46 pagesIeee STD 404 2012juanita sanchez buitragoNo ratings yet

- WILCON Order Form Group BDocument9 pagesWILCON Order Form Group BAlleine TupazNo ratings yet

- ECE 171 Digital Circuits: Prof. Mark G. Faust Maseeh College of Engineering and Computer ScienceDocument30 pagesECE 171 Digital Circuits: Prof. Mark G. Faust Maseeh College of Engineering and Computer ScienceMinh HoangNo ratings yet

- Alternating Current: Peak Value and R.M.S ValueDocument9 pagesAlternating Current: Peak Value and R.M.S ValueBinod KhatriNo ratings yet

- Experiment 2 Open-Loop Dynamics Response of Second Order Systems 1. ObjectivesDocument7 pagesExperiment 2 Open-Loop Dynamics Response of Second Order Systems 1. ObjectivessinadasqNo ratings yet

- GMS2 Operating ManualDocument0 pagesGMS2 Operating Manualgomore14No ratings yet

- VG 88Document24 pagesVG 88Jairo NascimentoNo ratings yet

- MULTISER-xx-PC-TFT ManualDocument34 pagesMULTISER-xx-PC-TFT ManualChoukoura AldfeerNo ratings yet

- Sma Grid Guard 10.0: Technical InformationDocument38 pagesSma Grid Guard 10.0: Technical InformationGary FortuinNo ratings yet

- WGC 090 - 1401 Specifications ENGDocument2 pagesWGC 090 - 1401 Specifications ENGEmerson BatistaNo ratings yet

- 2013 LED/LCD TV Engineering GuideDocument72 pages2013 LED/LCD TV Engineering GuideRivaldoNo ratings yet

- Tny 279 PN ComDocument24 pagesTny 279 PN ComAnonymous gZYQAPv100% (1)

- Reluctance Motor: Fig.1 4 Pole Synchronous MotorDocument2 pagesReluctance Motor: Fig.1 4 Pole Synchronous MotorSourav KumarNo ratings yet

- DMX LED RGB Crystal Magic Ball ManualDocument4 pagesDMX LED RGB Crystal Magic Ball ManualImporta de ChinaNo ratings yet

- Final Microwave AntennaDocument13 pagesFinal Microwave AntennaHanilavMoraNo ratings yet

- NSE8 NSE12 IM EN - (988-0175-03) - B WDocument88 pagesNSE8 NSE12 IM EN - (988-0175-03) - B WJonAshleyNo ratings yet

- Accuracy of Voltage Sag AnalysisDocument29 pagesAccuracy of Voltage Sag AnalysisLalita VNo ratings yet

- A New High-Speed Foreign Fiber Detection System With Machine VisionDocument23 pagesA New High-Speed Foreign Fiber Detection System With Machine VisionijtrobinNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet