Professional Documents

Culture Documents

Four Bit Up Counter

Four Bit Up Counter

Uploaded by

Yashasvi Vijayvargiya0 ratings0% found this document useful (0 votes)

55 views2 pagesThe plagiarism scan report found 0% plagiarism across the 897-word content that was checked, with 0 plagiarized sentences out of the 33 unique sentences. The report indicates that the content is original and not copied from other sources.

Original Description:

Floor planning if 4 bitup counter

Original Title

Four bit up counter

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe plagiarism scan report found 0% plagiarism across the 897-word content that was checked, with 0 plagiarized sentences out of the 33 unique sentences. The report indicates that the content is original and not copied from other sources.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

55 views2 pagesFour Bit Up Counter

Four Bit Up Counter

Uploaded by

Yashasvi VijayvargiyaThe plagiarism scan report found 0% plagiarism across the 897-word content that was checked, with 0 plagiarized sentences out of the 33 unique sentences. The report indicates that the content is original and not copied from other sources.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 2

PLAGIARISM SCAN REPORT

Words 897 Date April 17,2019

Characters 5958 Exclude Url

100 0

0% 33

Plagiarism % Plagiarized

Sentences

Unique Sentences

Unique

Content Checked For Plagiarism

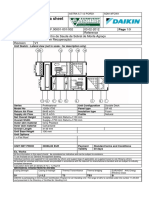

as expected. Fig. 3 Using SR flip flop and gates layout design of 4 bit synchronous up counter in cadence using

180nm technology As shown in the figure above is the layout design of the four bit synchronous up counter which is

designed by integrating the layout of the single four bit synchronous counter. IV. RESULT AND SIMULATION: The 4

bit synchronous up counter is designed using the 180nm technology in the cadence virtuoso and it’s layout is

further made from it and the figure 3 given above can be considered as the layout. Now the floor plan of the

counter designed is being done in the 180nm technology of cadence.the figure 4 shown below is the floor plan of

the 4bit synchronous up counter using 180nm technology of cadence. Fig.4Floor planning of 4 bit synchronous up

counter in cadence In order to maintain the privacy of patients information of not disclosing it to others this floor

map is designed so that the data of one patient should in one to one correspondence with the counters aligned in

the queue and should be at the distance away from the staff patient communication so hence the privacy of a

patient is maintained and is not disclosed to others. In order to reduce the glitch violations I the circuit the circuit or

the layout is simulated number of times and through each iteration simulation report is created ,from the report

through which the glitch violations become zero is considered as the final floor map and the layout . As the report of

the first two iterations is not satisfactory we have done the simulation three times in order to get the best possible

synthesis report and the least glitch violations. So in the iteration 3 we get the desired output and the no of

iterations in total are three. So, we have design the desired 4 bit synchronous up counter using 180 nm technology

of cadence and its floor planning is done in a way so that a patient’s privacy is maintained in the health care system

and the hospitals. V. CONCLUSION The floor planning for the 4 bit synchronous up counter is done using the 180 nm

technology and the corresponding output is recorded . from the our observations we can conclude that a counter

will be in it’s most efficient stage if it has the least area consumed and the least power consumption. This is

achieved in the initial circuit design of the cadence. In this method of the counter design all these characteristics

are achieved. by doing so, in floor planning the number of glitch violations are reduced and hence the patient’ s

information privacy is maintained. Future work in this field of floor planning of counters for health care applications

can be proceeded using the parallel circuitry. REFERENCES [1] Yogita Hiremath1, Akalpita L. Kulkarni2, J. S.

Baligar3, “ Design and Implementation of Synchronous 4-bit Up Counter using 180nm CMOS Process

Technology†IJRET: International Journal of Research in Engineering and Technology, eISSN: 2319-1163 | pISSN:

2321-7308, Volume: 03, Issue: 05, May-2014. [2] Milad Sangsefidi , Dariuh Abedi , Elnaz Yoosefi , Morteza

Karimpour, â€High speed and low cost synchronous counter design in quantum-dotcellular automata “,1–11,

Microelectronics Journal 73 (2018). [3] Tao Zhao , Tao Li , Biao Han , Zhigang Sun , Jinfeng Huang,†Design and

implementation of Software Defined Hardware Counters for SDN†129– 144, Computer Networks 102 (2016).

[4] Mark P. Mobach,†Counter design influences the privacy of patients in health careâ€, 1000–1005, Social

Science & Medicine 68 (2009). [5] Silviu Drăghici, Cornelia Victoria Anghel Drugărinb,†The Design of The

Moebius Mod-6 Counter Using ElectronicWorkbench Softwareâ€, 2316 – 2324, Procedia - Social and Behavioral

Sciences 191 ( 2015 ). [6] Pakpoom Subsoontorn, Drew Endy, “Design and analysis of genetically encoded

counters†Proceedings of the 3rd International Conference on Computational Systems-Biology and Bioinformatics

(CSBio 2012), 43 – 54, Procedia Computer Science 11 ( 2012 ). [7] KodaiMatsuoka n, FortheBelleIIPIDGroup,

“Design and performance study of the TOP counter†Nuclear Instruments and Methods in Physics Research

A732(2013)357–360, Elsevier, 2013. [8] Alexander Barkalov, Larysa Titarenko, Jacek Bieganowski, “Design of

FPGA-based Moore FMSs with Counters†12th IFAC Conference on Programmable Devices and Embedded

Systems The International Federation of Automatic Control September 25-27, 2013. [9] Aida S Tharakana, Binu K

Mathew, “Design and Implementation of an On-Chip Test Generation Scheme Based on Reconfigurable Run-Time

Programmable and Multiple Twisted-Ring Counters†International Conference on Information and Communication

Technologies (ICICT 2014), 1409 – 1416, Procedia Computer Science 46 ( 2015 ). [10] V.G. Podoynikovb, E.E.

Rikhtera, G.G. Protsenko, “Research and Design of Construction of a Bearing Plate of a Counter Rail Attachment

Fitting†International Conference on Industrial Engineering, ICIE 2016, 138 – 143 Procedia Engineering 150 (

2016 ). [11] M.M. Abutaleb, “Robust and efficient quantum-dot cellular automata synchronous countersâ€,

6–14, Microelectronics Journal 61 (2017). [12] Doshi N. A., Dhobale S. B., and Kakade S. R., “LFSR Counter

Implementation in CMOS VLSI†World Academy of Science, Vol:2, No:12, Engineering and Technology

International Journal of Computer and Information Engineering, 2008. [13] Sandeep Thakur, Rajesh Mehra,

“Optimized Design and Simulation of Ring Counter using 45nm Technology†International Journal of

Engineering Trends and Techno logy (IJETT) – Volume 36 Number 4- June 2016. [14] S. Radha, Jisha Mathew,

“Linearization Of Low Noise Amplifier For Wireless Sensor Networks “International Conference on Inventive

Systems and Control (ICISC-2017)

Sources Similarity

You might also like

- Sol3e Adv Progress Test Answer Keys BDocument9 pagesSol3e Adv Progress Test Answer Keys Bridik katin100% (3)

- General Curse Breaking PrayersDocument12 pagesGeneral Curse Breaking Prayersmotmagic100% (2)

- Paper 8871Document6 pagesPaper 8871IJARSCT JournalNo ratings yet

- Evaluation of Fruit Ripeness Using Electronic Nose: This Paper Describes The Use of AnDocument34 pagesEvaluation of Fruit Ripeness Using Electronic Nose: This Paper Describes The Use of AnpadmaNo ratings yet

- The Intelligent Vehicle Number Plate Recognition System Based On ArduinoDocument19 pagesThe Intelligent Vehicle Number Plate Recognition System Based On ArduinoIJRASETPublicationsNo ratings yet

- ETCW01Document3 pagesETCW01Editor IJAERDNo ratings yet

- AircraftmroDocument38 pagesAircraftmrosr7671No ratings yet

- Iccter ProceedingsDocument196 pagesIccter ProceedingsiaetsdiaetsdNo ratings yet

- Sensor Fusion To Estimate The Orientation of A Scale Autonomous Vehicle Using The Kalman FilterDocument7 pagesSensor Fusion To Estimate The Orientation of A Scale Autonomous Vehicle Using The Kalman FilterAriel BogadoNo ratings yet

- A Simple Method For Estimation of Queue Length: Digitalcommons@University of Nebraska - LincolnDocument6 pagesA Simple Method For Estimation of Queue Length: Digitalcommons@University of Nebraska - LincolnAltaf HossainNo ratings yet

- Traffic Sign DetectionDocument5 pagesTraffic Sign DetectionIJRASETPublicationsNo ratings yet

- Biometric Authentication Using Fingerprint Recognition: Rajiv Gandhi Institute of TechnologyDocument7 pagesBiometric Authentication Using Fingerprint Recognition: Rajiv Gandhi Institute of TechnologySarvesh DesaiNo ratings yet

- Association Rule Mining Using FP-Growth and An Innovative Artificial Neural Network TechniquesDocument8 pagesAssociation Rule Mining Using FP-Growth and An Innovative Artificial Neural Network TechniquesIJRASETPublicationsNo ratings yet

- Automatic Object Sorting Machine: International Research Journal of Engineering and Technology (IRJET)Document6 pagesAutomatic Object Sorting Machine: International Research Journal of Engineering and Technology (IRJET)Umar FarouqNo ratings yet

- 10 1109@icacccn 2018 8748287Document6 pages10 1109@icacccn 2018 8748287darkdevil12082001No ratings yet

- Smart Door Unlock System Using FingerprintDocument6 pagesSmart Door Unlock System Using Fingerprintshital shermaleNo ratings yet

- Smart Traffic Management System Using Machine LearningDocument12 pagesSmart Traffic Management System Using Machine LearningVedant AgrawalNo ratings yet

- Comparative Analysis of Minutiae Based Fingerprint Matching AlgorithmsDocument13 pagesComparative Analysis of Minutiae Based Fingerprint Matching AlgorithmsAnonymous Gl4IRRjzNNo ratings yet

- Fault Diagnosis of Automobile Gearbox Using Artificial Neural NetworkDocument8 pagesFault Diagnosis of Automobile Gearbox Using Artificial Neural NetworkGovindraj ChittapurNo ratings yet

- ReportDocument56 pagesReportDr. crazyNo ratings yet

- Car Parking System Using IR Sensors: International Journal of Advance Research in Engineering, Science & TechnologyDocument4 pagesCar Parking System Using IR Sensors: International Journal of Advance Research in Engineering, Science & TechnologySaqlainNo ratings yet

- Icitct'13 1Document146 pagesIcitct'13 1dhasdjNo ratings yet

- Traffic Sign Recognition System Using CNNDocument7 pagesTraffic Sign Recognition System Using CNNInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Traffic Sign Detection Using Convolutional Neural NetworksDocument7 pagesTraffic Sign Detection Using Convolutional Neural NetworksIJRASETPublicationsNo ratings yet

- Design of Vehicle Accident Prevention System Using Wireless TechnologyDocument8 pagesDesign of Vehicle Accident Prevention System Using Wireless TechnologyParam SinghNo ratings yet

- (IJCST-V4I5P34) :D.Thamaraiselvi, Dr.M.RamakrishnanDocument5 pages(IJCST-V4I5P34) :D.Thamaraiselvi, Dr.M.RamakrishnanEighthSenseGroupNo ratings yet

- Iot Based Parking Sensor Network For Smart CampusDocument10 pagesIot Based Parking Sensor Network For Smart CampusChristiana MarasiganNo ratings yet

- Information Security of Intelligent Vehicles Communication: Overview, Perspectives, Challenges, and Possible SolutionsFrom EverandInformation Security of Intelligent Vehicles Communication: Overview, Perspectives, Challenges, and Possible SolutionsRating: 5 out of 5 stars5/5 (1)

- Downloads Papers N56e7c208d031bDocument7 pagesDownloads Papers N56e7c208d031bqueenie sabanalNo ratings yet

- Moving Vehicle Registration Plate DetectionDocument6 pagesMoving Vehicle Registration Plate DetectionIJRASETPublicationsNo ratings yet

- 3-D Printable Open Source Dual Axis Gimbal System For OptoelectronicDocument13 pages3-D Printable Open Source Dual Axis Gimbal System For Optoelectronicmuhammet zahit bakışNo ratings yet

- Iccter - 2014Document299 pagesIccter - 2014iaetsdiaetsdNo ratings yet

- Final Project Report Crime Data 2Document38 pagesFinal Project Report Crime Data 2kz9057No ratings yet

- Data-Driven Manufacturing A Paradigm Shift in The Manufacturing IndustryDocument5 pagesData-Driven Manufacturing A Paradigm Shift in The Manufacturing IndustryIJRASETPublicationsNo ratings yet

- A Low-Cost Calibration Method For Low-Cost MEMS AcDocument19 pagesA Low-Cost Calibration Method For Low-Cost MEMS AcAerojet Rocketdyne RS-25No ratings yet

- Adaptive Traffic Control SystemDocument7 pagesAdaptive Traffic Control SystemIJRASETPublicationsNo ratings yet

- Paper 8847Document5 pagesPaper 8847IJARSCT JournalNo ratings yet

- Overview On The Object Rejection and Counting Machine: July 2017Document4 pagesOverview On The Object Rejection and Counting Machine: July 2017dhanshri kolekarNo ratings yet

- 1 Ijcnwmcdec20181Document8 pages1 Ijcnwmcdec20181TJPRC PublicationsNo ratings yet

- Implementation of Hardware and Energy Efficient Approximate Multiplier Architectures UsingDocument9 pagesImplementation of Hardware and Energy Efficient Approximate Multiplier Architectures UsingIJRASETPublicationsNo ratings yet

- Development of A Methodology For ConditiDocument19 pagesDevelopment of A Methodology For ConditiAmag2011No ratings yet

- M.Phil Computer Science Biometric System ProjectsDocument3 pagesM.Phil Computer Science Biometric System ProjectskasanproNo ratings yet

- Smart Car Parking With Reservation System Using QR GeneratorDocument6 pagesSmart Car Parking With Reservation System Using QR GeneratorTechwikmathsNo ratings yet

- Mini Project Documentation1Document18 pagesMini Project Documentation1likithsiddardh3No ratings yet

- A Review On Lane Detection and Tracking TechniquesDocument8 pagesA Review On Lane Detection and Tracking TechniquesIJIERT-International Journal of Innovations in Engineering Research and TechnologyNo ratings yet

- Multilevel Secure Image Communication Based On (Cipher &stegnography) and Evaluation SecureDocument9 pagesMultilevel Secure Image Communication Based On (Cipher &stegnography) and Evaluation SecureInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Seminar ReportDocument30 pagesSeminar Reportmonty08350% (2)

- Implementation of Smart Vehicle Parking SystemDocument8 pagesImplementation of Smart Vehicle Parking SystemChany WeerasingheNo ratings yet

- 1 s2.0 S1877050922022815 MainDocument10 pages1 s2.0 S1877050922022815 Mainxdddd123aNo ratings yet

- Parking Survey Made Efficient in Intelligent Parking - 2016 - Procedia EngineerDocument9 pagesParking Survey Made Efficient in Intelligent Parking - 2016 - Procedia EngineerRamses BoxbergNo ratings yet

- 23621-Article Text-35768-1-10-20200613Document8 pages23621-Article Text-35768-1-10-20200613Samuel HamiltonNo ratings yet

- An Intelligent Data-Driven Model To Secure Intra - Vehicle Communications Based On Machine LearningDocument8 pagesAn Intelligent Data-Driven Model To Secure Intra - Vehicle Communications Based On Machine LearningIJRASETPublicationsNo ratings yet

- Robotic ArmDocument18 pagesRobotic ArmTrinesh GowdaNo ratings yet

- Vehicle Allowance SystemDocument7 pagesVehicle Allowance SystemIJRASETPublicationsNo ratings yet

- Accuracy in The Digital Work Ow: From Data Acquisition To The Digitally Milled CastDocument6 pagesAccuracy in The Digital Work Ow: From Data Acquisition To The Digitally Milled Castmarianaduque82No ratings yet

- Rfid Based Metro Train SystemDocument4 pagesRfid Based Metro Train SystemJane VpnNo ratings yet

- Project ReportDocument26 pagesProject ReportHarshith Kumar hvNo ratings yet

- A Three Dimensional Triangular Vision Based Contouring Error Detection System and Method For Machine Tools - 2017 - Precision EngineeringDocument14 pagesA Three Dimensional Triangular Vision Based Contouring Error Detection System and Method For Machine Tools - 2017 - Precision EngineeringCamilo BaronNo ratings yet

- CSTRNGDocument5 pagesCSTRNGTulasi RadhikaNo ratings yet

- Design of Intelligent Braking System: February 2000Document7 pagesDesign of Intelligent Braking System: February 2000Sandeepkumar SgNo ratings yet

- ANN and ANFIS Based Inverse Kinematics of Six Arm Robot ManipulatorDocument81 pagesANN and ANFIS Based Inverse Kinematics of Six Arm Robot Manipulatorpaloooo0% (1)

- Rfid BunDocument7 pagesRfid BunSimona NicoletaNo ratings yet

- Meaning and Nature of SMDocument3 pagesMeaning and Nature of SMArpit SharmaNo ratings yet

- MR Regis N MRS Dorcas Taruvinga - 050209Document1 pageMR Regis N MRS Dorcas Taruvinga - 050209pzarchitectural99No ratings yet

- Goodman ss-gsz16Document36 pagesGoodman ss-gsz16nam nguyenNo ratings yet

- Practical Tools For Attackers and Defenders: 6.1 Steps To Launch An AttackDocument42 pagesPractical Tools For Attackers and Defenders: 6.1 Steps To Launch An AttackRaghu Vamsi PNo ratings yet

- Calculating The Temperature RiseDocument8 pagesCalculating The Temperature Risesiva anandNo ratings yet

- List of Doctors Clinics HospitalsDocument6 pagesList of Doctors Clinics HospitalsAjay Kaushik50% (2)

- Mendoza EAPP Q1 Module 2 Week 2 Structure of An Academic TextDocument10 pagesMendoza EAPP Q1 Module 2 Week 2 Structure of An Academic TextEllie Pasion67% (3)

- Naiad GettingstartedDocument37 pagesNaiad GettingstartedYurivanovNo ratings yet

- Chapter 1 Nature of OrganizationDocument29 pagesChapter 1 Nature of OrganizationNicole VelascoNo ratings yet

- English Mid Test A: Hawaiian TraditionsDocument4 pagesEnglish Mid Test A: Hawaiian TraditionsAnugrah WijagauNo ratings yet

- Report Evaporator Sculptor Behr 120405Document11 pagesReport Evaporator Sculptor Behr 120405gosculptorNo ratings yet

- COMM 263 Radio/TV Production TV Studio Production Notes: Birth of TelevisionDocument16 pagesCOMM 263 Radio/TV Production TV Studio Production Notes: Birth of TelevisionhotalamNo ratings yet

- Mba Project GayatriDocument55 pagesMba Project GayatriSubrat PatnaikNo ratings yet

- Types of Business WritingDocument103 pagesTypes of Business WritingJoe San JuanNo ratings yet

- ANAPHY Lec Session #4 - SASDocument10 pagesANAPHY Lec Session #4 - SASFherry Mae UsmanNo ratings yet

- Field Manual: System 1010Dvn Nema Clamp-On Multi-Function FlowmeterDocument182 pagesField Manual: System 1010Dvn Nema Clamp-On Multi-Function FlowmeterRicardo souzaNo ratings yet

- QC DissertationDocument85 pagesQC DissertationAhmed MahmoudNo ratings yet

- Elearning Brochure HL7Document2 pagesElearning Brochure HL7Raju RajputNo ratings yet

- Bagrut Module D Answers To The Treasure of Lemon BrownDocument8 pagesBagrut Module D Answers To The Treasure of Lemon BrownMohammed ArarNo ratings yet

- Pratik ResumeDocument2 pagesPratik ResumeHarshada lawaleNo ratings yet

- Turbo Chargers T3-T4Document1 pageTurbo Chargers T3-T4Andries FerreiraNo ratings yet

- Hot Dip Galvanized CoatingDocument28 pagesHot Dip Galvanized CoatingOci Rizal100% (6)

- E. TABLE OF CONTENTSDocument9 pagesE. TABLE OF CONTENTSAlexa Nicole GayosoNo ratings yet

- 2009 SL School Release MaterialsDocument146 pages2009 SL School Release MaterialsAditiPriyankaNo ratings yet

- A Detailed Lesson Plan in English 9: (Using Adverbs in Narration)Document8 pagesA Detailed Lesson Plan in English 9: (Using Adverbs in Narration)Faith Malinao100% (1)

- Chapter-I Elections of 1936-37 and Muslim LeagueDocument63 pagesChapter-I Elections of 1936-37 and Muslim LeagueAdeel AliNo ratings yet

- Maxim Hand OutDocument7 pagesMaxim Hand OutArlene Aurin-AlientoNo ratings yet

- AFATL-TR-72-401 - Developement of 20MM and 30MM Plastic-Aluminium Cartridge Cases (1972)Document91 pagesAFATL-TR-72-401 - Developement of 20MM and 30MM Plastic-Aluminium Cartridge Cases (1972)defendercc130No ratings yet