Professional Documents

Culture Documents

Digital System Design - UEC 612 Tutorial# 8

Digital System Design - UEC 612 Tutorial# 8

Uploaded by

Lakshit GuptaCopyright:

Available Formats

You might also like

- Qualcomm Interview ExperienceDocument2 pagesQualcomm Interview Experienceksnmurthy0475No ratings yet

- Tute 3Document4 pagesTute 3mgayanan0% (1)

- Microprocessor AptiDocument7 pagesMicroprocessor AptiprachiumangNo ratings yet

- Master SetDocument624 pagesMaster SetEr Lokesh MahorNo ratings yet

- DC Assignment 2019 PDFDocument2 pagesDC Assignment 2019 PDFRashmi VermaNo ratings yet

- Sample Questions: Chapter One: Digital Building BlocksDocument4 pagesSample Questions: Chapter One: Digital Building BlocksDonnNo ratings yet

- Assignment 2Document3 pagesAssignment 2Super SpecialNo ratings yet

- Te Oct 2014Document149 pagesTe Oct 2014contrasterNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- AVR Microcontroller TestDocument9 pagesAVR Microcontroller TestNiranjan AgravatNo ratings yet

- 6 CountersDocument61 pages6 CountersRJ AdepuNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- QuizzDocument1 pageQuizzkalshkinguNo ratings yet

- Tutorial 03Document2 pagesTutorial 03balNo ratings yet

- MSQ Session 5 19Document30 pagesMSQ Session 5 19Voleti VnkumarNo ratings yet

- QPDocument3 pagesQPAnonymous 9WJ7YeGNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- Ejercicios S3Document10 pagesEjercicios S3diegogachet1618No ratings yet

- Ee6008 Fiat QBDocument2 pagesEe6008 Fiat QBAthithyaNo ratings yet

- DCEPFDocument11 pagesDCEPFkanishkhatanaNo ratings yet

- List of Important QuestionsDocument6 pagesList of Important Questions4025 deeptika pNo ratings yet

- DC Question BankDocument2 pagesDC Question BankAnanda HembramNo ratings yet

- Hours - ?: Model Questigi/ Yiiar Examination Fifth Examination Electrical DigitalDocument1 pageHours - ?: Model Questigi/ Yiiar Examination Fifth Examination Electrical Digitalapi-279049687No ratings yet

- MCI Question BankDocument2 pagesMCI Question BankHet PatelNo ratings yet

- Network Basics CollectionDocument11 pagesNetwork Basics Collectionrocks66aryanNo ratings yet

- Questions On Digital Electronics and MicroprocessorsDocument12 pagesQuestions On Digital Electronics and MicroprocessorsHarendra KumarNo ratings yet

- Question Paper: A Answer All The QuestionsDocument3 pagesQuestion Paper: A Answer All The QuestionsHarshita GauravNo ratings yet

- Question Bank - DC 6501Document10 pagesQuestion Bank - DC 6501karthikamageshNo ratings yet

- Analog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Document11 pagesAnalog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Adonis LealNo ratings yet

- Quiz Questions On Unit 2 Microcontroller (8051)Document15 pagesQuiz Questions On Unit 2 Microcontroller (8051)Manveen KaurNo ratings yet

- Eee ADocument6 pagesEee ASundaravadivel ArumugamNo ratings yet

- FL051 DethiCLC20222 De1 Dapan Vi Dieu KhienDocument8 pagesFL051 DethiCLC20222 De1 Dapan Vi Dieu KhienMinh Nguyen HoangNo ratings yet

- Question Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Document9 pagesQuestion Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Nithya SNo ratings yet

- Aprilmay 2009Document8 pagesAprilmay 2009Viswa ChaitanyaNo ratings yet

- ADVD Digital Assignment Updated - Microwind-2023Document20 pagesADVD Digital Assignment Updated - Microwind-2023nimitjain.248No ratings yet

- QB - Basics of Com - OrganizationDocument11 pagesQB - Basics of Com - OrganizationAarya ShilimkarNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- Advanced Digital Communication1 December 2011Document2 pagesAdvanced Digital Communication1 December 2011Sneha UpadhyayulaNo ratings yet

- Computer Organization and Architecture (01CE0402) Lab ManualDocument4 pagesComputer Organization and Architecture (01CE0402) Lab ManualrockyNo ratings yet

- Sample Exam QuestionsDocument9 pagesSample Exam Questionssomeguyinoz100% (1)

- Final Exam: ECE 697 Delta-Sigma Data Converter Design (Spring 2010) Due On Thursday, May 15, 2010Document5 pagesFinal Exam: ECE 697 Delta-Sigma Data Converter Design (Spring 2010) Due On Thursday, May 15, 2010anjugaduNo ratings yet

- Digital Communications (DCOM)Document4 pagesDigital Communications (DCOM)Mamotete MohohloNo ratings yet

- Final Apr 03 SolnsDocument16 pagesFinal Apr 03 Solnsapi-3755462No ratings yet

- Digital QuestionsDocument3 pagesDigital Questionsmdhuq1No ratings yet

- 7 Counters PDFDocument13 pages7 Counters PDFsaraswatthiNo ratings yet

- PDC 1Document4 pagesPDC 1Lavanya_123No ratings yet

- Do Practice CODocument2 pagesDo Practice COSudeep SharmaNo ratings yet

- 4C Reports: Introduction To Labview & Ni-Usrp (C1)Document3 pages4C Reports: Introduction To Labview & Ni-Usrp (C1)Cyrille MagdiNo ratings yet

- Assignment 4Document4 pagesAssignment 4fungp 0505No ratings yet

- Assignment-EE 361/chapter 4: (CLO-2) : MT T MT T T MT T T MT C T MT MT TDocument4 pagesAssignment-EE 361/chapter 4: (CLO-2) : MT T MT T T MT T T MT C T MT MT TRana AbrarNo ratings yet

- Assignment 4Document4 pagesAssignment 4Shahzaib NadeemNo ratings yet

- Unit 5Document11 pagesUnit 5RajaNo ratings yet

- Ec34 Question BankDocument6 pagesEc34 Question Bankkartheeswaran11No ratings yet

- Sequential CircuitsDocument33 pagesSequential CircuitsPrasun SinghalNo ratings yet

- Tutorial 11 19042024Document10 pagesTutorial 11 19042024Sayam SanchetiNo ratings yet

- Analog Guide RajaReddyDocument30 pagesAnalog Guide RajaReddyKirti Susan VargheseNo ratings yet

- Sayıcılar (Counters) : Mantık Devreleri Yard - Doç.Dr. Mutlu BOZTEPEDocument37 pagesSayıcılar (Counters) : Mantık Devreleri Yard - Doç.Dr. Mutlu BOZTEPEGe NNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

Digital System Design - UEC 612 Tutorial# 8

Digital System Design - UEC 612 Tutorial# 8

Uploaded by

Lakshit GuptaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital System Design - UEC 612 Tutorial# 8

Digital System Design - UEC 612 Tutorial# 8

Uploaded by

Lakshit GuptaCopyright:

Available Formats

Digital System Design – UEC 612

Tutorial# 8

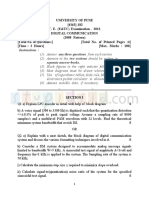

1. A 10-bit ripple counter has a 256-kHz clock signal applied: -

(a) What is the MOD number of this counter?

(b) What will be the frequency at the MSB output?

(c) What will be the duty cycle of the MSB signal?

(d) Assume that the counter starts at zero. What will be the count in hexadecimal after

1000 input pulses?

2. A four-bit ripple counter is driven by a 20-MHz clock signal. Draw the waveforms at the

output of each FF if each FF has tpd of 20 ns. Determine which counter states, if any, will not

occur because of the propagation delays.

3. What is the maximum clock frequency fmax that can be used with the counter in above

problem? What would fmax be if the counter is expanded to six bits?

4. For the following state table:-

(a) Draw the corresponding state diagram.

(b) Identify redundant states, if any. Tabulate the reduced state table.

(c) Draw the state diagram corresponding to the reduced state table

6. Derive the state table and the state diagram of the sequential circuit below.

Explain the function that the circuit performs.

You might also like

- Qualcomm Interview ExperienceDocument2 pagesQualcomm Interview Experienceksnmurthy0475No ratings yet

- Tute 3Document4 pagesTute 3mgayanan0% (1)

- Microprocessor AptiDocument7 pagesMicroprocessor AptiprachiumangNo ratings yet

- Master SetDocument624 pagesMaster SetEr Lokesh MahorNo ratings yet

- DC Assignment 2019 PDFDocument2 pagesDC Assignment 2019 PDFRashmi VermaNo ratings yet

- Sample Questions: Chapter One: Digital Building BlocksDocument4 pagesSample Questions: Chapter One: Digital Building BlocksDonnNo ratings yet

- Assignment 2Document3 pagesAssignment 2Super SpecialNo ratings yet

- Te Oct 2014Document149 pagesTe Oct 2014contrasterNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- AVR Microcontroller TestDocument9 pagesAVR Microcontroller TestNiranjan AgravatNo ratings yet

- 6 CountersDocument61 pages6 CountersRJ AdepuNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- QuizzDocument1 pageQuizzkalshkinguNo ratings yet

- Tutorial 03Document2 pagesTutorial 03balNo ratings yet

- MSQ Session 5 19Document30 pagesMSQ Session 5 19Voleti VnkumarNo ratings yet

- QPDocument3 pagesQPAnonymous 9WJ7YeGNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- Ejercicios S3Document10 pagesEjercicios S3diegogachet1618No ratings yet

- Ee6008 Fiat QBDocument2 pagesEe6008 Fiat QBAthithyaNo ratings yet

- DCEPFDocument11 pagesDCEPFkanishkhatanaNo ratings yet

- List of Important QuestionsDocument6 pagesList of Important Questions4025 deeptika pNo ratings yet

- DC Question BankDocument2 pagesDC Question BankAnanda HembramNo ratings yet

- Hours - ?: Model Questigi/ Yiiar Examination Fifth Examination Electrical DigitalDocument1 pageHours - ?: Model Questigi/ Yiiar Examination Fifth Examination Electrical Digitalapi-279049687No ratings yet

- MCI Question BankDocument2 pagesMCI Question BankHet PatelNo ratings yet

- Network Basics CollectionDocument11 pagesNetwork Basics Collectionrocks66aryanNo ratings yet

- Questions On Digital Electronics and MicroprocessorsDocument12 pagesQuestions On Digital Electronics and MicroprocessorsHarendra KumarNo ratings yet

- Question Paper: A Answer All The QuestionsDocument3 pagesQuestion Paper: A Answer All The QuestionsHarshita GauravNo ratings yet

- Question Bank - DC 6501Document10 pagesQuestion Bank - DC 6501karthikamageshNo ratings yet

- Analog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Document11 pagesAnalog - Sine Wave Generation With Psoc 1 (Demonstration With CTCSS)Adonis LealNo ratings yet

- Quiz Questions On Unit 2 Microcontroller (8051)Document15 pagesQuiz Questions On Unit 2 Microcontroller (8051)Manveen KaurNo ratings yet

- Eee ADocument6 pagesEee ASundaravadivel ArumugamNo ratings yet

- FL051 DethiCLC20222 De1 Dapan Vi Dieu KhienDocument8 pagesFL051 DethiCLC20222 De1 Dapan Vi Dieu KhienMinh Nguyen HoangNo ratings yet

- Question Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Document9 pagesQuestion Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Nithya SNo ratings yet

- Aprilmay 2009Document8 pagesAprilmay 2009Viswa ChaitanyaNo ratings yet

- ADVD Digital Assignment Updated - Microwind-2023Document20 pagesADVD Digital Assignment Updated - Microwind-2023nimitjain.248No ratings yet

- QB - Basics of Com - OrganizationDocument11 pagesQB - Basics of Com - OrganizationAarya ShilimkarNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- Advanced Digital Communication1 December 2011Document2 pagesAdvanced Digital Communication1 December 2011Sneha UpadhyayulaNo ratings yet

- Computer Organization and Architecture (01CE0402) Lab ManualDocument4 pagesComputer Organization and Architecture (01CE0402) Lab ManualrockyNo ratings yet

- Sample Exam QuestionsDocument9 pagesSample Exam Questionssomeguyinoz100% (1)

- Final Exam: ECE 697 Delta-Sigma Data Converter Design (Spring 2010) Due On Thursday, May 15, 2010Document5 pagesFinal Exam: ECE 697 Delta-Sigma Data Converter Design (Spring 2010) Due On Thursday, May 15, 2010anjugaduNo ratings yet

- Digital Communications (DCOM)Document4 pagesDigital Communications (DCOM)Mamotete MohohloNo ratings yet

- Final Apr 03 SolnsDocument16 pagesFinal Apr 03 Solnsapi-3755462No ratings yet

- Digital QuestionsDocument3 pagesDigital Questionsmdhuq1No ratings yet

- 7 Counters PDFDocument13 pages7 Counters PDFsaraswatthiNo ratings yet

- PDC 1Document4 pagesPDC 1Lavanya_123No ratings yet

- Do Practice CODocument2 pagesDo Practice COSudeep SharmaNo ratings yet

- 4C Reports: Introduction To Labview & Ni-Usrp (C1)Document3 pages4C Reports: Introduction To Labview & Ni-Usrp (C1)Cyrille MagdiNo ratings yet

- Assignment 4Document4 pagesAssignment 4fungp 0505No ratings yet

- Assignment-EE 361/chapter 4: (CLO-2) : MT T MT T T MT T T MT C T MT MT TDocument4 pagesAssignment-EE 361/chapter 4: (CLO-2) : MT T MT T T MT T T MT C T MT MT TRana AbrarNo ratings yet

- Assignment 4Document4 pagesAssignment 4Shahzaib NadeemNo ratings yet

- Unit 5Document11 pagesUnit 5RajaNo ratings yet

- Ec34 Question BankDocument6 pagesEc34 Question Bankkartheeswaran11No ratings yet

- Sequential CircuitsDocument33 pagesSequential CircuitsPrasun SinghalNo ratings yet

- Tutorial 11 19042024Document10 pagesTutorial 11 19042024Sayam SanchetiNo ratings yet

- Analog Guide RajaReddyDocument30 pagesAnalog Guide RajaReddyKirti Susan VargheseNo ratings yet

- Sayıcılar (Counters) : Mantık Devreleri Yard - Doç.Dr. Mutlu BOZTEPEDocument37 pagesSayıcılar (Counters) : Mantık Devreleri Yard - Doç.Dr. Mutlu BOZTEPEGe NNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet