Professional Documents

Culture Documents

Tugas Rangkaian Logika

Tugas Rangkaian Logika

Uploaded by

Ilham Bayu TiasmoroOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tugas Rangkaian Logika

Tugas Rangkaian Logika

Uploaded by

Ilham Bayu TiasmoroCopyright:

Available Formats

Technical Diagnosis of Basic Logic Gates

Z. Tucaković

Automatic Control and Electronics Department, Faculty of Electrical Engineering Sarajevo

Sarajevo, Bosnia and Herzegovina

ztucakovic1@etf.unsa.ba

Abstract - In this paper, fault diagnosis of elementary logic

gates is presented and most common causes of gate failure

with a special focus on the diagnostic tests are discussed.

The practical part of this paper includes the solution

implementation, and more specifically, building the testing

prototype. To support this, electrical schematic of the circuit

is included, as well as the final design of the device.

I. INTRODUCTION

During laboratory assignments in electronics, different

problems might occur. Resistors, capacitors, transistors, as

well as other components in complex devices such as

logic gates might be dysfunctional or damaged. Many Figure 1: Common symbols for logic gates (NOT, AND, OR, NAND,

integrated chips have several integrated logic gates on NOR) and symbols according to IEC

them (i.e. gate 7400 has four NAND gates, each with two

inputs). If one gate on a chip is damaged, usually another

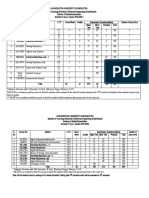

TABLE I. TRUTH TABLE FOR ABOVE MENTIONED OPERATIONS

gate is used. After that, the chip is left in the laboratory

and the person coming next will assume it is fully A B A’ B’ A˄B A˅B A|B A↓B

functional. 0 0 1 1 0 0 1 1

That is the reason behind checking the functionality of 0 1 1 0 0 1 1 0

a chip. It can be done by setting logic zeros and logic ones 1 0 0 1 0 1 1 0

on inputs of logic gates. This can be a cumbersome task,

1 1 0 0 1 1 0 0

and that is the reason why automation of the process is

useful, easier and faster. Automation of logic gates

functionality check is the subject of this paper. The Sheffer’s and Peirce’s operation, respectively [6].

prototype of a device which checks the functionality of Symbols of all these gates are given in Figure 1.

basic logic gates has been made and the user would be

provided with the information which gates inside the chip In Table I the truth tables for aforementioned

are functional. References [1] and [2] deal with this operations are given.

problem.

III. CAUSES OF LOGIC GATES MALFUNCTION

In the second chapter, theoretical basis for basic logic

gates is given. In the third and fourth chapter, causes of A malfunction of a logic gate is a physical defect of

malfunction and generation of diagnostic tests are one or more of its components, which causes malfunction

analyzed. Fifth chapter contains description of the of the entire system. Sometimes, a logic gate is

prototype structure and its parts (specifically power supply, permanently damaged. This class of malfunctions is

microcontroller [3], display [4], keyboard, zero insertion caused by errors in element production or by the

force socket, as well as integrated chip, whose components aging [7].

functionality will be tested). In the sixth chapter the The class of temporary malfunctions is caused by

algorithm of testing is presented, and in the seventh is badly synchronized structures or asynchronous structures

given programming code that implements the algorithm. of digital systems, different disturbances caused by

Chapter eight contains appendices, i.e. photos of the internal noise or external influences. In this class there

prototype and its electronic scheme. are categories of random and categories of occasional

malfunctions. Occasional malfunctions can become

II. THEORETICAL BASIS FOR BASIC LOGIC GATES permanent with time, and these malfunctions are then

The logic gate is an electronic circuit or a device, called constant malfunctions. They usually occur in

implementing a Boolean function [5]. Basic logic gates digital systems, discrete systems or in integrated circuits.

are usually NOT, AND, OR, NAND and NOR gates, and They occur in the lowest levels of integration, as well as

they represent logical negation, conjunction, disjunction, in Large-scale integration (LSI) and Very-large-scale-

integration (VLSI).

MIPRO 2016/SP 1879

However, in digital systems which use LSI and VLSI IV. DIAGNOSTICS TEST GENERATION

components, temporary malfunctions often occur. They

are a special problem regarding malfunction detection, Inspecting the functionality of logic gate varies from

especially in attempts to identify what causes them. Many one gate to another. For example, if the integrated chip

methods, which are formed for detection and 7400 is inspected (it consists of four NAND gates with

identification of constant malfunctions can be used for two inputs, and its pin arrangement is shown in Figure 3),

diagnostics of temporary malfunctions, if diagnostics then each of four NAND gates will be inspected as

programs are processed in an on-line mode of the digital described in the following text, and results will be

system. This applies only to digital systems, which compared with the results of ideal, correct NAND gate.

include at least one digital computer. Every method of checking logic gate functionality

In Figure 2, an implementation of a NOT gate is must set gate inputs on logic zeros or ones and compare

shown. The input is marked as x, and the output as y. If output to the ideal, expected output (output of the

this circuit works correctly, then y should be negated x. functional gate). If they are not identical, inspected logic

Possible physical defect of the NOT gate (Figure 2) gate has a malfunction. If they are identical, next

and the value of output in that case are shown in Table II. combination of logic zeros and ones should be set on

In these cases, output holds the same value for both inputs. This process continues until there are no

inputs (0 and 1). That value is permanent 0 or permanent combinations left untested.

1 (p-0 or p-1), and represents a class of constant There are many methods for checking logic gate

malfunctions. functionality. In this paper, two will be considered:

Multiple malfunctions are also possible, but they are

rare and can cause other types and classes of - Checking logic gate functionality using sequential logic,

malfunctions. In essence, malfunction in a circuit also - Using a microcontroller.

appears when a logic gate does not have output. That is Basic properties of each method are:

defined by the truth table of a given operation. In this

paper, the accent is not on finding the reason of 1. Size of prototype

malfunction, but on the identification of malfunction (if

Use of both sequential logic and microcontroller

one exists).

results in small final product, especially if a printed

circuit board (PCB) is used.

2. Connections between components

Sequential logic demands much more components

than a microcontroller, which makes the final product

more complicated and increases the probability that

one of used components has a malfunction. In

sequential logic, a large number of flip-flops is

necessary, because the final product is quite

complicated automaton. On the other hand, there are

less components if a microcontroller is used, but it

requires a source code for it.

3. Necessity for additional elements and the

Figure 2: Possible implementation of NOT gate [7] increase of the number of gates that are able to

inspect

TABLE II. POSSIBLE PHYSICAL DEFECTS OF NOT GATE (FIGURE 2)

[7] Sequential logic cannot provide simple addition of

external components (without making the prototype

Physical defects Value of output y extremely complicated), unlike microcontroller.

Base (b) of transistor T is open-circuited 1 Keyboard, display and other elements that make the

Collector (c) is open-circuited 0 prototype more user friendly, can be easily added to

Emitter (e) is open-circuited 1 microcontroller. The user utilizes a keyboard to

specify which logic gate will be tested. Every

Points b and c are short-circuited 0

additional component functionality must be

Points b and e are short-circuited 1 implemented in the code, but it doesn’t require much

Points c and e are short-circuited 0 effort.

Resistor Rc is open-circuited 0

Subject to the above mentioned advantages, a

Resistor Rc is short-circuited 1 microcontroller is chosen to be used for testing the

functionality of a logic gate.

1880 MIPRO 2016/SP

Figure 3: Pin arrangement of 7400 chip

Figure 4: Block structure of the system

Figure 5: Pin rearrangements of gates 7400, 7402, 7404, 7408 and

7432 and gate numeration inside the chip

V. SYSTEM STRUCTURE

the row of that button are on the same potential.

The system consists of a microcontroller, a keyboard,

a display and some additional elements, such as zero

insertion force socket and an integrated chip whose 5. Zero insertion force socket

functionality is tested [1], [2]. Figure 4 shows a block The zero insertion force socket (ZIF) is used to

structure of the prototype. The central element is a simplify usage for users. In this case, ZIF with 20 pins

microcontroller. It communicates with a logic gate, is used. An integrated chip, which is to be tested, is

keyboard and display. Communications Microcontroller- put in ZIF. Afterwards, the chip cannot be pulled out

gate and microcontroller-keyboard are bidirectional, without moving the handle, there is a firm connection

unlike microcontroller-display which uses unidirectional between ZIF and the integrated chip.

communication (a display is used only for displaying data

sent by microcontroller). 6. Integrated circuit

Testing of aforementioned gates is done for this

1. Power supply matter. The following gates are used:

Very important element of the developed system is - 7400 - consists of four NAND gates with two inputs,

power supply. For this matter, 230V/50Hz AC voltage - 7402 - consists of four NOR gates with two inputs,

is used. Microcontroller and logic gates demand 5V - 7404 - consists of six NOT gates,

DC for their power supply, therefore AC-DC - 7408 - consists of four AND gates with two inputs,

conversion is needed and the following elements are - 7432 - consists of four OR gates with two inputs.

used: filter, switch, fuse, transformer, rectifier and

regulator, resistors and capacitors (shown in Figure 8, Figure 5 shows pin rearrangements of listed gates.

lower part).

2. Microcontroller VI. TESTING ALGORITHM

Microchip’s microcontroller PIC16F1939 is used for

this purpose [3]. Testing algorithm is shown in Figure 6 via flow charts

[1].

3. Display

Liquid Crystal Display (LCD) AV1624 of ANAG VII. SOURCE CODE

VISION is used for displaying results of logic gate

testing, as well as user-machine interaction. Two rows, The algorithm is developed in programming language

each with 16 characters can be displayed C, and written into the microcontroller. Code must include

simultaneously [4]. functions for initialization of microcontrollers’ ports and

initialization and testing the functionality of

4. Keyboard aforementioned gates, a function for identifying which

Using a keyboard, a user can enter a number of a button on keyboard is pressed (if any) and the main

logic gate to be tested. The keyboard has 16 buttons function in which, depending on the button pressed,

(4 rows and 4 columns) and eight pins. First four pins certain procedures are given.

represent rows, the rest represent columns. When a

button is pushed, pins corresponding the column and

MIPRO 2016/SP 1881

Figure 7: Final design of the prototype

The procedure of functionality testing is described

earlier. Every gate is presumed to be without malfunction

until proven contrary. If for every combination of inputs,

output of gate is identical to the expected output, then the

gate is without malfunctions. If for at least one

combination of inputs, the output is different, then the gate

has a malfunction.

Checking whether any button is pressed is done by

checking whether two pins (one from first half and the

other from second) are on same potential, and that is done

by setting one by one, four output pins on logic one, and

testing if there is a logic one on any of input pins.

In the main function, depending on pressed button,

certain procedure is given. If a user enters more than six

digits that symbolize the gate’s name, an error message

will be written on LCD. If the gate name entered is not in

database (7400, -02, -04, -08 and -32), there will be an

error message.

VIII. FINAL PRODUCT

Figure 7 shows the final design of the prototype. In

Figure 8 complete electronic scheme of the prototype is

shown.

IX. CONCLUSION

In this paper, entire process of planning and

production of electronic device is given. First, theoretical

basis of logic gates, causes of malfunction and

malfunction diagnosis are explained. After that, thorough

analysis and planning software (programming code), as

Figure 6: Testing algorithm of the prototype well as hardware (electronic components) is made.

Functionality of code was checked, first through

A port (eight pins) connected with the keyboard is simulation, and later by a number of experiments on a real

initialized as half input and half output port. Integrated circuit. After numerous verifications, the final version of

chip to be tested is connected with two ports. The port code is obtained. Only after that, the device could be built,

connected to LCD is the output port. Pins connected to the and packed in a box. In that way, the prototype is simpler

integrated chip (via ZIF) are initialized as output pins if and safer for usage. Final product can be commercialized,

corresponding pin of the chip is input, and vice versa. A and be very useful during laboratory assignments.

pin connected to power supply of the chip is declared as

output. All mentioned pins are digital outputs or inputs.

1882 MIPRO 2016/SP

Figure 8: Complete electronic scheme of the prototype

The prototype, besides for checking functionality of [2] A.A. Shinde, M.A. Tarkunde, “IC Tester Using 89s52

logic gates, can be used for identification of unknown 14- Microcontroller”, International Journal of Computational

Engineering Research, vol. 2, issue 7, pp.24-27, November 2012.

pinned logic gate from 74-series. It is advised to

[3] Microchip’s PIC16F1939 Microcontroller Datasheet,

implement functionalities for a larger number of logic http://ww1.microchip.com/downloads/en/DeviceDoc/40001574C.

gates through the programming code. pdf

[4] ANAG VISION’s AV1624 LCD Datasheet, http://www.iq-

REFERENCES tm.de/astro/EQ6/184594-da-01-ml-

LCD_Modul_16x2_Zeichen_LED_de_en.pdf

[1] A. Bhattacharya, “Digital Integrated Circuit Tester (Using

[5] M. Ahić-Đokić, “Logički dizajn”, Faculty of Electrical

AT89s51 Microcontroller)”, International Journal of Emerging

Engineering Sarajevo, Sarajevo, 2006.

Technology and Advanced Engineering, vol. 3, issue 6, pp.175-

178, June 2013. [6] Ž. Jurić, “Diskretna matematika za studente tehničkih nauka”,

Faculty of Electrical Engineering Sarajevo, Sarajevo, 2011.

[7] Dž. Hasanbegović, “Osnove tehničke dijagnostike digitalnih

sistema”, Svjetlost, Sarajevo, 1985.

MIPRO 2016/SP 1883

View publication stats

You might also like

- On The LoRa Chirp Spread Spectrum Modulation Signal Properties and Their Impact On Transmitter and Receiver ArchitecturesDocument13 pagesOn The LoRa Chirp Spread Spectrum Modulation Signal Properties and Their Impact On Transmitter and Receiver ArchitecturesDavenne IdrissiNo ratings yet

- Manual Laboratorio LaunchpadDocument54 pagesManual Laboratorio LaunchpadAnthony ACNo ratings yet

- Lab5 Synopsys Tetramax DFTDocument20 pagesLab5 Synopsys Tetramax DFTJay PadaliyaNo ratings yet

- EIP Book of KnowledgeDocument120 pagesEIP Book of Knowledgelarry_beeNo ratings yet

- K Value of FittingsDocument4 pagesK Value of FittingsJoydip Misra100% (6)

- Signals and Systems Kuestion (EE) PDFDocument48 pagesSignals and Systems Kuestion (EE) PDFsanthoshNo ratings yet

- HP Signature AnalysisDocument24 pagesHP Signature AnalysisRodolfoBucaloNo ratings yet

- DIGITAL CIRCUIT SimulationDocument60 pagesDIGITAL CIRCUIT SimulationNidheesh KMNo ratings yet

- Report On Logic Gates SimulatorDocument62 pagesReport On Logic Gates SimulatorAmrita0527100% (4)

- Experiment Title. 1Document9 pagesExperiment Title. 1Pragnya RajNo ratings yet

- Cpe 301 Lab 1 - CaringalDocument8 pagesCpe 301 Lab 1 - CaringalAlecxis CaringalNo ratings yet

- Synthesizing Combinational Logic Circuits: Laboratory Experiment No. 4Document8 pagesSynthesizing Combinational Logic Circuits: Laboratory Experiment No. 4DervNo ratings yet

- Plate No. 1 Application of Sequential Circuit Queueing SystemDocument5 pagesPlate No. 1 Application of Sequential Circuit Queueing SystemejlorsNo ratings yet

- L28 Unit 5 ANALOG AND DIGITAL ELECTRONIC CIRCUITSDocument5 pagesL28 Unit 5 ANALOG AND DIGITAL ELECTRONIC CIRCUITSDr G VijayakumarNo ratings yet

- FPGA Implementation of Self-Testing Logic Gates AdDocument7 pagesFPGA Implementation of Self-Testing Logic Gates AdTakashi SuohNo ratings yet

- 255 - For Ubicc - 255Document6 pages255 - For Ubicc - 255Ubiquitous Computing and Communication JournalNo ratings yet

- Sensitivity of A Chaotic Logic GateDocument5 pagesSensitivity of A Chaotic Logic Gatenfhdh1094No ratings yet

- Department of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsDocument14 pagesDepartment of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsMuhammad RehanNo ratings yet

- PP 41-45 Testing System For Control Panel of SwitchgearDocument6 pagesPP 41-45 Testing System For Control Panel of SwitchgearEditorijset IjsetNo ratings yet

- Programmable Logic Control: Department of Electrical and ElectronicsDocument35 pagesProgrammable Logic Control: Department of Electrical and ElectronicsApurva BangaleNo ratings yet

- DT Key MaretrialDocument12 pagesDT Key MaretrialSudheer RajaNo ratings yet

- ECEN 248 Lab 7 ReportDocument7 pagesECEN 248 Lab 7 ReportRebecca Sontheimer0% (1)

- In-Field Test For Permanent Faults in FIFO Buffers of NoC RoutersDocument6 pagesIn-Field Test For Permanent Faults in FIFO Buffers of NoC Routersanon_287498671No ratings yet

- Test AbilityDocument13 pagesTest AbilityGaurav MehraNo ratings yet

- Asynchronous Microcontroller Simulation Model in VHDL: M. KovacDocument4 pagesAsynchronous Microcontroller Simulation Model in VHDL: M. KovacIacob CiprianNo ratings yet

- Final - Volume 3 No 4Document105 pagesFinal - Volume 3 No 4UbiCC Publisher100% (1)

- Cell-Aware ATPG Test Methods Improve Test Quality: A Brief History of IC TestDocument8 pagesCell-Aware ATPG Test Methods Improve Test Quality: A Brief History of IC Testsenthilkumar100% (1)

- Automatic Power Saving System Using PLC (Programmable Logic Controller)Document3 pagesAutomatic Power Saving System Using PLC (Programmable Logic Controller)Hamza QadirNo ratings yet

- A Study On Test Quality Analysis and Improvement For An Embedded Asynchronous FIFODocument7 pagesA Study On Test Quality Analysis and Improvement For An Embedded Asynchronous FIFORamesh DamaNo ratings yet

- A New Interlock System For The Vulcan LaserDocument4 pagesA New Interlock System For The Vulcan LaserMohammad A. BawtagNo ratings yet

- Ecen 248 Lab 9 ReportDocument5 pagesEcen 248 Lab 9 Reportapi-241454978No ratings yet

- ECT Chapter 2Document9 pagesECT Chapter 2Hnd FinalNo ratings yet

- Cacho, KathleenJoyC. (ESD FE)Document5 pagesCacho, KathleenJoyC. (ESD FE)KATHLEEN JOY CACHONo ratings yet

- Hima Fail Safe PesDocument17 pagesHima Fail Safe PeschochoroyNo ratings yet

- LAB04Document15 pagesLAB04زياد عبدالله عبدالحميدNo ratings yet

- Security Labs in OPNET IT Guru: Enginyeria I Arquitectura La Salle Universitat Ramon Llull Barcelona 2004Document9 pagesSecurity Labs in OPNET IT Guru: Enginyeria I Arquitectura La Salle Universitat Ramon Llull Barcelona 2004Florin SilivăstruNo ratings yet

- Automated Anomaly and Root Cause Detection in Distributed SystemsDocument6 pagesAutomated Anomaly and Root Cause Detection in Distributed Systemssurendiran123No ratings yet

- Assignment 1Document3 pagesAssignment 1dheeraj.d JainNo ratings yet

- Application Diagnostics With Unity: System User GuideDocument34 pagesApplication Diagnostics With Unity: System User Guideia2e techNo ratings yet

- ECT Chapter 1Document3 pagesECT Chapter 1Hnd FinalNo ratings yet

- DLD Lab ManualDocument27 pagesDLD Lab ManualHome Cuisine With RaheelaNo ratings yet

- Api I C2Document31 pagesApi I C2mihai37No ratings yet

- Final Project Report: Sequential Circuit Simulator With FaultsDocument10 pagesFinal Project Report: Sequential Circuit Simulator With FaultszeSky ArmourNo ratings yet

- Experiment No 04 Ladder Diagram Development For Different Types of Logic GatesDocument7 pagesExperiment No 04 Ladder Diagram Development For Different Types of Logic GatesRavindra0% (1)

- Complexity Fuzzy LogicDocument10 pagesComplexity Fuzzy Logicp31202202481No ratings yet

- Plate 21Document8 pagesPlate 21Charles RitterNo ratings yet

- Design For Testability NotesDocument41 pagesDesign For Testability NotesNaga Nithesh100% (3)

- Digital Design of A Digital Combination LockDocument6 pagesDigital Design of A Digital Combination LockIJERAS-International Journal of Engineering Research and Applied Science (ISSN: 2349-4522)No ratings yet

- PLC Operation - 8.1Document9 pagesPLC Operation - 8.1GvidonNo ratings yet

- Logic Locking A To ZDocument18 pagesLogic Locking A To ZShantonu DebnathNo ratings yet

- Capstone Project On Digital LocksDocument27 pagesCapstone Project On Digital LocksBeing RajatNo ratings yet

- Digital Logic Design Practice ManualDocument67 pagesDigital Logic Design Practice ManualBhargav VarmaNo ratings yet

- Mikroelektronika Books Introduction To PLC ControllersDocument157 pagesMikroelektronika Books Introduction To PLC ControllersemylangamNo ratings yet

- 23mac0002 VL2023240502132 Ast01Document12 pages23mac0002 VL2023240502132 Ast01payalspatil22No ratings yet

- PLC ProgrammingDocument116 pagesPLC Programmingbryan_robinsonuscNo ratings yet

- PDF Lab 2 DLDDocument13 pagesPDF Lab 2 DLDSana KhitranNo ratings yet

- Xor XnorDocument16 pagesXor Xnorapi-254068557No ratings yet

- SYSTEM ARCHETECTURE - OdtDocument8 pagesSYSTEM ARCHETECTURE - Odtlamha KhanNo ratings yet

- A Self Checking Reed Solomon Encoder Design and AnalysisDocument9 pagesA Self Checking Reed Solomon Encoder Design and AnalysisRAJKUMAR SAMIKKANNUNo ratings yet

- 05-Introduction To PLCDocument63 pages05-Introduction To PLCMohamed Gawad ARayaNo ratings yet

- PLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsFrom EverandPLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsRating: 5 out of 5 stars5/5 (1)

- TBD 616 PDFDocument6 pagesTBD 616 PDFIlham Bayu TiasmoroNo ratings yet

- 1 Electronic ComponentsDocument66 pages1 Electronic ComponentsIlham Bayu TiasmoroNo ratings yet

- Control Valves PDFDocument6 pagesControl Valves PDFIlham Bayu TiasmoroNo ratings yet

- Logam Print (Repaired)Document47 pagesLogam Print (Repaired)Ilham Bayu TiasmoroNo ratings yet

- Odel SerialDocument15 pagesOdel SerialSanjeev MarjaraNo ratings yet

- A Presentation On: "Multi-Terminal High Voltage Direct Current Transmission"Document22 pagesA Presentation On: "Multi-Terminal High Voltage Direct Current Transmission"Manish Kumar MeenaNo ratings yet

- Ch2 Macroscopic Fields V8Document19 pagesCh2 Macroscopic Fields V8christian26brownNo ratings yet

- 4-Storey Lift and Traverse Mechanical Garage Operation ManualDocument7 pages4-Storey Lift and Traverse Mechanical Garage Operation Manualzanuar mutyaNo ratings yet

- HI-8444, HI-8445, HI-8448: Quad / Octal ARINC 429 Line ReceiversDocument10 pagesHI-8444, HI-8445, HI-8448: Quad / Octal ARINC 429 Line ReceiversVarshaNo ratings yet

- Annexure - A12 (Electrical & Electronics Engg - )Document6 pagesAnnexure - A12 (Electrical & Electronics Engg - )Pradeep SinglaNo ratings yet

- Types of Antenna (Sir)Document9 pagesTypes of Antenna (Sir)Muhammad AbdullahNo ratings yet

- Implementation of A High Performance Stand-Alone Motion ControllerDocument5 pagesImplementation of A High Performance Stand-Alone Motion ControllerBook4AllNo ratings yet

- Project Report On Robotic ArmDocument17 pagesProject Report On Robotic ArmGina SreeNo ratings yet

- 41 Operation of Generators EDocument2 pages41 Operation of Generators EanNo ratings yet

- Getting Started With AT91SAM7S MicrocontrollersDocument23 pagesGetting Started With AT91SAM7S Microcontrollersapi-3697475No ratings yet

- Pro 404Document1 pagePro 404Luis MontañezNo ratings yet

- 2multifan DipoleDocument4 pages2multifan DipolelokiknoppenNo ratings yet

- BHSS 50W Step ServoDocument20 pagesBHSS 50W Step ServoAnonymous m36V0bvzNo ratings yet

- ELE754 Course OutlineDocument4 pagesELE754 Course Outlineknighthood4allNo ratings yet

- 1 General Information: Nettime Timestamp of The Position and Trigger TimeDocument51 pages1 General Information: Nettime Timestamp of The Position and Trigger TimeСтив АааNo ratings yet

- AD-DC MotorDocument7 pagesAD-DC MotorJay Mark BalaneNo ratings yet

- 2f3e0 LA-8671P 1ADocument50 pages2f3e0 LA-8671P 1ASelmar CavalcantiNo ratings yet

- EC 6404 Linear Integrated CircuitsDocument202 pagesEC 6404 Linear Integrated CircuitsVasanthNo ratings yet

- XPROG ManualDocument19 pagesXPROG ManualLorenna Ruth100% (1)

- Mandatory Disclosure 2010Document40 pagesMandatory Disclosure 2010Casey JonesNo ratings yet

- Tadiran PNR-500: Personal Network Radio - Full-Duplex Voice and Data ConferencingDocument4 pagesTadiran PNR-500: Personal Network Radio - Full-Duplex Voice and Data ConferencingPeter Bobocky100% (1)

- Design of 50 MW SolarDocument14 pagesDesign of 50 MW Solarbhargav100% (1)

- Design Price M&E. MDCDocument2 pagesDesign Price M&E. MDCmcgNo ratings yet

- TaperecorderDocument6 pagesTaperecorderjassiscNo ratings yet

- AnExperiment On CmosDocument10 pagesAnExperiment On CmosVinny VenizNo ratings yet

- Matlab Questions Tangirala Naga Venkata Sri HarshaDocument1 pageMatlab Questions Tangirala Naga Venkata Sri HarshaSri Harsha TNo ratings yet

- Almag WP-20221304Document4 pagesAlmag WP-20221304RUBEN ESTEBAN RODRIGUEZ BARRERANo ratings yet