Professional Documents

Culture Documents

DD Handout

DD Handout

Uploaded by

AsdgjkOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DD Handout

DD Handout

Uploaded by

AsdgjkCopyright:

Available Formats

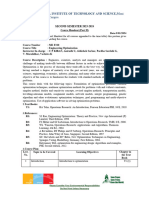

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

Instruction Division

Date: 02/08/2017

FIRST SEMESTER 2017-2018

In addition to Part-I (General Handout for all courses appended to the timetable) this portion

gives further specific details regarding the course.

Course Handout

Course No : CS F 215/ EEE F215 / INSTR F215

Course Title : Digital Design

Instructor-in-charge : Dr. Pawan K. Ajmera (pawan.ajmera@pilani.bits-pilani.ac.in)

Instructors for Lecture : Dr. Nitin Chaturvedi, Dr. Pawan K. Ajmera.

Tutorial Instructors : Prof. S. Mohan, Pawan K. Ajmera,

Dr. Asutosh Kar, Mr. Harshvardhan

Practical Instructors : Tulsi Ram Sharma, Abheek Gupta, Ravinder Kumar, Dhananjay,

Prateek Bindra, Punit Khatri

Scope and Objective: The objective of the course is to impart knowledge of the basic

tools for the design of digital circuits and to provide methods and procedures suitable

for a variety of digital design applications.

Text Books :

T1: M. Moris Mano and Michael D. Ciletti “Digital Design”, PHI, 5th Edition, 2013.

T2: G. Raghurama, S. Gurunarayanan, S. Mohan, Karthik, “Laboratory Manual”, EDD

notes 2007.

Reference Books:

R1: Ronald J. Tocci and Neal S. Widmer, “Digital Systems-Principles and Application”,

Pearson, 10th Edition, 2007.

R2: Thomas l. Floyd, “Digital Fundamentals,” Pearson, 9th Edition, 20

R2: Donald D. Givonne, “Digital Principles and Design” TMH, 2003

Please Do Not Print Unless Necessary

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

Instruction Division

Course Plan

Lecture

Main Topic Contents Reference

No.

01 Introduction Introduction to Digital systems and characteristics

Number systems Digital, Binary, Octal and Hexadecimal, Number-Base T1:1.1-1.9

02

and codes Conversions, Complements, Signed Binary Numbers.

Logic Gates and Digital Logic Gates, Truth Table, Boolean Algebra, Theorems T1:2.1-2.8

03

Boolean Algebra and Properties, Boolean Functions, Canonical and Std. forms.

Minimization Gate-Level Minimization, The Karnaugh Map Method, T1:3.1-3.8

04-05

Techniques Quine-McCluskey Method

Simulation and Hardware Description Language (Verilog HDL) T1:3.11

07

synthesis

Introduction, Analysis and Design Procedure, Binary Adder- T1:4.1-4.7

Combinational

08-11 Subtractor, Decimal Adder, Binary Multiplier, HDL Models of T1:4.12

Logic Circuits

Combinational Circuits.

Sequential Logic Introduction, Storage Elements: Latches and Flip-Flops. T1:5.1-5.4

12-13

Circuits

Magnitude Comparator, Decoders, Encoders, Multiplexers, T1:4.8-

14-18 MSI Logic Circuits

HDL Models of Combinational Circuits. 4.12

Analysis of Clocked Sequential Circuits, State Reduction and T1:5.5-5.8

Synchronous

19-23 Assignment, Design Procedure, HDL Models of Sequential

Sequential circuits

Circuits

Registers and Registers, Shift Registers, Ripple Counters, Synchronous T1:6.1-6.5

24-28

Counters Counters, HDL for Registers and Counters

Introduction, Random-Access Memory, Memory Decoding, T1:7.1-7.8

Memory and

29-32 Error Detection and Correction, Read-Only Memory,

PLD’s

Programmable Logic Array, Programmable Array Logic

Design of Digital Register Transfer Level (RTL) Notation, Algorithmic State T1:8.1-8.8

33-37

Systems Machines (ASMs), HDL description.

Digital Integrated TTL, MOS Logic families and characteristics. T1:10.1-

38-40

Circuits 10.9

Evaluation Scheme:

EC No. Evaluation Component Duration Marks Date and Time Nature of Component

1 Weekly Quiz 10 Min 45 Continuous Close Book

Laboratory

2 180 Min 12 + 33 Continuous Close Book

(Attendance + Lab exam)

10/10 2:00 -

3 Mid-Semester Exam 90 Min 90 Close Book

3:30 PM

_

Please Do Not Print Unless Necessary

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

Instruction Division

4 Comprehensive Exam 180 Min 120 5/12 FN Open/Close Book

Total 300

Practicals

S.No. Name of experiment

1. BOOLEAN FUNCTIONS IMPLEMENTATION

2. DESIGN OF ARITHMATIC CIRCUITS

3. IMPLEMENTATION OF BCD ADDER

4. DECODERS, MULTIPLEXERS AND DEMULTIPLEXERS

5. LATCHES & FLIP-FLOPS

6. OPERATION OF A 4-BIT COUNTER

7. COMPARATORS & ARITHMETIC LOGIC UNIT

8. COUNTER DESIGN

9. SHIFT REGISTERS

10. DESIGN OF SEQUENCE DETECTOR

11. MEMORIES AND FPGAS

Assignments: There will be simulation based assignments, which will be as take home assignments.

Chamber Consultation Hours: To be announced in the class.

Notices: Notices regarding the course will be displayed only on the EEE (FD II) notice

board/NALANDA.

Makeup Policy: Makeup will be granted to extremely genuine cases only, provided the IC has been

informed.

Instructor - in - charge

CS F215/ EEE F215 / INSTR F215

Please Do Not Print Unless Necessary

You might also like

- 400G Module User Guide 22142947 R012Document214 pages400G Module User Guide 22142947 R012Orlando MedinaNo ratings yet

- Iso 8373Document27 pagesIso 8373Rob O'DeaNo ratings yet

- Electrical and Computer EngineeringDocument45 pagesElectrical and Computer EngineeringAklilu Hailu50% (2)

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument4 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionTrideeb BhattacharyaNo ratings yet

- DDDocument3 pagesDDJAY JANAK MANEKNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- Bits PilaniDocument3 pagesBits PilaniasdmddamcNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- Ece F215 Digital Design - HandoutDocument3 pagesEce F215 Digital Design - HandoutRishiNo ratings yet

- Page 1 of 2: W.E.F. AY 2018-19Document2 pagesPage 1 of 2: W.E.F. AY 2018-19Jenny BhadouriyaNo ratings yet

- 2.digital Electronics TheoryDocument15 pages2.digital Electronics TheoryYash KuncolienkerNo ratings yet

- Course Handout: Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument3 pagesCourse Handout: Birla Institute of Technology and Science, Pilani Pilani Campus Instruction Divisionsaurjyesh nayakNo ratings yet

- Handout 2016 PDFDocument4 pagesHandout 2016 PDFShubham RohilaNo ratings yet

- Uttarakhand Technical University Dehradun: Study and Evaluation Scheme (B.Tech. Iii Year)Document7 pagesUttarakhand Technical University Dehradun: Study and Evaluation Scheme (B.Tech. Iii Year)Ankit SharmaNo ratings yet

- 15ec751 DSP AlogorithmsDocument40 pages15ec751 DSP AlogorithmsSudheer BabuNo ratings yet

- Department of Electronics and Communication Engineering: Mr.K.Aanandhasaravanan AanandhasaravananDocument4 pagesDepartment of Electronics and Communication Engineering: Mr.K.Aanandhasaravanan AanandhasaravanansarvanmeNo ratings yet

- Digital Electronics and Computer OrganizationDocument3 pagesDigital Electronics and Computer OrganizationSai Prajwal SavanamNo ratings yet

- Handout DSP Ece Eee f434Document2 pagesHandout DSP Ece Eee f434Nitesh JainNo ratings yet

- Diploma IT 3rd Sem SylDocument20 pagesDiploma IT 3rd Sem Sylshriram1082883No ratings yet

- IT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesDocument2 pagesIT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesVyshnavi ThottempudiNo ratings yet

- Digital Design: Cs/Eee/Ece /instr F215Document34 pagesDigital Design: Cs/Eee/Ece /instr F215SIDDHANT RAVINDRA KULKARNINo ratings yet

- M.Tech ECE SyllabusDocument4 pagesM.Tech ECE Syllabuspaku deyNo ratings yet

- Academic Course DescriptionDocument8 pagesAcademic Course DescriptionRajalearn2 Ramlearn2No ratings yet

- Number System and CodesDocument300 pagesNumber System and Codes011S6Amit PandeyNo ratings yet

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- SY Btech E&TC Syllabus - 2!03!2021Document40 pagesSY Btech E&TC Syllabus - 2!03!2021legad40026No ratings yet

- Course Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Document10 pagesCourse Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Huzaifa YasirNo ratings yet

- Fourth Semester: S. No Course Code Course Title Contact Hrs. / Week Credit L T PDocument10 pagesFourth Semester: S. No Course Code Course Title Contact Hrs. / Week Credit L T Pjiman84235No ratings yet

- Updated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Document9 pagesUpdated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Laiqa AliNo ratings yet

- Aei-5th & 6TH Sem23062008Document44 pagesAei-5th & 6TH Sem23062008War MachineNo ratings yet

- Attachment Circular 2023081115025923 Ic 001Document9 pagesAttachment Circular 2023081115025923 Ic 001shivam.cs667No ratings yet

- Birla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019Document3 pagesBirla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019PriNo ratings yet

- Gujarat Technological University: Semester - III Subject Name: Digital ElectronicsDocument3 pagesGujarat Technological University: Semester - III Subject Name: Digital ElectronicsBhargavsinh ParmarNo ratings yet

- CS ECE EEE INSTR F241 - Microprocessor Programming Interfacing - Handout 2018 (2 Files Merged)Document5 pagesCS ECE EEE INSTR F241 - Microprocessor Programming Interfacing - Handout 2018 (2 Files Merged)Parth SoodanNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- 05 Unit V DTEDocument217 pages05 Unit V DTEKrunal WaniNo ratings yet

- 311001-Fundamentals of Ict SyllabusDocument10 pages311001-Fundamentals of Ict SyllabusSuriRawatNo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument22 pagesChhattisgarh Swami Vivekanand Technical University, Bhilaibheshram janghelNo ratings yet

- Dtev 180916171027Document217 pagesDtev 180916171027vaishnavi biradarNo ratings yet

- Birla Institute of Technology & Science, Pilani Instruction Division FIRST SEMESTER 2017 - 2018 Course Handout (Part Ii)Document2 pagesBirla Institute of Technology & Science, Pilani Instruction Division FIRST SEMESTER 2017 - 2018 Course Handout (Part Ii)prabhatNo ratings yet

- ECE-VII-DSP ALGORITHMS & ARCHITECTURE Part ADocument111 pagesECE-VII-DSP ALGORITHMS & ARCHITECTURE Part AmanjumathgowdaNo ratings yet

- Deca ChoDocument9 pagesDeca ChoTARANGITNo ratings yet

- ECE 6th Sem SyllabusDocument7 pagesECE 6th Sem SyllabusHarsh KumarNo ratings yet

- Digital Communication SystemsDocument4 pagesDigital Communication SystemsMarina KhanNo ratings yet

- EE407 Digital Signal ProcessingDocument2 pagesEE407 Digital Signal ProcessingbibuthomasNo ratings yet

- Ece VII DSP Algorithms Architecture 10ec751 Notes PDFDocument181 pagesEce VII DSP Algorithms Architecture 10ec751 Notes PDFManojNo ratings yet

- ME F320 Engineering OptimizationDocument5 pagesME F320 Engineering OptimizationARYAAN PARIDANo ratings yet

- RTS SyllabusDocument3 pagesRTS SyllabusthejasNo ratings yet

- Syallbus B. Tech CSE First YearDocument12 pagesSyallbus B. Tech CSE First YearRishav RajNo ratings yet

- Digital ElectronicsDocument2 pagesDigital ElectronicsretheeshvkmNo ratings yet

- CS C363Document3 pagesCS C363Aravind KondamudiNo ratings yet

- CP16036Document6 pagesCP16036Sankar TerliNo ratings yet

- B Tech CIVIL Engineering CurriculumDocument36 pagesB Tech CIVIL Engineering CurriculumG Ravi Kiran HSCNo ratings yet

- Digital Design EEE F215 HandoutDocument3 pagesDigital Design EEE F215 HandoutHarshilGargNo ratings yet

- Bits g553 Real Time SystemsDocument2 pagesBits g553 Real Time SystemsUriti Venkata Naga KishoreNo ratings yet

- Don Bosco Institute of Technology: Course Syllabi With CO'sDocument2 pagesDon Bosco Institute of Technology: Course Syllabi With CO'sprashantgeminiNo ratings yet

- CP Je Tele PH1Document2 pagesCP Je Tele PH1Sagnik ChakrabortyNo ratings yet

- UT Dallas Syllabus For Ee4361.501.08f Taught by Issa Panahi (Imp015000)Document2 pagesUT Dallas Syllabus For Ee4361.501.08f Taught by Issa Panahi (Imp015000)UT Dallas Provost's Technology GroupNo ratings yet

- DPSD CS8351 U1 PDFDocument182 pagesDPSD CS8351 U1 PDFPragna SidhireddyNo ratings yet

- Scope and Objective of The CourseDocument3 pagesScope and Objective of The CourseNitu SharmaNo ratings yet

- Digital Signal Processing: A Practical Guide for Engineers and ScientistsFrom EverandDigital Signal Processing: A Practical Guide for Engineers and ScientistsRating: 4.5 out of 5 stars4.5/5 (7)

- SAP How To Step by Step Guide With Screen ShotDocument16 pagesSAP How To Step by Step Guide With Screen ShotPriyesh ET100% (1)

- Spaj 140CDocument68 pagesSpaj 140CTiago Marques PereiraNo ratings yet

- Emc Networker Module For Microsoft SQL Server: Installation GuideDocument52 pagesEmc Networker Module For Microsoft SQL Server: Installation Guidehello helloNo ratings yet

- Sonardyne Scout USBLDocument3 pagesSonardyne Scout USBLZair VaikamNo ratings yet

- Oracle 10G Installation: Step I: Check For Following Required Package Versions (Or Later)Document46 pagesOracle 10G Installation: Step I: Check For Following Required Package Versions (Or Later)Faisal SaitNo ratings yet

- Eucalpytus, AzureDocument13 pagesEucalpytus, AzureRebaNo ratings yet

- Terminal Server LicenseDocument4 pagesTerminal Server Licenseadriana lNo ratings yet

- (A) 1024 Gigabyte (B) 1024 Kilobyte (C) 1024 Megabyte (D) 1024 ByteDocument5 pages(A) 1024 Gigabyte (B) 1024 Kilobyte (C) 1024 Megabyte (D) 1024 ByteSubhraprakash MondalNo ratings yet

- Python Cheat Sheet April 2021Document26 pagesPython Cheat Sheet April 2021Rajesh Shinde100% (1)

- DS Tic Tac Toe DocumentationDocument20 pagesDS Tic Tac Toe DocumentationB. S BabuNo ratings yet

- Aws CliDocument240 pagesAws CliHerminia MarcanoNo ratings yet

- Operation Manual: Line Differential Protection and Control RED615Document116 pagesOperation Manual: Line Differential Protection and Control RED615Mirza AtayevNo ratings yet

- Instagram and WhatsApp in Health and Healthcare: An OverviewDocument15 pagesInstagram and WhatsApp in Health and Healthcare: An OverviewRaditya NovasaniNo ratings yet

- India IPMS DemandDocument103 pagesIndia IPMS DemandYanyan2009No ratings yet

- z10 UNIX ReferenceDocument1,020 pagesz10 UNIX Referencesdxiu2000No ratings yet

- © The Institute of Chartered Accountants of IndiaDocument6 pages© The Institute of Chartered Accountants of IndiaMenuka SiwaNo ratings yet

- SAP ERP 6.0 EHP6 IDES Install On Oracle and Windows 2008 R2Document16 pagesSAP ERP 6.0 EHP6 IDES Install On Oracle and Windows 2008 R2Sidharth KumarNo ratings yet

- International Organization For Standardization Payment CardsDocument10 pagesInternational Organization For Standardization Payment CardsSankalp MathurNo ratings yet

- Evolutionary Algorithms N NLPDocument28 pagesEvolutionary Algorithms N NLPKomal Singh GillNo ratings yet

- MV 3000 Getting Started ManualDocument160 pagesMV 3000 Getting Started ManualterranohrNo ratings yet

- SQL 123Document2 pagesSQL 123sushant2391980No ratings yet

- As 2162.1-1996 Verification and Use of Volumetric Apparatus General - Volumetric GlasswareDocument7 pagesAs 2162.1-1996 Verification and Use of Volumetric Apparatus General - Volumetric GlasswareSAI Global - APACNo ratings yet

- Web Servers: Implementation and Performance: Erich NahumDocument143 pagesWeb Servers: Implementation and Performance: Erich NahumimshwezNo ratings yet

- (Untitled) : This Spreadsheet Was Created by Either POM, QM or POM-QM For Windows, V4Document7 pages(Untitled) : This Spreadsheet Was Created by Either POM, QM or POM-QM For Windows, V4Miguel ArambulaNo ratings yet

- World Class ManufacturingDocument78 pagesWorld Class ManufacturingRAJASREE SNo ratings yet

- Database 1Document59 pagesDatabase 1Dr-Raghad Al-FahamNo ratings yet