Professional Documents

Culture Documents

Indian Institute of Technology Kanpur Department of Electrical Engineering Practice Problems - 3

Indian Institute of Technology Kanpur Department of Electrical Engineering Practice Problems - 3

Uploaded by

Nitish DeshpandeCopyright:

Available Formats

You might also like

- 2006 VW Rabbit Wiring DiagramsDocument100 pages2006 VW Rabbit Wiring DiagramsmikeNo ratings yet

- Daedong Service ManualDocument402 pagesDaedong Service ManualFrançois Charrière100% (2)

- Access 125 OmDocument84 pagesAccess 125 OmRushabh DoshiNo ratings yet

- ECE 534 Project 1 F19Document6 pagesECE 534 Project 1 F19JAY CHHEDANo ratings yet

- ESQUEMA ELECTRICO c9 PDFDocument2 pagesESQUEMA ELECTRICO c9 PDFOswaldo AndradeNo ratings yet

- 25 NehaDocument6 pages25 NehaKingNo ratings yet

- Renewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationDocument3 pagesRenewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationiirNo ratings yet

- Tests - New ProcedureDocument17 pagesTests - New ProcedurebhargavNo ratings yet

- Valliammai Engineering College: (A Member of SRM Group of Institutions)Document7 pagesValliammai Engineering College: (A Member of SRM Group of Institutions)Jayasuriya PalaniNo ratings yet

- ??? ??? ???? ??????Document19 pages??? ??? ???? ??????Anupam ChittoraNo ratings yet

- Icp IccDocument6 pagesIcp IccGiovani ScarpatiNo ratings yet

- Draft ABT Spec With TOD & Billing DataDocument51 pagesDraft ABT Spec With TOD & Billing DataSristi MitraNo ratings yet

- Final MI SET A Fall 20-21Document2 pagesFinal MI SET A Fall 20-21Elisabeth Burnett MartinNo ratings yet

- 220 - EC8453, EC6404 Linear Integrated Circuits - Question BankDocument7 pages220 - EC8453, EC6404 Linear Integrated Circuits - Question BankStephan HawkingNo ratings yet

- Design and Construction of 0 500V 3KVA Variac With Digital DisplayDocument9 pagesDesign and Construction of 0 500V 3KVA Variac With Digital DisplayEditor IJTSRDNo ratings yet

- 3 Hours / 100 Marks: Seat NoDocument6 pages3 Hours / 100 Marks: Seat Nosahil satputeNo ratings yet

- EE198B - Wireless Battery Charger PDFDocument21 pagesEE198B - Wireless Battery Charger PDFV'nod Rathode BNo ratings yet

- Convention Centre-E-8.11.2019 - R0Document11 pagesConvention Centre-E-8.11.2019 - R0ManojNo ratings yet

- 22423-2019-Winter-Model-Answer-Paper (Msbte Study Resources)Document18 pages22423-2019-Winter-Model-Answer-Paper (Msbte Study Resources)OM BURADENo ratings yet

- The Reliability of Neutral Point Clamped vs. Cascaded H-Bridge InvertersDocument4 pagesThe Reliability of Neutral Point Clamped vs. Cascaded H-Bridge InvertersDevas ShuklaNo ratings yet

- Dec 2009Document8 pagesDec 2009Viswa ChaitanyaNo ratings yet

- Electronics 06 00038 PDFDocument20 pagesElectronics 06 00038 PDFsathishNo ratings yet

- Computational Tool For Sizing and Assessment of GridConnected Photovoltaic SystemsDocument10 pagesComputational Tool For Sizing and Assessment of GridConnected Photovoltaic Systemsel_ruso__83No ratings yet

- Electronics 10 01185 v2 PDFDocument9 pagesElectronics 10 01185 v2 PDFfeenNo ratings yet

- WWW Manaresults Co inDocument1 pageWWW Manaresults Co inmocharla sandeepNo ratings yet

- 1 PDFDocument6 pages1 PDFfadillahNo ratings yet

- Adsd ManualDocument69 pagesAdsd Manualsce21cs133No ratings yet

- EPM445 - Lecture 5 - Design and Performance AnalysisDocument36 pagesEPM445 - Lecture 5 - Design and Performance AnalysisSalma MahmoudNo ratings yet

- EEE312 EEE282 Lab4 Spring2015 PDFDocument5 pagesEEE312 EEE282 Lab4 Spring2015 PDFvognarNo ratings yet

- LaboratoryManualForOperationalAmplifiersAndLinearICs 3E PDFDocument130 pagesLaboratoryManualForOperationalAmplifiersAndLinearICs 3E PDFRajalingam BossNo ratings yet

- High SR 2 Stage Opamp TechPaperDocument3 pagesHigh SR 2 Stage Opamp TechPaperVarad KeniNo ratings yet

- EC6404-Linear Integrated Circuits Question BankDocument7 pagesEC6404-Linear Integrated Circuits Question BankkundaviNo ratings yet

- 1252-Transducer Engineering Question PaperDocument5 pages1252-Transducer Engineering Question Papermoney_kandan2004100% (1)

- Circuits - Lab - Handbook RA ZJSUDocument8 pagesCircuits - Lab - Handbook RA ZJSUlanxinNo ratings yet

- Linear and Digital Ic Applications RRDocument8 pagesLinear and Digital Ic Applications RRNizam Institute of Engineering and Technology LibraryNo ratings yet

- Electrical Machines IIDocument8 pagesElectrical Machines IIPremkumar KodamanchiliNo ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- InverterDocument31 pagesInverterĐẹp PhanNo ratings yet

- Lect03 Qual MetricsDocument14 pagesLect03 Qual MetricsKumar GaneshNo ratings yet

- Design and Simulation of Modified Ultra Low Power CMOS Comparator For Sigma Delta ModulatorDocument3 pagesDesign and Simulation of Modified Ultra Low Power CMOS Comparator For Sigma Delta ModulatorASHFAQ AHMEDNo ratings yet

- Linear and Digital Ic ApplicatonsDocument4 pagesLinear and Digital Ic ApplicatonsViswa ChaitanyaNo ratings yet

- 54102-mt - Analog & Digital Ic DesignDocument2 pages54102-mt - Analog & Digital Ic DesignSRINIVASA RAO GANTANo ratings yet

- 33ssc04 ZarabadiDocument7 pages33ssc04 ZarabadiArindam ChakrabortyNo ratings yet

- Aim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Document3 pagesAim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Jeyakumar VenugopalNo ratings yet

- Experiment 5 - Inverter CharacteristicsDocument7 pagesExperiment 5 - Inverter CharacteristicsGowtham SpNo ratings yet

- Course: EC2P001 Introduction To Electronics Lab: Indian Institute of Technology Bhubaneswar School of Electrical ScienceDocument5 pagesCourse: EC2P001 Introduction To Electronics Lab: Indian Institute of Technology Bhubaneswar School of Electrical ScienceAnik ChaudhuriNo ratings yet

- You're Reading A Preview. Unlock Full Access With A Free TrialDocument91 pagesYou're Reading A Preview. Unlock Full Access With A Free TrialbashasvuceNo ratings yet

- Case Study 2 - Marking GuideDocument8 pagesCase Study 2 - Marking GuideMBIEDA NGOMEGNI FRANK GAETANNo ratings yet

- Ee141 HW2 3 PDFDocument5 pagesEe141 HW2 3 PDFVidhya DsNo ratings yet

- 3 Hours / 100 Marks: Seat NoDocument6 pages3 Hours / 100 Marks: Seat Nosahil satputeNo ratings yet

- Question Paper Electrical Engineering For Group-B SelectionDocument4 pagesQuestion Paper Electrical Engineering For Group-B SelectionHimanku BoraNo ratings yet

- Efficient Current Bleeding Mixer For Wimax Applications: SciencedirectDocument7 pagesEfficient Current Bleeding Mixer For Wimax Applications: SciencedirectMihaela ElenaNo ratings yet

- Design and Simulation of A 100W Pure SinDocument4 pagesDesign and Simulation of A 100W Pure SinZeeshan Khan100% (1)

- IIT BH DNC Lab EE Manual Expt 4Document6 pagesIIT BH DNC Lab EE Manual Expt 4Priyesh PandeyNo ratings yet

- ELE341 Project OPAmpDocument4 pagesELE341 Project OPAmpbabycryyNo ratings yet

- Fy Comp Sem II Bec 22225 QP & Model AnswersDocument86 pagesFy Comp Sem II Bec 22225 QP & Model AnswersUmesh PatilNo ratings yet

- LIC - Question BankDocument8 pagesLIC - Question Banksriramraghu4_6423936No ratings yet

- Exercise 3 - VlsiDocument6 pagesExercise 3 - Vlsiujjwal mishraNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Design and Implementation of Portable Impedance AnalyzersFrom EverandDesign and Implementation of Portable Impedance AnalyzersNo ratings yet

- 2-Wire, Programmable RH + Temperature Transmitter: 2 X Isolated 4 20 Ma Outputs, Dual Led DisplayDocument2 pages2-Wire, Programmable RH + Temperature Transmitter: 2 X Isolated 4 20 Ma Outputs, Dual Led DisplaypiyushpandeyNo ratings yet

- Writeup On Automatic Turbine Runup SystemDocument18 pagesWriteup On Automatic Turbine Runup Systemlp mishraNo ratings yet

- Fire Water Jockey PumpDocument2 pagesFire Water Jockey PumpSalim BakhshNo ratings yet

- Heat DetectorDocument2 pagesHeat DetectorFederico GonzálezNo ratings yet

- Sony Dcrip5eDocument81 pagesSony Dcrip5ePaco RodriguezNo ratings yet

- Bulldozer Komatsu D65EP-12 - 0Document6 pagesBulldozer Komatsu D65EP-12 - 0Esti NugrohadiNo ratings yet

- S. R. 2007 - I (Internal)Document168 pagesS. R. 2007 - I (Internal)Vilas_123No ratings yet

- Arduino TMP36 Precision Temperature Sensor-GuideDocument1 pageArduino TMP36 Precision Temperature Sensor-GuideMC. Rene Solis R.100% (1)

- CX70 - Diagramas ElectricosDocument362 pagesCX70 - Diagramas ElectricosSDanielTorresPachasNo ratings yet

- TAMD41: Volvo Penta Inboard DieselDocument2 pagesTAMD41: Volvo Penta Inboard DieselDaliborNo ratings yet

- Job Vedc 2020 Cad DiklatDocument1 pageJob Vedc 2020 Cad DiklatPemesinan SMK Migas CepuNo ratings yet

- AN108-Designing A Half Bridge Converter Using A CoreMaster E2000Q CoreDocument7 pagesAN108-Designing A Half Bridge Converter Using A CoreMaster E2000Q Coreatkxyz777No ratings yet

- Parts Book GD511A-1 - LEPBG51103Document231 pagesParts Book GD511A-1 - LEPBG51103Denias MaleoNo ratings yet

- Vpvo Vdo Catalogue 2019 06 enDocument66 pagesVpvo Vdo Catalogue 2019 06 enstarykNo ratings yet

- PROFIBUS-DP BoardDocument98 pagesPROFIBUS-DP BoardLalo De GanteNo ratings yet

- Fairbanks Fb100Document44 pagesFairbanks Fb100edefrtgNo ratings yet

- SM1800 GBDocument4 pagesSM1800 GBAristides AnselmoNo ratings yet

- Drum Lifting MethodDocument4 pagesDrum Lifting MethodRajeev MaheshwariNo ratings yet

- OIL PUMP (Bus) MERCEDESDocument3 pagesOIL PUMP (Bus) MERCEDESKarthickNo ratings yet

- Inventory Custodian Slip - Appendix-59Document4 pagesInventory Custodian Slip - Appendix-59Maria Fatima ArnaizNo ratings yet

- TE InclinometerDocument4 pagesTE InclinometerPankaj RamoleNo ratings yet

- Automatic Transfer System Explained in Details Part 1Document4 pagesAutomatic Transfer System Explained in Details Part 1lam266No ratings yet

- Elevation Section: Dia 10. MM Galvanized Steel Screw With Acmon BoltDocument1 pageElevation Section: Dia 10. MM Galvanized Steel Screw With Acmon BoltROSE STONENo ratings yet

- Datavision Tft-Products Shortform (0,3 MB)Document2 pagesDatavision Tft-Products Shortform (0,3 MB)Adam BerdyszakNo ratings yet

- 2008 CX 7 Maintenance ScheduleDocument6 pages2008 CX 7 Maintenance Scheduleuriel avila garciaNo ratings yet

Indian Institute of Technology Kanpur Department of Electrical Engineering Practice Problems - 3

Indian Institute of Technology Kanpur Department of Electrical Engineering Practice Problems - 3

Uploaded by

Nitish DeshpandeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Indian Institute of Technology Kanpur Department of Electrical Engineering Practice Problems - 3

Indian Institute of Technology Kanpur Department of Electrical Engineering Practice Problems - 3

Uploaded by

Nitish DeshpandeCopyright:

Available Formats

EE370A - Monsoon 2019

Indian Institute of Technology Kanpur

Department of Electrical Engineering

Practice Problems – 3

Due: Friday 23rd August, 2019

For the problems discussed below, assume that for nMOSFETs Kn' = 200 A V-2 and VTn = 1 V, and

for pMOSFETs |Kp'| = 100 A V-2 and |VTp|= 1 V. The supply voltage used is VDD = 5 V. The

minimum size of W and L are Wmin = Lmin = 0.5 m. The capacitive load seen by the inverters

may be taken to be 10 pF. For the circuit in which these inverters are to be placed the period of

switching of the clock used is ten times the inverter tp and the activity factor is 0.1 (i.e., the

probability of energy consuming transition of the input is 0.1). Use reasonable approximation

wherever necessary in your analysis and calculations.

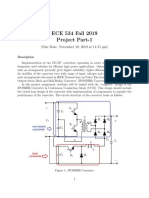

1. For the inverter shown in Fig. 1:

(i) Calculate the VOH, VOL, VIH, VIL and VM. Confirm whether you assumption

for the region of operation of transistor is valid after you obtain the final

result. What design changes will you make to push the parameters you have

obtained to their ideal value.

(ii) Calculate tpHL and tpLH and tp for this inverter. What will be the design

changes you may want to obtain improved performance of the inverter?

(iii) Determine the static and dynamic power dissipation for these circuits.

What design changes would you suggest to minimize power consumption by

the inverter?

2. For the inverter shown in Fig. 2:

(i) What will be your choice for Vbais if you want to achieve maximum

VOH? Give your reasons for your choice.

(ii) Calculate the VOH, VOL, VIH, VIL and VM. Confirm whether you

assumption for the region of operation of transistor is valid after you

obtain the final result. What design changes will you make to push

the parameters you have obtained to their idea value.

(iii) Calculate tpHL and tpLH and tp for this inverter. What will be

design changes you will make to obtain improved performance of the

inverter?

(iv) Determine the static and dynamic power dissipation for these

circuits. What design changes will be you make to minimize power

consumption by the inverter?

EE370A - Monsoon 2019

3. For the inverter shown in Fig. 3:

(i) What will be your logical choice for Vbais? Give your reasons. What

will be the size of the p-MOSFET that will be reasonable?

(ii) Calculate the VOH, VOL, VIH, VIL and VM. Confirm whether you

assumption for the region of operation of transistor is valid after you

obtain the final result. What design changes will you make to push the

parameters you have obtained to their idea value.

(iii) Calculate tpHL and tpLH and tp for this inverter. What will be design

changes you will make to obtain improved performance of the inverter?

(iv) Determine the static and dynamic power dissipation for these

circuits. What design changes will be you make to minimize power

consumption by the inverter?

4. Consider the inverter shown in Fig. 4.

(i) What will be the values of W and L you will choose for your

transistors to make the PUN and PDN equally strong?

(ii) What are the VOH, VOL, VIH, VIL and VM for this inverter’s VTC?

[Notice the symmetry in the results.]

(iii) Calculate tpHL and tpLH and tp for this inverter.

(iv) Determine the static and dynamic power dissipation for these circuits.

5. Run SPICE simulation for the above inverter circuits. You may use any (open source) SPICE

simulator. Indicate the technology you are using corresponding to the SPICE parameters for the

transistors.

(a) Determine the voltage transfer characteristics as well as the key parameters in the VTC

quantitatively.

(b) Then determine tpHL and tpLH and tp for these invertors (i) no external capacitor attached; (ii) with

an external capacitor of 10 pF attached to the output.

(c) Determine the static and dynamic power dissipation for these inverters.

You might also like

- 2006 VW Rabbit Wiring DiagramsDocument100 pages2006 VW Rabbit Wiring DiagramsmikeNo ratings yet

- Daedong Service ManualDocument402 pagesDaedong Service ManualFrançois Charrière100% (2)

- Access 125 OmDocument84 pagesAccess 125 OmRushabh DoshiNo ratings yet

- ECE 534 Project 1 F19Document6 pagesECE 534 Project 1 F19JAY CHHEDANo ratings yet

- ESQUEMA ELECTRICO c9 PDFDocument2 pagesESQUEMA ELECTRICO c9 PDFOswaldo AndradeNo ratings yet

- 25 NehaDocument6 pages25 NehaKingNo ratings yet

- Renewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationDocument3 pagesRenewable Energy Based On Current Fed Switched Inverter For Smart Grid ApplicationiirNo ratings yet

- Tests - New ProcedureDocument17 pagesTests - New ProcedurebhargavNo ratings yet

- Valliammai Engineering College: (A Member of SRM Group of Institutions)Document7 pagesValliammai Engineering College: (A Member of SRM Group of Institutions)Jayasuriya PalaniNo ratings yet

- ??? ??? ???? ??????Document19 pages??? ??? ???? ??????Anupam ChittoraNo ratings yet

- Icp IccDocument6 pagesIcp IccGiovani ScarpatiNo ratings yet

- Draft ABT Spec With TOD & Billing DataDocument51 pagesDraft ABT Spec With TOD & Billing DataSristi MitraNo ratings yet

- Final MI SET A Fall 20-21Document2 pagesFinal MI SET A Fall 20-21Elisabeth Burnett MartinNo ratings yet

- 220 - EC8453, EC6404 Linear Integrated Circuits - Question BankDocument7 pages220 - EC8453, EC6404 Linear Integrated Circuits - Question BankStephan HawkingNo ratings yet

- Design and Construction of 0 500V 3KVA Variac With Digital DisplayDocument9 pagesDesign and Construction of 0 500V 3KVA Variac With Digital DisplayEditor IJTSRDNo ratings yet

- 3 Hours / 100 Marks: Seat NoDocument6 pages3 Hours / 100 Marks: Seat Nosahil satputeNo ratings yet

- EE198B - Wireless Battery Charger PDFDocument21 pagesEE198B - Wireless Battery Charger PDFV'nod Rathode BNo ratings yet

- Convention Centre-E-8.11.2019 - R0Document11 pagesConvention Centre-E-8.11.2019 - R0ManojNo ratings yet

- 22423-2019-Winter-Model-Answer-Paper (Msbte Study Resources)Document18 pages22423-2019-Winter-Model-Answer-Paper (Msbte Study Resources)OM BURADENo ratings yet

- The Reliability of Neutral Point Clamped vs. Cascaded H-Bridge InvertersDocument4 pagesThe Reliability of Neutral Point Clamped vs. Cascaded H-Bridge InvertersDevas ShuklaNo ratings yet

- Dec 2009Document8 pagesDec 2009Viswa ChaitanyaNo ratings yet

- Electronics 06 00038 PDFDocument20 pagesElectronics 06 00038 PDFsathishNo ratings yet

- Computational Tool For Sizing and Assessment of GridConnected Photovoltaic SystemsDocument10 pagesComputational Tool For Sizing and Assessment of GridConnected Photovoltaic Systemsel_ruso__83No ratings yet

- Electronics 10 01185 v2 PDFDocument9 pagesElectronics 10 01185 v2 PDFfeenNo ratings yet

- WWW Manaresults Co inDocument1 pageWWW Manaresults Co inmocharla sandeepNo ratings yet

- 1 PDFDocument6 pages1 PDFfadillahNo ratings yet

- Adsd ManualDocument69 pagesAdsd Manualsce21cs133No ratings yet

- EPM445 - Lecture 5 - Design and Performance AnalysisDocument36 pagesEPM445 - Lecture 5 - Design and Performance AnalysisSalma MahmoudNo ratings yet

- EEE312 EEE282 Lab4 Spring2015 PDFDocument5 pagesEEE312 EEE282 Lab4 Spring2015 PDFvognarNo ratings yet

- LaboratoryManualForOperationalAmplifiersAndLinearICs 3E PDFDocument130 pagesLaboratoryManualForOperationalAmplifiersAndLinearICs 3E PDFRajalingam BossNo ratings yet

- High SR 2 Stage Opamp TechPaperDocument3 pagesHigh SR 2 Stage Opamp TechPaperVarad KeniNo ratings yet

- EC6404-Linear Integrated Circuits Question BankDocument7 pagesEC6404-Linear Integrated Circuits Question BankkundaviNo ratings yet

- 1252-Transducer Engineering Question PaperDocument5 pages1252-Transducer Engineering Question Papermoney_kandan2004100% (1)

- Circuits - Lab - Handbook RA ZJSUDocument8 pagesCircuits - Lab - Handbook RA ZJSUlanxinNo ratings yet

- Linear and Digital Ic Applications RRDocument8 pagesLinear and Digital Ic Applications RRNizam Institute of Engineering and Technology LibraryNo ratings yet

- Electrical Machines IIDocument8 pagesElectrical Machines IIPremkumar KodamanchiliNo ratings yet

- Eee312 Eee282 Lab7 Spring2015Document6 pagesEee312 Eee282 Lab7 Spring2015vognarNo ratings yet

- InverterDocument31 pagesInverterĐẹp PhanNo ratings yet

- Lect03 Qual MetricsDocument14 pagesLect03 Qual MetricsKumar GaneshNo ratings yet

- Design and Simulation of Modified Ultra Low Power CMOS Comparator For Sigma Delta ModulatorDocument3 pagesDesign and Simulation of Modified Ultra Low Power CMOS Comparator For Sigma Delta ModulatorASHFAQ AHMEDNo ratings yet

- Linear and Digital Ic ApplicatonsDocument4 pagesLinear and Digital Ic ApplicatonsViswa ChaitanyaNo ratings yet

- 54102-mt - Analog & Digital Ic DesignDocument2 pages54102-mt - Analog & Digital Ic DesignSRINIVASA RAO GANTANo ratings yet

- 33ssc04 ZarabadiDocument7 pages33ssc04 ZarabadiArindam ChakrabortyNo ratings yet

- Aim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Document3 pagesAim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Jeyakumar VenugopalNo ratings yet

- Experiment 5 - Inverter CharacteristicsDocument7 pagesExperiment 5 - Inverter CharacteristicsGowtham SpNo ratings yet

- Course: EC2P001 Introduction To Electronics Lab: Indian Institute of Technology Bhubaneswar School of Electrical ScienceDocument5 pagesCourse: EC2P001 Introduction To Electronics Lab: Indian Institute of Technology Bhubaneswar School of Electrical ScienceAnik ChaudhuriNo ratings yet

- You're Reading A Preview. Unlock Full Access With A Free TrialDocument91 pagesYou're Reading A Preview. Unlock Full Access With A Free TrialbashasvuceNo ratings yet

- Case Study 2 - Marking GuideDocument8 pagesCase Study 2 - Marking GuideMBIEDA NGOMEGNI FRANK GAETANNo ratings yet

- Ee141 HW2 3 PDFDocument5 pagesEe141 HW2 3 PDFVidhya DsNo ratings yet

- 3 Hours / 100 Marks: Seat NoDocument6 pages3 Hours / 100 Marks: Seat Nosahil satputeNo ratings yet

- Question Paper Electrical Engineering For Group-B SelectionDocument4 pagesQuestion Paper Electrical Engineering For Group-B SelectionHimanku BoraNo ratings yet

- Efficient Current Bleeding Mixer For Wimax Applications: SciencedirectDocument7 pagesEfficient Current Bleeding Mixer For Wimax Applications: SciencedirectMihaela ElenaNo ratings yet

- Design and Simulation of A 100W Pure SinDocument4 pagesDesign and Simulation of A 100W Pure SinZeeshan Khan100% (1)

- IIT BH DNC Lab EE Manual Expt 4Document6 pagesIIT BH DNC Lab EE Manual Expt 4Priyesh PandeyNo ratings yet

- ELE341 Project OPAmpDocument4 pagesELE341 Project OPAmpbabycryyNo ratings yet

- Fy Comp Sem II Bec 22225 QP & Model AnswersDocument86 pagesFy Comp Sem II Bec 22225 QP & Model AnswersUmesh PatilNo ratings yet

- LIC - Question BankDocument8 pagesLIC - Question Banksriramraghu4_6423936No ratings yet

- Exercise 3 - VlsiDocument6 pagesExercise 3 - Vlsiujjwal mishraNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Design and Implementation of Portable Impedance AnalyzersFrom EverandDesign and Implementation of Portable Impedance AnalyzersNo ratings yet

- 2-Wire, Programmable RH + Temperature Transmitter: 2 X Isolated 4 20 Ma Outputs, Dual Led DisplayDocument2 pages2-Wire, Programmable RH + Temperature Transmitter: 2 X Isolated 4 20 Ma Outputs, Dual Led DisplaypiyushpandeyNo ratings yet

- Writeup On Automatic Turbine Runup SystemDocument18 pagesWriteup On Automatic Turbine Runup Systemlp mishraNo ratings yet

- Fire Water Jockey PumpDocument2 pagesFire Water Jockey PumpSalim BakhshNo ratings yet

- Heat DetectorDocument2 pagesHeat DetectorFederico GonzálezNo ratings yet

- Sony Dcrip5eDocument81 pagesSony Dcrip5ePaco RodriguezNo ratings yet

- Bulldozer Komatsu D65EP-12 - 0Document6 pagesBulldozer Komatsu D65EP-12 - 0Esti NugrohadiNo ratings yet

- S. R. 2007 - I (Internal)Document168 pagesS. R. 2007 - I (Internal)Vilas_123No ratings yet

- Arduino TMP36 Precision Temperature Sensor-GuideDocument1 pageArduino TMP36 Precision Temperature Sensor-GuideMC. Rene Solis R.100% (1)

- CX70 - Diagramas ElectricosDocument362 pagesCX70 - Diagramas ElectricosSDanielTorresPachasNo ratings yet

- TAMD41: Volvo Penta Inboard DieselDocument2 pagesTAMD41: Volvo Penta Inboard DieselDaliborNo ratings yet

- Job Vedc 2020 Cad DiklatDocument1 pageJob Vedc 2020 Cad DiklatPemesinan SMK Migas CepuNo ratings yet

- AN108-Designing A Half Bridge Converter Using A CoreMaster E2000Q CoreDocument7 pagesAN108-Designing A Half Bridge Converter Using A CoreMaster E2000Q Coreatkxyz777No ratings yet

- Parts Book GD511A-1 - LEPBG51103Document231 pagesParts Book GD511A-1 - LEPBG51103Denias MaleoNo ratings yet

- Vpvo Vdo Catalogue 2019 06 enDocument66 pagesVpvo Vdo Catalogue 2019 06 enstarykNo ratings yet

- PROFIBUS-DP BoardDocument98 pagesPROFIBUS-DP BoardLalo De GanteNo ratings yet

- Fairbanks Fb100Document44 pagesFairbanks Fb100edefrtgNo ratings yet

- SM1800 GBDocument4 pagesSM1800 GBAristides AnselmoNo ratings yet

- Drum Lifting MethodDocument4 pagesDrum Lifting MethodRajeev MaheshwariNo ratings yet

- OIL PUMP (Bus) MERCEDESDocument3 pagesOIL PUMP (Bus) MERCEDESKarthickNo ratings yet

- Inventory Custodian Slip - Appendix-59Document4 pagesInventory Custodian Slip - Appendix-59Maria Fatima ArnaizNo ratings yet

- TE InclinometerDocument4 pagesTE InclinometerPankaj RamoleNo ratings yet

- Automatic Transfer System Explained in Details Part 1Document4 pagesAutomatic Transfer System Explained in Details Part 1lam266No ratings yet

- Elevation Section: Dia 10. MM Galvanized Steel Screw With Acmon BoltDocument1 pageElevation Section: Dia 10. MM Galvanized Steel Screw With Acmon BoltROSE STONENo ratings yet

- Datavision Tft-Products Shortform (0,3 MB)Document2 pagesDatavision Tft-Products Shortform (0,3 MB)Adam BerdyszakNo ratings yet

- 2008 CX 7 Maintenance ScheduleDocument6 pages2008 CX 7 Maintenance Scheduleuriel avila garciaNo ratings yet