Professional Documents

Culture Documents

Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation Principles

Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation Principles

Uploaded by

Sindhu RajanOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation Principles

Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation Principles

Uploaded by

Sindhu RajanCopyright:

Available Formats

VERILOG HDL BASICS

LAB ASSIGNMENTS

Lab work 1. Study of Module Declaration and Module Instantiation Principles

Write the module declaration for T Flip-Flop with information input - T, clock input – clk, Q and

Q_bar outputs. Do not care about module internals. Write the Verilog description of 4 –bit

counter instantiating the previously declared TFFs.

Lab work 2. Study of Basic Operations for Simulation Control

Task 1

Practice the following numbers

a) A 4 bit hexadecimal number with 2 least significant bits unknown.

b) Decimal number 299 as a sized 16 bit number.

c) An unsized hex number 1112.

Task 2

Declare the following in VERILOG.

a) A 16 bit vector net data_in.

b) A 8 bit register named data_out

c) An integer called sweep_value;

Task 3

A number contained in a reg variable idata is 4’b1001. Write a statement to display its value on

the screen. Use the system task $display.

Lab work 3. Study of Port Connection Rules

Write the module definition for 1 bit full adder with a and b inputs, cin carry-in input, sum and

cout outputs. Declare a top-level module stimulus and instantiate the full adder. Write the correct

port types in the top-level module.

Lab work 4. Study of Gate-Level Design Principles

Task 1

Write the Verilog description for RS latch using NOR gates. Include delays for 1 unit when

instantiating the NOR gates. Write the stimulus module for the RS latch, using the following

table, and verify output.

set reset qn+1

0 0 qn

0 1 0

1 0 1

1 1 ?

Verilog HDL Basics Lab Assignments Page 1 of 3

Task 2

Write the Verilog description for D latch using NAND gates. Include delays for 1 unit when

instantiating the NAND gates. Write the stimulus module for the D latch, using the following

table, and verify output.

D clk qn+1

0 0 qn

1 0 qn

0 1 0

1 1 1

Task 3

Design a 2 to 1 multiplexer using bufif0 and bufif1 gates.

The delay specification for gates b_1 and b_2 as follows:

Min Typ Max

Rise 1 2 3

Fall 3 4 5

Turnoff 5 6 7

Check the results using VCS for simulations.

Task 4

Write the gate-level description of one-bit full adder. Apply the stimulus and check the results

using VCS simulator.

Lab work 5. Study of Dataflow Design Principles

Task 1

Write the dataflow description of negative edge triggered D Flip Flop with asynchronous clear.

Simulate the design using VCS and verify the simulation results.

Task 2

Design a 4 bit adder with carry lookahead. Use dataflow statements to describe the functionality.

Apply stimulus and check the results by VCS simulations.

Task 3

Write the dataflow description of master-slave JK Flip Flop with low active clear signal. Data

gets latched on positive edge of clock, and the output of the Flip Flop appears on the negative

edge of clock.

Verilog HDL Basics Lab Assignments Page 2 of 3

Task 4

Write the dataflow description for the 4-bit synchronous counter. Use the master-slave JK Flip

Flop to design the counter. Counting is disabled when enable signal is low. Check the

functionality of the counter by VCS simulations.

Lab work 6. Study of Behavioral Design Principles

Task 1

Declare a register called oscillate. Initialize it to 0 and make it toggle very 30 time units. Do not

use always statement. (hint: use the forever loop).

Task 2

Define a function to multiply two 4-bit numbers a and b. The output is an 8-bit value. Invoke the

function by using stimulus and check the simulation results by VCS simulations.

Task 3

Using the wait statement, design a level-sensitive latch that takes clock and d as inputs and q as

output. q = d whenever clock = 1.

Task 4

Define a task to compute the factorial of a 4-bit number. The output is a 32-bit value. The result

is assigned to the output after a delay of 10 time units

Task 5

Design a negative edge-triggered D-flipflop (DFF) with synchronous clear, active high. Use

behavior statement only. Design a clock with a period of 10 units and test the DFF.

Lab work 7. Study of RTL Design Principles

Task 1

Design a 3-to-8 decoder, using a Verilog RTL description. A 3-bit input a[2:0] is provided to the

decoder. The output of the decoder is out [7:0]. The output bit indexed by a[2:0] gets the value 1,

the other bits are 0. Synthesize the decoder, using any technology library available to you. Apply

identical stimulus to the RTL and the gate-level netlist and compare the output.

Task 2

Write the RTL description for 4-bit full adder with carry lookahed. Synthesize the full adder,

using a demo technology library. Apply stimulus to the RTL and the gate-level netlist and

compare the output.

Verilog HDL Basics Lab Assignments Page 3 of 3

You might also like

- Questa Tool Usage Beginers GuideDocument131 pagesQuesta Tool Usage Beginers GuideharishkashaNo ratings yet

- Sram Part1Document36 pagesSram Part1api-285860375No ratings yet

- 72 UVM Callbacks Vs Factory PDFDocument1 page72 UVM Callbacks Vs Factory PDFQuastnNo ratings yet

- Register Transfer Level Design With Verilog: Verilog Digital System Design Z. Navabi, Mcgraw-Hill, 2005Document77 pagesRegister Transfer Level Design With Verilog: Verilog Digital System Design Z. Navabi, Mcgraw-Hill, 2005I am number 4No ratings yet

- Lec4 VerilogDocument58 pagesLec4 VerilogRohit BhelkarNo ratings yet

- 03-Verilog Modules and Ports-MergedDocument170 pages03-Verilog Modules and Ports-MergedqwertyNo ratings yet

- Chapter10 VerilogDocument62 pagesChapter10 VerilogdilipbagadiNo ratings yet

- VerilogexampleDocument20 pagesVerilogexampleGayathri SankarNo ratings yet

- Test Benches in VerilogDocument16 pagesTest Benches in VerilogSharan ChaitanyaNo ratings yet

- System Verilog: Program Block & InterfaceDocument38 pagesSystem Verilog: Program Block & InterfaceMeghana VeggalamNo ratings yet

- Verilog Imp...Document105 pagesVerilog Imp...Arun JyothiNo ratings yet

- 2 Mark Questions & AnswersDocument6 pages2 Mark Questions & AnswersMuthu KumarNo ratings yet

- Notes3 PDFDocument97 pagesNotes3 PDFrahulsportyNo ratings yet

- VLSI Cadance ManualDocument84 pagesVLSI Cadance ManualTony ParkerNo ratings yet

- FSM Design Using Verilog - ElectrosoftsDocument7 pagesFSM Design Using Verilog - ElectrosoftsAbhishek KumarNo ratings yet

- SVTBDocument222 pagesSVTBsandeepNo ratings yet

- Class 12 TopicsDocument43 pagesClass 12 Topicsgideontargrave7No ratings yet

- System Verilog - Verification Methodology ManualDocument36 pagesSystem Verilog - Verification Methodology ManualpearlkrishNo ratings yet

- Sandeepani VerilogDocument354 pagesSandeepani Verilogadi_risingsunNo ratings yet

- System Verilog TrainingDocument2 pagesSystem Verilog TrainingVlsi GuruNo ratings yet

- Digital Electronics QuestionsDocument8 pagesDigital Electronics QuestionsShivamahendar SunkaNo ratings yet

- Structural Data Types: Wire and RegDocument25 pagesStructural Data Types: Wire and RegRAGUL RAJ SNo ratings yet

- Timing Design in Digital Systems: Dr. Paul D. FranzonDocument24 pagesTiming Design in Digital Systems: Dr. Paul D. FranzonMaheshNo ratings yet

- Limit Time Oerfor $99: Verilog Tips and Interview QuestionsDocument9 pagesLimit Time Oerfor $99: Verilog Tips and Interview QuestionsvijenderNo ratings yet

- Verilog HDL Introduction: TextbookDocument41 pagesVerilog HDL Introduction: TextbookAbhishek RanjanNo ratings yet

- Design Verification Engineer RTL in Austin TX Resume Sumaira KhowajaDocument3 pagesDesign Verification Engineer RTL in Austin TX Resume Sumaira KhowajaSumairaKhowaja4No ratings yet

- Verilog Modules and PortsDocument28 pagesVerilog Modules and PortsJayesh Baviskar100% (1)

- Verilog ProgramDocument24 pagesVerilog ProgramRahul BhatiaNo ratings yet

- Lecture 2 Verilog PDFDocument35 pagesLecture 2 Verilog PDFkayleNo ratings yet

- Ones CounterDocument28 pagesOnes CounterGOKUL TNo ratings yet

- Vlsi Lab Manual 2010Document88 pagesVlsi Lab Manual 2010Karthik V KalyaniNo ratings yet

- Up Down CounterDocument20 pagesUp Down Countersumi36117No ratings yet

- VerilogDocument61 pagesVerilogSathish Kumar100% (1)

- Interfacing and Some Common Building Blocks: Coe 111: Advanced Digital DesignDocument35 pagesInterfacing and Some Common Building Blocks: Coe 111: Advanced Digital DesignFrancisNo ratings yet

- VerilogDocument18 pagesVerilogvortex2910_899547857No ratings yet

- RTL Verilog Navabi PDFDocument294 pagesRTL Verilog Navabi PDFSiva chowdaryNo ratings yet

- Digital Logic DesignDocument3 pagesDigital Logic Designthatflamyguy2216No ratings yet

- Verilog Parameters and OperatorsDocument25 pagesVerilog Parameters and OperatorsR INI BHANDARINo ratings yet

- Vlsi World - Verilog Code For RAM & ROM12456Document6 pagesVlsi World - Verilog Code For RAM & ROM12456gssharma888No ratings yet

- 2005-SNUG-Paper SystemVerilog Unique and PriorityDocument24 pages2005-SNUG-Paper SystemVerilog Unique and Priorityvaibhav27aprilNo ratings yet

- Setup and Hold TimeDocument17 pagesSetup and Hold TimeVamsi SomisettyNo ratings yet

- SV Lab ManualDocument20 pagesSV Lab ManualShakeel ScetNo ratings yet

- 19 MooreMealyDocument23 pages19 MooreMealynvsrox100% (1)

- Vlsi/Fpga Design and Test CAD Tool Flow in Mentor Graphics: Victor P. NelsonDocument44 pagesVlsi/Fpga Design and Test CAD Tool Flow in Mentor Graphics: Victor P. NelsonAvinash B RajNo ratings yet

- Timing Analysis: Elec 326 Sequential Circuit TimingDocument43 pagesTiming Analysis: Elec 326 Sequential Circuit TimingArpit KapoorNo ratings yet

- Dvcon2017 Uvm Debug Lib FinalDocument9 pagesDvcon2017 Uvm Debug Lib FinalIkshvaku ModiNo ratings yet

- VLSI Guru Ethernet-Mac-feb22-notes - VLSI GuruDocument80 pagesVLSI Guru Ethernet-Mac-feb22-notes - VLSI Gurudvlsi dvlsiNo ratings yet

- Radix-4 Modified Booth's Multiplier Using Verilog RTLDocument10 pagesRadix-4 Modified Booth's Multiplier Using Verilog RTLPrem KumarNo ratings yet

- Adding Spare CellsDocument4 pagesAdding Spare CellsmanojkumarNo ratings yet

- Io MultiplexingDocument19 pagesIo Multiplexingsubramanyam62No ratings yet

- Verilog HDL Training GuideDocument67 pagesVerilog HDL Training GuideSreekanth PagadapalliNo ratings yet

- Verilog HDL - IntroductionDocument59 pagesVerilog HDL - IntroductionBhargavi AndraNo ratings yet

- I2c Bit Controller in VerilogDocument14 pagesI2c Bit Controller in VerilogHarish TellaNo ratings yet

- 15 SVAssertionsLecture1Document20 pages15 SVAssertionsLecture1Mihaela ScanteianuNo ratings yet

- RISC-V RV32I RTL Design Using Verilog HDLDocument1 pageRISC-V RV32I RTL Design Using Verilog HDLSiddharth GuptaNo ratings yet

- Design & Verification of AMBA APB ProtocolDocument4 pagesDesign & Verification of AMBA APB ProtocolKrishnajithKjNo ratings yet

- Interview QuestionsDocument29 pagesInterview Questionspritam044100% (1)

- DCD QB Dec 2023 StudentDocument7 pagesDCD QB Dec 2023 StudentPranav VasudevNo ratings yet

- Lec25 Place RouteDocument36 pagesLec25 Place RouteSindhu RajanNo ratings yet

- Sequential CircuitsDocument212 pagesSequential CircuitsSindhu RajanNo ratings yet

- Seer VerilogDocument59 pagesSeer VerilogSindhu RajanNo ratings yet

- Sear Digital BasicsDocument27 pagesSear Digital BasicsSindhu RajanNo ratings yet

- Protech 203 ManualDocument40 pagesProtech 203 ManualLuciano SantanaNo ratings yet

- Scs 1806Document12 pagesScs 1806botelhodurskiNo ratings yet

- Charger Bettery SHARYSDocument4 pagesCharger Bettery SHARYSYosri KanounNo ratings yet

- Avh P5750DVDDocument212 pagesAvh P5750DVDmarco agudeloNo ratings yet

- Mdaq AN7 EncoderDocument9 pagesMdaq AN7 EncoderMOHAMED IBRAHIMNo ratings yet

- IP Phone InstallationDocument8 pagesIP Phone InstallationPrabath KalanaNo ratings yet

- 2SB1132 BluerocketelectronicsDocument6 pages2SB1132 BluerocketelectronicsAno InkNo ratings yet

- Experiment The PN Junction: Band Theory of SolidsDocument7 pagesExperiment The PN Junction: Band Theory of SolidsVaibhav bhargavaNo ratings yet

- Cisco - Understand Gpon TechnologyDocument20 pagesCisco - Understand Gpon TechnologyNwayOo YeNo ratings yet

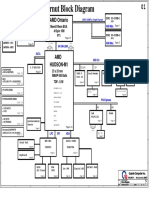

- Amd Ontario: 413pin 18W 19Mmx19Mm Bga Ft1Document31 pagesAmd Ontario: 413pin 18W 19Mmx19Mm Bga Ft1Muhammad IlyasNo ratings yet

- Pioneer Xr-Vs66 Vs88Document30 pagesPioneer Xr-Vs66 Vs88M'ncarriCintadllmhatikkmuu LloveNo ratings yet

- SUN-FOS-1×2 Mechanical Optical SwitchDocument3 pagesSUN-FOS-1×2 Mechanical Optical SwitchMangoNo ratings yet

- ZXONE 8300&8500&8700 Acceptance Test Guide - R1.7Document441 pagesZXONE 8300&8500&8700 Acceptance Test Guide - R1.7Felipe Ignacio Lopez GordilloNo ratings yet

- Dry Fly Ash Bin Weighing SystemDocument15 pagesDry Fly Ash Bin Weighing SystemonrabiNo ratings yet

- Eecs 2012 265 PDFDocument12 pagesEecs 2012 265 PDFSaeid MirNo ratings yet

- Microsoft Word - Revised Microcomputer & Interfacing - RepaiDocument152 pagesMicrosoft Word - Revised Microcomputer & Interfacing - RepaimickygbNo ratings yet

- Electrical Test EquipmentDocument23 pagesElectrical Test EquipmentChristine joy VelezNo ratings yet

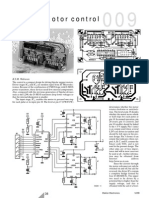

- Driver L297 + L6203Document2 pagesDriver L297 + L6203TatiiieleeeNo ratings yet

- ANT-A194518R0v06-1867-001 DatasheetDocument2 pagesANT-A194518R0v06-1867-001 DatasheetDavid NigraNo ratings yet

- Yl 007M2BDocument34 pagesYl 007M2BFernando GarcíaNo ratings yet

- Interleave Division Multiple Access (Idma)Document21 pagesInterleave Division Multiple Access (Idma)Parth PatelNo ratings yet

- Lege0001 01Document21 pagesLege0001 01DEYNERNo ratings yet

- Lecture - Switching Systems and Multistage NetworkDocument29 pagesLecture - Switching Systems and Multistage NetworkMOHAMMED FAYEZ KHANNo ratings yet

- Form Substation+400V+Switchboard+Test+FormDocument2 pagesForm Substation+400V+Switchboard+Test+Formyudo heruNo ratings yet

- DVD Camcorder: VP-DC161 (I) /DC161W (I) /DC161WB (I) /DC163 (I) /DC165W (I) /DC165WB (I)Document132 pagesDVD Camcorder: VP-DC161 (I) /DC161W (I) /DC161WB (I) /DC163 (I) /DC165W (I) /DC165WB (I)JohnnyTF1000No ratings yet

- IM NT MGCB MCB Global Guide - 1 PDFDocument540 pagesIM NT MGCB MCB Global Guide - 1 PDFGilder GonzalezNo ratings yet

- Users-Manual-4630833 TPMSDocument2 pagesUsers-Manual-4630833 TPMSmarcelo ustarezNo ratings yet

- PT2313L PDFDocument3 pagesPT2313L PDFMaugrys Castillo100% (1)

- SRP-350 v2 SVC EngDocument125 pagesSRP-350 v2 SVC EngMichael HanniganNo ratings yet

- Progress in Electromagnetics Research B, Vol. 49, 155-176, 2013Document22 pagesProgress in Electromagnetics Research B, Vol. 49, 155-176, 2013srikandiujungNo ratings yet